# PCI-946-1 & P3S440BX

PENTIUM III SBC

Technical Reference Manual

Version 1.4, June 2002

Note: The latest releases of the Technical Reference Manuals are available at: ftp://ftp.kontron.ca/Support/Product Manuals/

Ref.: M946R1\_TECH

# Historical

| Rel.                                                              | Date     | Comments                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|-------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.0                                                               | Aug-1999 | Initial document release.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 1.1                                                               | Nov-1999 | N/A                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 1.2                                                               | Sep-2000 | N/A                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 1.3                                                               | Mar-2002 | - Replace all Teknor occurrences by Kontron.<br>- Update to Kontron Logo.                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 1.4 Apr-23-2002 - Add lin - In sect: " The F - Change - Appendent |          | <ul> <li>Remove "Documentation Survey" manual revision identification.</li> <li>Add link to the FTP site on initial page.</li> <li>In section 1.1 replace "The PCI-948 SBC and P3S440BX" by "The PCI-946-1 SBC and P3S440BX"</li> <li>Changed the cover page for the new Kontron template.</li> <li>Appendix, section D, page D-8, J20 and J21, changed the PS/2 connector illustration (pin 1 and 2 were inverted)</li> </ul> |  |  |

## **FOREWORD**

The information in this document is provided for reference purposes only. Kontron does not assume any liability for the application of information or the use of products described herein.

This document may contain information or refer to products protected by the copyrights or patents of others and does not convey any license under the patent rights of Kontron, nor the rights of others.

Printed in Canada. Copyright 2002 by Kontron Inc., Boisbriand, Qc J7G 2A7.

#### PCI-946-1 and P3S440BX Technical Reference Manual

6. Is some information not properly or clearly explained?  $\square$  Yes  $\square$  No

7. Additional comments (suggestions, errors found, etc.):

If yes, can you comment?\_\_\_\_\_

## Please send your comments to:

Kontron Inc Technical Writing dept. 616 Curé Boivin, Boisbriand (Québec) CANADA J7G 2A7

|         | optiona. |  |

|---------|----------|--|

|         |          |  |

| Name    |          |  |

| Company |          |  |

| Address |          |  |

|         |          |  |

|         |          |  |

# **FCC Compliance Statement**

# Warning

Changes or modifications to this unit not expressly approved by the party responsible for the compliance could void the user's authority to operate this equipment.

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference, in which case the user will be required to correct the interference at his or her own expense.

# **European Statement**

# Warning

This is a class B product. If not installed in a properly shielded enclosure, and used in accordance with the instruction manual, this product may cause radio interference in which case the user may be required to take adequate measures at his or her own expense.

# **Safety Standard**

UL Recognized Component, File # E186339 vol. 1 section 2

# Care and handling precautions for Lithium batteries

- Do not short circuit

- Do not heat or incinerate

- Do not charge

- Do not deform or disassemble

- Do not apply solder directly

- Do not mix different types or partially used batteries together

- Always observe proper polarities

# **READ ME FIRST**

Your computer board has a standard non-rechargeable lithium battery. To preserve the battery lifetime, the battery enable jumper is removed when you receive the board.

#### **EXERCISE CAUTION WHILE REPLACING LITHIUM BATTERY**

#### WARNING

There is danger of explosion if battery is incorrectly replaced. Replace only with the same or equivalent type recommended by the manufacturer. Dispose of used batteries according to the manufacturer's instructions.

#### **ATTENTION**

Il y a danger d'explosion s'il y a remplacement incorrect de la batterie.

Remplacer uniquement avec une batterie du même type ou d'un type équivalent recommandé par le constructeur. Mettre au rebut les batteries usagées conformément aux instructions du fabriquant.

#### **ACHTUNG**

Explosionsgefahr bei falschem Batteriewechsel. Verwenden Sie nur die empfohlenen Batterietypen des Herstellers. Entsorgen Sie die verbrauchten Batterien laut Gebrauchsanweisung des Herstellers.

#### **ATENCION**

Puede explotar si la pila no este bien reemplazada.

Solo reemplazca la pila con tipas equivalentes segun las instrucciones del manifacturo. Vote las pilas usadas segun las instrucciones del manifacturo.

#### **IMPORTANT**

This manual covers both PCI-946-1 and P3S440BX Single Board Computers where the difference resides in the usage of the Celeron® and Pentium® III® processor respectively.

#### POWERING-UP THE BOARD

## If you should encounter a problem, verify the following items:

Make sure that all connectors are properly connected.

Check your boot diskette.

If the board still does not start up properly, you should try booting your system with the PCI-946-1 and P3S440BX installed in the system, a monitor and a mouse connected to the board. This is the minimum required to verify the board's operation.

If you still are not able to verify your board, please refer to the emergency Procedure in the Appendix Section.

If you still are not able to get your board up and running, contact our technical Support department for assistance.

#### BIOS UPGRADE & AUTOMATIC CPLD HARDWARE UPGRADE

During the first system boot up after you update the Boot Block Flash BIOS with the UPGBIOS utility, the BIOS may need to upgrade the CPLD devices. In such a case, do not interrupt the system in any way (power down, reset, mouse or keyboard functions). The devices will be damaged and your board rendered inoperative if you disturb the CPLD hardware upgrade process!

If your device upgrade was successful, the following message is displayed under the "Status:" line prior to rebooting:

$\label{thm:pdate_complete} \mbox{Update complete successfully, wait for the automatic reboot.}$

Rebooting in 5 second(s).

If the update is not successful, the following message appears under the "Status:" line:

ERROR: general failure programming CPLDs!

Please contact Kontron's technical support.

You must contact Kontron's technical support for further instructions.

#### ADAPTER CABLES

While adapter cables are provided from various sources, the pinout is often different. The direct crimp design offered by Kontron allows the simplest cable assembly. All cables are available from Kontron Sales Department.

#### UNPACKING AND SAFETY PRECAUTIONS

#### STATIC ELECTRICITY

Since static electricity can cause damage to electronic devices, the following precautions should be taken:

- 1. Keep the board in its anti-static package, until you are ready to install it.

- Touch a grounded surface or wear a grounding wrist strap before removing the board from its package; this will discharge any static electricity that may have built up in your body.

- 3. Handle the board by the edges.

# **Storage Environment**

Electronic boards are sensitive devices. Do not handle or store devices near strong electrostatic, electromagnetic, magnetic or radioactive fields.

# **Power Supply**

Before any installation or setup, ensure that the board is unplugged from power sources or subsystems.

# Unpacking

Follow these recommendations while unpacking:

- 1. After opening the box, save it and the packing material for possible future shipment.

- 2. Remove the board from its anti-static wrapping and place it on a grounded surface.

- 3. Inspect the board for damage. If there is any damage or missing items, notify Kontron immediately.

When unpacking you will find:

- 1. One PCI-946-1 or P3S440BX Single Board Computer.

- 2. One Quick Reference sheet

- 3. One CDROM containing drivers.

# **TABLE OF CONTENTS**

| 1    | PK    | RODUCT DESCRIPTION                            |     |

|------|-------|-----------------------------------------------|-----|

| 1.   | .1    | PRODUCT OVERVIEW                              | 1-1 |

| 1    | .2.   | PCI-946-1 and P3S440BX Product Specifications | 1-2 |

| 2. ( | ONB   | BOARD FEATURES                                |     |

| 2    | .1.   | System Core                                   | 2-1 |

|      | 2.1.1 | .1. Processors                                | 2-1 |

|      | 2.1.2 | .2. Memory                                    | 2-2 |

|      | 2.1.3 | .3. Battery                                   | 2-3 |

| 2.   | .2.   | Ethernet                                      | 2-4 |

| 2    | .3.   | I/O Devices                                   | 2-5 |

|      | 2.3.1 | .1. I/O Connections                           | 2-5 |

|      | 2.3.2 | .2. Keyboard                                  | 2-6 |

|      | 2.3.3 | .3. PS/2 Mouse                                | 2-6 |

| 2    | .4.   | Parallel Port                                 | 2-7 |

| 2    | .5.   | Serial Ports                                  | 2-8 |

|      | 2.5.1 | .1. Serial Port 1                             | 2-8 |

|      | 2.5.2 | .2. Serial Port 2                             | 2-9 |

| 2.6.        | US             | 2-1                                                                                           | 1  |

|-------------|----------------|-----------------------------------------------------------------------------------------------|----|

| 2.7.        | Sto            | orage Devices2-1                                                                              | 12 |

| 2.7         | 7.1.           | Floppy Disk Drives                                                                            | 12 |

| 2.7         | 7.2.           | IDE Devices                                                                                   | 13 |

| 2.7         | 7.3.           | SCSI Devices                                                                                  | 14 |

| 2.7         | 7.4.           | Compact FlashDisk                                                                             | 16 |

| 2.8.        | Vic            | deo Features2-1                                                                               | ۱7 |

| 2.9.        | Pov            | wer Supply2-1                                                                                 | 18 |

| 3 IN        | JSTA           | ALLING THE BOARD                                                                              |    |

| <i>J</i> 11 | IDIA           | ALLING THE BOARD                                                                              |    |

| 3.1.        | PC             | CI-946 & P3S440BX Connector and Jumper Locations3                                             | -1 |

| 3.2.        | Set            | tting jumpers3                                                                                | -2 |

| 3.3.        | SU             | PERVISOR REGISTERS3                                                                           | -5 |

| 3.3         | 3.1.           | Register x90h: Serial port                                                                    | -6 |

| 3.3         | 3.2.           | Register X91h: Reset History & CPU Fault                                                      | -7 |

| 3.3         | 3.3.           | Register x92h: Clearing Reset History & Lock for Watchdog3                                    | -7 |

|             | 3.4.<br>onnect | Register x93h: Silicon ID Chip Interface, Local I <sup>2</sup> C, System Monitor or Interface | -8 |

| 3.3         | 3.5.           | Register x94h & x95h                                                                          | -8 |

| 3.3         | 3.6.           | Register x96h: Programmable Watchdog                                                          | -8 |

| 3.3         | 3.7.           | Register x97h: NMI sources & mask                                                             | -9 |

| 3.4. Or | aboard Interconnectivity3-10                       |

|---------|----------------------------------------------------|

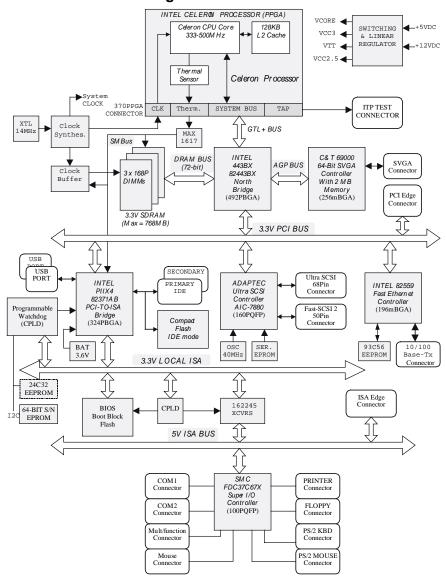

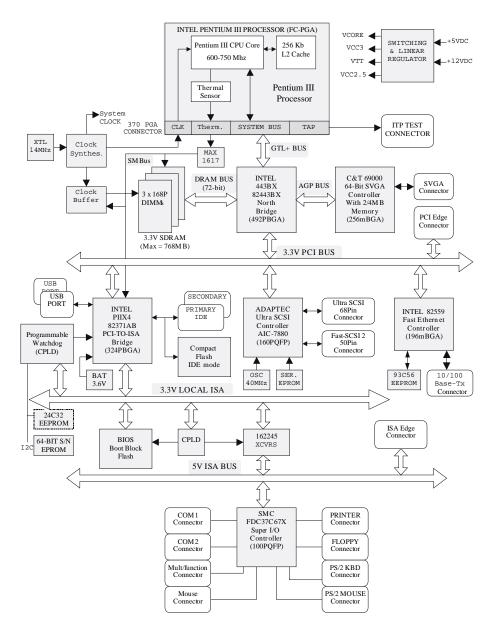

| PCI-946 | 5-1 Block Diagram3-10                              |

| 3.4.2.  | P3S440BX Block Diagram3-11                         |

| 3.4.3.  | Single Board Computer Main Features                |

| 3.4.4.  | Celeron and Pentium <sup>®</sup> III processors    |

| 3.4.5.  | North Bridge Chipset                               |

| 3.4.6.  | 21554 PCI-to-PCI Bridge3-13                        |

| 3.4.7.  | 82371AB PCI-to-ISA Bridge / IDE Xcelerator (PIIX4) |

| 3.5. Cu | stomizing the Board3-14                            |

| 3.5.1.  | Processor                                          |

| 3.5.2.  | Backup Battery                                     |

| 3.5.3.  | Installing the Memory                              |

| 3.5.4.  | Power Fail Monitoring                              |

| 3.5.5.  | Watchdog                                           |

| 3.5.6.  | Thermal Management                                 |

| 3.6. IN | STALLING DRIVERS 3-21                              |

| 3.6.1.  | SCSI Drivers                                       |

| 3.6.2.  | Video Drivers                                      |

| 3.6.3.  | Ethernet Drivers                                   |

| 3.6.4.  | Chipset Driver for Windows 95                      |

| 3.6.5.  | Other Drivers                                      |

# 4. SOFTWARE SETUPS

| 4.1. | AW   | VARD BIOS Setup Program                      | 4-1  |

|------|------|----------------------------------------------|------|

| 1.2  | Aco  | cessing the BIOS setup program               | 4-2  |

| 4.2  | 2.1. | Main Menu                                    | 4-4  |

| 4.2  | 2.2. | Setups                                       | 4-5  |

| 4.2  | 2.3. | Standard CMOS Setups                         | 4-6  |

| 4.2  | 2.4. | BIOS Features Setup                          | 4-7  |

| 4.2  | 2.5. | Chipset Features Setup                       | 4-9  |

| 4.2  | 2.6. | Power Management Setup                       | 4-11 |

| 4.2  | 2.7. | PnP/PCI Configuration                        | 4-13 |

| 4.2  | 2.8. | CPU/Board Features Setup                     | 4-14 |

| 4.2  | 2.9. | Integrated Peripherals                       | 4-15 |

| 1.3  | Up   | dating or Restoring the BIOS in Flash        | 4-16 |

| 4.3  | 3.1  | UBIOS.EXE 4.0 - BIOS update and copy utility | 4-16 |

| 4.3  | 3.2  | How to do a successful update                | 4-16 |

| 4.3  | 3.3  | How to do a successful copy                  | 4-17 |

| 4.3  | 3.4  | UBIOS - Interactive Mode                     | 4-18 |

| 4.3  | 3.5  | UBIOS – Batch Mode                           | 4-25 |

| 4.4  | VT   | 100 Mode                                     | 4-26 |

| 4.4  | l.1  | Requirements                                 | 4-26 |

| 4.4  | 1.2  | Setup & Configuration                        | 4-26 |

| 4.4  | 1.3  | Running Without a Terminal                   | 4-27 |

# 5 APPENDICES

| Α | ME  | MORY & I/O MAPS                               | A-1 |

|---|-----|-----------------------------------------------|-----|

|   | A.1 | Memory Mapping                                | A-1 |

|   | A.2 | I/O Mapping                                   | A-2 |

| В | IRO | Q AND DMA LINES                               | B-3 |

|   | B.1 | IRQ Lines                                     | B-3 |

|   | B.2 | DMA Channels                                  | B-3 |

| С | ВО  | OARD DIAGRAMS                                 | C-1 |

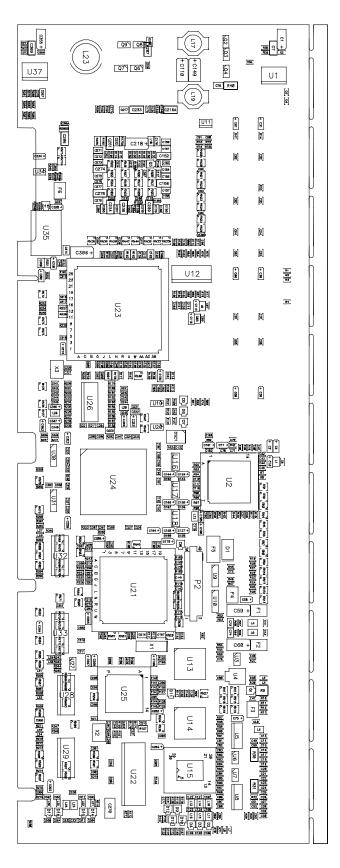

|   | C.1 | Assembly Top Diagram - PCI-946-1 and P3S440BX | C-1 |

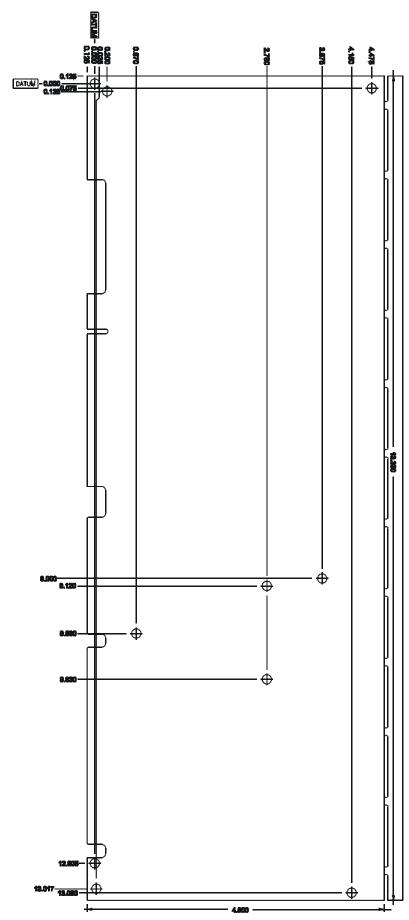

|   | C.2 | Mounting Holes - PCI-946-1 and P3S440BX       | C-2 |

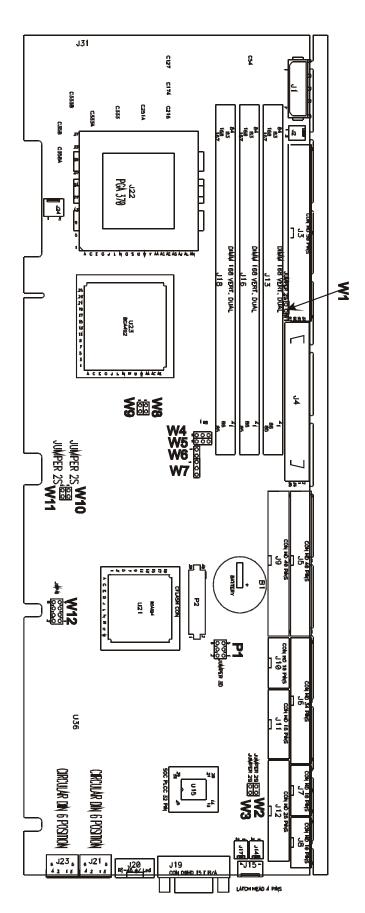

|   | C.3 | Connector C.S PCI-946-1 and P3S440BX          | C-3 |

| D | Со  | nnector Pinouts                               | D-1 |

|   | D.1 | PCI-946-1 AND P3S440BX Connectors and Headers | D-1 |

|   | D.2 | CONNECTOR PINOUTS                             | D-2 |

|   |     | D.2.1 Power Supply Connector (J1)             | D-2 |

|   |     | D.2.2 EIDE/SCSI ACTIVITY LED Header (J2)      | D-2 |

|   |     | D.2.3 8-bit SCSI Interface Connector (J3)     | D-2 |

|   |     | D.2.4 16-bit SCSI Interface Connector (J4)    | D-3 |

| D.2.5  | Primary & Secondary EIDE Connector (J5 & J9) | D-4  |

|--------|----------------------------------------------|------|

| D.2.6  | Floppy Drive Connector (J6)                  | D-4  |

| D.2.7  | Serial Port 2 & 1 - (J7 & J8) RS-232         | D-5  |

| D.2.8  | Serial Port 2 - (J8) RS-422/RS-485           | D-5  |

| D.2.9  | USB Header (J10)                             | D-5  |

| D.2.10 | Multi-Function Connector (J11)               | D-5  |

| D.2.11 | Parallel Port Connector (J12)                | D-6  |

| D.2.12 | Standard Mode                                | D-6  |

| D.2.13 | EPP Mode                                     | D-6  |

| D.2.14 | ECP Mode                                     | D-7  |

| D.2.15 | External Battery Header (J14)                | D-7  |

| D.2.16 | PS/2 Mouse Header (J15)                      | D-7  |

| D.2.17 | Power Button Connector (J17)                 | D-7  |

| D.2.18 | CRT VGA Interface Connector (J19)            | D-8  |

| D.2.19 | Ethernet 10Base-T/100Base-TX Connector (J20) | D-8  |

| D.2.20 | PS/2 Mouse Connector (J21)                   | D-8  |

| D.2.21 | PS/2 Keyboard Connector (J23)                | D-8  |

| D.2.22 | CPU Fan Header (J24)                         | D-9  |

| D.2.23 | CompactFlash™ Disk Pinout (P2)               | D-9  |

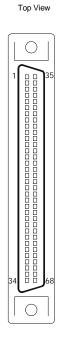

| D.2.24 | PCI Bus Edge Connector                       | D-10 |

| D.2.25 | ISA Bus Edge Connector                       | D-11 |

| E | BIC | DS SETUP ERROR CODES                                        | E-1 |

|---|-----|-------------------------------------------------------------|-----|

|   | E.1 | POST Beep                                                   |     |

|   | E.2 | POST Messages                                               | E-1 |

|   |     | E.1.1 If a message is displayed, it will be accompanied by: |     |

|   | E.3 | Error Messages                                              | E-2 |

|   | E.4 | POST Codes                                                  | E-3 |

| F | EM  | IERGENCY PROCEDURE                                          | F-1 |

|   | F.1 | How to run Emergency Procedure                              | F-1 |

|   |     | F.1.1 To run an EMERGENCY PROCEDURE, proceed as follows:    | F-1 |

|   | F.2 | Generate an Emergency Floppy Diskette :                     | F-2 |

|   |     | F.2.1 Use a system that has a 1.44 Mbytes floppy drive A    | F-2 |

| G | GE  | TTING HELP                                                  | G-1 |

|   | G.1 | LIMITED WARRANTY                                            | G-1 |

|   | G.2 | Returning Defective Merchandise                             | G-2 |

# 1 PRODUCT DESCRIPTION

- 1. PRODUCT OVERVIEW

- 2. PRODUCT SPECIFICATIONS

# 1.1 PRODUCT OVERVIEW

The PICMG compliant PCI-946-1 Single Board Computer (SBC) is built around an Intel Celeron processor running at a speed ranging from 300 to 433 MHz, in a PPGA package supported by an on die 128KB, 64-bit L2 Cache and a 66MHz Front Side Bus (FSB)

The PICMG compliant P3S440BX SBC is built around an Intel Pentium® III processor running at a speed ranging from 600 to 750 MHz, in a FC-PGA package supported by an on die 256KB, 64-bit L2 Cache and a 100MHz FSB.

The PCI-946-1 SBC and P3S440BX both offer the superior performance of the P6 microarchitecture meeting the unique low power consumption and smaller package requirements of the embedded application market.

# 1.2. PCI-946-1 AND P3S440BX PRODUCT SPECIFICATIONS

| FEATURES                    | DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Processor Option            | PCI-946 Rev. 1: PICMG Single Board Computer supports Intel's PPGA Celeron Processor (370-pin PPGA 'Plastic Pin Grid Array') at 300, 366, and 433MHz. Supports Front Side Bus (FSB) speeds of 66 MHz  P3S440BX: PICMG Single Board Computer supports Intel's FC-PGA Pentium® III Processor (370-pin FC-PGA form factor) at 600, 700, and 750MHz Supports Front Side Bus (FSB) speeds of 100MHz |  |  |  |  |

|                             | The Pentium® III uses a 370-pin FC-PGA form factor.                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Chipset                     | The Intel 82440BX AGPset.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Internal Secondary<br>Cache | 16/16Kbytes Instruction/Data CPU-internal L1 cache.                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                             | 4GB cacheable memory.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                             | PCI-946 Rev. 1 : 128KB internal 64-bit wide SBP non-blocking ECC Level 2 running at full CPU core speed for the.                                                                                                                                                                                                                                                                              |  |  |  |  |

|                             | P3S440BX SBC 256KB 64-bit wide Advanced Transfer Cache (on die, full speed L2 cache with ECC) for the                                                                                                                                                                                                                                                                                         |  |  |  |  |

| System Memory               | Three 168-pin latching DIMM sockets, 64/72-bit.                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                             | ECC support and parity supported with 72-bit modules.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                             | Up to 768 MB with 2, 4, 8, 16 or 32M x 64/72, 100MHz SDRAM (PC 100) non-ECC mode (single bit error correction, double bit detection via Intel 82440BX AGPset); all 768MB cacheable.                                                                                                                                                                                                           |  |  |  |  |

|                             | Uses 3.3V, single-sided or double-sided 168-pin DIMMs.                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Data Path                   | 64-bit on CPU and memory bus                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                             | 32-bit on the PCI bus                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                             | 16-bit on the ISA bus                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

PCI-946-1 and P3S440BX Technical Specifications (cont'd)

| FEATURES                       | DESCRIPTIONS                                                                                                                                                                                   |                      |               |  |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------|--|

| Bus Interfaces                 | Front Side Bus                                                                                                                                                                                 | PCI-946 :            | 66MHz         |  |

|                                |                                                                                                                                                                                                | P3S440BX:            | 100MHz        |  |

|                                | AGP Bus                                                                                                                                                                                        |                      | 66MHz         |  |

|                                | PCI Bus                                                                                                                                                                                        |                      | 33MHz         |  |

|                                | ISA Bus                                                                                                                                                                                        |                      | 8.33MHz       |  |

|                                | Quick Switches to                                                                                                                                                                              | support up to 20-sl  | ot backplane. |  |

| Interrupts                     | 11 edge se                                                                                                                                                                                     | ensitive and configu | rable         |  |

|                                | 4 PCI level sensitive, configurable to any interrupt vector for PnP compatibility.                                                                                                             |                      |               |  |

|                                | All ISA onboard interrupts are PnP compliant.                                                                                                                                                  |                      |               |  |

| DMA Channels (ISA)             | Four 8-bit, three 16-bit                                                                                                                                                                       |                      |               |  |

|                                | Supports scatter / gather, Fast Type-F DMA                                                                                                                                                     |                      |               |  |

| Flash Memory                   | 2 Mb (256KB) Boot Block for BIOS field upgrade                                                                                                                                                 |                      |               |  |

|                                | 4 KB Serial EEPROM for user configuration                                                                                                                                                      |                      |               |  |

| CompactFlash <sup>™</sup> Disk | Optional bootable CompactFlash <sup>TM</sup> module interfaces to secondary IDE channel, user upgradeable, master/slave.                                                                       |                      |               |  |

| PCI Ethernet Interface         | Intel 82559 Fast Ethernet controller (Intel EthernetExpress Pro100+ equivalent) supports 10Base-T and 100Base-Tx Ethernet interface options via an RJ-45 connector on the board's I/O bracket. |                      |               |  |

|                                | LED indicators are supported on the connector.                                                                                                                                                 |                      |               |  |

|                                | Software drivers are supported for the most popular operating systems.                                                                                                                         |                      |               |  |

PCI-946-1 and P3S440BX Technical Specifications (cont'd)

| FEATURES                      |                                                                                                                  | DESCRIPTIONS                                                                                                                                                                 |

|-------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI SCSI Interface            | S                                                                                                                | Adaptec AIC-7880 (AHA-2940AU equivalent). Supports Wide-Ultra SCSI (16-bit, 40MB/s and data pursts to the host at full PCI speeds) via the 68-pin Wide-Ultra SCSI connector. |

|                               | Fast SCSI II                                                                                                     | 8-bit, 10MB/s)                                                                                                                                                               |

|                               | Fast-20 SCSI II                                                                                                  | (8-bit, 20MB/s)                                                                                                                                                              |

|                               | Active termination is<br>A SCSISelect Config                                                                     | ables available from Kontron.<br>provided onboard (enabled by jumpers).<br>guration Utility is available.<br>supported for the most popular operating systems.               |

| Serial Ports                  | Support two RS-232 serial ports, with RS-422/RS-485 available on Serial Port 2.                                  |                                                                                                                                                                              |

|                               | 16C550 compatible v                                                                                              | with internal 16-byte FIFO buffers for more efficient                                                                                                                        |

|                               | Configurable COM1-4 with BIOS selectable IRQs and adressing.                                                     |                                                                                                                                                                              |

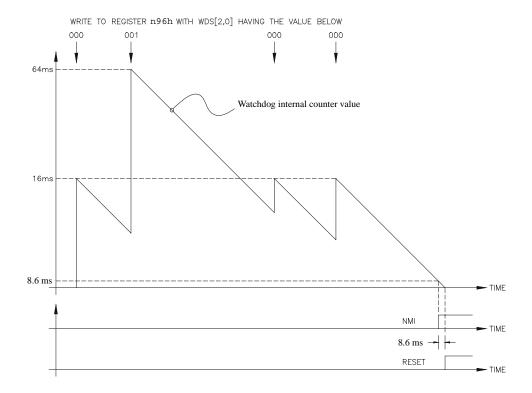

|                               | The serial ports suppose console redirection.                                                                    | port VT100 mode for remote BIOS setup and                                                                                                                                    |

| Basic Interface Devices       | Supports PS/2 mouse, AT standard keyboard, speaker, reset switch and hard disk LED.                              |                                                                                                                                                                              |

| Parallel Port                 | Supports multiple mode parallel port (Strandard, IEEE 1284, SPP, EPP, ECP); BIOS selectable IRQs and addressing. |                                                                                                                                                                              |

| Universal Serial Bus<br>(USB) | Supports two USB ports.                                                                                          |                                                                                                                                                                              |

|                               | USB voltages protec                                                                                              | eted by self-resetting fuse.                                                                                                                                                 |

|                               | Cable assembly, whi for connection to US                                                                         | ich provides two USB ports on a bracket, available B 10-pin header.                                                                                                          |

|                               | Cable/bracket assem                                                                                              | nbly to be sold as a separate accessory.                                                                                                                                     |

PCI-946-1 and P3S440BX Technical Specifications (cont'd)

| FEATURES       | DESCRIPTIONS                                                                                                                 |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------|--|

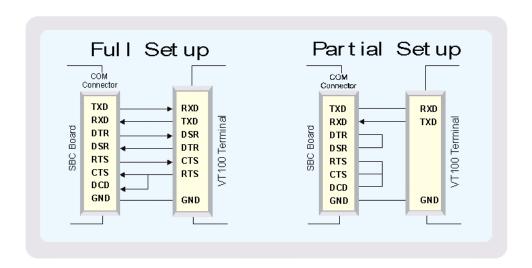

| Video Support  | High performance 64-bit Frame AGP (Accelerated Graphic Port) video.                                                          |  |

|                | 2MB SDRAM Video Memory 83MHz SDRAM memory (C&T 69000A).                                                                      |  |

|                | Supports CRT displays with resolution of up to 1024x768, 64K colors, non-interlaced or 1280x1024x256 colors, non-interlaced. |  |

|                | Compatible with CGA, EGA, Hercules, MDA, VGA, SVGA, XGA and SXGA.                                                            |  |

|                | Software drivers are available for the most popular operating systems.                                                       |  |

| Clock/Calendar | Real-time clock with 256 byte battery backup CMOS RAM                                                                        |  |

| BIOS           | Award Elite BIOS in Boot Block Flash with recovery code; save CMOS in Flash option and boot from LAN Capability.             |  |

|                | Auto configuration, extended setup.                                                                                          |  |

|                | CC00-E000 address blocking; PnP tables.                                                                                      |  |

|                | Setup console redirection to serial port (VT100 mode) with CMOS setup access.                                                |  |

|                | Software enable/disable of onboard Ethernet and SCSI.                                                                        |  |

|                | hardware enable/disable of onboard video.                                                                                    |  |

|                | Diskless, keyboardless and videoless operation extensions.                                                                   |  |

|                | System, video, LAN and SCSI BIOS shadowing.                                                                                  |  |

|                | Programmable bus and I/O speeds, and memory states.                                                                          |  |

|                | Advanced security feature for floppy and HDD.                                                                                |  |

|                | DMI & HDD S.M.A.R.T. support.                                                                                                |  |

|                | Advanced Configuration and Power Interface (ACPI 1.0),                                                                       |  |

|                | Advanced Power Management (APM 1.2),                                                                                         |  |

|                | Advanced thermal management, resume overheat alarm, auto slow down, and Green support.                                       |  |

PCI-946-1 and P3S440BX Technical Specifications (cont'd)

| FEATURES                   | DESCRIPTIONS                                                                                                                                                                                                                   |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

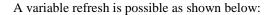

| Supervisory                | Two-stage software programmable watchdog timer drives NMI on 1 <sup>st</sup> stage, system reset on 2 <sup>nd</sup> stage.  Time out from 16ms to 4.25min.                                                                     |  |

|                            |                                                                                                                                                                                                                                |  |

|                            | CPU temperature monitor/alarm.                                                                                                                                                                                                 |  |

|                            | Board temperature sensor.                                                                                                                                                                                                      |  |

|                            | Power failure/low battery detector.                                                                                                                                                                                            |  |

|                            | Two end-user defined open-drain general purpose I/O; SMBus, I <sup>2</sup> C Bus.                                                                                                                                              |  |

| Serial ID Number<br>Device | Serial ID Tag for unique board identification.                                                                                                                                                                                 |  |

|                            | The 48-bit serial number device contains the board's unique serial number. The number can be read by software.                                                                                                                 |  |

|                            | For instructions on accessing this device, contact Kontron's Technical Support.                                                                                                                                                |  |

| 4KB Serial EEPROM          | The 4KB serial EEPROM device is non-volatile memory.                                                                                                                                                                           |  |

|                            | This storage area is completely user-defined.                                                                                                                                                                                  |  |

|                            | For instructions on accessing this device, contact Kontron's Technical Support.                                                                                                                                                |  |

| Watchdog Timer             | A two-stage software programmable watchdog timer drives a NMI on 1 <sup>st</sup> stage, and the system reset on 2 <sup>nd</sup> stage.                                                                                         |  |

| Power Fail Detection       | Monitoring either the real time clock and CMOS RAM power source (3.6V onboard or offboard battery), or an offboard battery of arbitrary voltage (a resistor must be installed to provide the appropriate voltage attenuation). |  |

| Thermal Management         | Advanced thermal management with resume and overheat alarm for CPU including an audio alarm. Auto Slow Down CPU When Over Temperature.                                                                                         |  |

# PCI-946-1 and P3S440BX Technical Specifications (cont'd)

| FEATURES                      | DESCRIPTIONS                                                                                                                                                                                                                  |  |  |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Hardware Monitoring<br>System | A system hardware circuit monitors all system voltages, ambient temperature and fan speed.                                                                                                                                    |  |  |

| Battery                       | A built-in lithium battery is provided for data retention of CMOS memory.                                                                                                                                                     |  |  |

| Operating Systems             | Supports all operating systems developed for x86 and Pentium® processors.                                                                                                                                                     |  |  |

|                               | PC and MS-DOS <sup>™</sup> , Windows® 3.X, Windows® 95/98, Windows® NT 4.0/5.0, OS/2® Warp; SCO UNIX™, QNX™. NOVELL™; UnixWare™.                                                                                              |  |  |

| Boot Block Flash BIOS         | The 256KB Boot Block Flash device contains all the board's BIOSs and is used for storing the nonvolatile configuration required for Plug and Play. The protected boot block section allows for the reprogramming of the BIOS. |  |  |

| Power Supply                  | Voltage: VCore set by CPU VID; 3.3V ±5% ; +5V ±5% ; +12V ±5%                                                                                                                                                                  |  |  |

|                               | PCI-946 Rev. 1: On-board switching regulators for 2.0V (Vcore), and 3.3 VDC (Vio).                                                                                                                                            |  |  |

|                               | Current Ratings (Celeron)                                                                                                                                                                                                     |  |  |

|                               | Frequency (MHz) 300 366 433 566                                                                                                                                                                                               |  |  |

|                               | Current (Amps) 3.26 3.60 3.82 3.18                                                                                                                                                                                            |  |  |

|                               | P3S440BX: On-board switching regulators for 1.6V (Vcore), and 3.3 VDC (Vio).                                                                                                                                                  |  |  |

|                               | Current Ratings (Pentium III)                                                                                                                                                                                                 |  |  |

|                               | Frequency (MHz) 600 700                                                                                                                                                                                                       |  |  |

|                               | Current (Amps) 2.92 4.12                                                                                                                                                                                                      |  |  |

| Mechanical                    | Board Dimensions:                                                                                                                                                                                                             |  |  |

|                               | 338 x 122 x 36mm at CPU FAN (13.32" x 4.80" 1.4 in. at CPU / Fan)                                                                                                                                                             |  |  |

|                               | Conforms to IEEE P996 PC/AT bus, PCI Rev. 2.1 & PICMG Rev. 2.0 standards                                                                                                                                                      |  |  |

PCI-946-1 and P3S440BX Technical Specifications (cont'd)

| FEATURES    | DESCRIPTIONS                                                                          |  |  |

|-------------|---------------------------------------------------------------------------------------|--|--|

| Temperature | Operating Temperature 0 to 60°C (32° to 140°F) with airflow                           |  |  |

|             | Humidity 5 to 95% @ 40°C / 104°F non-condensing                                       |  |  |

|             | Storage: Temperature -40 to +70°C / -40° to 158°F                                     |  |  |

|             | Humidity 0% to 95% R.H. @ 40°C/104°F non-condensing                                   |  |  |

| Reliability | SCSI termination, USB and mouse / keyboard voltage protected by self-resetting fuses. |  |  |

|             | Unique silicon serial number accessible via software.                                 |  |  |

|             | 2 year limited warranty.                                                              |  |  |

|             | Designed to meet or exceed:                                                           |  |  |

|             | Safety: UL 1950 ; CSA C22.2 No 950 ; EN 60950, IEC 950                                |  |  |

|             | EMI/EMC: FCC 47 CFR Part 15/CISPR22; CE Mark to EN55022/EN50082                       |  |  |

# PART 2

# 2. ONBOARD FEATURES

- 1. SYSTEM CORE

- 2. ETHERNET INTERFACES

- 3. I/O DEVICES

- 4. PARALLEL PORT

- 5. SERIAL PORTS

- 6. USB PORTS

- 7. STORAGE

- 8. VIDEO FEATURES

- 9. POWER SUPPLY INTERFACE

## 2.1. SYSTEM CORE

#### 2.1.1. Processors

The following processors can be installed on the PCI-946-1:

PPGA Celeron Processors running at 300, 366, 433, MHz and future processors as technology evolves.

The Celeron Processor and its cooling fan assembly are factory installed and the speed of the processor is preset to its nominal value (maximum internal speed).

The following processors can be installed on the P3S440BX:

FC-PGA Pentium® III Processors running from 600 to 750 MHz and future processors as technology evolves.

The Pentium® III processor and its cooling fan assembly are factory installed and the speed of the processor is preset to its nominal value (maximum internal speed).

## **BIOS Setups**

See Section 6-13: AWARD Setup Program, CPU/Board Features Setup option

The processor must be mounted to the board using the J22 socket. A fan connector referred to as J24 provides the power voltage for the CPU fan assembly.

#### NOTE

Celeron processors have fixed built-in multipliers and cannot be changed.

## **2.1.2.** Memory

The board supports up to 768MB of 64/72-bit Synchronous DRAM (SDRAM) divided-up into three DIMM sockets (J13, J16 and J18). The minimum configuration is 16MB (one SDRAM module installed in socket J18).

#### **Related Jumpers**

None

#### **BIOS Setups**

See Section 4.1.6 - AWARD Setup Program, Chipset Features Setup option

The following SDRAM modules are supported:

- 16MB (2Mx64 or 2Mx72)

- 32MB (4Mx64 or 4Mx72)

- 64MB (8Mx64 or 8Mx72)

- 128MB (16Mx64 or 16Mx72)

- 256MB (32Mx64 or 32Mx72)

## NOTE

The total size of the system memory available on the board is equal to the sum of the memory module sizes installed in the DIMM sockets.

# **2.1.3.** Battery

The battery is required to keep the BIOS settings and the real-time clock stored into the CMOS RAM. The board is shipped from factory with the battery electrically disconnected from the board. Before powering the board, the battery must be connected using the W4 CMOS backup source jumper.

#### **Related Jumpers**

W4: Internal or external CMOS backup source selection Setups are described in Section 2 – Setting Jumpers

#### **BIOS Settings**

None

The battery specifications are as follows: 3.6V Lithium battery, 0.37A/h

#### Installation

- Connect the battery to the B1 header. The positive pin of the battery is located at the bottom center.

- The onboard battery power can be replaced by an external power source by connecting a 3.6V power to the J14 External Battery connector. When using an off board battery source, W4 jumper must be set to position 2-3.

# **₩** Warning

Danger of explosion if battery is incorrectly replaced

Replace only with the same or equivalent type recommended by the manufacturer. Dispose of used batteries according to the manufacturer's instructions.

## 2.2. ETHERNET

The Ethernet interface is available through the J20 RJ-45 connector located on the edge bracket.

The 10Mbps or 100Mbps (10Base-T, 100Base-Tx) network speed is automatically detected and selected.

#### **Related Jumpers**

None

#### **BIOS Settings**

The onboard Ethernet feature is enabled by default.

To change settings, see Section 4.1.10: AWARD CMOS Setup Utility, Integrated Peripherals Setup option

The 10Base-T interface uses UTP (Unshielded Twisted Pair) cables, category 5, 4 or 3 (5 is better) while the 100Base-TX interface requires category 5 UTP cables.

#### NOTE

To boot the board from LAN, the *Boot from LAN First* option must be *enabled* using the AWARD CMOS Setup Utility, BIOS Features Setup (see Section 4.2.2).

The Ethernet controller has specific drivers for various operating systems and software. To install these drivers, refer to the Utility Disk containing the Ethernet drivers for your operating system (see Section 8 - Installing Drivers).

# 2.3. I/O DEVICES

## 2.3.1. I/O Connections

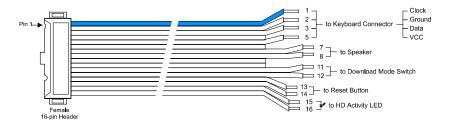

Standard AT keyboard, speaker port, reset button and hard disk LED signals are issued on the J11 multifunction header.

A 22" multifunction flat cable (Kontron part number 150-018-01) is provided with the board for connecting the respective devices.

# **Related Jumpers**

None

## **BIOS Settings**

None

Signals on the flat cable are issued as follows:

# 2.3.2. Keyboard

The simplest way to connect a PS/2 keyboard to the board is to use the J23 standard PS/2 keyboard connector (mini-DIN) on the edge bracket. No additional cabling is required. The onboard keyboard controller is 8042 software compatible.

#### **Related Jumpers**

None

#### **BIOS Settings**

To setup keyboard typematic features, refer to Section 4.1.5: AWARD CMOS Setup Utility, BIOS Features Setup option

#### 2.3.3. PS/2 Mouse

The easiest way to connect a PS/2 mouse to the board is to use the J21 standard PS/2 mouse connector (mini-DIN) on the edge bracket. No additional cabling is required.

#### **Related Jumpers**

None

#### **BIOS Settings**

To enable automatically the PS/2 mouse when installed, refer to Section 4.1.10 AWARD CMOS Setup Utility, Integrated Peripherals Setup option

A PS/2 mouse header (J15) is also provided on board. To connect a mouse through this header, a shielded PS/2 mouse adapter cable is required. It is available from Kontron as 18" shielded mouse cable, part number 150-337-00.

#### **CAUTION**

While it is also possible to connect a mouse through the J15, PS/2 mouse header, do not connect two PS/2 mice simultaneously to the board. This can damage the mouse interface. The same also applies to possible connection of a keyboard through the multifunction header (J11), do not connect two keyboards simultaneously to the board. This can damage the keyboard interface.

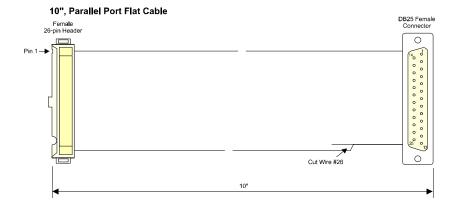

# 2.4. PARALLEL PORT

The Parallel Port is available through the J12 26-pin connector. It is bi-directional and supports the Standard, EPP and ECP operating modes.

#### **Related Jumpers**

None

#### **BIOS Settings**

To setup the Parallel Port, refer to Section 4.1.10: AWARD CMOS Setup Utility, Integrated Peripherals option

The usual way to use the parallel port is to issue signals from the J12 26-pin connector to a standard 25-pin D-Sub connector using an adapter cable. Such a cable is available from Kontron (Part Number: 150-172). One cable is supplied with your board.

## 2.5. SERIAL PORTS

Two full function serial ports are provided on the board for asynchronous serial communications. They are 16C550 high-speed UART compatible and support 16-byte FIFO buffers for transfer rates from 50bps to 115Kbaud.

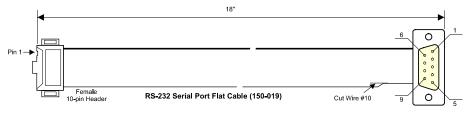

#### 2.5.1. Serial Port 1

The Serial Port 1 is available through the J7, 10-pin connector and supports the RS-232 operation mode. It is buffered directly for RS-232 operation. Signals include the complete signal set for handshaking, modem control, interrupt generation, and data transfer. When assigned as COM1, the port is 100% compatible with the IBM-AT serial port in RS-232 mode

#### **Related Jumpers**

None

#### **BIOS Settings**

To setup the Serial Port 1, refer to Section 4.1.10 – AWARD CMOS Setup Utility, Integrated Peripherals Setup option

The usual way to use to the serial port is to issue its signals through a 10-pin header/9-pin D-Sub adapter cable. An 18 inches 10-pin header/9-pin D-Sub adapter cable is available from Kontron: Part number 150-019. Two cables are provided with your board.

While adapter cables are provided from various sources, the pinout is often different. The direct crimp design offered by Kontron allows the simplest cable assembly. All cables are available from Kontron by contacting the Sales Department.

#### 2.5.2. Serial Port 2

The Serial Port 2 is available through the J8 10-pin connector, and supports both RS-232, RS-422 and RS-485 operation modes.

#### **Related Jumpers**

W2 and W3: to connect/disconnect Serial Port 2 termination resistors Setups are described in Section 3.2 – Setting Jumpers

#### **BIOS Settings**

To setup the Serial Port 2, refer to Section 4.1.10: AWARD CMOS Setup Utility, Integrated Peripherals Setup option

The usual way to use the serial port is to issue signals through a 10-pin header/9-pin D-Sub adapter cable (see description provided for the Serial Port 1).

#### 2.5.2.1. RS-232 Mode

By default, the Serial Port 2 is configured for RS-232 operation mode. To change the operating mode, refer to Section 4.1.10: AWARD CMOS Setup Utility, Integrated Peripherals Setup option.

#### 2.5.2.2. RS-422/RS-485 Modes

Use the AWARD CMOS Setup Utility, Integrated Peripherals Setup option, to select the operation mode within RS-232, RS-422 or RS-485.

In RS-422 and RS-485 modes, transmitting and receiving use differential signals in either full-duplex (RS-422) or party line (RS-485) communication.

Communicating with differential signals requires one pair of wires for RS-485 and two pairs for RS-422 (one for transmission and one for reception).

For a better noise rejection, the use of twisted pair cable is highly recommended. This will enable faster serial transmissions over greater distances than with the common RS-232 cables.

If the board is installed at one end of the network and the Serial Port 2 is configured for communicating in RS-422 or RS-485 mode, use the W2 and W3 jumpers to connect the RS-485/RS-422 termination resistors (120 ohms) while the board is terminating the network.

#### 2.5.2.3. RS-422 - Full Duplex Operation

The RS-422 protocol uses both RX and TX lines during a communication session. Upon power-up or reset, the Serial Port 2 interface circuits are automatically configured for full duplex operation. Pins 3 and 4 of J8 act as the receiver lines and pins 5 and 6 act as the transmitter lines.

In RS-422 mode, the software should not use the handshake signals (e.g., DSR, DTR), since they are not connected. However, software handshaking can be used (e.g., XON-XOFF).

#### 2.5.2.4. RS-485 - Party Line Operation

The RS-485 offers to multiple station the ability to transmit and receive over the same pair of wires (RX outputs: pins 3 and 4 of J8), and share the same communication line with multiple stations.

The RS-485 protocol offers advantages such as increased speed over long distances, improved reliability over similar RS-232 setups, the ability to share transmission line, and simpler cabling requirements than the RS-422 protocol.

In this configuration, only one system takes control of the communication at a time.

Upon power-up or reset, the transceiver is by default in "receiver mode" to avoid line perturbation.

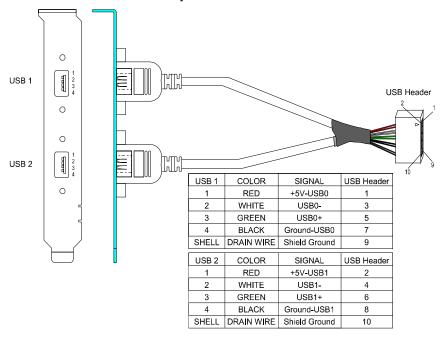

## 2.6. USB PORTS

The board provides a dual-USB interface through the J10 10-pin header. To connect standard USB devices, a USB cable/bracket assembly is required. It is available from Kontron: part number 150-316-00. One is provided with your board.

#### **Related Jumpers**

None

#### **BIOS Settings**

If required USB keyboard support for DOS and BIOS can be activated at the BIOS level.

Refer to Section 4.1.10: AWARD CMOS Setup Utility, Integrated Peripherals Setup option

The USB cable/bracket assembly is described as follows:

## 2.7. STORAGE DEVICES

## 2.7.1. Floppy Disk Drives

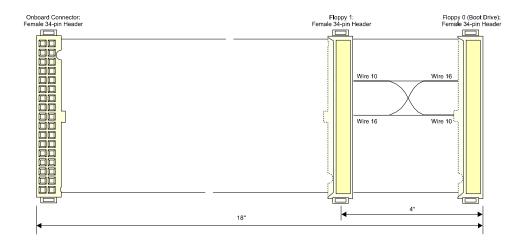

Two floppy disk drive units can be connected to the board through the J6 Floppy Disk connector using a standard IBM 34-pin flat ribbon cable. An 18" floppy disk cable is available from Kontron: part number 150-051. One cable is provided with your board.

#### **Related Jumpers**

None

#### **BIOS Settings**

To define the Floppy Disk installation, refer to Section 4.1.4: AWARD CMOS Setup Utility, Standard CMOS Setup option

To enable/disable the system to boot from the floppy disk, refer to Section 4.1.5: AWARD CMOS Setup Utility, BIOS Features Setup option

The floppy disk cable is illustrated below:

#### 2.7.2. IDE Devices

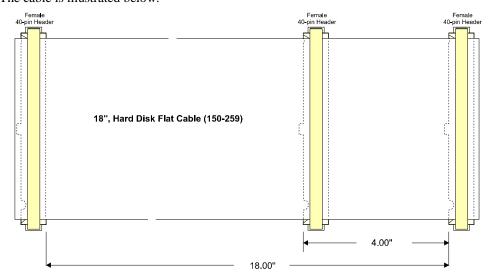

Two IDE interfaces are provided to support up to four IDE devices, such as hard disks, CD-ROM, and ZIP drives. The interfaces are referred to as Primary (J5 connector) and Secondary (J9 connector). Connections are supported through 40-pin dual row headers.

#### **Related Jumpers**

None

#### **BIOS Settings**

To detect a hard disk drive type, refer to Section 4.1.4: AWARD CMOS Setup Utility, Standard CMOS Setup option

To enable/disable the system to boot from the floppy disk, refer to Section 4.1.5: AWARD CMOS Setup Utility, BIOS Feature Setup option

To connect one IDE interface, use a 40-pin flat ribbon cable. An 18 inches length cable is available from Kontron: part number 150-259. One is provided with your board.

The cable is illustrated below:

#### 2.7.3. SCSI Devices

The board supports PCI Ultra Fast/Wide SCSI 3 with operation up to 40 MB/s and data bursts to the host at full PCI speeds, Fast and Ultra SCSI 2 Adaptec AIC 7880.

The PCI Wide-Ultra SCSI 3 port is available at J4. A wide SCSI cable, 68-pin male to 68-pin male is supplied with the PCI-946 (part number 150-371-00).

You can access the PCI Fast and Ultra SCSI 2 through J3 using a 50 pin SCSI cable. This cable is supplied with the PCI-946 (part number 150-183).

#### **Related Jumpers**

W6 to determine the SCSI mode (8-bit or 16-bit)

W7 to set the board as terminated or not

#### **BIOS Settings**

Setup is described in Section 4.1.10 – AWARD CMOS Setup Utility, Integrated Peripherals option

The onboard SCSI interface is enabled by default.

To change setups, see Section 4.1.10 AWARD CMOS Setup Utility, Integrated Peripherals option

## 2.7.3.1. SCSI activity monitoring

The SCSI activity status signal is available through J2 (2-pin lock header). Connect the LED as follows: anode (red lead) on pin 1 and cathode (black lead) on pin 2. No external current limiting resistor is required since it is already present on the board (330 ohm resistor).

50-pin Fast SCSI and Fast-20 SCSI devices are also supported using a 68-pin to 50-pin adapter cable.

#### NOTE

Ensure that the onboard SCSI controller is enabled in the AWARD CMOS Setup Utility, Integrated Peripherals.

The Adaptec SCSISelect configuration software is provided with the board to configure or view the default SCSI settings of the host adapter (See Section 7 Configuring SCSI). It replaces the <Ctrl-A> feature on standard Adaptec controllers

The EZ-SCSI software is provided with the board to install the appropriate driver for your specific operating system.

Ensure that the onboard SCSI controller is enabled in the AWARD CMOS Setup Utility, Integrated Peripherals. To boot from the SCSI device, please refer to the AWARD CMOS Setup Utility, BIOS Features option.

## NOTE

The Adaptec SCSISelect configuration software is provided with the board to configure or view the default SCSI settings of the host adapter (See Section 7 *Configuring SCSI*). It replaces the <Ctrl-A> feature on standard Adaptec controllers.

The EZ-SCSI software is provided with the board to install the appropriate driver according to your specific operating system.

## 2.7.4. Compact FlashDisk

The PCI-946 board also supports standard CompactFlash disks through a CompactFlash module. It is supported on the board as a standard IDE drive and connects to the Primary EIDE interface. The CompactFlash drive can be set as a Master or Slave device and combined with any standard hard disk drive.

#### **Related Jumpers**

W10 to set CompactFlash Disk as Master or Slave Setup is described in Section 3.2 – Setting Jumpers

#### **BIOS Settings**

Since a CompactFlash Disk is the same as an IDE Hard Disk, refer to section 4.1.5 and 4.1.10 (AWARD CMOS Setup Utility) to set options for this drive: master or slave, boot disk, etc.

CompactFlash is installed on the C-FLASH connector. The board supports an IDE compatible flash disk by using a CompactFlash module (Kontron part number T069). CompactFlash (C-Flash) disks are the world's smallest resident industry-standard ATA/IDE subsystem for application, data, image, and audio storage. They have the same functionality and capabilities as intelligent disk drives, but with the advantages of being very compact, rugged (typical M.T.B.F. is 1,000,000 hours) and low power.

The CompactFlash disk connects directly on the Primary EIDE interface. It must be declared the same way as a standard hard disk using the AWARD CMOS Setup Utility (IDE HDD Auto Detection function).

To setup the CompactFlash disk for Master or Slave configuration, use the W10 jumper located on the SBC.

#### NOTE

Since data is accessed as an IDE drive, no specific flash disk driver is required for most operating systems.

## 2.8. VIDEO FEATURES

The CRT display connects directly to the J18 standard VGA 15-pin D-Sub connector located on the edge bracket.

#### **Related Jumpers**

W1 to enable or disable the onboard video controller W9 to assign the PCI INTA to the onboard video controller Setup is described in Section 3.2 – Setting Jumpers

#### **BIOS Settings**

Refer to Section 4.1.6: AWARD CMOS Setup Utility, Chipset Features Setup for RAM cache and video BIOS shadow capabilities

When the PCI INTA is assigned to the video controller (W9 shorted), the video controller will issue an interrupt request signal when the end of an active field (VSYNC pulse to the CRT monitor) is reached. By default the interrupt is disabled.

## 2.9. POWER SUPPLY

When used as a stand-alone system, the PCI-946 must be powered through the J1 Power connector. When installed on a backplane, the power is drawn to the board through the power lines of the ISA and PCI edge bracket.

## **Related Jumpers**

None

## **BIOS Settings**

See Power Management options described in Section 4.1.7: AWARD CMOS Setup Utility, Power Management Setup option

The power requirements are specified as follows:

| Part                     | Voltage<br>Core (V) | Frequency<br>INT/BUS<br>(MHz) | Vcc<br>Power<br>MAX<br>(Watts) | Vcc<br>Power<br>TYP<br>(Watts) | Vcc<br>Suspended<br>Mode<br>(Watts) | +12V<br>(Watts) | Ambient<br>Maximum<br>Temp. °C |

|--------------------------|---------------------|-------------------------------|--------------------------------|--------------------------------|-------------------------------------|-----------------|--------------------------------|

| Celeron 300A MHz         | 2.0                 | 300/66                        | 21.35                          | 16.3                           | 7.4                                 | 2.1             | 65                             |

| Celeron 366 MHz          | 2.0                 | 366/66                        | 24.2                           | 18.0                           | 7.4                                 | 2.1             | 65                             |

| Celeron 433 MHz          | 2.0                 | 433/66                        | 26.2                           | 19.1                           | 7.5                                 | 2.1             | 65                             |

| Celeron 566 MHz          | 1.5                 | 566/66                        | 19.0                           | 15.9                           | 7.9                                 | 2.1             | 60                             |

| Pentium® III 600E<br>MHz | 1.65                | 600/100                       | 23.4                           | 18.6                           | 8.3                                 | 2.1             | 60                             |

| Pentium® III 700<br>MHz  | 1.65                | 700/100                       | 26.9                           | 20.6                           | 8.5                                 | 2.1             | TBD                            |

# **3 INSTALLING THE BOARD**

- 1. CONNECTOR AND JUMPER LOCATIONS

- 2. SETTING JUMPERS

- 3. SUPERVISORY REGISTERS

- 4. ONBOARD INTERCONNECTIVITY

- 5. CUSTOMIZING THE BOARD

- 6. INSTALLING DRIVERS

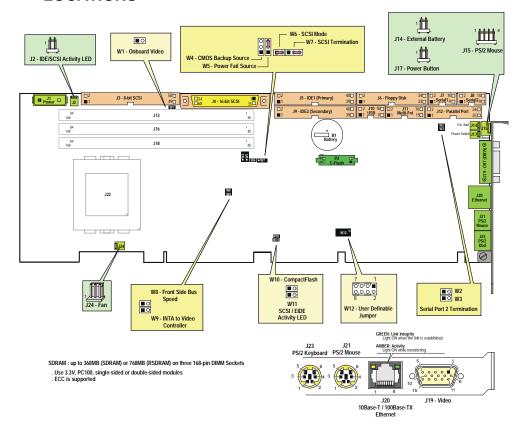

# 3.1. PCI-946 & P3S440BX CONNECTOR AND JUMPER LOCATIONS

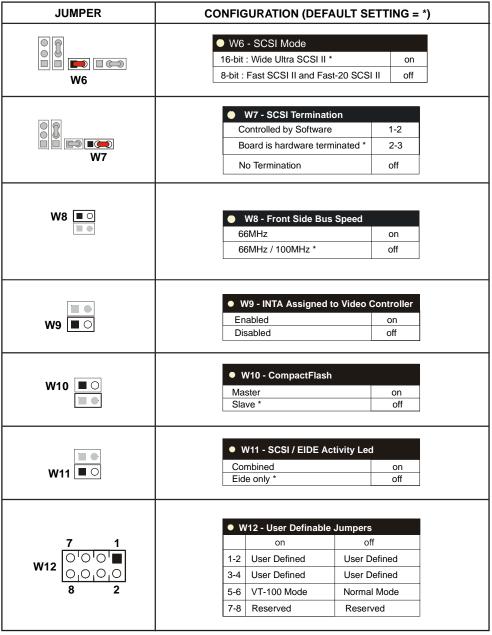

# 3.2. SETTING JUMPERS

| JUMPER           | CONFIGURATION (Defa                                                                                                            | ult Settin                        | gs = ¹            |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------|--|

|                  | A WA Only and Vista                                                                                                            |                                   |                   |  |

| W1 ■○            | W1- Onboard Video  Enabled *                                                                                                   |                                   | off               |  |

| VVI 💻 🔾          | Disabled                                                                                                                       |                                   | on                |  |

|                  |                                                                                                                                |                                   |                   |  |

|                  | ● W2, W3 - Serial Port                                                                                                         |                                   |                   |  |

| W2 <b>■</b> ○    | Set in RS-485 Mode only                                                                                                        | W2                                | W3                |  |

| W3 <b>■</b> ○    | Termination Enabled                                                                                                            | on                                | on                |  |

|                  | Termination Disabled *                                                                                                         | off                               | off               |  |

| W4               | Onboard Battery         1 - 2           External Power (3.6V only)         2 - 3           No Power (clear CMOS) *         off |                                   |                   |  |

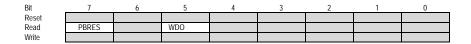

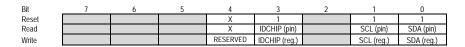

|                  | There is a danger of explincorrectly replaced. Repor equivalent type. Dispoaccording to the manufacture.                       | lace only with<br>se of used batt | thesame<br>teries |  |