# INTEGRIDAD DE SEÑAL

Fundamentos y Metodologías: tiempo y frecuencia

**Héctor Carreño**

Application Engineer

[hector\\_carreno@agilent.com](mailto:hector_carreno@agilent.com)

Need help?

[contactcenter\\_spain@agilent.com](mailto:contactcenter_spain@agilent.com)

91 631 3300

# AGENDA

Unlocking Measurement Insights for 75 Years

- Introduction / Signal Integrity Definition

- Evolution of Test Parameters

- Traditional TDR/TDT instrument

- Vector Network Analyzer Basis

- Single Ended / Differential Topologies

- Physical Layer Test System (PLTS Software)

Agilent Technologies

# AGENDA

Unlocking Measurement Insights for 75 Years

- **Introduction / Signal Integrity Definition**

- Evolution of Test Parameters

- Traditional TDR/TDT instrument

- Vector Network Analyzer Basis

- Single Ended / Differential Topologies

- Physical Layer Test System (PLTS Software)

Agilent Technologies

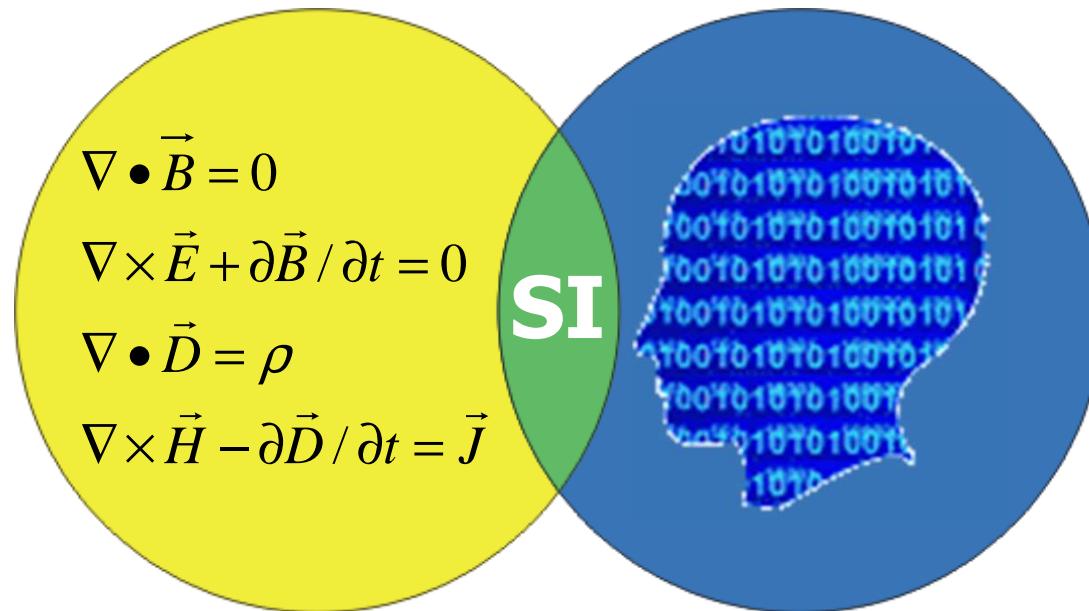

# What is Signal Integrity ?

Unlocking Measurement Insights for 75 Years

- from Marketing's Viewpoint

Mr. Maxwell meet Mr. Boole and Mr. Moore !

Agilent Technologies

# What is Signal Integrity ?

Unlocking Measurement Insights for 75 Years

- from Engineer's Viewpoint

**Signal Integrity =**

Where the electrical properties of the interconnects can cause significant distortions in digital signals.

Agilent Technologies

# What is Signal Integrity ?

Unlocking Measurement Insights for 75 Years

- from [http://en.wikipedia.org/wiki/Signal\\_integrity](http://en.wikipedia.org/wiki/Signal_integrity)

**Signal integrity** or **SI** is a measure of the **quality of an electrical signal**. In digital electronics, a stream of binary values is represented by a voltage (or current) waveform.

Over short distances and at low bit rates, a simple conductor can transmit this with sufficient fidelity. However, at **high bit rates** and over **longer distances**, various effects can degrade the electrical signal to the point where errors occur, and the system or device fails.

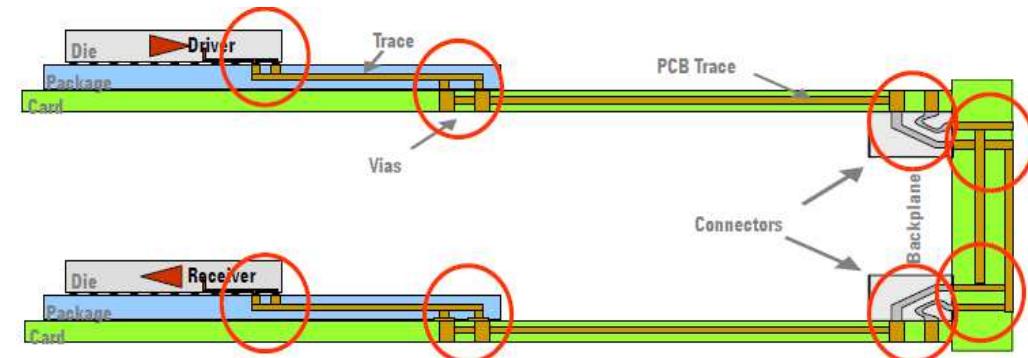

Signal integrity engineering is the task of analyzing and mitigating these impairments. Signal integrity engineering is at all levels of electronics packaging, from internal connections of an IC through the package, the printed circuit board (PCB), the backplane, and inter-system connections.

Some of the main issues of concern for signal integrity are *ringing, crosstalk, ground bounce, distortion, signal loss, and power supply noise*.

Agilent Technologies

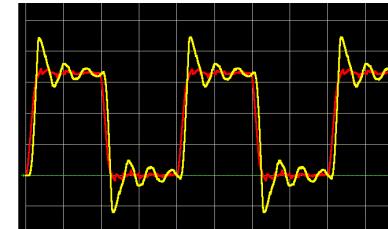

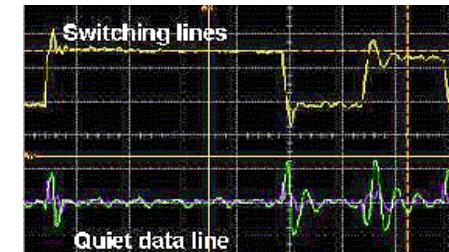

# 4 SI problems and their cause

Unlocking Measurement Insights for 75 Years

**1. Poor signal quality of one net:** reflections and distortions from impedance discontinuities in the signal or return path. Manufacturing tolerances for PCB and packages. Line width changes, Vias, Serpentine, Connectors, Cables...

**2. Crosstalk between multiple nets:** electromagnetic coupling between signal lines. Trace-to-trace crosstalk, Via-to-Via coupling, Digital-to-RF coupling.

**3. Power/Ground Noise:** voltage drops across impedance in the power/ground network

**4. Jitter and EMI** from causes listed above and variety of other sources

Agilent Technologies

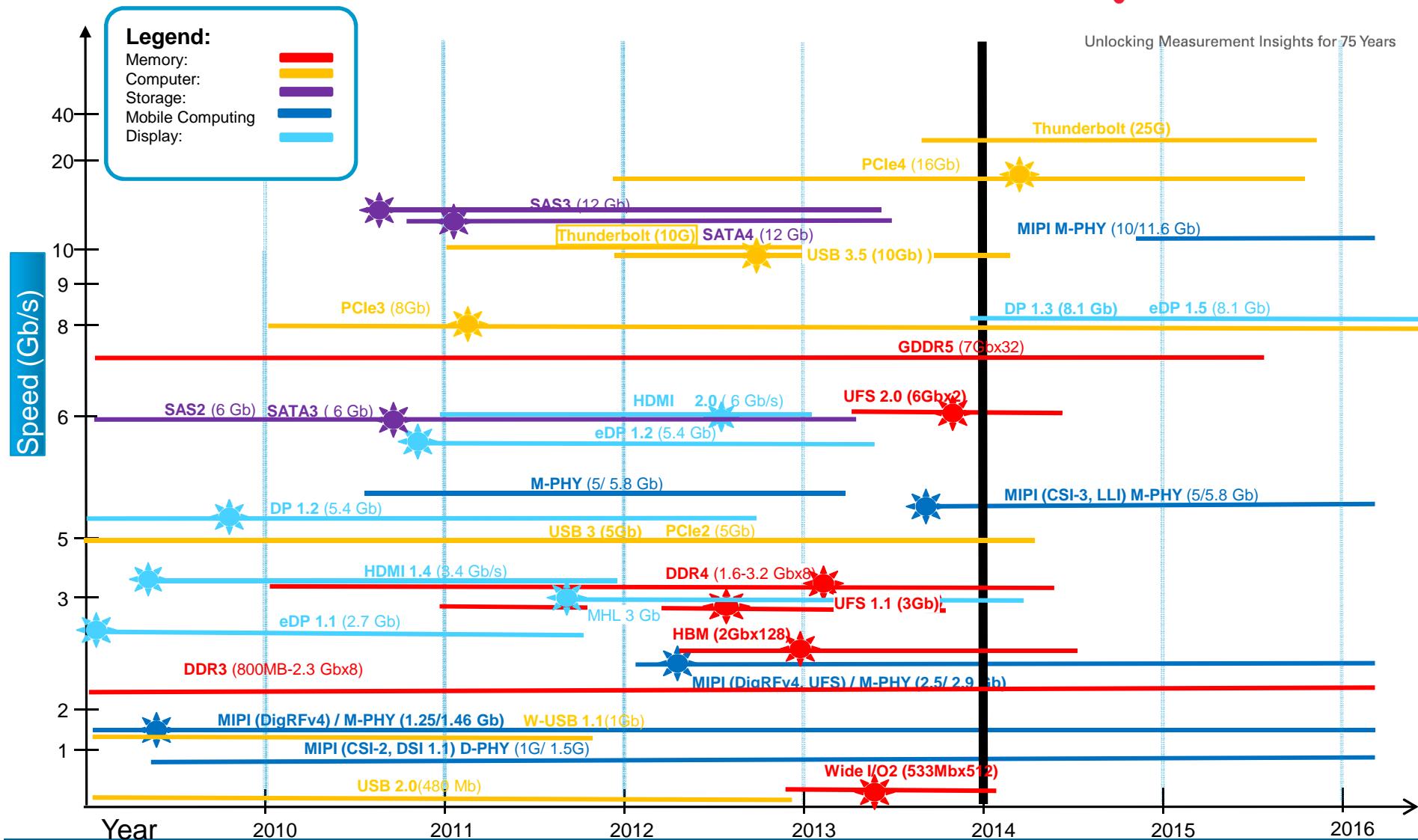

# Today High Speed I/O Standards

Unlocking Measurement Insights for 75 Years

## Physical Layer Test of High-Speed Devices

### Digital Displays

Video

### Memory

Consumer

Computation

### Computing I/O

Chip-to-Chip

Backplane

### Enterprise

Storage

LAN

### Communications

Wireline

Wireless

### Aerospace/ Defense

Sat/Comm

Key Multi-Gigabit

Technologies

SPEED

DisplayPort

HD

HDMI

DVI

FBD

DDR

CSI

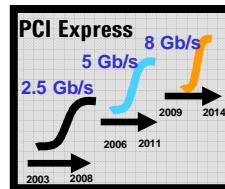

PCI Express

Rapid IO

HyperTransport

Fibre Channel

SATA

CWUSB

USB

10G Ethernet

CEI

Ethernet

XFP

ATCA

PON

DigRF

OC-768

Sat.Comm

Agilent Technologies

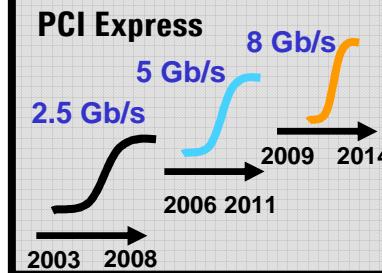

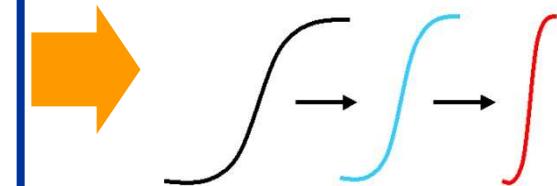

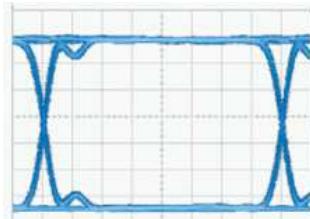

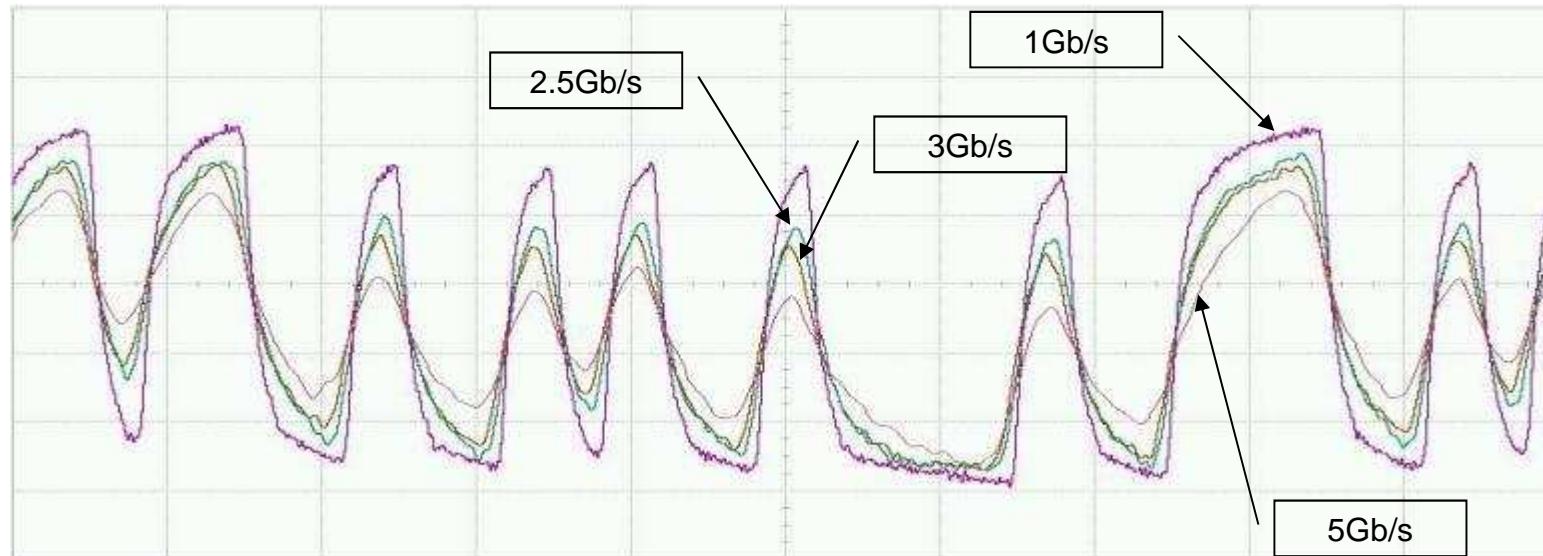

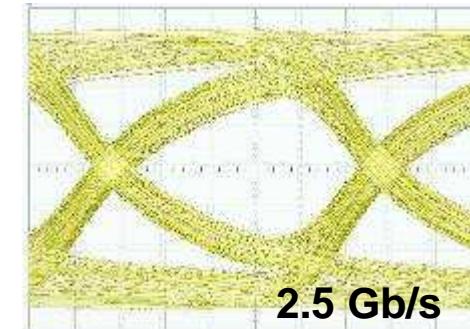

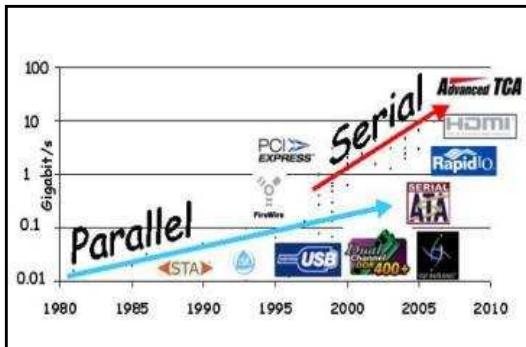

# Data Rates continuously increasing

Unlocking Measurement Insights for 75 Years

# SI is becoming more important

Unlocking Measurement Insights for 75 Years

Risetimes become faster

Frequency Domain data is ALSO required

Agilent Technologies

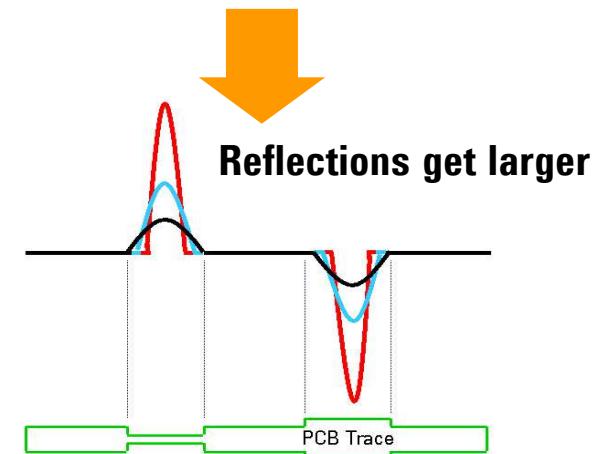

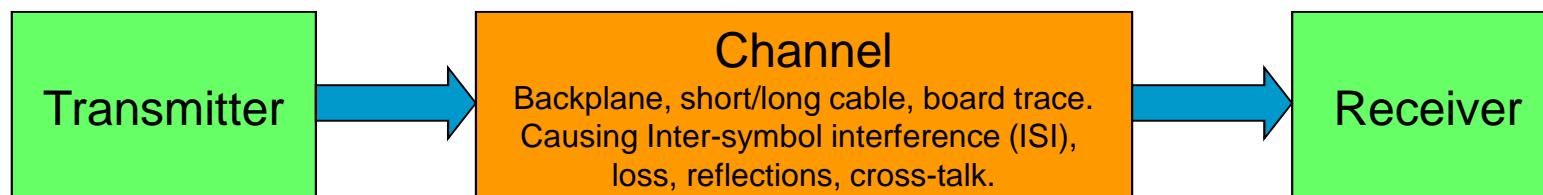

# What about using existing channels ?

Unlocking Measurement Insights for 75 Years

Agilent Technologies

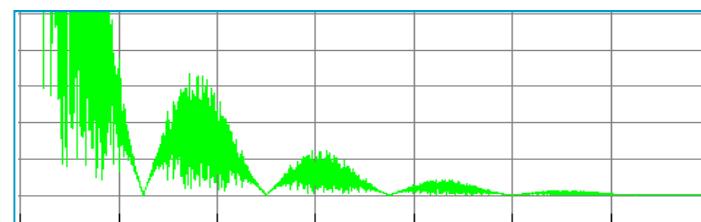

# Example: FR4 is showing its limitations

**FR4 is common, low cost and easy to manufacture BUT it has problems:**

- Reflections at high speeds

- Dispersion varies with frequency

- High Insertion Loss

- ISI induced Jitter

- Effects vary with temperature and humidity

What Works Today

Gets Worse The Next Time

No longer usable

Unlocking Measurement Insights for 75 Years

# Signal Integrity Challenge

Unlocking Measurement Insights for 75 Years

|                |                       |

|----------------|-----------------------|

| <b>USB 3.0</b> | <b>4.8 Gb/s</b>       |

| <b>HDMI</b>    | <b>5 Gb/s</b>         |

| <b>DVI</b>     | <b>8 Gb/s</b>         |

| <b>DP</b>      | <b>8.6 Gb/s</b>       |

| <b>PCIe</b>    | <b>5 Gb/s</b>         |

| <b>SATA</b>    | <b>3 Gb/s</b>         |

| <b>DDR3</b>    | <b>0.8-2.133 Gb/s</b> |

Agilent Technologies

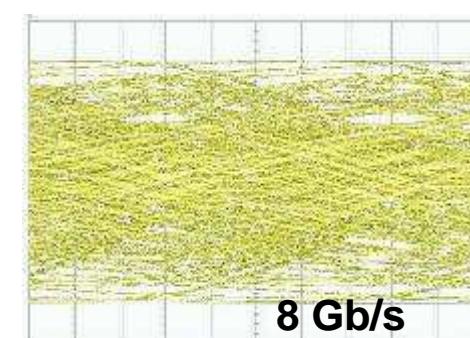

# Signal Integrity problems everywhere !

Unlocking Measurement Insights for 75 Years

Backplanes

Connectors

PC Boards

IC Packages

Cables

Agilent Technologies

# AGENDA

Unlocking Measurement Insights for 75 Years

- Introduction / Signal Integrity Definition

- **Evolution of Test Parameters**

- Traditional TDR/TDT instrument

- Vector Network Analyzer Basis

- Single Ended / Differential Topologies

- Physical Layer Test System (PLTS Software)

Agilent Technologies

# Trends in Compliance Test

Unlocking Measurement Insights for 75 Years

With the increase in bit rates, standards continue to evolve and new measurements are often the result. There is a growing need in the industry for more thorough evaluation of components, as well as evaluation under actual operating conditions

| High-speed serial standards |                    | Compliance Test Parameters                                                                                                                                                                                           |

|-----------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1990s                       | Gen 1 (~100s Mbps) | <ul style="list-style-type: none"><li>time domain (impedance, delay, skew, ...)</li></ul>                                                                                                                            |

| 2000~                       | Gen 2 (1~3 Gbps)   | <ul style="list-style-type: none"><li>time domain (impedance, delay, skew)</li><li>frequency domain (insertion loss, return loss, ...)</li></ul>                                                                     |

| 2007~                       | Gen 3 (~3 Gbps)    | <ul style="list-style-type: none"><li>time domain (impedance, delay, skew)</li><li>frequency domain (insertion loss, return loss, crosstalk, mode conversion, ...)</li></ul>                                         |

| 2010~                       | Next Gen (~6 Gbps) | <ul style="list-style-type: none"><li>time domain (impedance, impedance in active state, delay, skew, eye diagram)</li><li>frequency domain (insertion loss, return loss, crosstalk, mode conversion, ...)</li></ul> |

Agilent Technologies

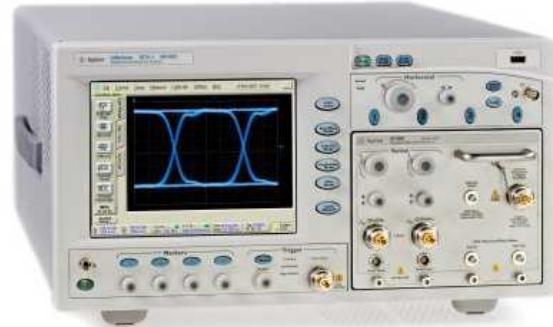

# Traditional Test

Unlocking Measurement Insights for 75 Years

## Time Domain

(impedance, delay, skew, eye diagram) (return/insertion losses, xtalk, mode conv.)

Oscilloscopes / TDRs

## Frequency Domain

(return/insertion losses, xtalk, mode conv.)

Vector Network Analyzers

Agilent Technologies

# AGENDA

Unlocking Measurement Insights for 75 Years

- Introduction / Signal Integrity Definition

- Evolution of Test Parameters

- **Traditional TDR/TDT instrument**

- Vector Network Analyzer Basis

- Single Ended / Differential Topologies

- Physical Layer Test System (PLTS Software)

Agilent Technologies

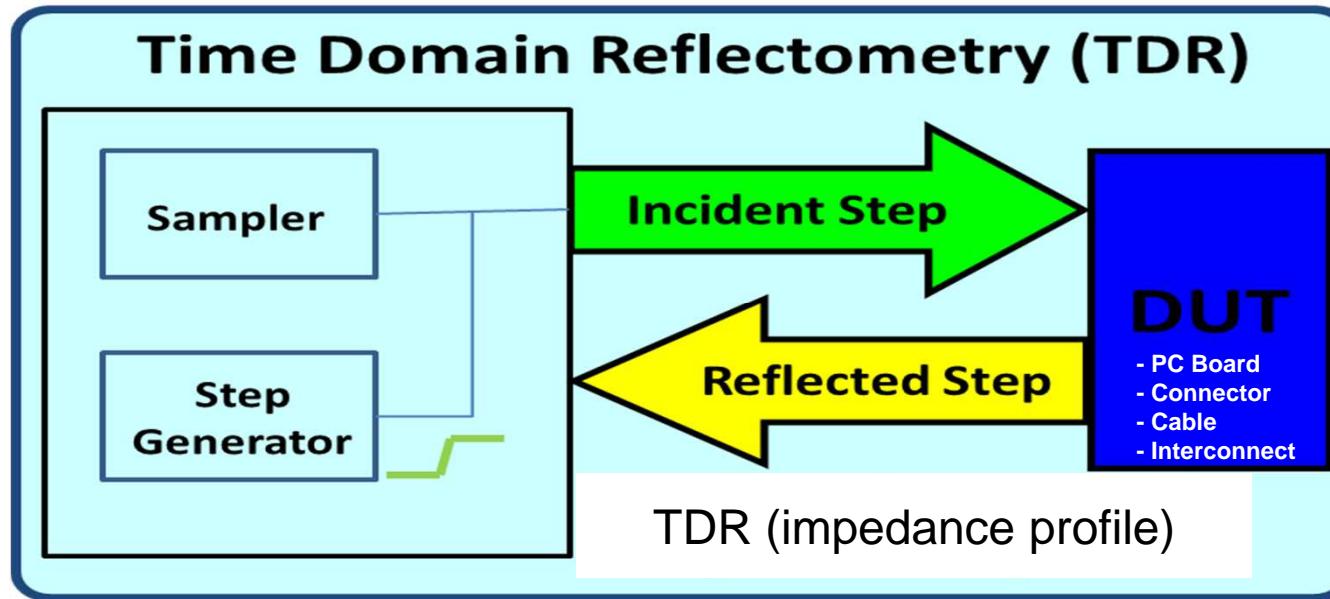

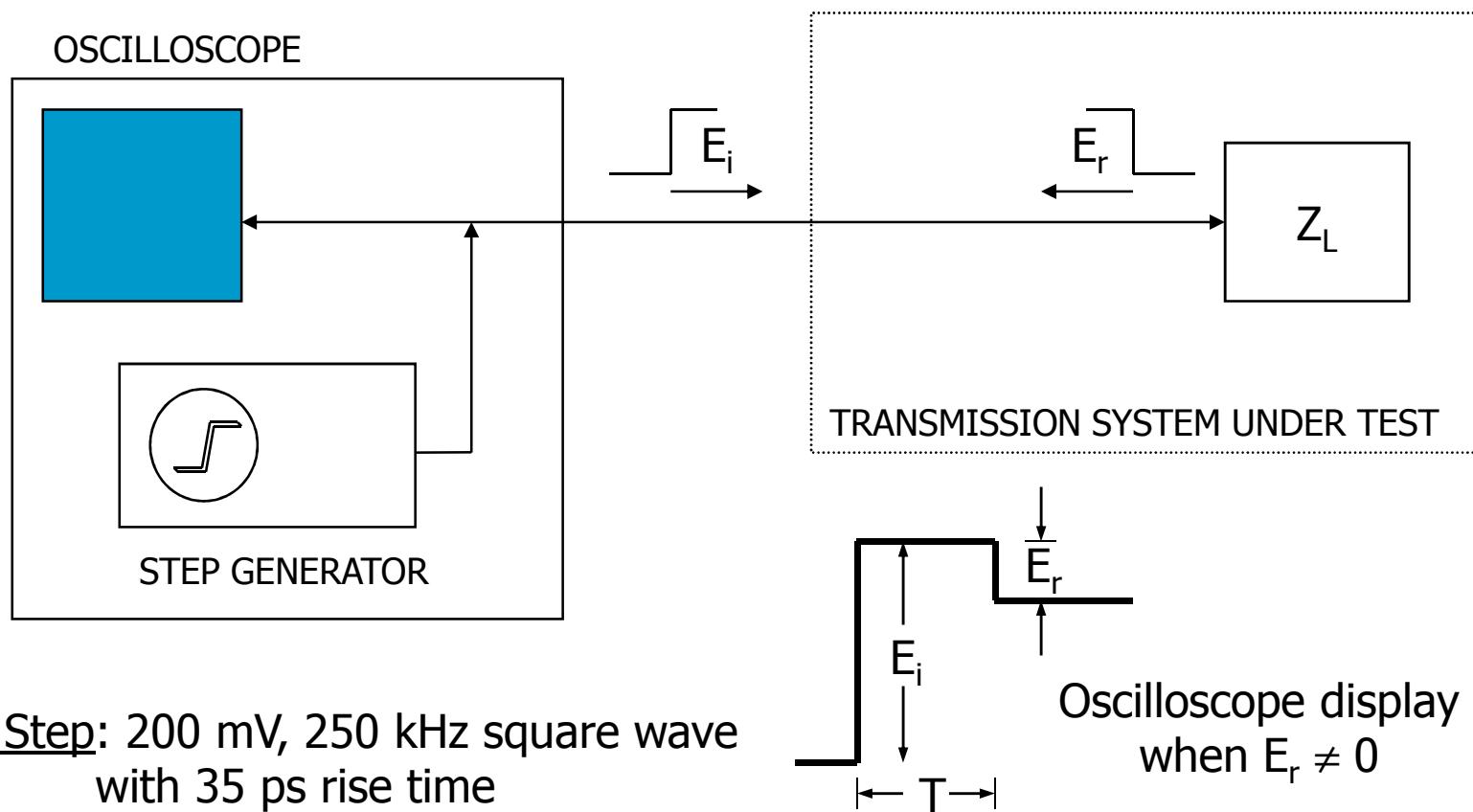

# Time Domain Reflectometry (TDR)

Unlocking Measurement Insights for 75 Years

## Time Domain Reflectometry (TDR)

- Impedance measurements

- Locate the position and nature of each discontinuity

- Propagation/Time delay

- Excess Reactance (Capacitance or Inductance)

- Effective dielectric constant

Agilent Technologies

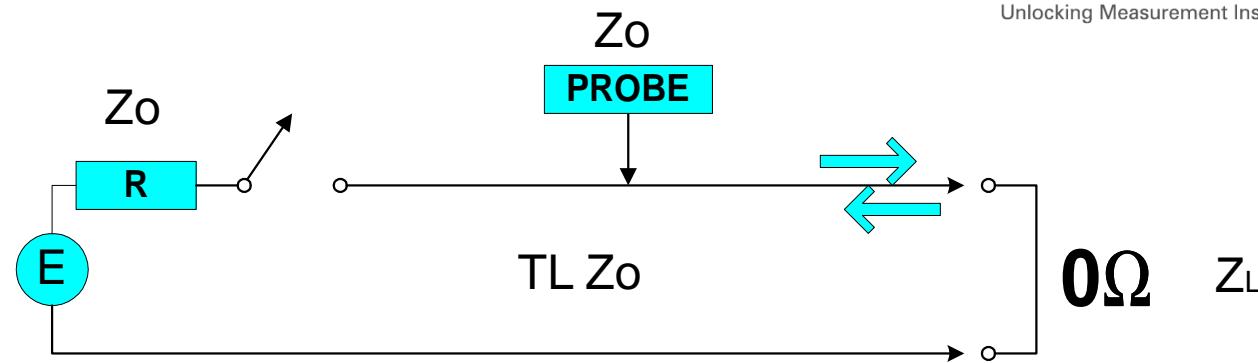

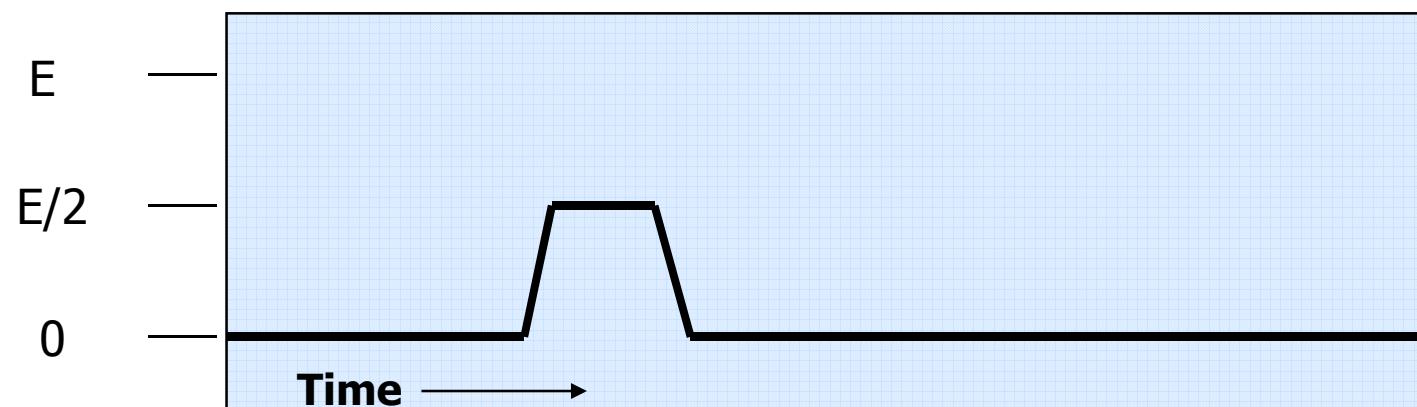

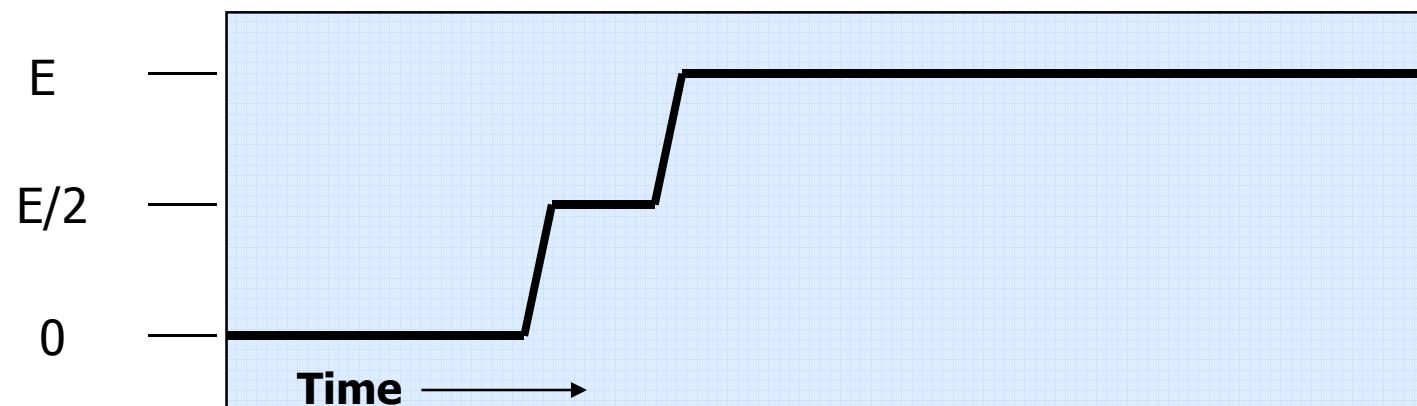

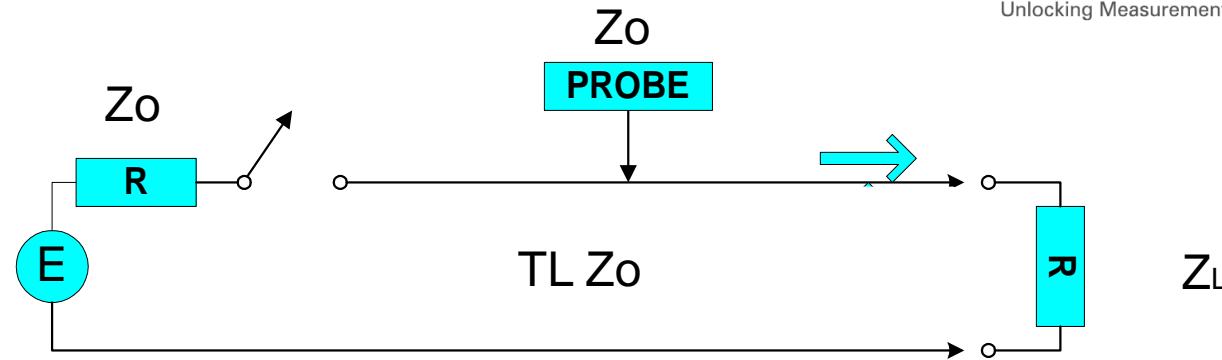

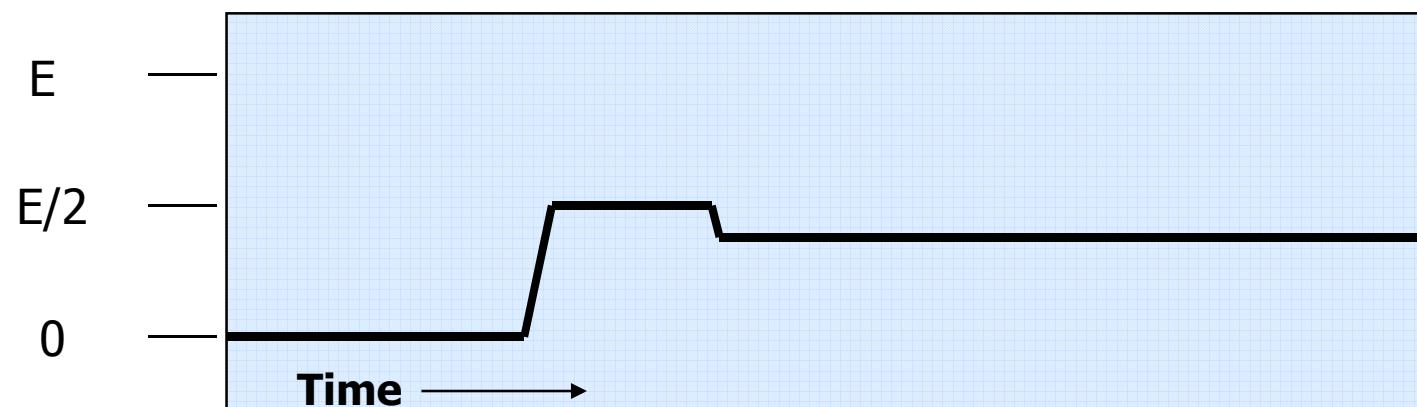

# TDR - Short Termination

Unlocking Measurement Insights for 75 Years

What do you expect to see at the probe before,

during, and after you close the switch?

Agilent Technologies

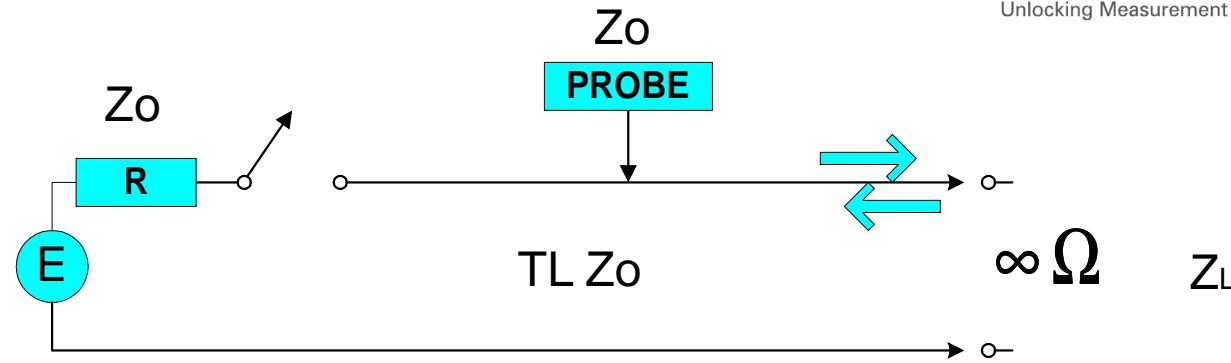

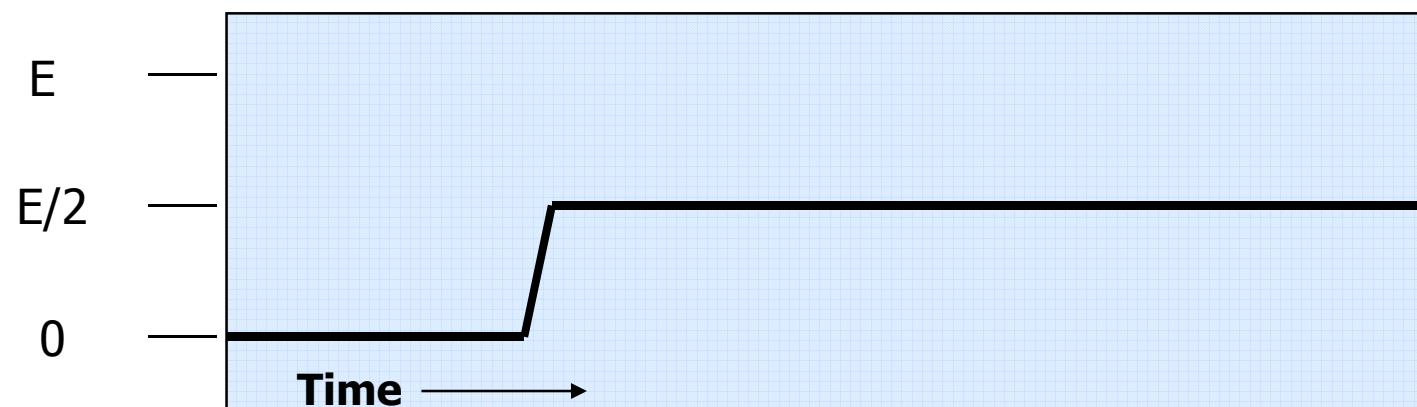

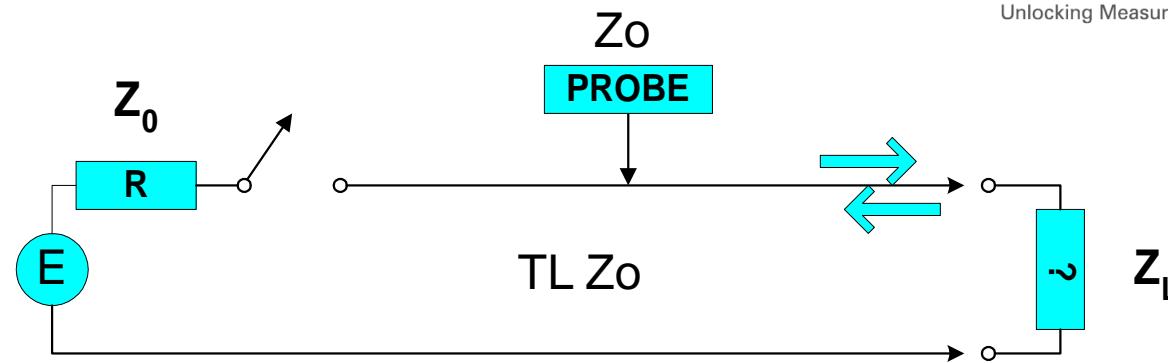

# TDR - Open Termination

Unlocking Measurement Insights for 75 Years

What do you expect to see at the probe before,

during, and after you close the switch?

Agilent Technologies

# TDR - Perfect Termination

Unlocking Measurement Insights for 75 Years

What do you expect to see at the probe before,

during, and after you close the switch?

Agilent Technologies

# TDR - Unknown Termination

Unlocking Measurement Insights for 75 Years

Is the unknown resistor closer to a short

(zero  $\Omega$ ) or an open ( $\infty \Omega$ )?

Agilent Technologies

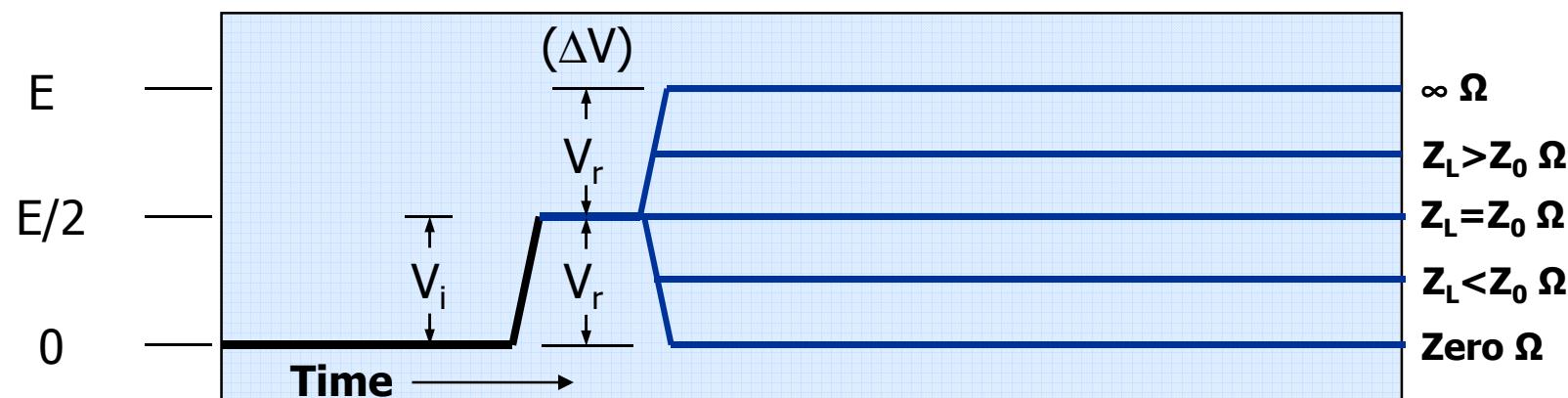

# TDR - Impedance Mismatch Terms

Unlocking Measurement Insights for 75 Years

What is the value of  $Z_{load}$ ?

$$Z_L = Z_0 \frac{1 + \rho}{1 - \rho}$$

Impedance Calculated from

Source Impedance and

Reflection Coefficient.

$$\rho = \frac{V_r}{V_i}$$

Reflection Coefficient, rho:

How much was reflected?

Agilent Technologies

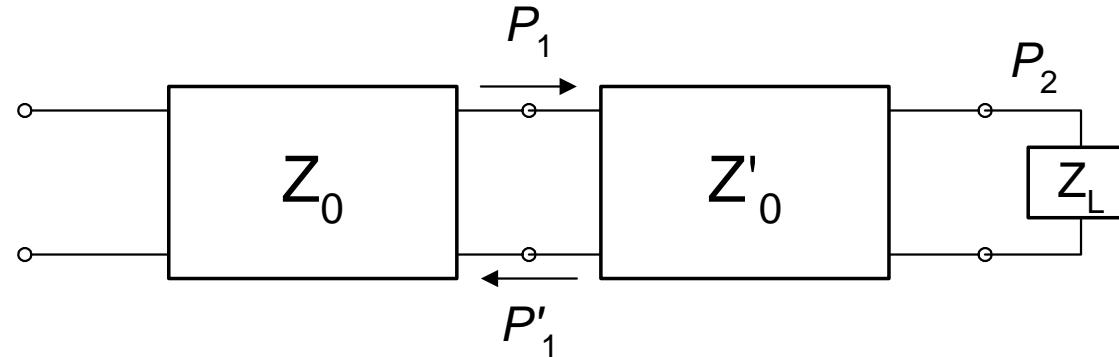

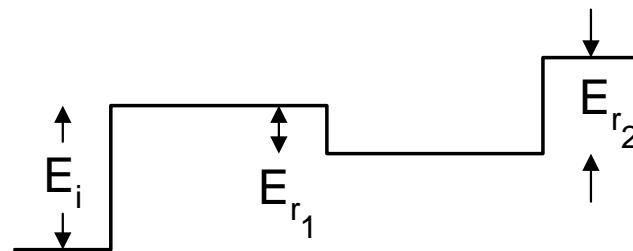

# TDR - Multiple Discontinuities

Unlocking Measurement Insights for 75 Years

$$P_1 = \frac{Z'_0 - Z_0}{Z'_0 + Z_0}$$

$$P_2 = \frac{Z_L - Z'_0}{Z_L + Z'_0}$$

**Accuracy decreases as you look further down

a line with multiple discontinuities**

Agilent Technologies

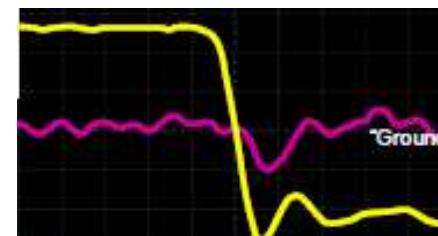

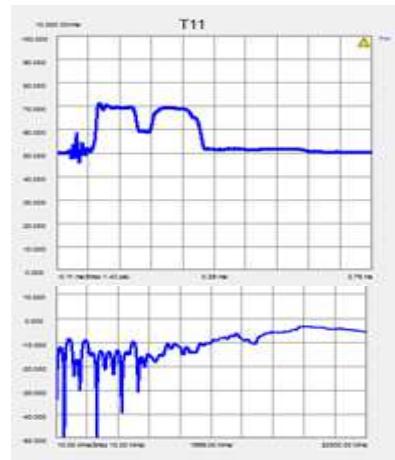

# TDR in the time domain

Unlocking Measurement Insights for 75 Years

Agilent Technologies

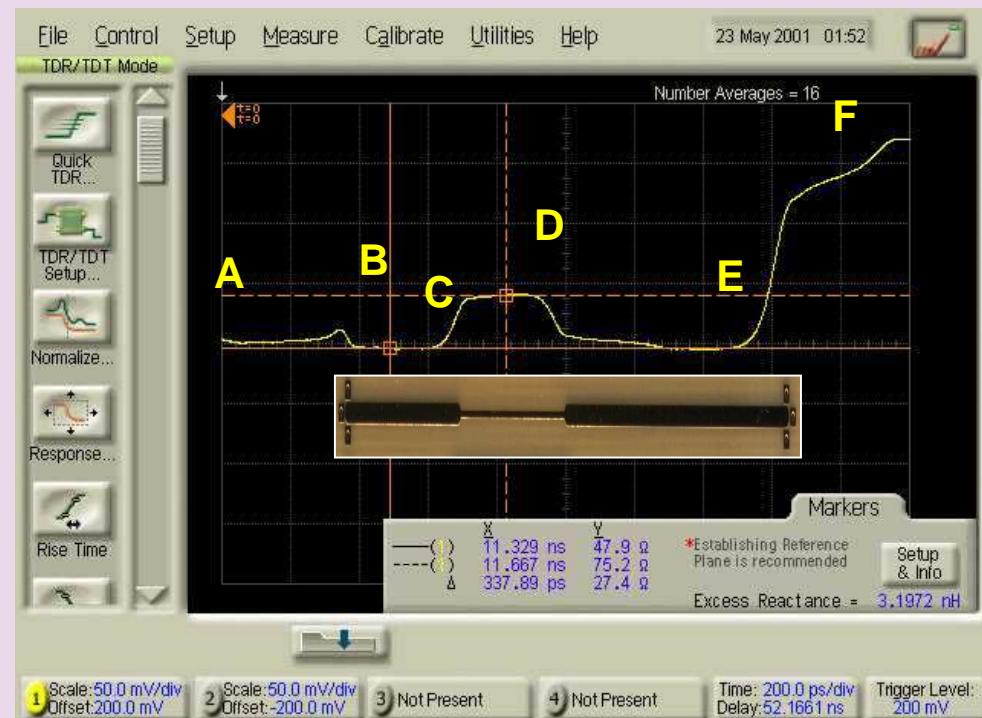

# TDR measurement based on Scope

Unlocking Measurement Insights for 75 Years

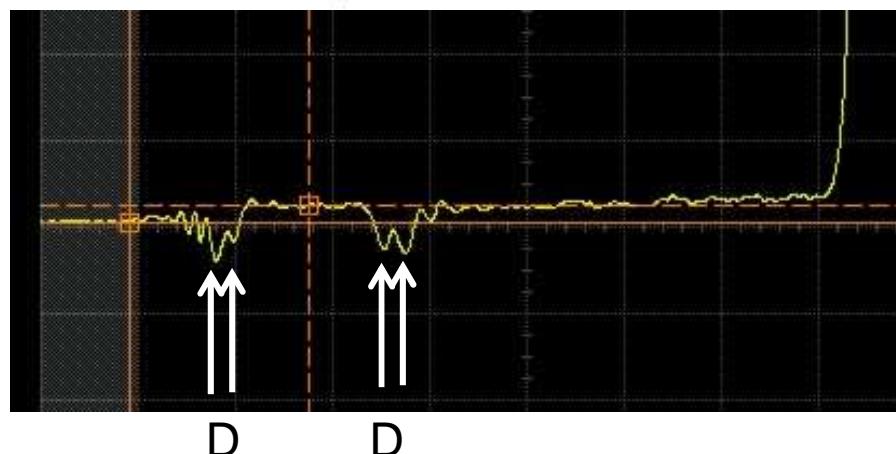

## Typical TDR result

- A: 50 Ohm cable

- B: Launch to microstrip

- C: 50 Ohm microstrip

- D: 75 Ohm microstrip

- E: 50 Ohm microstrip

- F: “open” circuit

Agilent Technologies

# Real-Time Oscilloscope

Unlocking Measurement Insights for 75 Years

Agilent Technologies

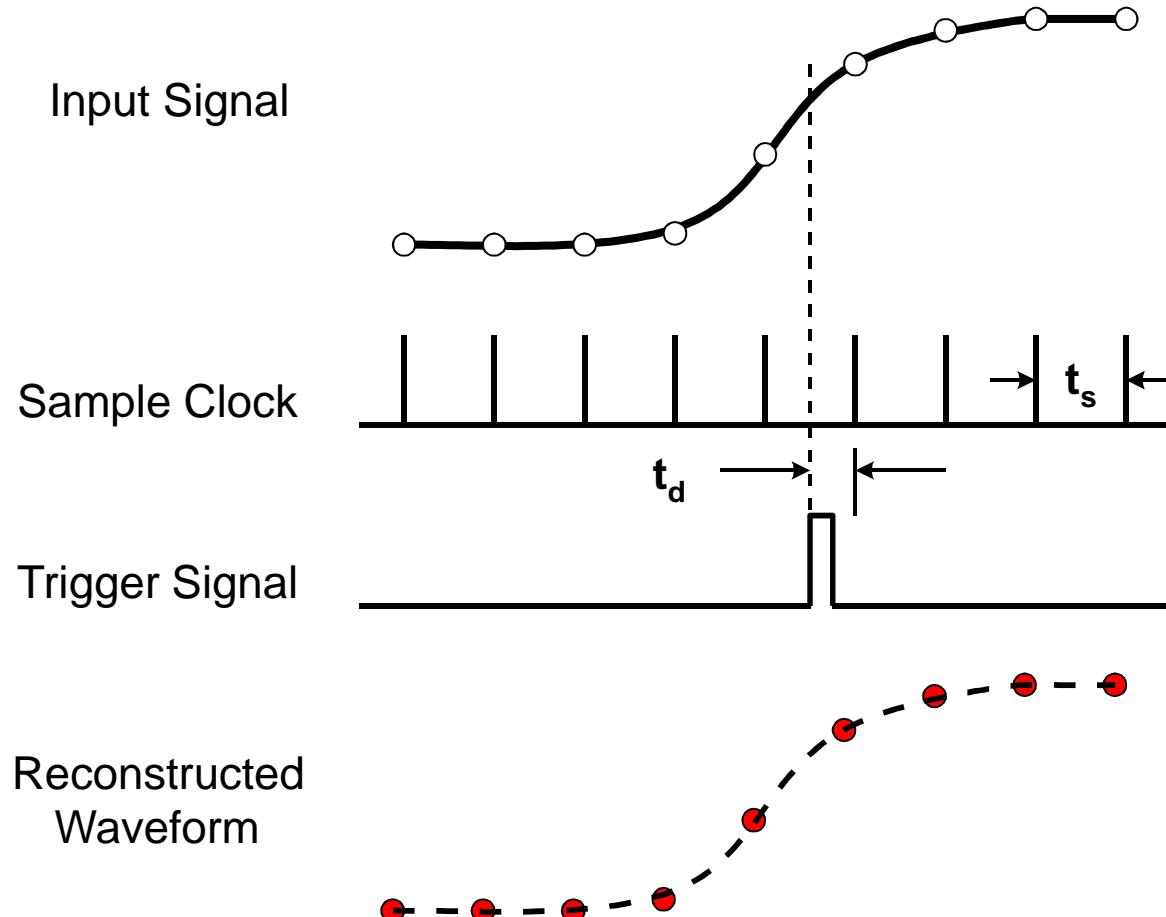

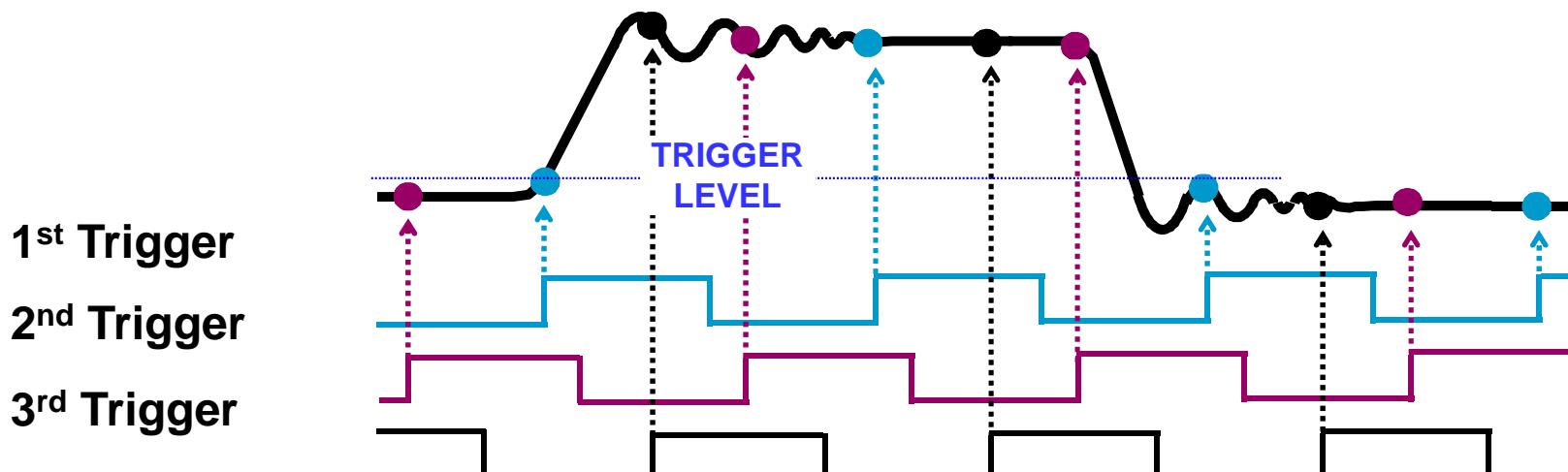

# Equivalent Time Oscilloscope

Unlocking Measurement Insights for 75 Years

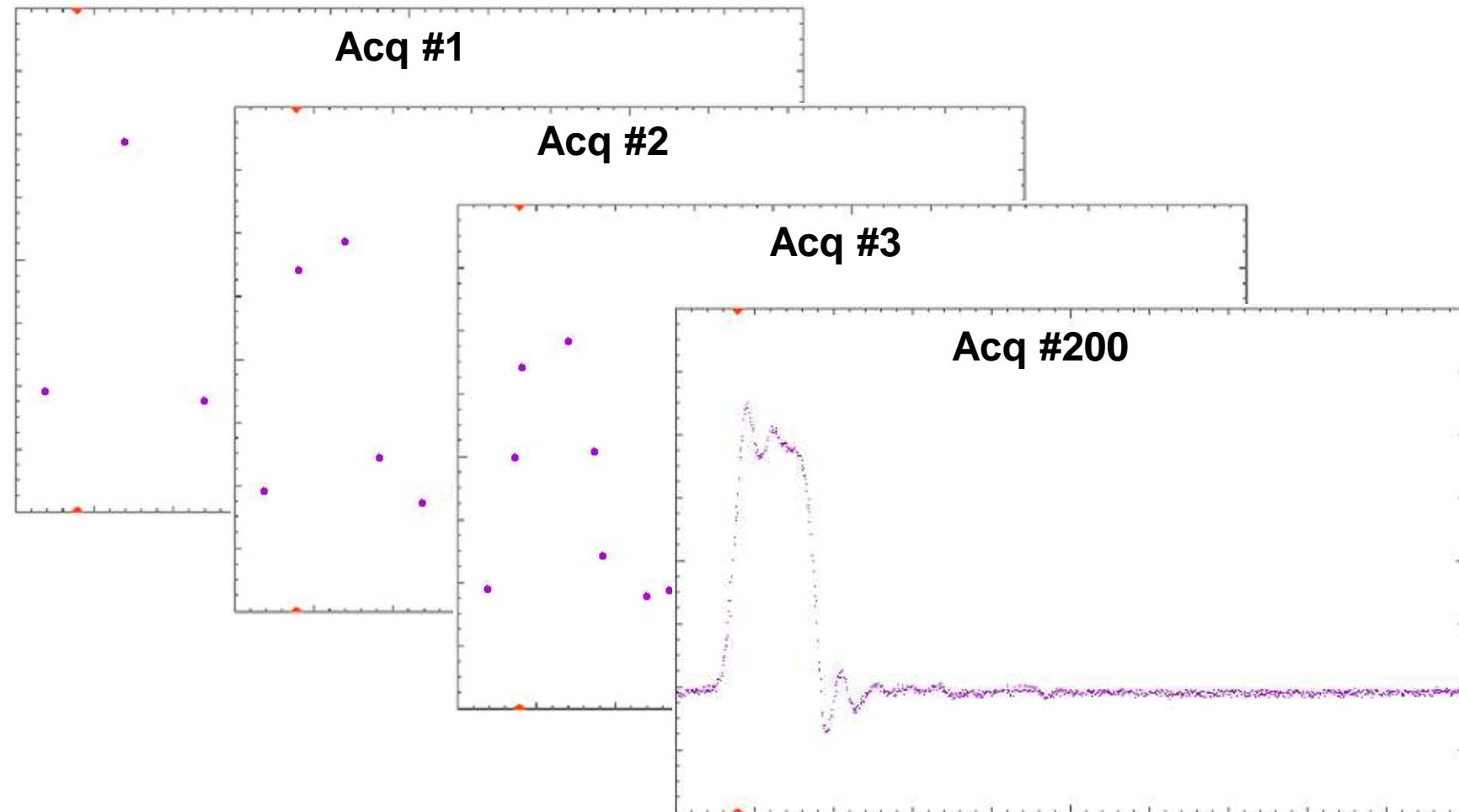

- 1) Builds up the waveform over several sweeps

- 2) samples part of the signal on the first sweep, then another part on the second sweep, and so on....

- 3) Laces all information together to recreate the waveform

- Useful for high-frequency signals

- Used ONLY with Repetitive Signals! No Glitches will be captured!

- Sample Rate is Not a Major Factor

Agilent Technologies

# Equivalent Time (Repetitive) Technique

Unlocking Measurement Insights for 75 Years

Build Up of Waveform over multiple sample events

Agilent Technologies

# TDR – Spatial Resolution

Unlocking Measurement Insights for 75 Years

## TDR Resolution

The faster the edge, the closer two impedance discontinuities can be identified as separate events on the TDR trace.

$$D_{\min} = \frac{c \cdot t_{\text{rise}}}{2\sqrt{\epsilon}}$$

- $t_{\text{r}_{\text{system}}} = \sqrt{t_{\text{r}_{\text{step}}}^2 + t_{\text{r}_{\text{scope}}}^2}$

- $\epsilon$  = dielectric constant of the transmission system

- $c$  = speed of light in a vacuum.

**For  $\epsilon = 4$  and system rise time of 8 ps,  $D_{\min} < 1\text{mm}$ .**

Agilent Technologies

# What TDR edge should I use?

Unlocking Measurement Insights for 75 Years

Select a solution based on your **application**:

- **Too fast:** you'll see impedance discontinuities that will not affect the real signals in your design (you'll waste time fixing things that do not matter)

- **Too slow:** discontinuities are masked

Agilent Technologies

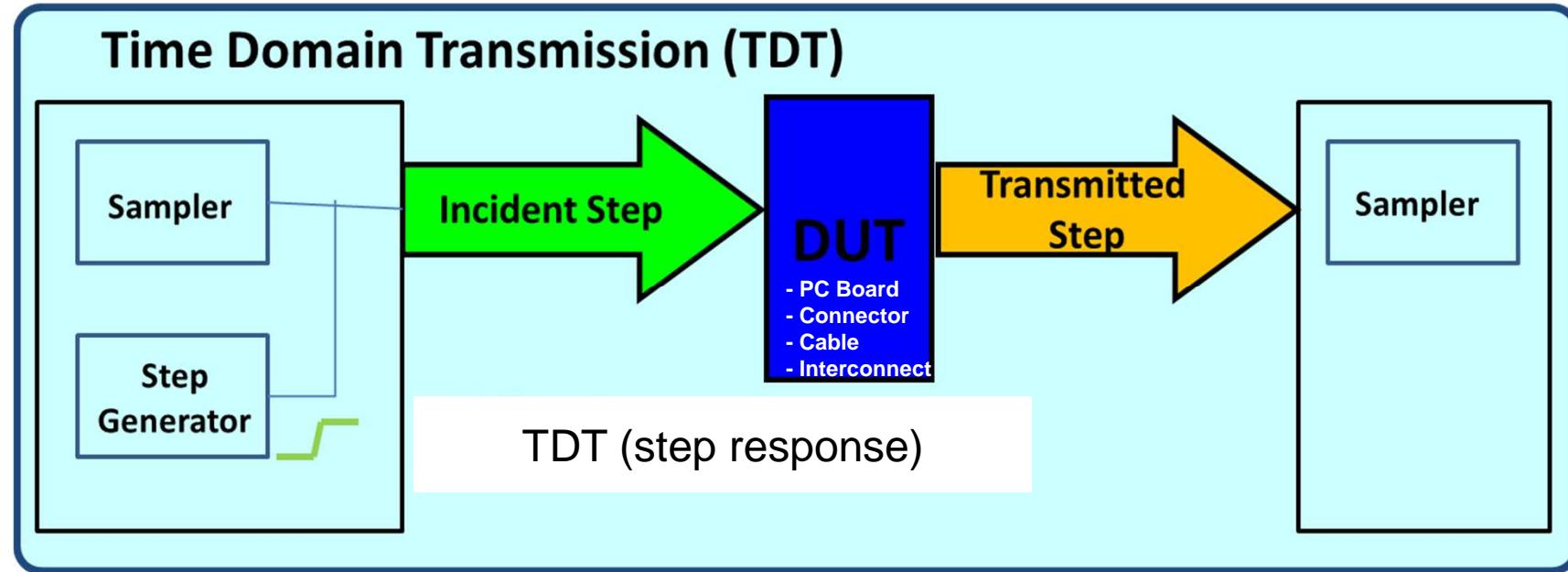

# Time Domain Transmission (TDT)

Unlocking Measurement Insights for 75 Years

## Time Domain Transmission (TDT)

- Step Response

- Propagation/Time delay

- Propagation velocity

- Rise time degradation

- Near-end crosstalk (NEXT)

- Far-end crosstalk (FEXT)

- Skew

Agilent Technologies

# AGENDA

Unlocking Measurement Insights for 75 Years

- Introduction / Signal Integrity Definition

- Evolution of Test Parameters

- Traditional TDR/TDT instrument

- **Vector Network Analyzer Basis**

- Single Ended / Differential Topologies

- Physical Layer Test System (PLTS Software)

Agilent Technologies

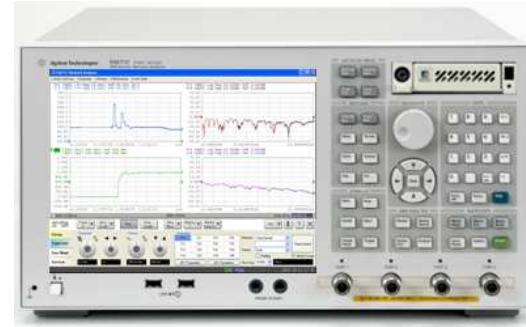

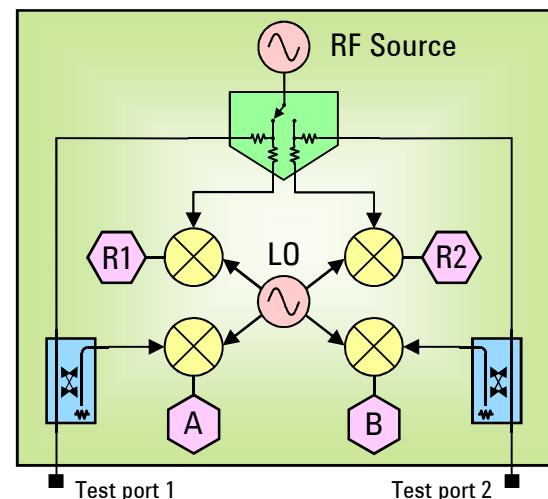

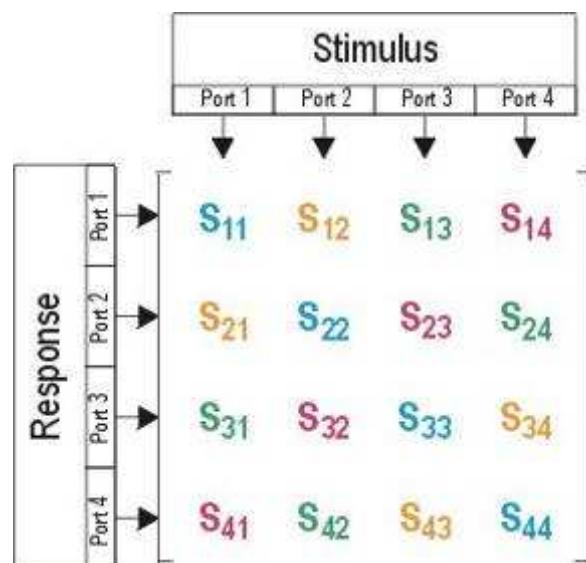

# What is Vector Network Analyzer?

Unlocking Measurement Insights for 75 Years

## Vector network analyzers (VNAs)...

- Are stimulus-response test systems

- Characterize forward and reverse reflection and transmission responses (S-parameters) of RF and microwave components

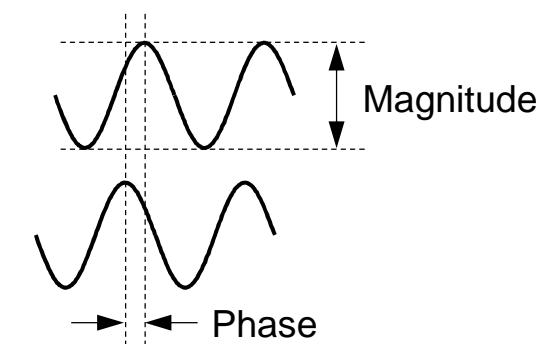

- Quantify linear magnitude and phase

- Are very fast for swept measurements

- Provide the highest level of measurement accuracy

Agilent Technologies

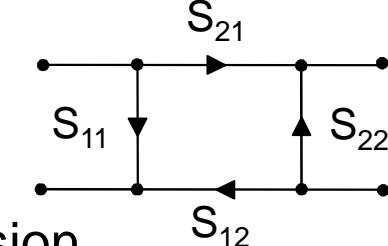

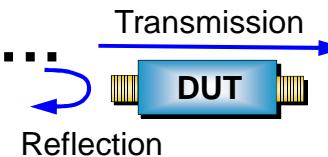

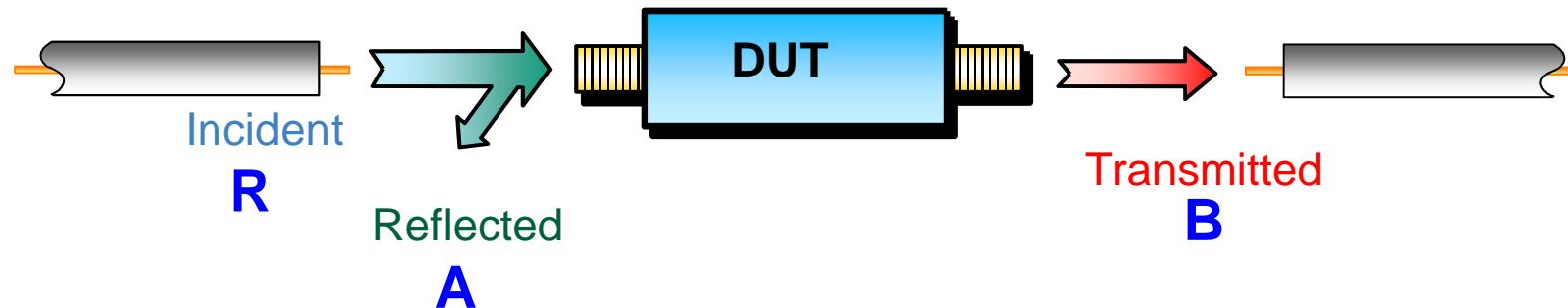

# Reflection / Transmission Coefficients

Unlocking Measurement Insights for 75 Years

## REFLECTION

$$\frac{\text{Reflected}}{\text{Incident}} = \frac{A}{R}$$

SWR

S-Parameters  $S_{11}, S_{22}$

Reflection Coefficient  $\Gamma, \rho$

Return Loss

Impedance, Admittance  $R+jX, G+jB$

## TRANSMISSION

$$\frac{\text{Transmitted}}{\text{Incident}} = \frac{B}{R}$$

Gain / Loss

S-Parameters  $S_{21}, S_{12}$

Transmission Coefficient  $T, \tau$

Group Delay

Insertion Phase

Agilent Technologies

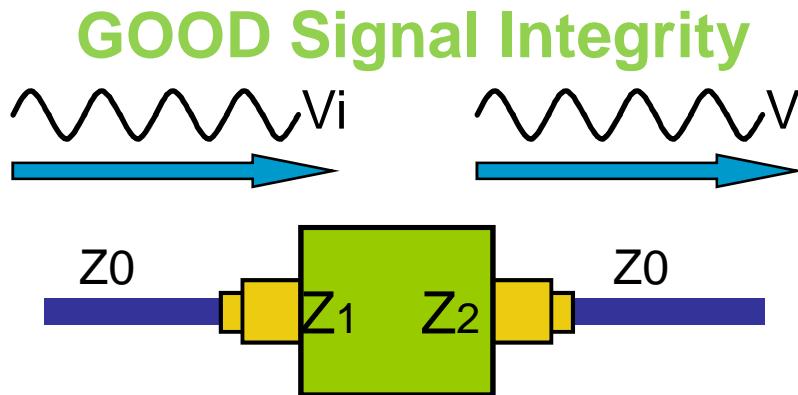

# Signal Integrity vs S-Parameters

Unlocking Measurement Insights for 75 Years

$$Z_1 = Z_2 = Z_0$$

Well Controlled

Impedance Environment

$S_{11} \rightarrow$  low reflections

$S_{21} \rightarrow$  high transmission

$$Z_1, Z_2 \neq Z_0$$

Impedance

Discontinuities Present

$S_{11} \rightarrow$  high reflections

$S_{21} \rightarrow$  low transmission

Agilent Technologies

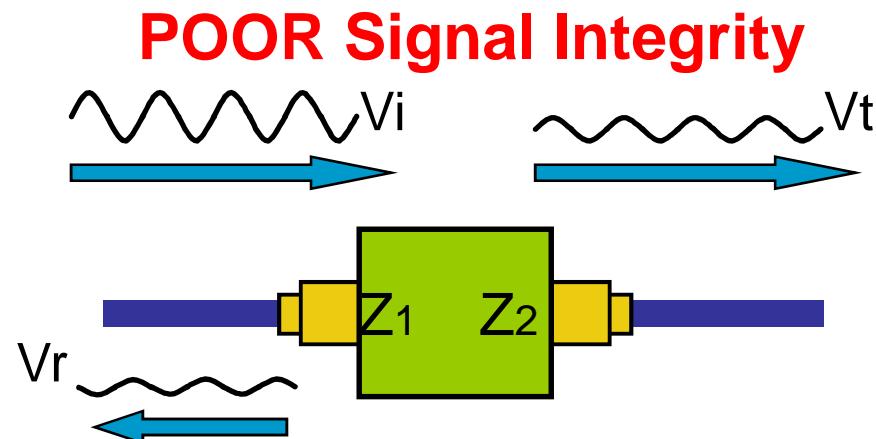

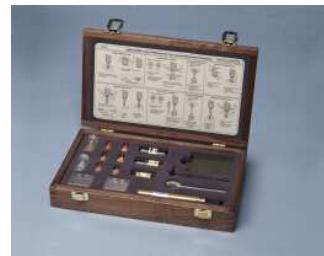

# Importance of Calibration !

Unlocking Measurement Insights for 75 Years

Agilent Technologies

# AGENDA

Unlocking Measurement Insights for 75 Years

- Introduction / Signal Integrity Definition

- Evolution of Test Parameters

- Traditional TDR/TDT instrument

- Vector Network Analyzer Basis

- **Single Ended / Differential Topologies**

- Physical Layer Test System (PLTS Software)

Agilent Technologies

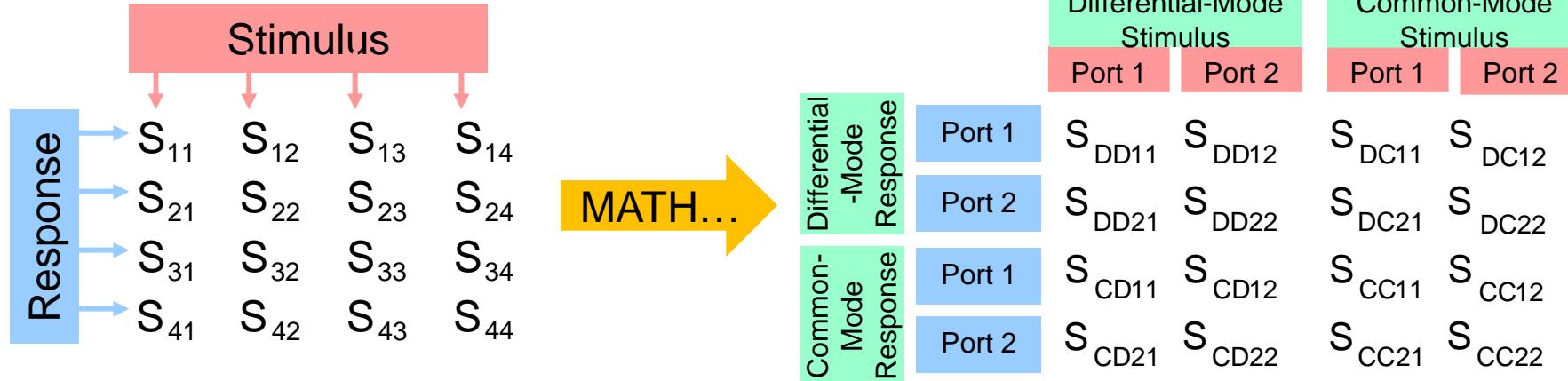

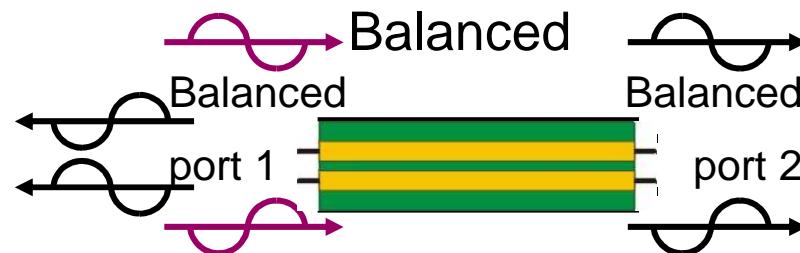

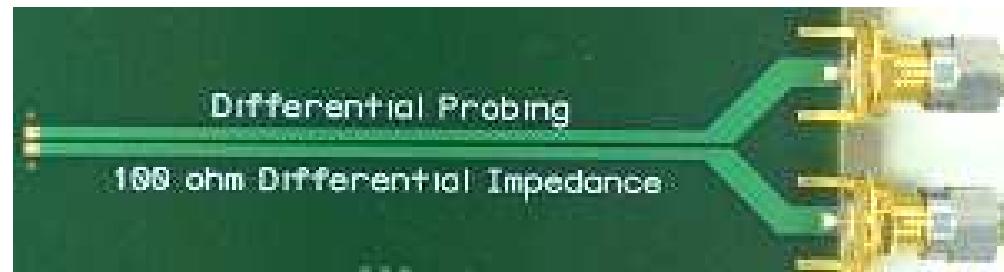

# Trend to Differential Topologies

Unlocking Measurement Insights for 75 Years

- **Ideal differential devices**

- Low voltage requirements

- Noise and EMI immunity

- Virtual grounding

- **Non-ideal devices are not symmetric**

- Can be identified by mode-conversions

- Differential  $\rightarrow$  Common

- Common  $\rightarrow$  Differential

- **Differential signal integrity design tools are needed**

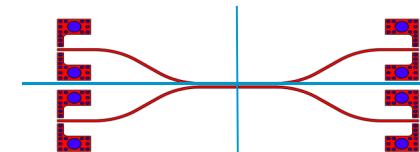

## Differential Structure

Agilent Technologies

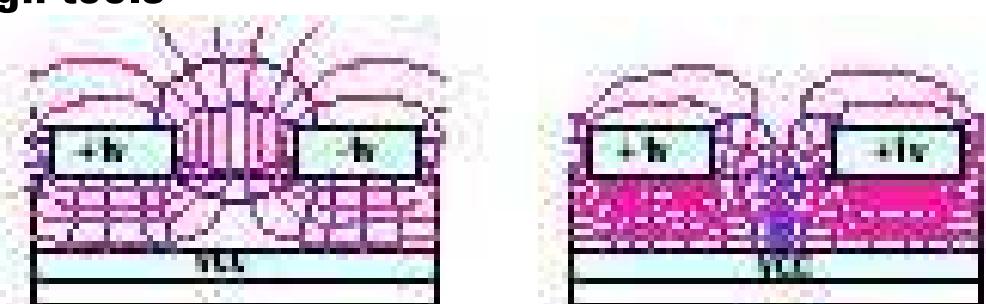

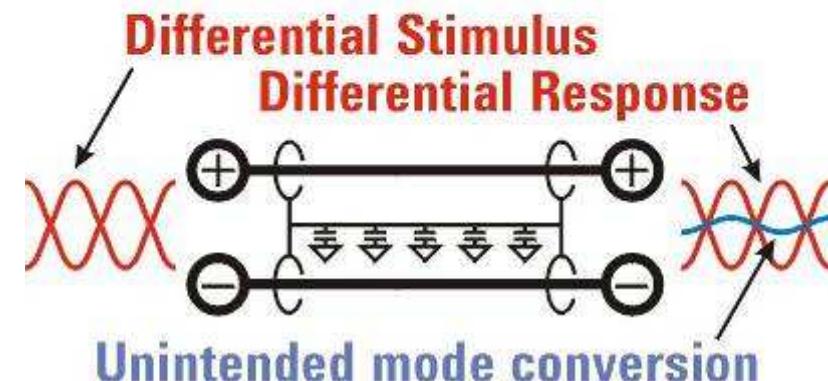

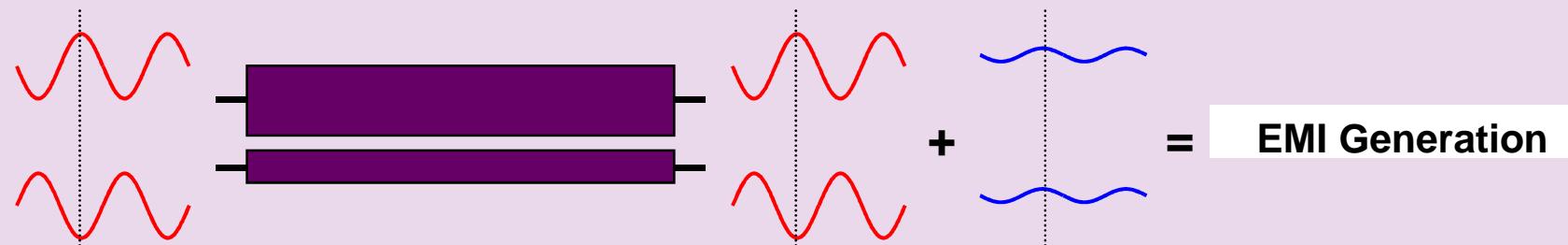

# What about non-ideal devices?

Unlocking Measurement Insights for 75 Years

- **Differential-stimulus to common-response conversion**

Imperfectly matched lines mean the electromagnetic fields of the signals are not as well confined as they should be – giving rise to generation of interference to neighboring circuits.

- **Common-stimulus to differential-response conversion**

Imperfectly matched lines mean that interfering signals do not cancel out completely when subtraction occurs at the receiver. Measured by stimulating common-mode to simulate interference.

Agilent Technologies

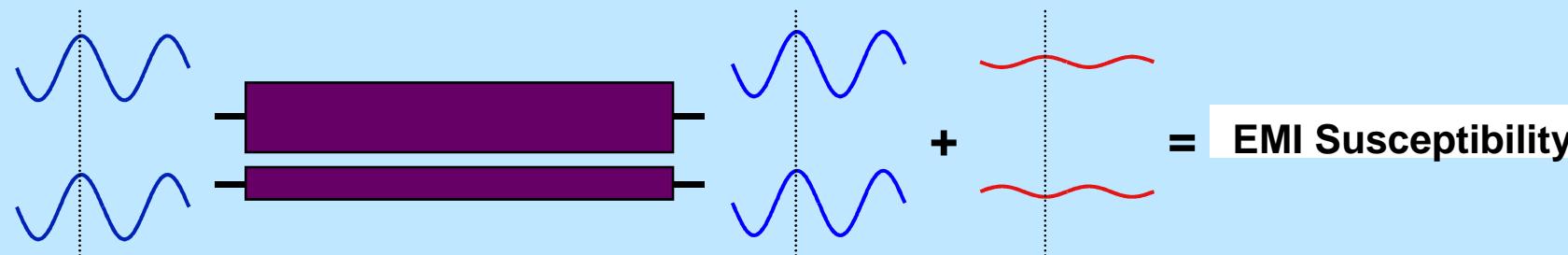

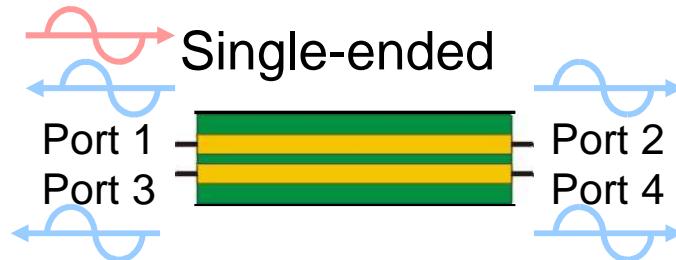

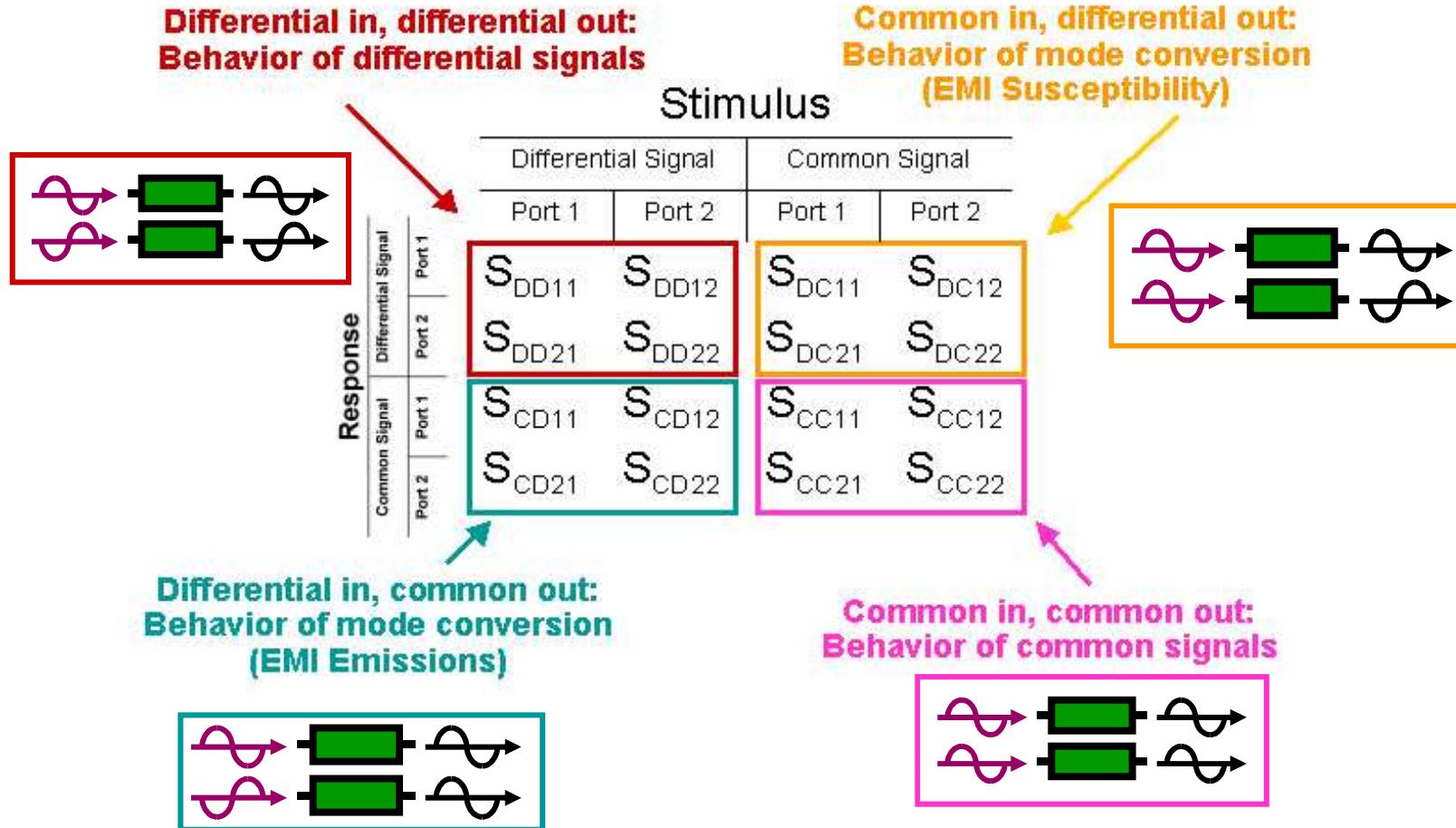

# Single-ended to Differential [S]

Unlocking Measurement Insights for 75 Years

Naming Convention:

$S_{\text{mode res.}, \text{mode stim.}, \text{port res.}, \text{port stim.}}$

Agilent Technologies

# Mixed-Mode S-Parameters

Unlocking Measurement Insights for 75 Years

**Example  $S_{CD21}$ :** Drive port 1 differentially and measure what has been converted to common mode at port 2

Agilent Technologies

# AGENDA

Unlocking Measurement Insights for 75 Years

- Introduction / Signal Integrity Definition

- Evolution of Test Parameters

- Traditional TDR/TDT instrument

- Vector Network Analyzer Basis

- Single Ended / Differential Topologies

- **Physical Layer Test System (PLTS Software)**

Agilent Technologies

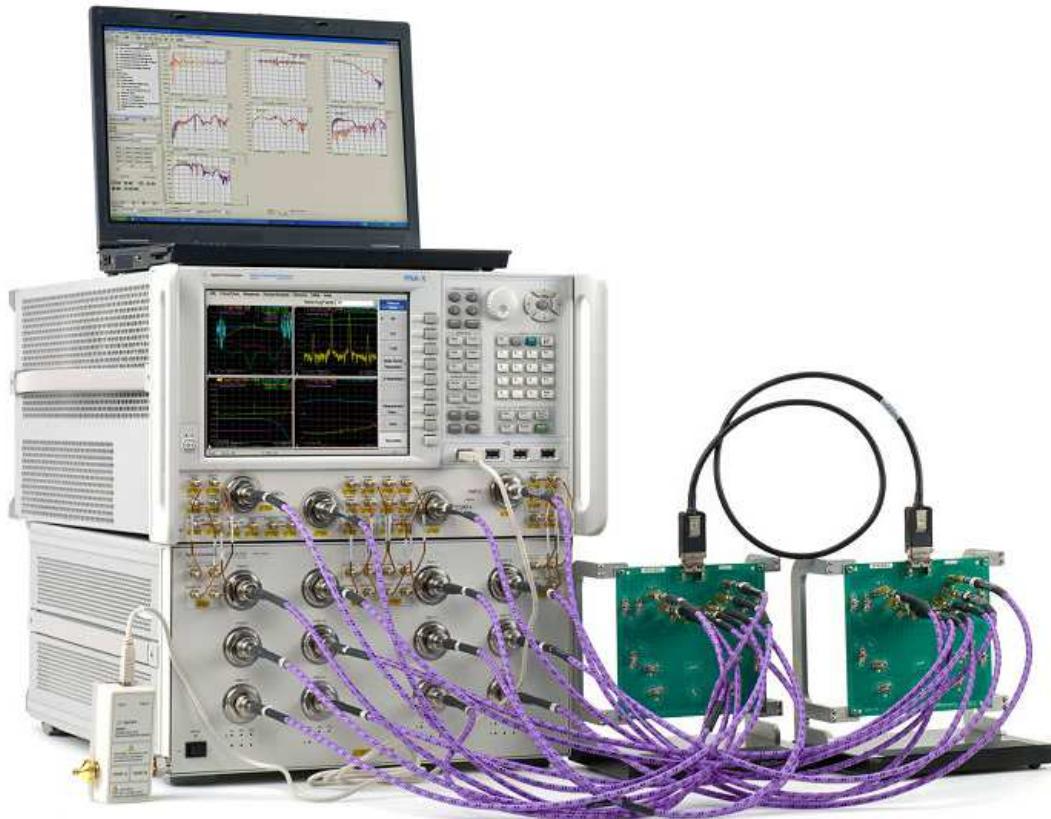

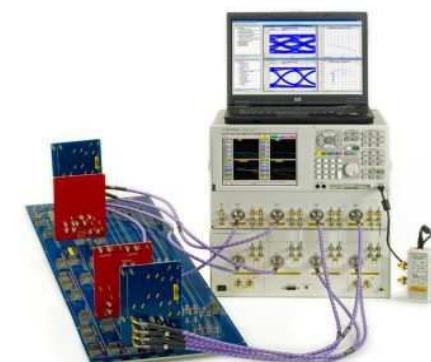

# What is PLTS?

Unlocking Measurement Insights for 75 Years

- N1930B - Software Solution

- Industry standard for interconnect analysis

- Calibrate, measure and analyze linear passive devices

- Use either VNA or TDR

- Provides Advanced Calibration Techniques

Agilent Technologies

# PLTS: The Ultimate SI Solution

Unlocking Measurement Insights for 75 Years

Agilent Physical Layer Test Systems (PLTS) are the most accurate and comprehensive tools for characterizing high-speed digital interconnects.

- Reduce development times

- Increase performance margins

- Improve signal quality

- Reduce EMI emissions/susceptibility

- Improve models for simulation

- Develop more competitive products

N1930B Physical Layer Test System (PLTS)

Agilent Technologies

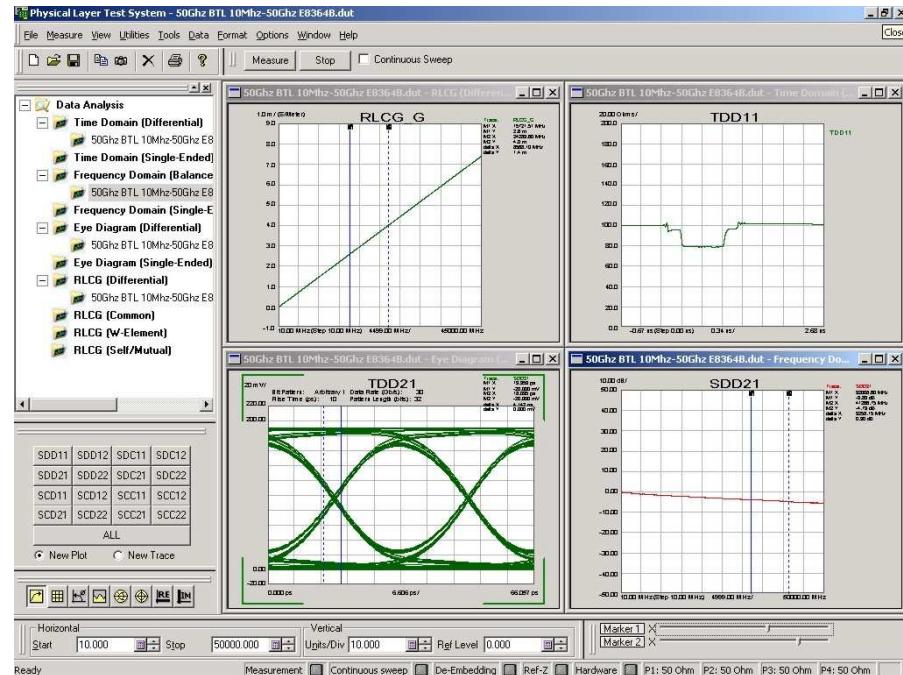

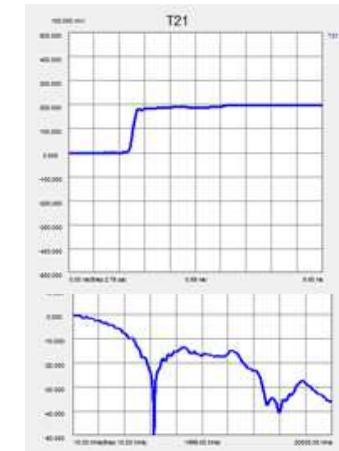

# TDR/TDT and S-Parameters

Tremendous insight together.

Frequency Domain Parameters

Return Loss or TDR

Insertion Loss or TDT

Near End Crosstalk (NEXT)

Far End Crosstalk (FEXT)

← FFT —

— IFFT →

Time Domain Parameters

Agilent Technologies

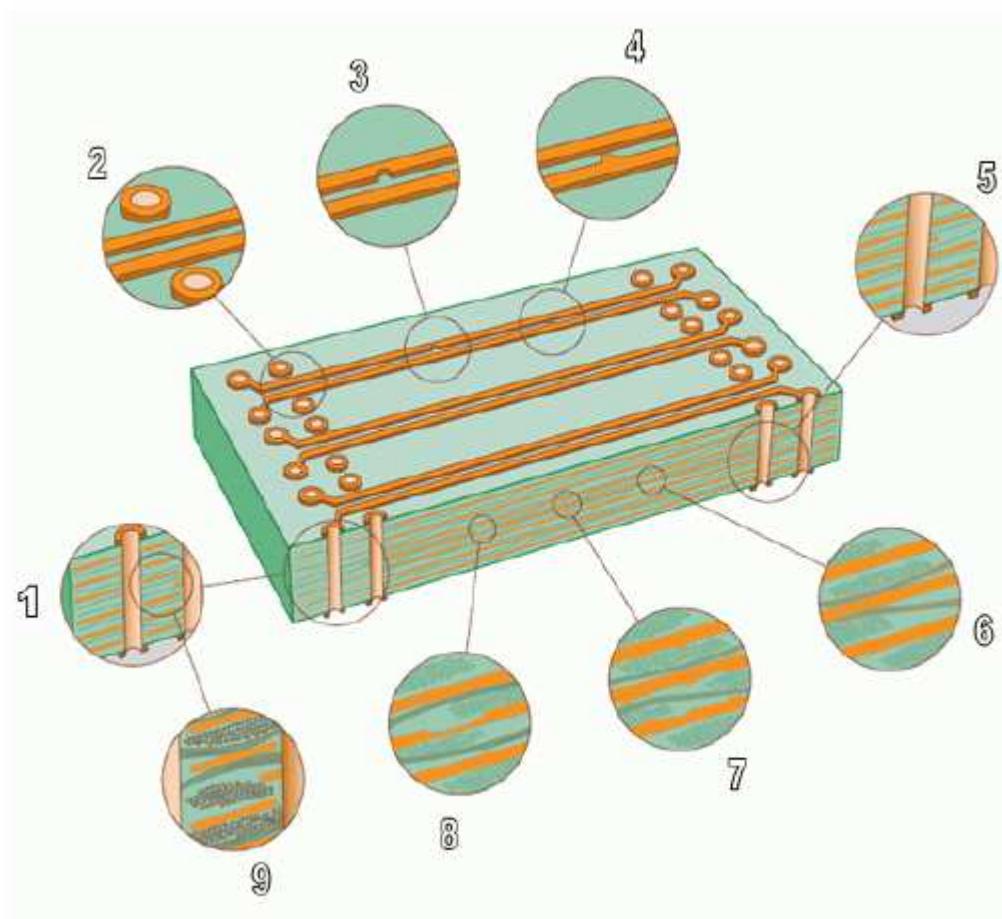

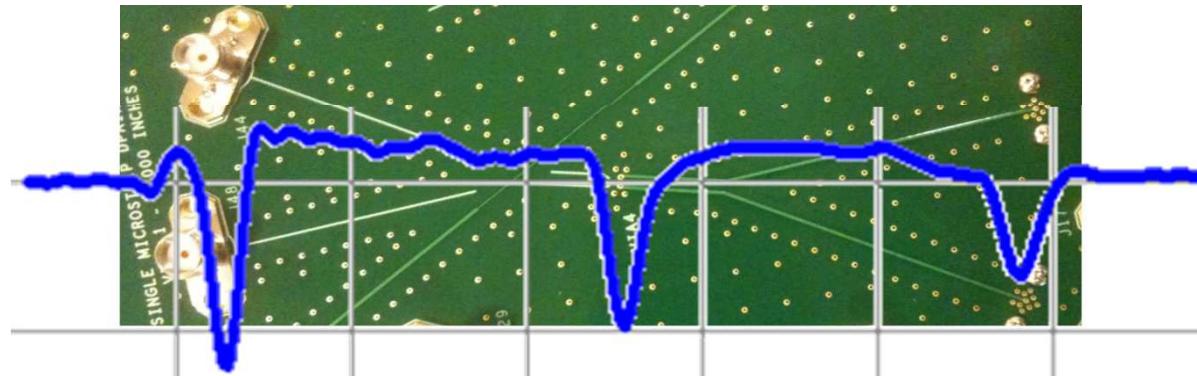

# Find out what's causing impedance discontinuities on your PCB

Unlocking Measurement Insights for 75 Years

1. Parasitic capacitance in through hole

2. Localized crosstalk

3. Localized changes in conductor width

4. Localized changes in conductor spacing

5. Reflections due to via stub

6. Non-uniform dielectric

7. Dielectric constant variation

8. Surface treatment thickness non-uniformity

9. Localized changes in foil thickness

Agilent Technologies

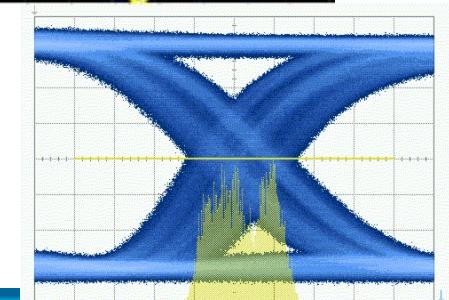

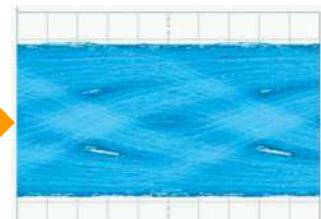

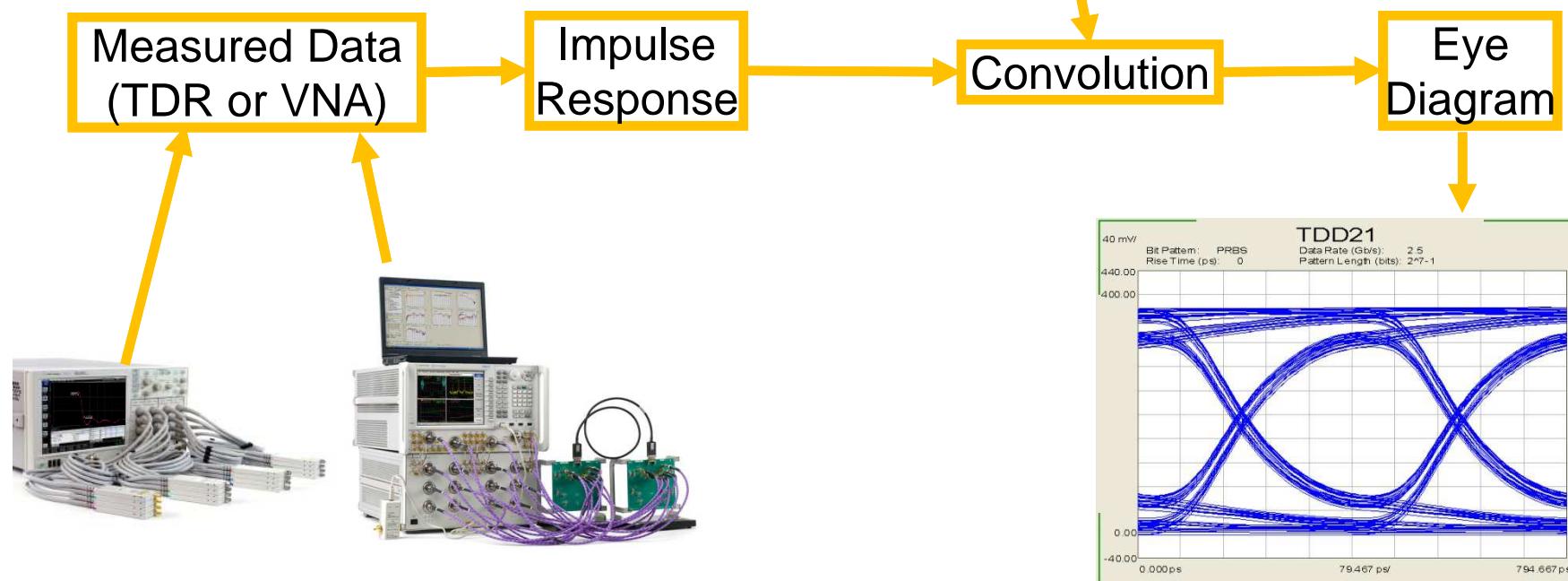

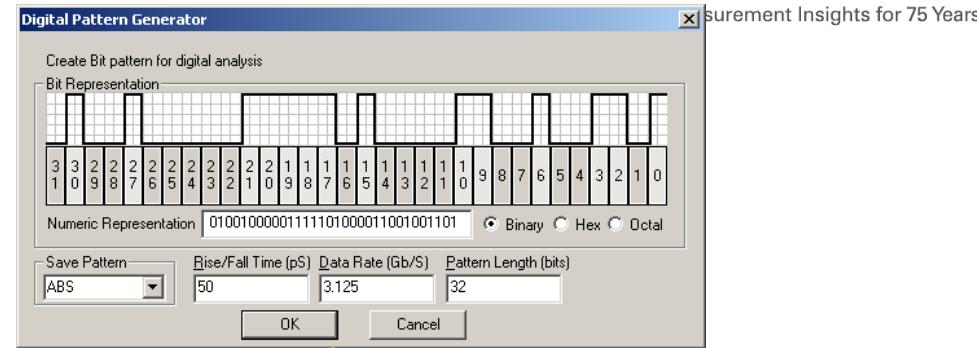

# PLTS Eye diagram

## PLTS Virtual Pattern Generator

Agilent Technologies

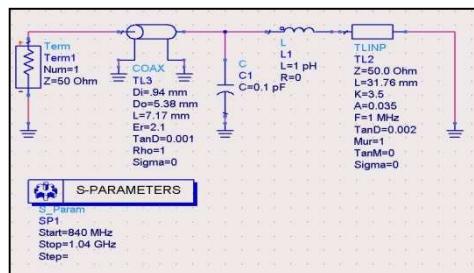

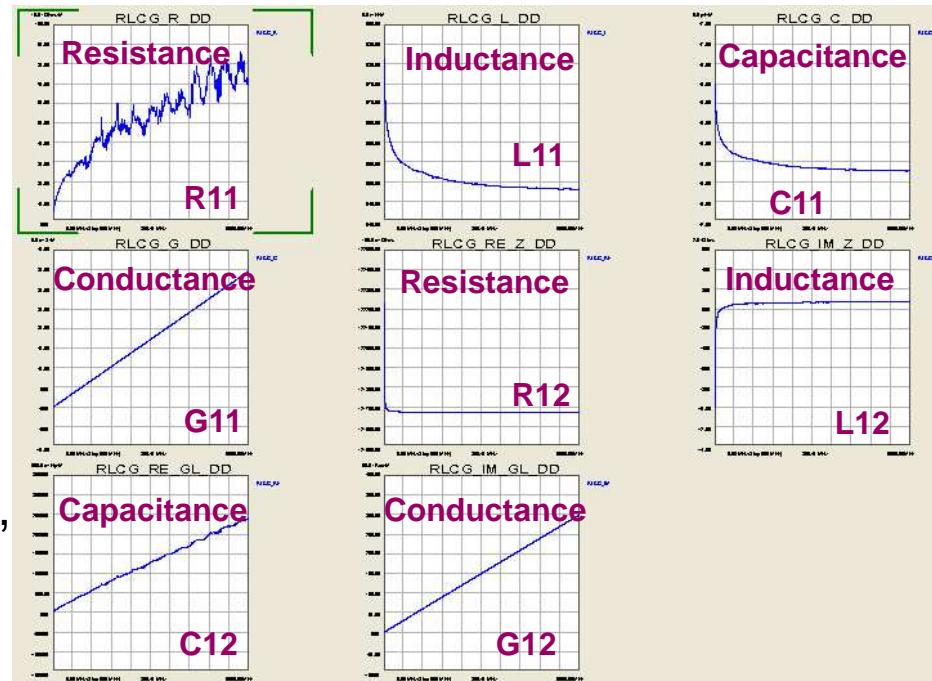

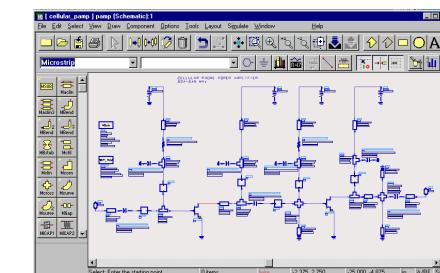

# PLTS RLCG Model Extraction

RLCG models describe electrical behavior of passive transmission lines in an equivalent circuit model

PLTS creates highly accurate, measurement-based coupled transmission line model

PLTS can export into modeling and simulation software such as Agilent ADS, Synopsis HSPICE, and TDA Systems Iconnect

Transmission line RLCG model

ADS schematic

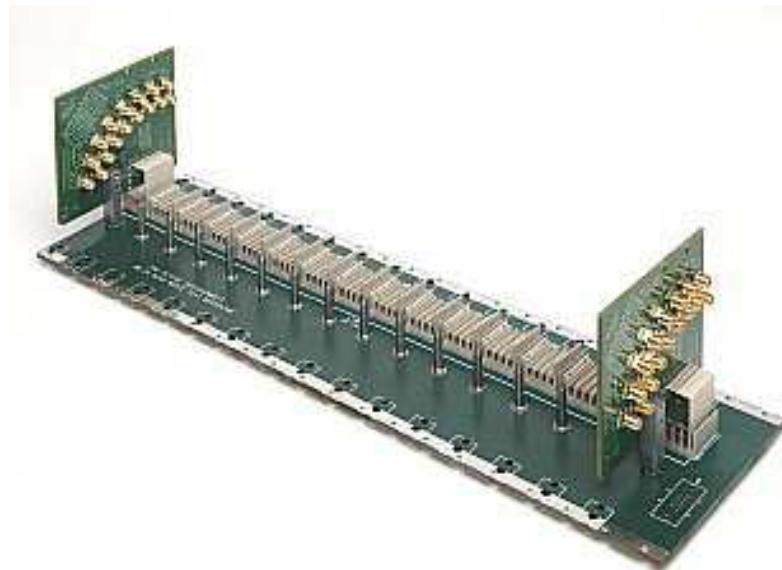

## XAUI Backplane Interconnect

The XAUI is designed as an interface extender, and the interface, which it extends, is the XGMII, the 10 Gigabit Media Independent Interface.

Differential Topology, Data Rate = 3.125Gbps , rise time = 60ps

Want to know more about XAUI?... <http://cp.literature.agilent.com/litweb/pdf/5988-5509EN.pdf>

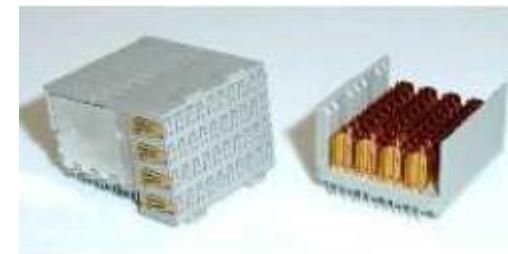

# Non Coaxial Challenge

Unlocking Measurement Insights for 75 Years

Signal Integrity devices do not have coax connectors

- Packages, high speed differential connectors, traces, cables, backplanes, etc

Many RF devices are fixtured for measurements

There are two choices (both can give good results):

- **Probe your device**

- Expensive, probing expertise required, can be difficult

- **Build a Fixture for your device to get to coax**

- How to remove your fixture effects when they can't be ignored?

Agilent Technologies

# The Problem...

Unlocking Measurement Insights for 75 Years

What I want to measure is embedded in the middle of a bunch of interconnect I don't care about

*I just want the via structure, or the connector, or the cable, or the interface, or the uniform trace,...*

Agilent Technologies

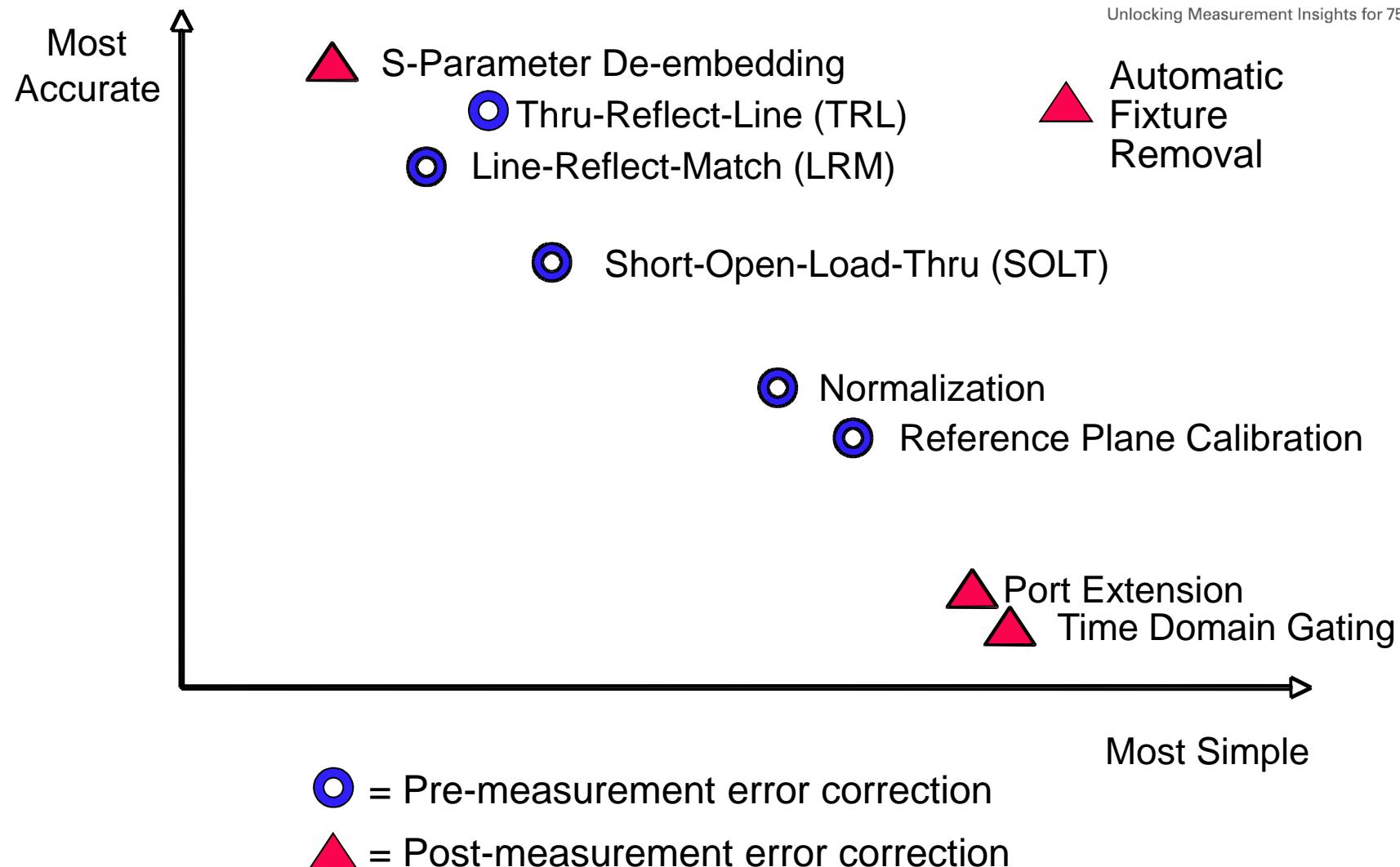

# Error Correction Techniques

Unlocking Measurement Insights for 75 Years

Agilent Technologies

# The Solution...

Unlocking Measurement Insights for 75 Years

## Traditional Calibration

- SOLT

- TRL (thru, reflect, line)

- LRM (line, reflect, match)

## De-embedding using

- Measured text fixtures

- Calculated test fixtures by 3D full wave field solver

- Calculated text fixtures by approximation (port extension)

The new way: really simple, **automatic fixture removal (AFR)**

Agilent Technologies

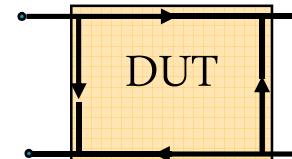

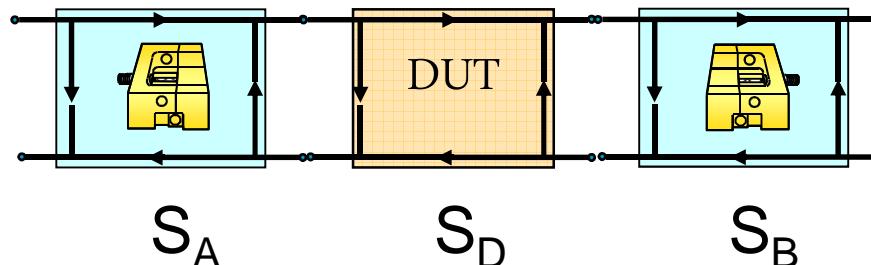

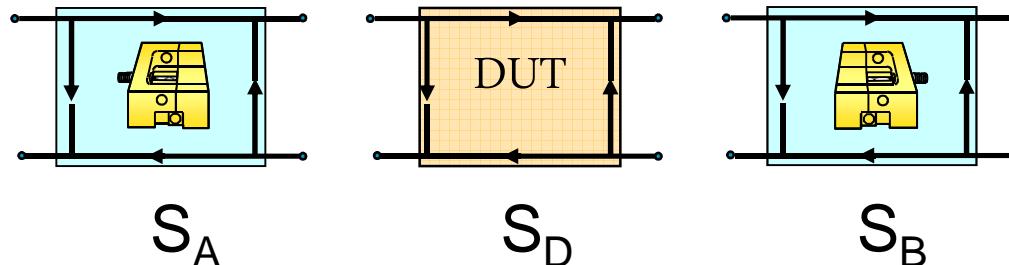

# De-Embedding “Automagically”

Unlocking Measurement Insights for 75 Years

**What we want:** DUT performance

$S_D$

**What we measure:**

composite measurement

of DUT and fixtures

With the separate fixtures' S-Parameters, we can de-embed the DUT alone from the composite measurements

***The challenge:*** getting the  $S_A$  and  $S_B$  de-embed files

Agilent Technologies

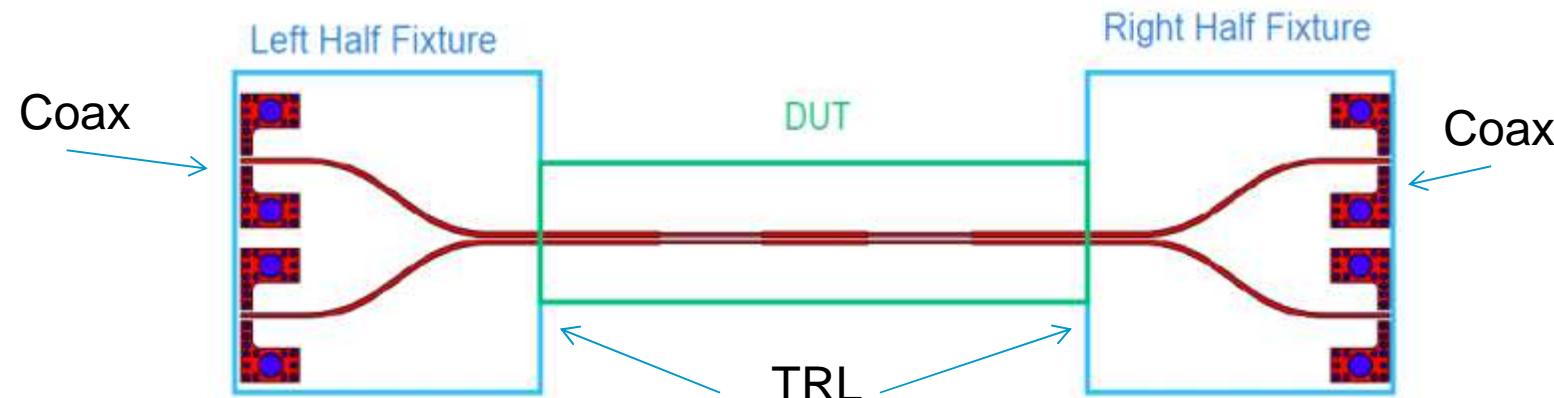

# Removing Fixtures

Unlocking Measurement Insights for 75 Years

Historically – 2 methods:

- Model fixture using EM Simulation and de-embed the fixtures from the measurement

- Use a TRL calibration technique to move measurement reference planes to the DUT.

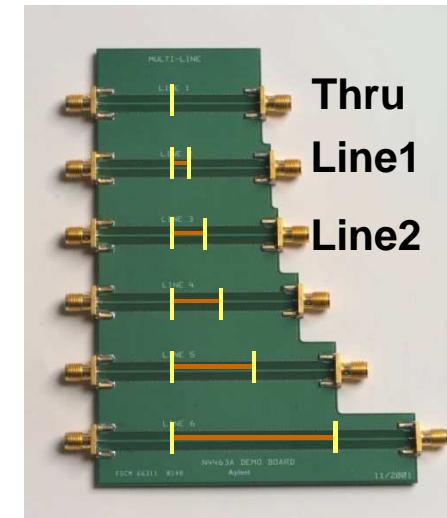

## Assumptions for single ended TRL

- Connectors and launches are identical

- All lines have same Transmission Line characteristics

- Impedance, loss, propagation

- Only differ in length

- Lines are usable 20 to 160 degrees relative to thru

- **No coupling in fixture is removed**

- Usually 2-4 lines depending on frequency range

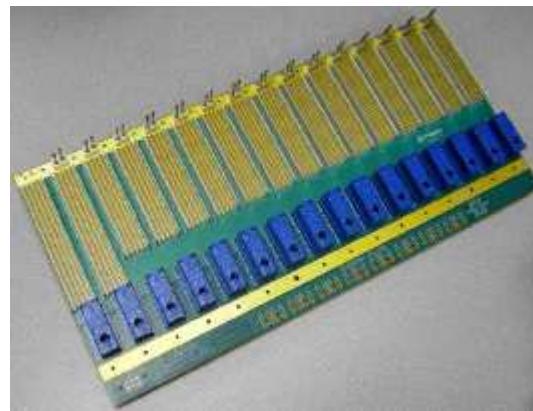

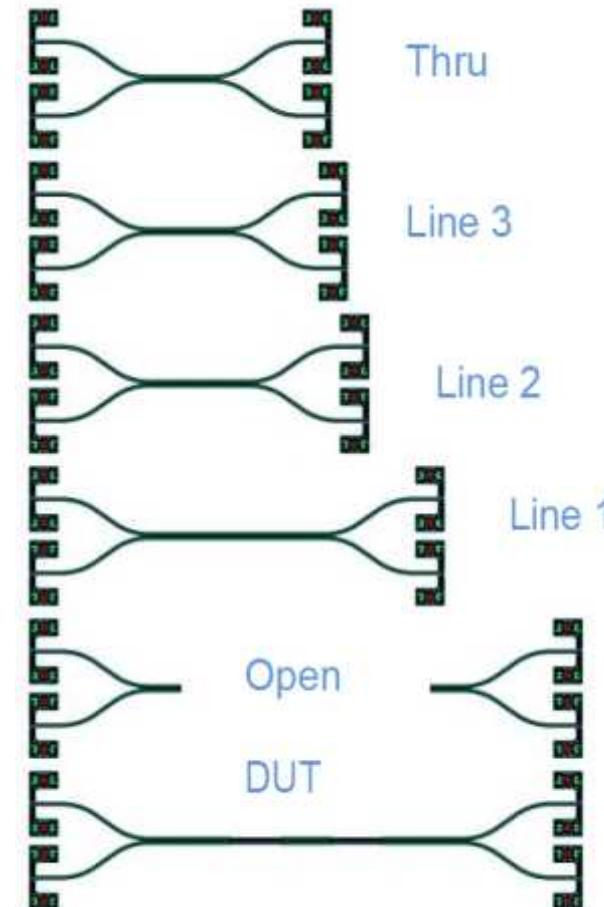

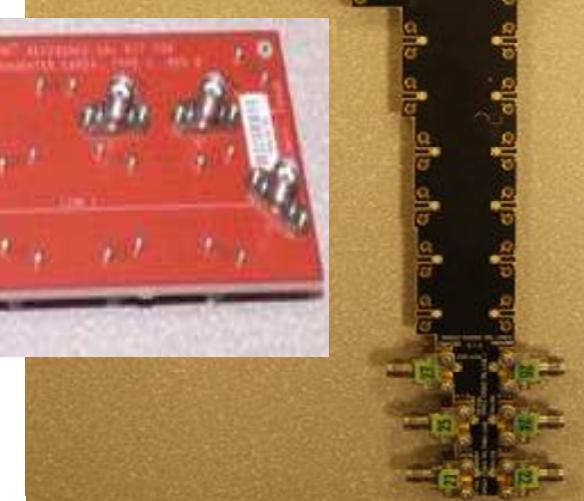

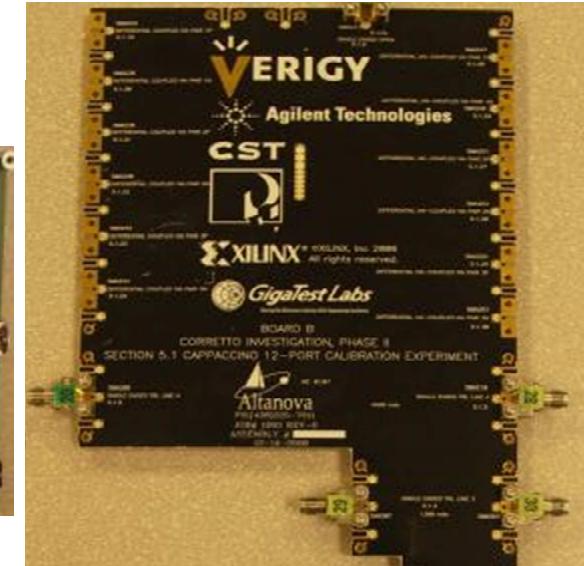

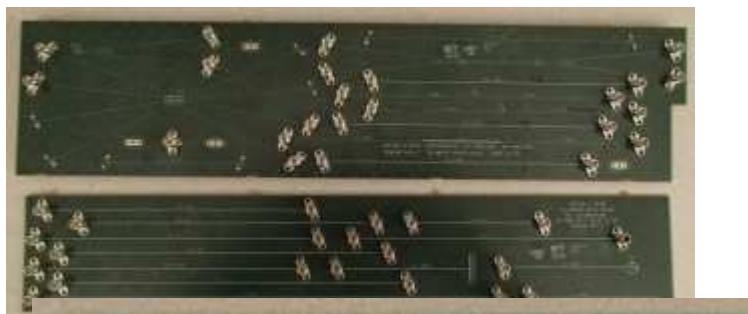

# Differential Cross Talk Calibration

Unlocking Measurement Insights for 75 Years

## 4-port TRL Calibration Technique

Fixture may be asymmetric

Similar assumptions to single ended TRL

- Repeatability of connector, launch, and line

- lines are usable 20 to 160 degrees relative to thru

Additional differential constraints

- $SDC_{nm}$  and  $SCD_{nm} < -30$  dB

- Skew between lines  $< 10$  degrees

**Coupling in fixture is removed**

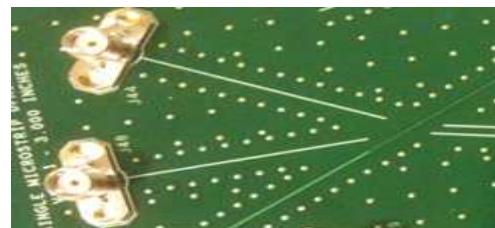

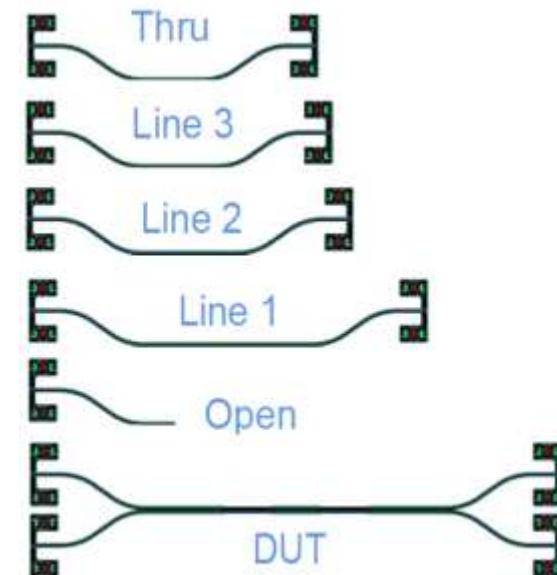

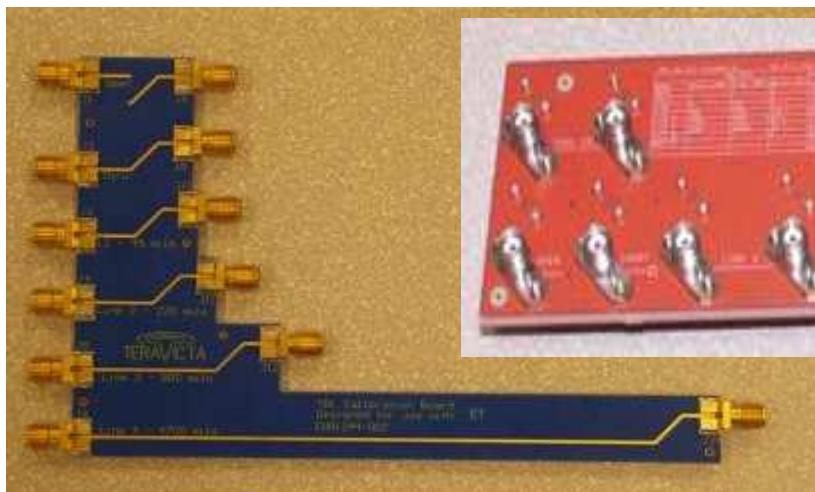

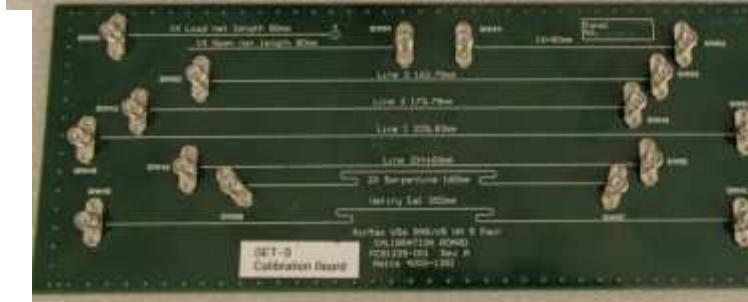

# Design/ Verify in PLTS your TRL calkits

Unlocking Measurement Insights for 75 Years

Agilent Technologies

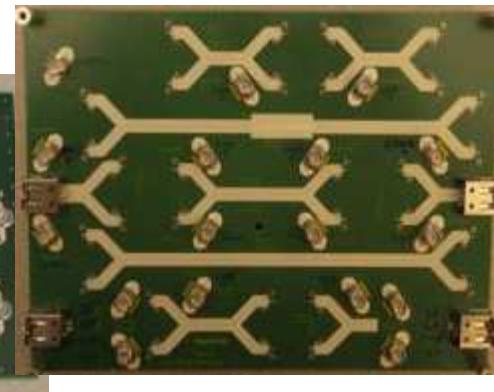

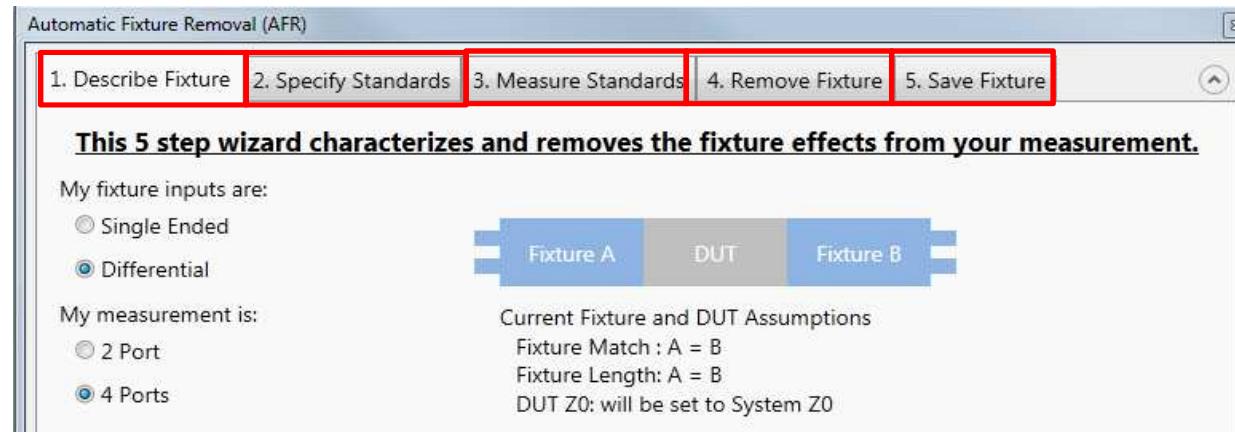

# Automatic Fixture Removal !!!

Unlocking Measurement Insights for 75 Years

New 5 Step Wizard makes it easy to define your fixture and remove it from your measurement.

Open or Short

2xTHRU

Agilent Technologies

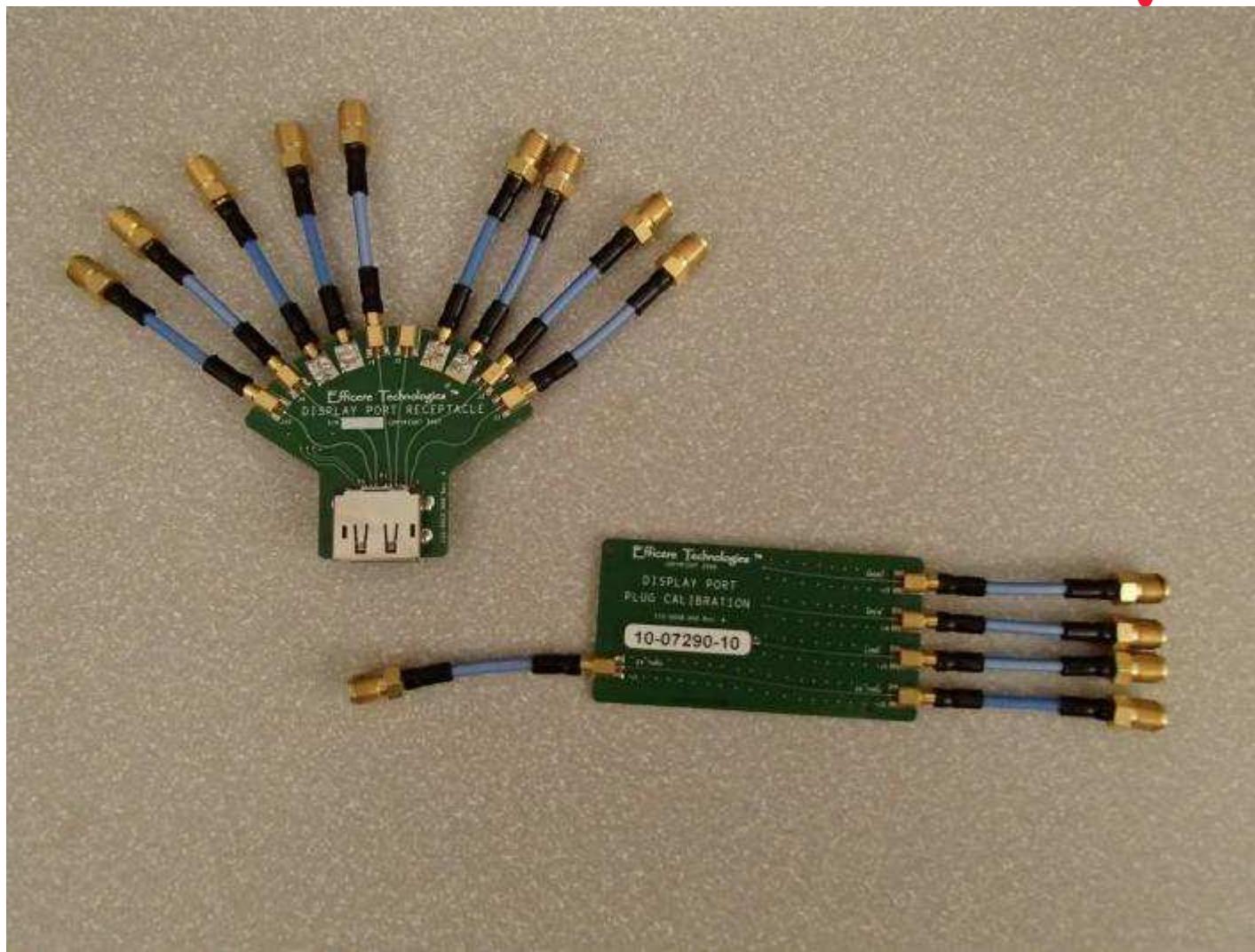

# Cable Fixtures – Display Port

ment Insights for 75 Years

Agilent Technologies

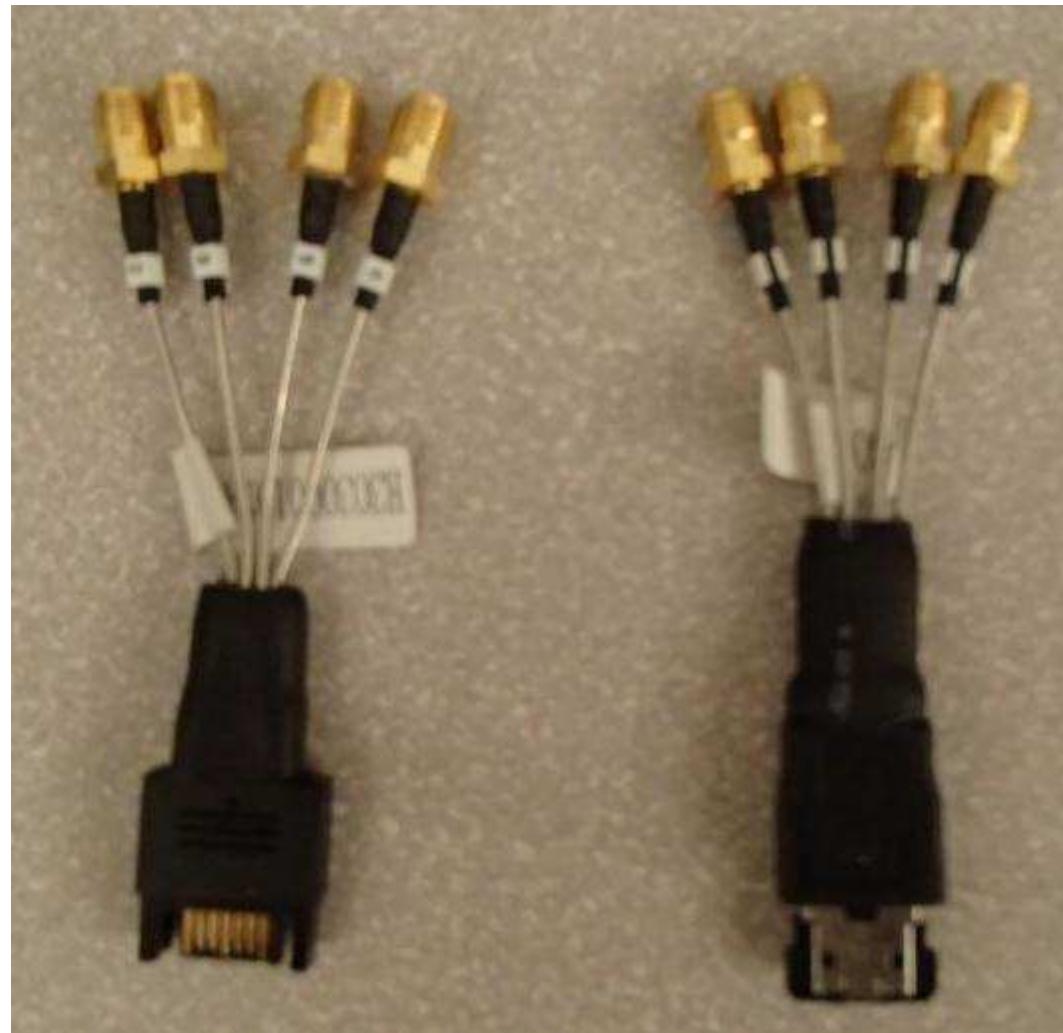

# Cable Fixtures – SATA

Bringing Measurement Insights for 75 Years

Agilent Technologies

# Cable Fixtures – HDMI

Unlocking Measurement Insights for 75 Years

Agilent Technologies

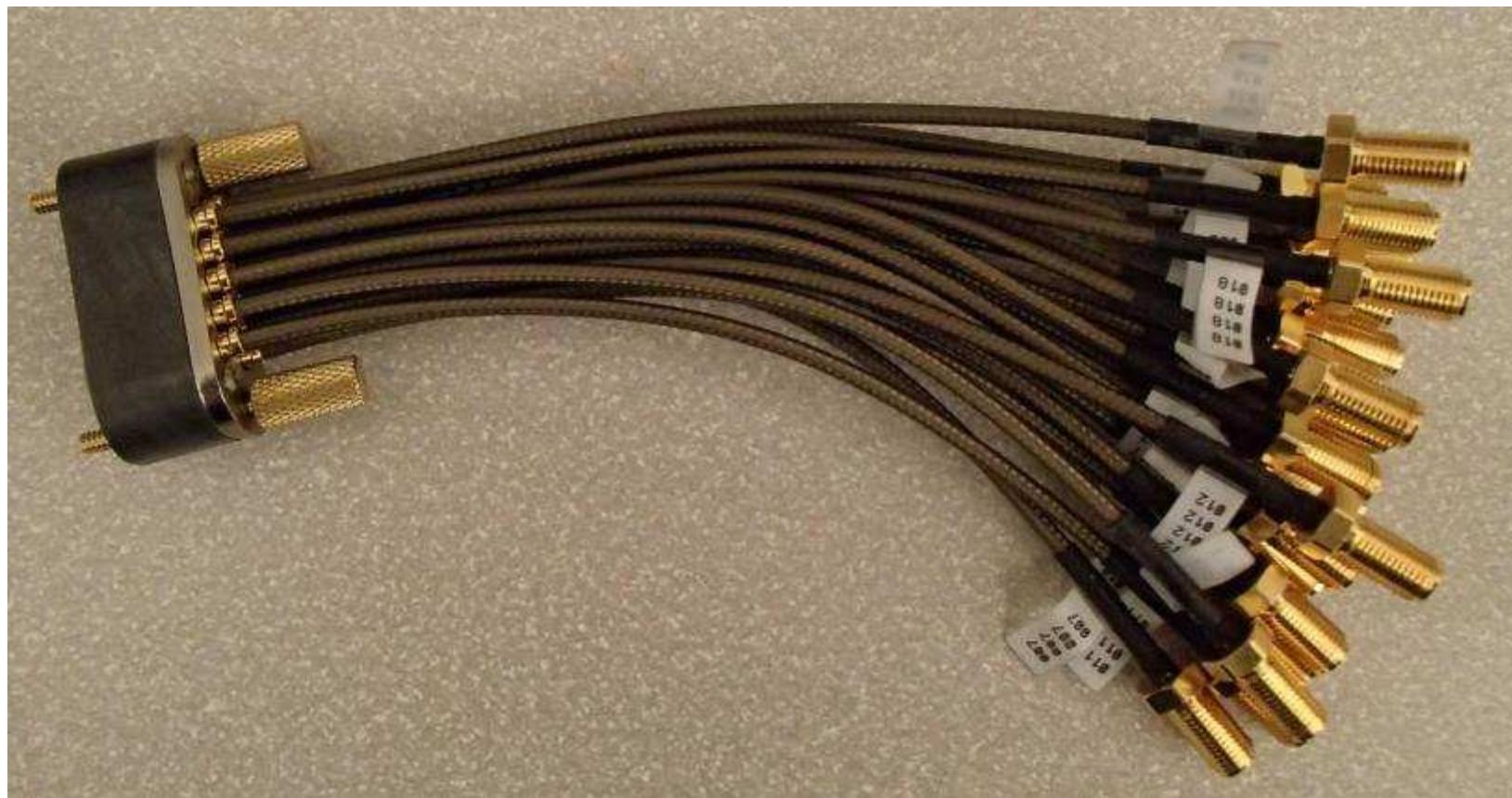

# Cable Fixtures – Bullseye Connector Fixture

Unlocking Measurement Insights for 75 Years

Agilent Technologies

# Demo: PLTS-AFR

Unlocking Measurement Insights for 75 Years

## One-Port Automatic Fixture Removal

Agilent Technologies