# DisplayPort Analysis Probe

For use with Agilent Logic Analyzers

FuturePlus® Systems

Power Tools for Bus Analysis

- Low cost DisplayPort analysis

- Supports Agilent 16900-series logic analyzers

- Includes protocol-decode software, probe configuration software, and automatic logic analyzer configuration software

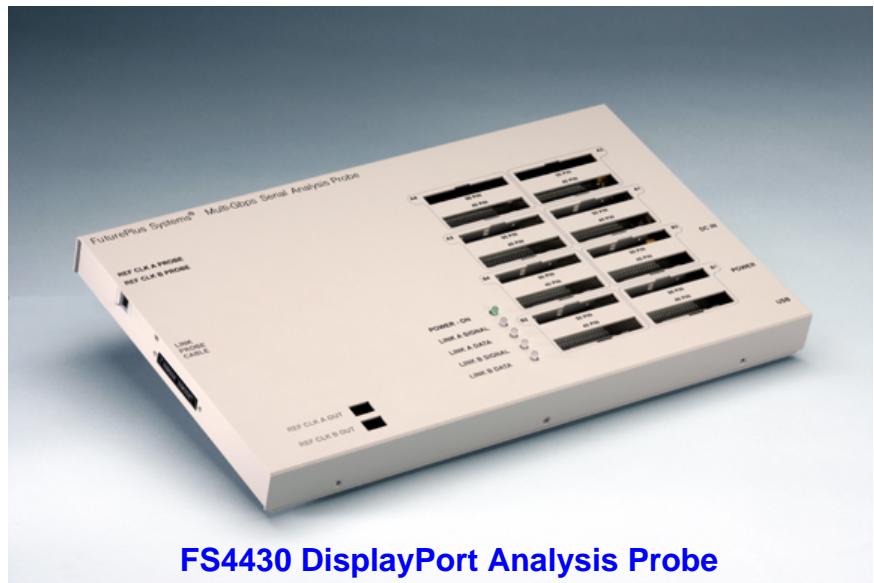

FS4430 DisplayPort Analysis Probe

## Key Features

- Supports X1, X2, and X4 DisplayPort

- Data acquisition up to 2.7 GT/s

- Probe Manager software controls FS4430 via USB link and defines complex protocol aware filters for use with the logic analyzer

- Quad state LED's display instant port activity status

- Powerful Protocol Decode software decodes and displays Main Link and Auxiliary channel activity on the Agilent logic analyzer

- Choose 1/2 size footprint, interposer, or flying leads adapter cables to connect FS4430 to your target system

- Probe Manager software allows instant lane reversal and polarity inversion

## Straightforward, Reliable DisplayPort Analysis

The FuturePlus FS4430 DisplayPort Analysis Probe provides a mechanical, electrical and software interface between an Agilent logic analyzer and the DisplayPort, a digital display interface standard supported by the Video Electronics Standards Association (VESA). The FS4430 is used to design and debug computer motherboards, monitors, home theater systems, and silicon chips incorporating DisplayPort technology.

## Helping you Design Tomorrow's Computers, Today

FuturePlus Systems is the technology leader in protocol analysis tools for the computer design industry. Our analysis probes and software help you monitor and verify complex activities on your advanced technology computer bus design. FuturePlus systems offerings include bus-analysis solutions for most popular computer buses. Visit [www.futureplus.com](http://www.futureplus.com) for more information.

Agilent Technologies

Channel Partner

# Main Link Native Agilent Protocol Decode

[Offline] Agilent Logic Analyzer - [...\Config Files\DisplayPortGoodDataRGB\_1.ala] - [Listing-1]

File Edit View Setup Tools Markers Run/Stop Listing Window Help

Horizontal blanking indicator

M1 to M2 = -785.738 us

Sample Number Time Protocol Decode Lane0 Lane1 Lane2 CLK L0S[5,4]

| Sample Number | Time  | Protocol Decode                      | Lane0 | Lane1 | Lane2 | CLK | L0S[5,4] |

|---------------|-------|--------------------------------------|-------|-------|-------|-----|----------|

| -2            | -8 ns | Dummy Data                           | 000   | 000   | 000   | X   | =        |

| -1            | -6 ns | Dummy Data                           | 000   | 000   | 000   | 0   |          |

| 0             | 0 ns  | MSA SS                               | 15C   | 15C   | 15C   | 0   |          |

| 1             | 4 ns  | MSA SS                               | 15C   | 15C   | 15C   |     |          |

| 2             | 6 ns  |                                      | 001   | 001   | 001   |     |          |

| 3             | 8 ns  |                                      | 0EF   | 0EF   | 0EF   |     |          |

| 4             | 12 ns | Mvid[23:0] #1 = 0x01EF3C             | 03C   | 03C   | 03C   |     |          |

| 4.1           |       | Mvid[23:0] #2 = 0x01EF3C             |       |       |       |     |          |

| 4.2           |       | Mvid[23:0] #3 = 0x01EF3C             |       |       |       |     |          |

| 4.3           |       | Mvid[23:0] #4 = 0x01EF3C             |       |       |       |     |          |

| 5             | 16 ns |                                      | 005   | 001   | 004   | 008 | 0        |

| 6             | 20 ns | Hor. Total(Pixels) = 001344          | 040   | 028   | 000   | 000 | 0        |

| 6.1           |       | Hor. Start(Pixels) = 000296          |       |       |       |     |          |

| 6.2           |       | Hor. Width(Pixels) = 001024          |       |       |       |     |          |

| 7             | 24 ns | Nvid = 0x080000                      | 003   | 000   | 000   |     |          |

| 8             | 28 ns | Ver. Total(Line Count) = 806         | 026   | 000   | 000   |     |          |

| 8.1           |       | Ver. Start (Line Count) = 35         |       |       |       |     |          |

| 8.2           |       | Ver. Height(Line Count) 768          |       |       |       |     |          |

| 8.3           |       | MISCO = 0x21                         |       |       |       |     |          |

| 8.4           |       | Link & Stream Ciks: Synchronous,     |       |       |       |     |          |

| 8.5           |       | Comp Format: RGB,                    |       |       |       |     |          |

| 8.6           |       | Dynamic Range: VES,                  |       |       |       |     |          |

| 8.7           |       | YCbCr Colorimetry: ITU-R BT601-5,    |       |       |       |     |          |

| 8.8           |       | Bit Depth Per Color: 8 Bits          |       |       |       |     |          |

| 9             | 32 ns | MISC1 = 0x0                          | 080   | 080   | 000   | 000 | 0        |

| 9.1           |       | # Of Interlaced Lines: Is Odd #,     |       |       |       |     |          |

| 9.2           |       | Stereo Video Attr: No Stereo Video   |       |       |       |     |          |

| 10            | 36 ns | Hor. Sync Polarity: Active Low Pulse | 088   | 006   | 000   | 000 | 0        |

| 10.1          |       | Hor. Sync Width(Pixels) = 16520      |       |       |       |     |          |

| 10.2          |       | Ver. Sync Polarity: Active Low Pulse |       |       |       |     |          |

| 10.3          |       | Ver. Sync Width(Pixels) = 16390      |       |       |       |     |          |

| 11            | 40 ns | MSA SE                               | 1FD   | 1FD   | 1FD   | 1FD | 0        |

| 12            | 44 ns | Dummy Data                           | 000   | 000   | 000   | 000 | 0        |

| 13            | 48 ns | Dummy Data                           | 000   | 000   | 000   | 000 | 0        |

| 14            | 52 ns | Dummy Data                           | 000   | 000   | 000   | 000 | 0        |

Overview Listing-1 Status... Offline

Symbols such as Blanking Start and Content Protection Scrambler Reset appear often in DisplayPort traffic

Horizontal blanking indicator

The tool gives an index number to each pixel and identifies its color value

These event codes are handy for triggering and logic analyzer post processing

# Aux Port Protocol Analysis

Offline] Agilent Logic Analyzer - [...\Sample Captures\AUX\_4\_with\_IA.ala] - [AUX Listing]

File Edit View Setup Tools Markers Run/Stop Listing Window Help

M1 to M2 = -5.2767 us

Aux Port is a bidirectional half duplex 1Mb/sec communication channel

| Time         | Sample Number | COMMAND                                             | Address | Command |

|--------------|---------------|-----------------------------------------------------|---------|---------|

|              |               |                                                     |         |         |

| 60.000 us    | -1            | Aux Read request, Address = 1 Byte Count = 1        | 0 0001  | Aux RE  |

|              | 0             | Aux ACK                                             |         |         |

| 130.000 us   | 0.1           | Max link rate= 2.7Gbps                              |         |         |

| 60.004 us    | 1             | Aux Read request, Address = 2 Byte Count            |         |         |

|              | 2             | Aux ACK                                             |         |         |

|              | 2.1           | Max lane count = 4 lanes                            |         |         |

|              | 2.2           | Enhanced Frame cap = 1                              |         |         |

| 24.296312 ms | 3             | Aux Read request, Address = 600 Byte Count = 1      |         |         |

| 62.000 us    | 4             | Aux ACK                                             |         |         |

|              | 4.1           | SET POWER                                           |         |         |

|              | 4.2           | Set Power sink ctrl(DPCD ver.1.1) = DO Normal opera |         |         |

| 80.000 us    | 5             | Aux Write request, Address = 600 Byte Count = 1     |         |         |

| 10.000 us    | 6             |                                                     |         |         |

|              | 6.1           | SET POWER                                           |         |         |

|              | 6.2           | Set Power sink ctrl(DPCD ver.1.1) = DO Normal opera |         |         |

| 52.004 us    | 7             | Aux ACK all Data bytes written                      | 0 0000  | Aux ACK |

| 138.000 us   | 8             | Aux Read request, Address = 206 Byte Count = 1      | 0 0005  | Aux RE  |

| 62.000 us    | 9             | Aux ACK                                             |         |         |

|              | 9.1           | VOLTAGE SWING AND EQUALIZATION SETTINGS             |         |         |

|              | 9.2           | Voltage Swing lane0 = Level 0                       |         |         |

|              | 9.3           | Pre-emphasis lane0 = Level 2                        |         |         |

|              | 9.4           | Voltage swing lane1 = Level 0                       |         |         |

|              | 9.5           | Pre-emphasis lane1 = Level 2                        |         |         |

| 80.000 us    | 10            | Aux Read request, Address = 207 Byte Count = 1      |         |         |

| 60.004 us    | 11            | Aux ACK                                             |         |         |

|              | 11.1          | VOLTAGE SWING AND EQUALIZATION SETTINGS             |         |         |

|              | 11.2          | Voltage Swing lane2 = Level 0                       |         |         |

|              | 11.3          | Pre-emphasis lane2 = Level 2                        |         |         |

|              | 11.4          | Voltage swing lane3 = Level 0                       |         |         |

The serial data is deserialized into a 48 bit wide bus and clocked to the logic analyzer. This wide bus makes triggering easy

Aux Port communicates configuration data between the monitor and the host PC

Diagnostic mode information is also communicated over the Aux Port

Overview    AUX Listing    AUX Waveform

Help, press F1    Status...    Offline] Agilent L...

start    1.00.0000    1.00.0000    InstallShield Express    DisplayPort - Micr...    [Offline] Agilent L...    12:07

## Ordering Information

**FS4430** – DisplayPort Analysis Probe for Main Link and Aux Port

**FS4432** - DisplayPort Analysis Probe for Aux Port

**One of the following is required to connect the FS4430 to the target system:**

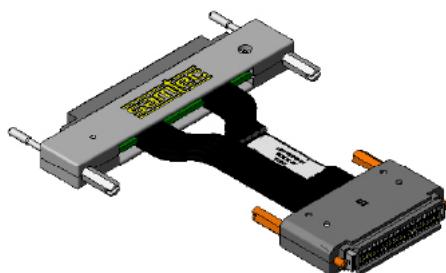

**FS1032** – ½ Midbus footprint Cable Adapter

**FS1036** – Flying Leads Cable Adapter

**FS1040** – Interposer Cable Adapter

**The FS4432 includes the connection to the target system.**

**Software included with the FS4430 and FS4432:**

Probe Manager, runs on a PC or the logic analyzer

Configuration files for the Agilent logic analyzer

Protocol Decoder software, runs on the Agilent logic analyzer

## Logic Analyzer Requirements

- 68 channels required for X1-X4 Main Link, 270 MHz state acquisition.

- 68 channels required for Aux Port, 100 KHz state acquisition.

- Both 40 and 90 pin logic analyzer pods are supported.

- The Agilent logic analyzer plugs directly into the FS4430.

**FS1032 ½ Size Midbus Cable Adapter**

**FS1036 Flying Leads Cable Adapter**

**FS1040 Interposer Cable Adapter**

**FuturePlus Systems Corporation**

P.O. Box 88155

Colorado Springs, CO 80908-8155

Tel: 719 278 3540

Fax: 603 471 2738

Website: [www.futureplus.com](http://www.futureplus.com)

**Represented By:**