MIPI D-PHY

Test Report

| Device Description | |

| Fixture Setup | Auto Load Switching |

| CTS Version | v1.00 |

| High Speed Data Rate(Mbps) | 800 |

| Test Session Details | |

| Infiniium SW Version | 04.10.0010 |

| Infiniium Model Number | DSO9104H |

| Infiniium Serial Number | MY52460107 |

| Application SW Version | 2.42 |

| Debug Mode Used | No |

| Compliance Limits (official) | MIPI D-PHY Test Limit v1.1 |

| Last Test Date | 2013-03-08 15:19:53 +08:00 |

| Test Statistics | |

| Failed | 5 |

| Passed | 25 |

| Total | 30 |

| Margin Thresholds | |

| Warning | < 2 % |

| Critical | < 0 % |

| Pass | # Failed | # Trials | Test Name | Actual Value | Margin | Pass Limits |

| 0 | 1 | 1.3.7 HS Data TX Static Common Mode Voltage(Vcmtx) | 171.13mV | 21.1 % | 150.00mV <= VALUE <= 250.00mV |

| 0 | 1 | 1.3.8 HS Data TX Vcmtx Mismatch | 2.80mV | 44.0 % | 0.00000V <= VALUE <= 5.00mV |

| 0 | 1 | 1.3.10 HS Data TX Common-Level Variations Above 450MHz (VCMTX(HF)) | 12.06mV | 19.6 % | VALUE < 15.00mV |

| 0 | 1 | 1.3.9 HS Data TX Common-Level Variations Between 50-450MHz (VCMTX(LF)) | 18.75mV | 25.0 % | VALUE < 25.00mV |

| 0 | 1 | 1.3.4 HS Data TX Differential Voltage(VOD0 Pulse) | -209.40mV | 46.6 % | -270.00mV <= VALUE <= -140.00mV |

| 0 | 1 | 1.3.4 HS Data TX Differential Voltage(VOD1 Pulse) | 145.15mV | 4.0 % | 140.00mV <= VALUE <= 270.00mV |

| 1 | 1 | 1.3.5 HS Data TX Differential Voltage Mismatch (Pulse) | 64.26mV | -359.0 % | 0.00000V <= VALUE <= 14.00mV |

| 0 | 1 | 1.3.6 HS Data TX Single Ended Output High Voltage(VOHHS Pulse) | 269.19mV | 25.2 % | VALUE <= 360.00mV |

| 0 | 1 | 1.3.11 HS Data TX 20%-80% Rise Time (tR) | 374ps | 0.4 % | 100ps <= VALUE <= ComplianceTranTimeMaxs |

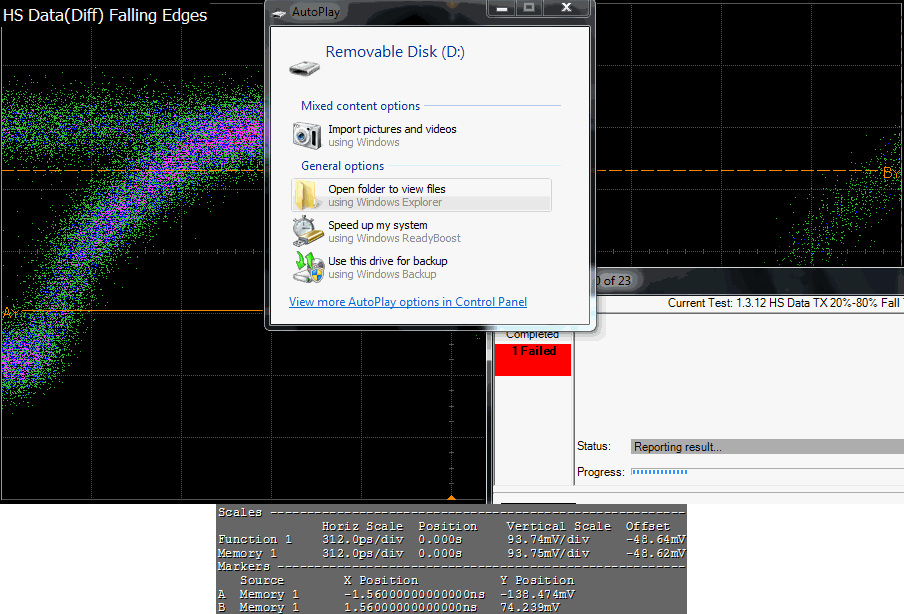

| 1 | 1 | 1.3.12 HS Data TX 20%-80% Fall Time (tF) | 386ps | -4.0 % | 100ps <= VALUE <= ComplianceTranTimeMaxs |

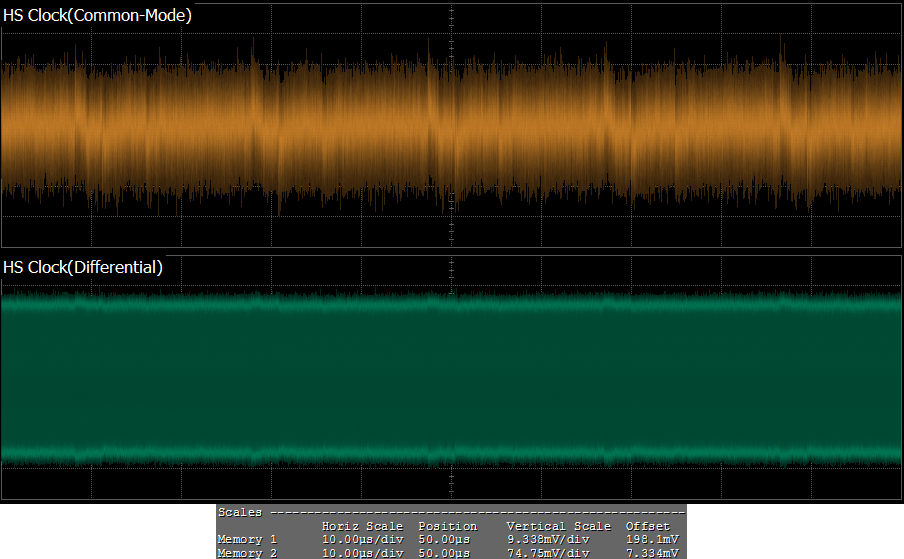

| 0 | 1 | 1.4.7 HS Clock TX Static Common Mode Voltage(Vcmtx) | 199.05mV | 49.1 % | 150.00mV <= VALUE <= 250.00mV |

| 0 | 1 | 1.4.8 HS Clock TX Vcmtx Mismatch | 580µV | 11.6 % | 0.00000V <= VALUE <= 5.00mV |

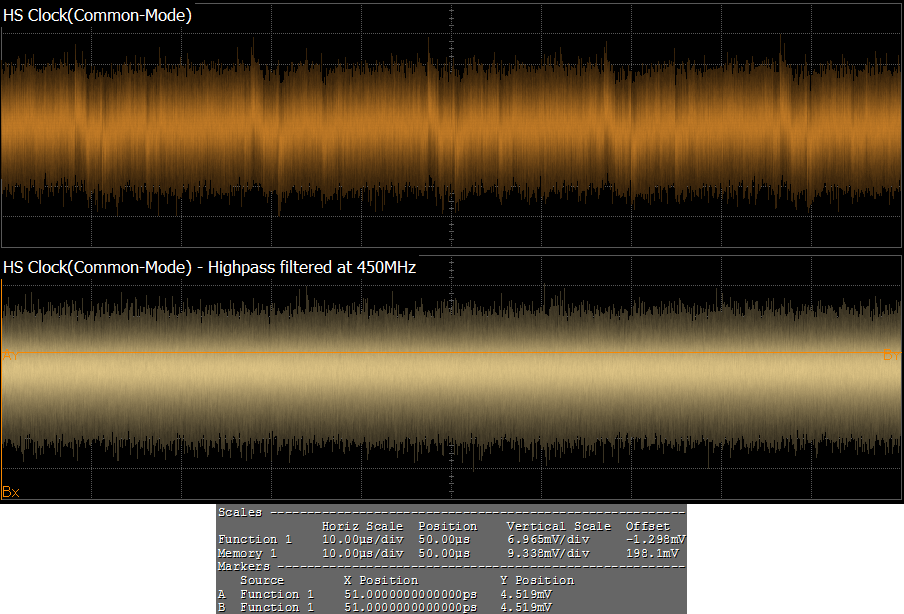

| 0 | 1 | 1.4.10 HS Clock TX Common-Level Variations Above 450MHz (VCMTX(HF)) | 4.52mV | 69.9 % | VALUE < 15.00mV |

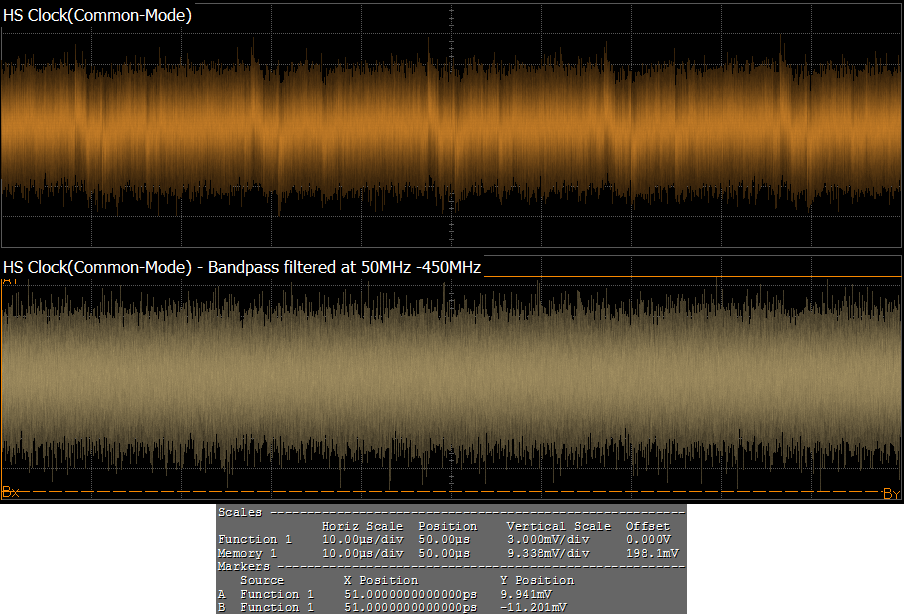

| 0 | 1 | 1.4.9 HS Clock TX Common-Level Variations Between 50-450MHz (VCMTX(LF)) | 11.20mV | 55.2 % | VALUE < 25.00mV |

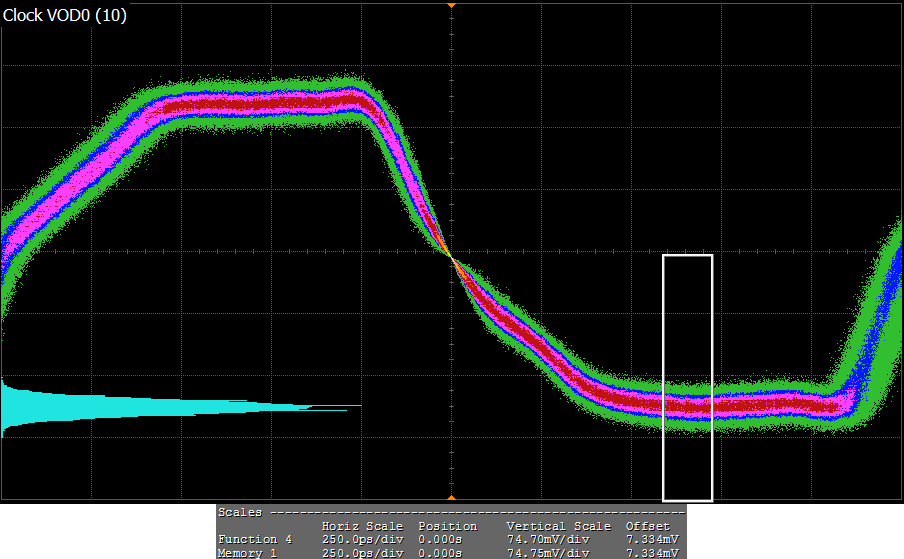

| 0 | 1 | 1.4.4 HS Clock TX Differential Voltage(VOD0 Pulse) | -180.33mV | 31.0 % | -270.00mV <= VALUE <= -140.00mV |

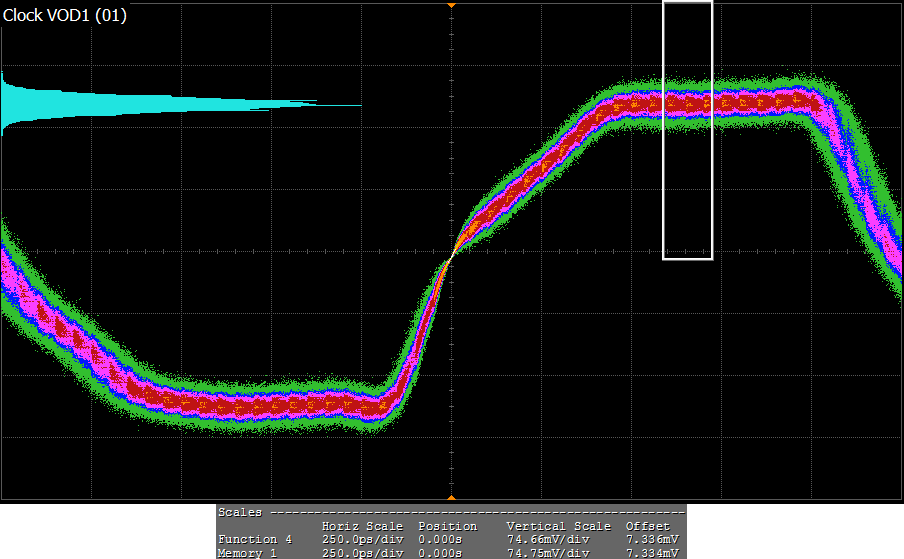

| 0 | 1 | 1.4.4 HS Clock TX Differential Voltage(VOD1 Pulse) | 184.37mV | 34.1 % | 140.00mV <= VALUE <= 270.00mV |

| 0 | 1 | 1.4.5 HS Clock TX Differential Voltage Mismatch (Pulse) | 4.04mV | 28.9 % | 0.00000V <= VALUE <= 14.00mV |

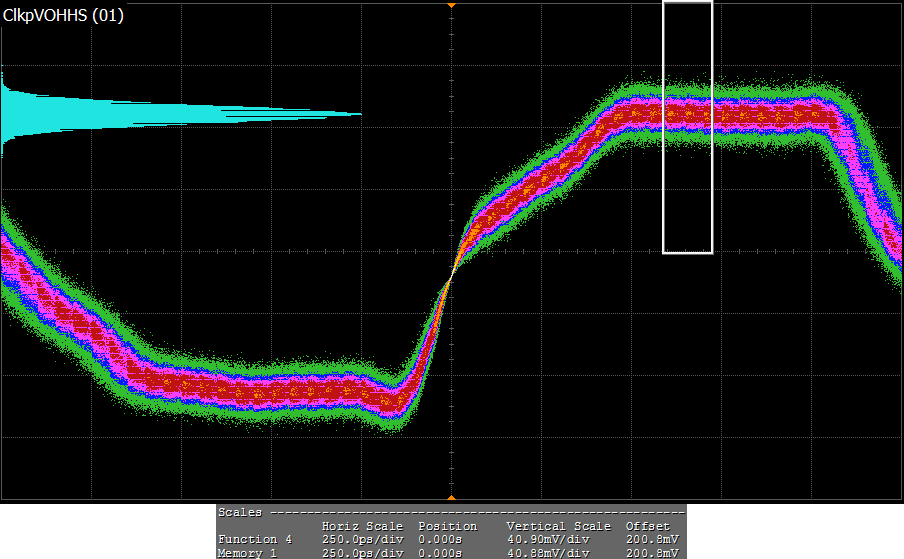

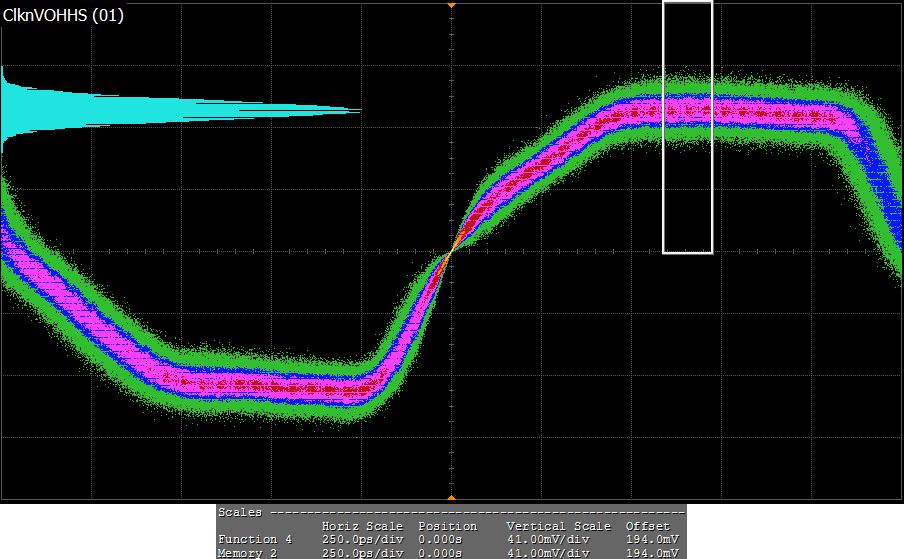

| 0 | 1 | 1.4.6 HS Clock TX Single Ended Output High Voltage(VOHHS Pulse) | 291.27mV | 19.1 % | VALUE <= 360.00mV |

| 0 | 1 | 1.4.11 HS Clock TX 20%-80% Rise Time (tR) | 358ps | 6.2 % | 100ps <= VALUE <= ComplianceTranTimeMaxs |

| 1 | 1 | 1.4.12 HS Clock TX 20%-80% Fall Time (tF) | 380ps | -1.8 % | 100ps <= VALUE <= ComplianceTranTimeMaxs |

| 0 | 1 | 1.3.1 LP Exit: DATA TLPX | 59.32ns | 18.6 % | VALUE >= 50.00ns |

| 0 | 1 | 1.3.3 LP Exit: DATA TX THS-PREPARE+THS-ZERO | 222.40ns | 41.2 % | VALUE >= ComplianceTimingMins |

| 0 | 1 | 1.3.13 HS Exit: DATA TX THS-TRAIL | 75.37ns | 16.0 % | VALUE >= ComplianceTimingMins |

| 0 | 1 | 1.3.14 HS Exit: DATA TX TREOT | 19.15ns | 45.3 % | VALUE <= 35.00ns |

| 0 | 1 | 1.3.15 HS Exit: DATA TX TEOT | 94.53ns | 21.2 % | VALUE <= ComplianceTimingMaxs |

| 0 | 1 | 1.3.16 HS Exit: DATA TX THS-EXIT | 2.88584µs | 279E+01 % | VALUE >= 100.00ns |

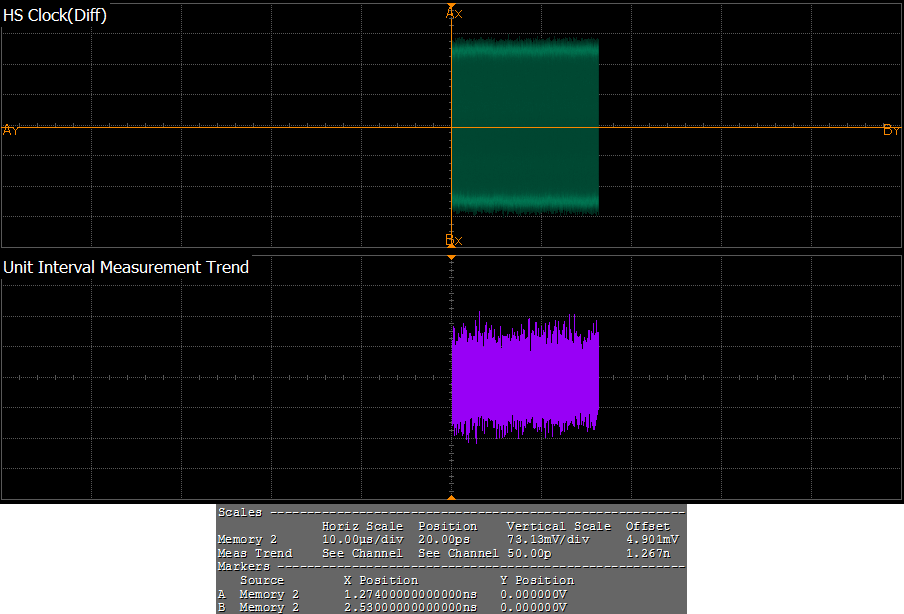

| 0 | 1 | 1.4.17 HS Clock Instantaneous (UIinst) | 1.255ns | 90.0 % | VALUE < 12.500ns |

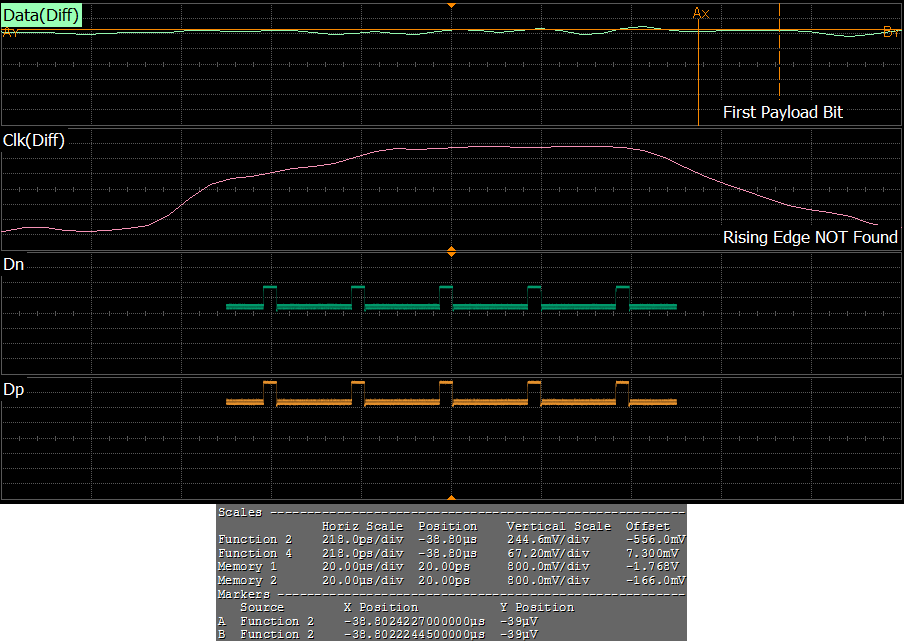

| 1 | 1 | 1.5.3 HS Clock Rising Edge Alignment to First Payload Bit | 1.000000000000 | -100.0 % | VALUE <= 500.000000000m |

| 1 | 1 | 1.5.4 Data-to-Clock Skew (TSKEW(TX)) | -322mUIinst | -57.3 % | ComplianceTranTimeMinUIinst <= VALUE <= ComplianceTranTimeMaxUIinst |

| 0 | 1 | 1.3.2 LP Exit: DATA TX THS-PREPARE | 66.58ns | 45.4 % | ComplianceTimingMins <= VALUE <= ComplianceTimingMaxs |

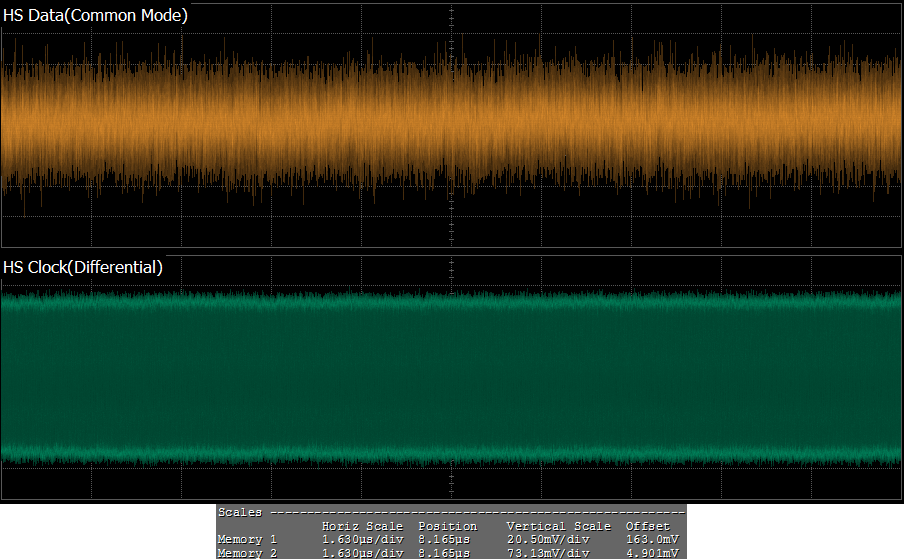

1.3.7 HS Data TX Static Common Mode Voltage(Vcmtx)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.3.7)

1.3.7 HS Data TX Static Common Mode Voltage(Vcmtx)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.3.7)

1.3.8 HS Data TX Vcmtx Mismatch

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.3.8)

1.3.8 HS Data TX Vcmtx Mismatch

Reference:

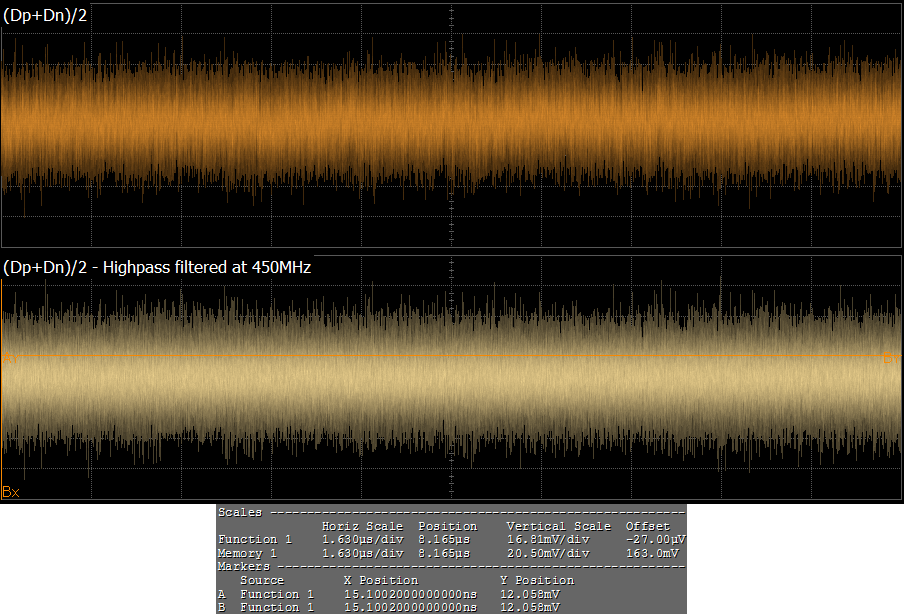

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.3.8) 1.3.10 HS Data TX Common-Level Variations Above 450MHz (VCMTX(HF))

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 17, CTS v1.00(Test 1.3.10)

1.3.10 HS Data TX Common-Level Variations Above 450MHz (VCMTX(HF))

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 17, CTS v1.00(Test 1.3.10)

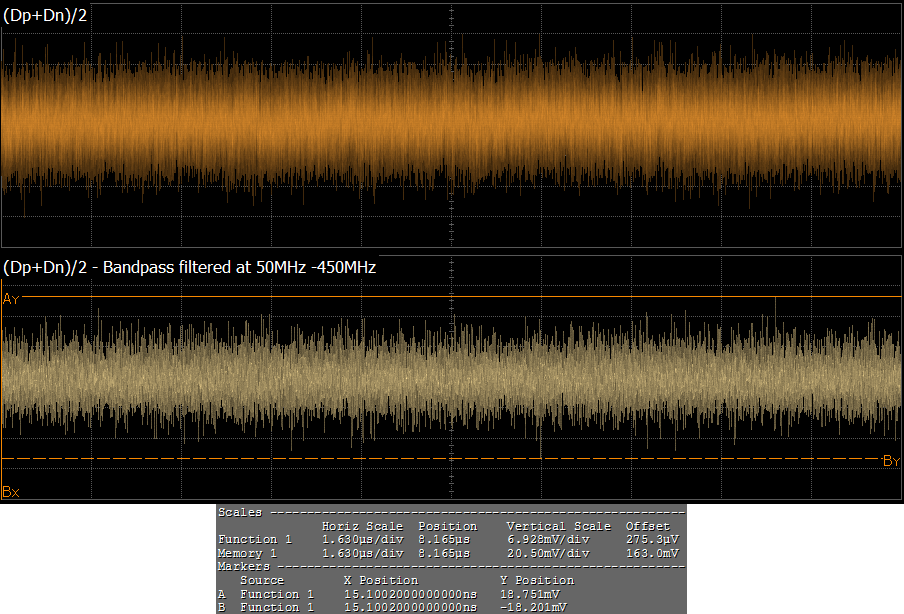

1.3.9 HS Data TX Common-Level Variations Between 50-450MHz (VCMTX(LF))

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 17, CTS v1.00(Test 1.3.9)

1.3.9 HS Data TX Common-Level Variations Between 50-450MHz (VCMTX(LF))

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 17, CTS v1.00(Test 1.3.9)

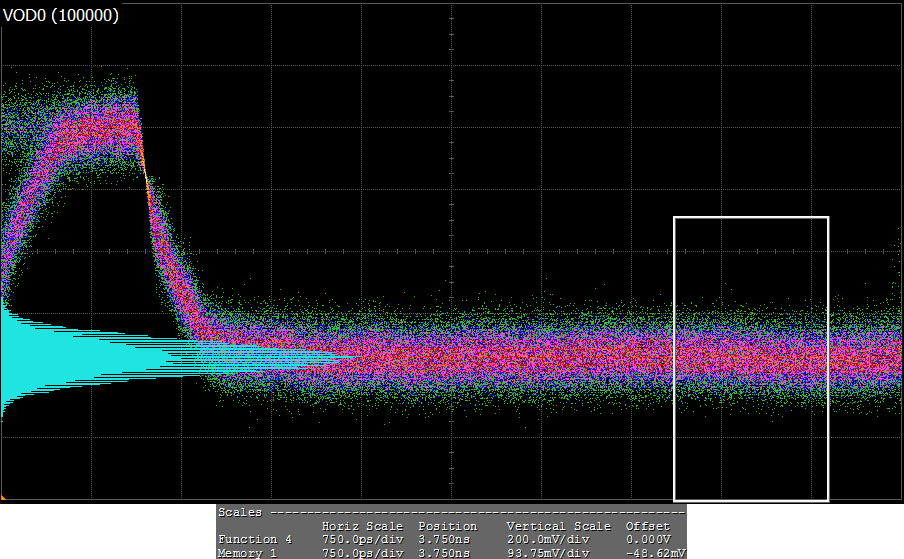

1.3.4 HS Data TX Differential Voltage(VOD0 Pulse)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.3.4)

1.3.4 HS Data TX Differential Voltage(VOD0 Pulse)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.3.4)

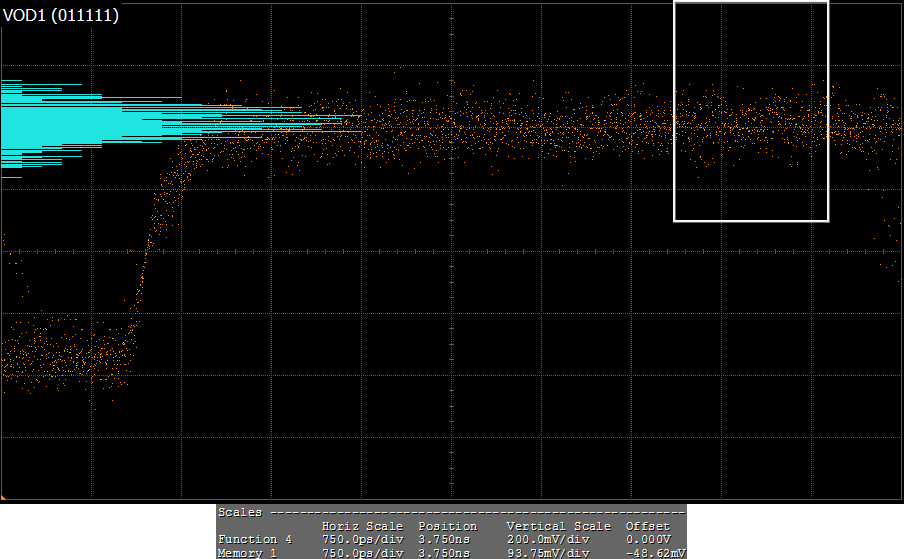

1.3.4 HS Data TX Differential Voltage(VOD1 Pulse)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.3.4)

1.3.4 HS Data TX Differential Voltage(VOD1 Pulse)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.3.4)

1.3.5 HS Data TX Differential Voltage Mismatch (Pulse)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.3.5)

1.3.5 HS Data TX Differential Voltage Mismatch (Pulse)

Reference:

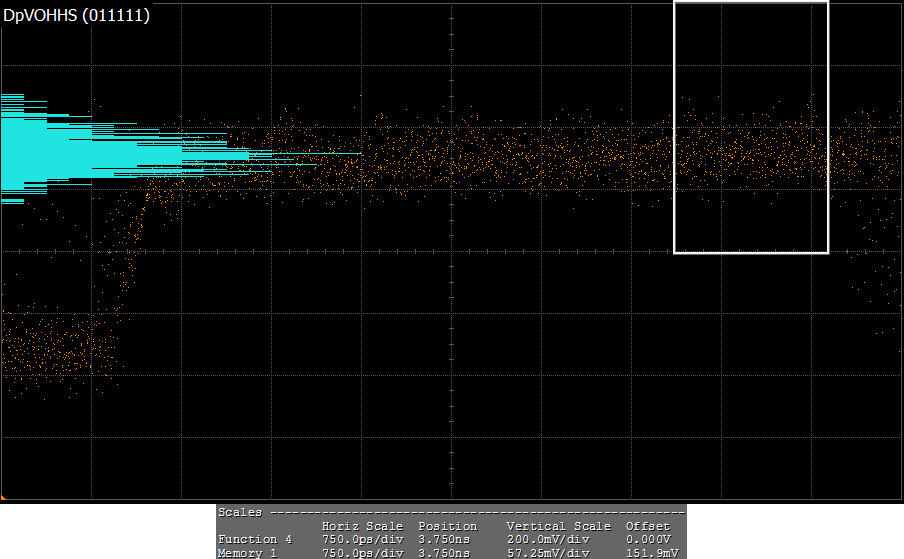

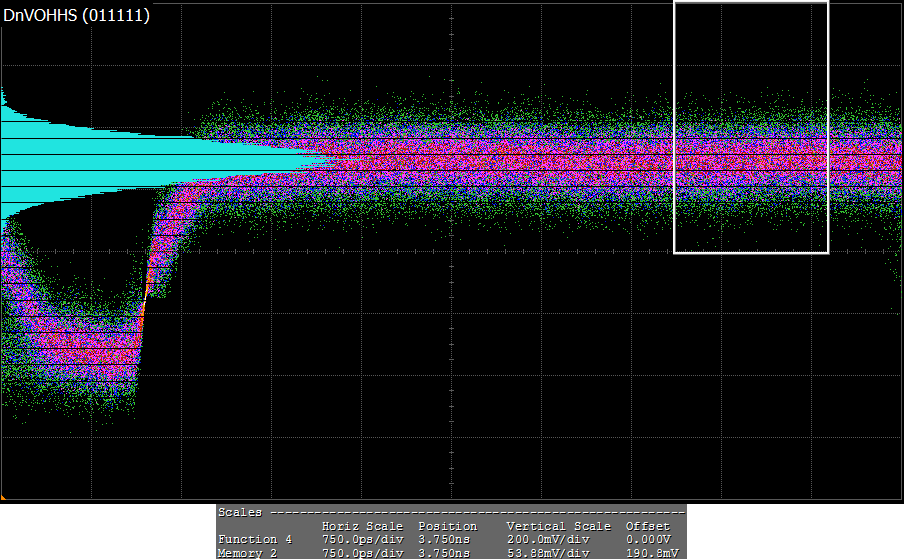

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.3.5) 1.3.6 HS Data TX Single Ended Output High Voltage(VOHHS Pulse)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.3.6)

1.3.6 HS Data TX Single Ended Output High Voltage(VOHHS Pulse)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.3.6)

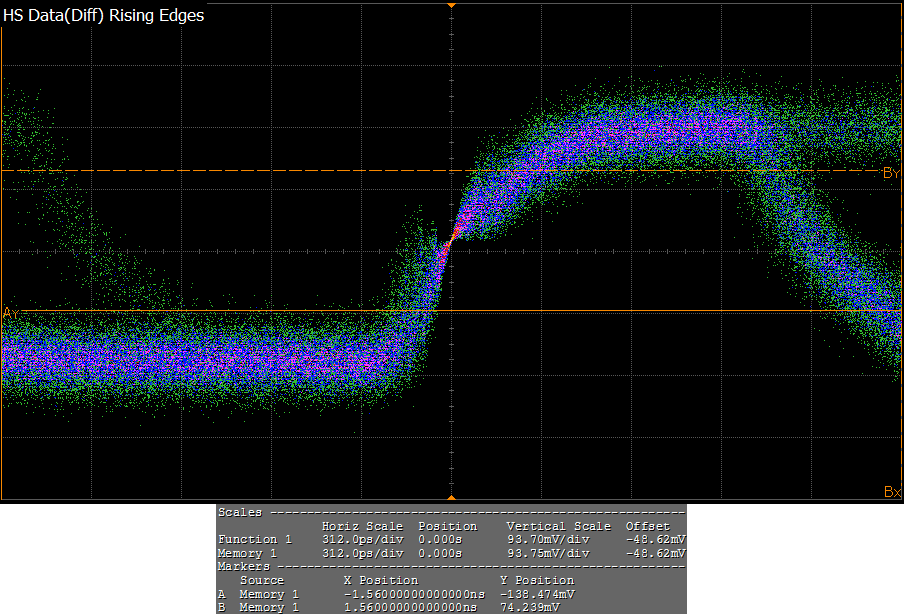

1.3.11 HS Data TX 20%-80% Rise Time (tR)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 17, CTS v1.00(Test 1.3.12)

1.3.11 HS Data TX 20%-80% Rise Time (tR)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 17, CTS v1.00(Test 1.3.12)

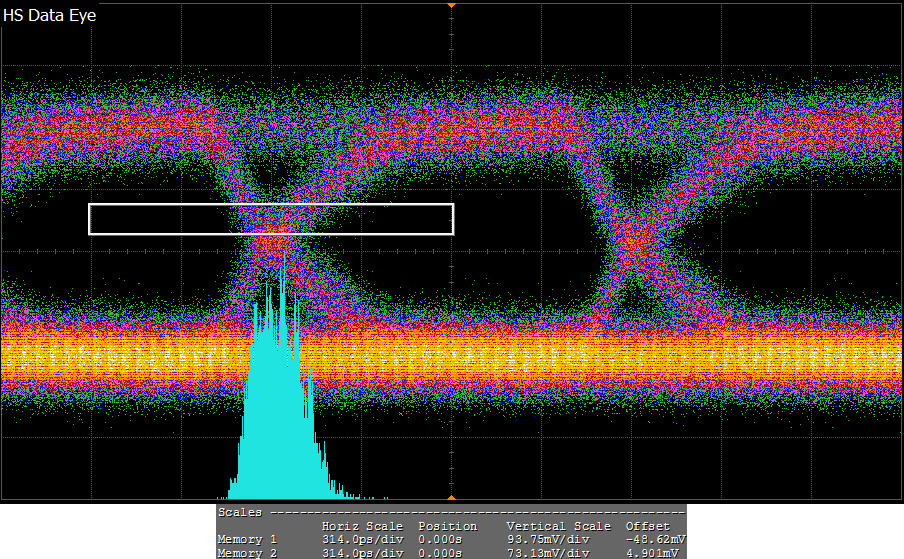

1.3.12 HS Data TX 20%-80% Fall Time (tF)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 17, CTS v1.00(Test 1.3.12)

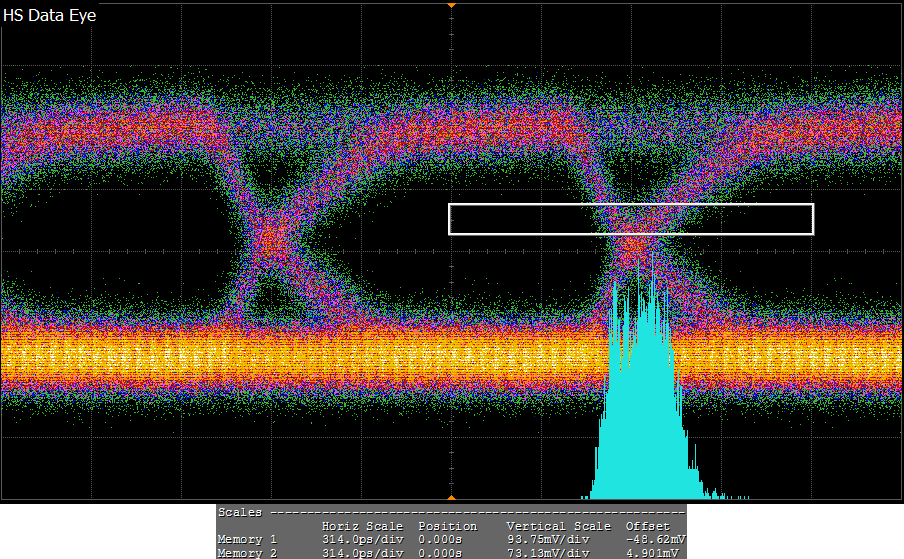

1.3.12 HS Data TX 20%-80% Fall Time (tF)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 17, CTS v1.00(Test 1.3.12)

1.4.7 HS Clock TX Static Common Mode Voltage(Vcmtx)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.4.7)

1.4.7 HS Clock TX Static Common Mode Voltage(Vcmtx)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.4.7)

1.4.8 HS Clock TX Vcmtx Mismatch

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.4.8)

1.4.8 HS Clock TX Vcmtx Mismatch

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.4.8) 1.4.10 HS Clock TX Common-Level Variations Above 450MHz (VCMTX(HF))

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 17, CTS v1.00(Test 1.4.10)

1.4.10 HS Clock TX Common-Level Variations Above 450MHz (VCMTX(HF))

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 17, CTS v1.00(Test 1.4.10)

1.4.9 HS Clock TX Common-Level Variations Between 50-450MHz (VCMTX(LF))

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 17, CTS v1.00(Test 1.4.9)

1.4.9 HS Clock TX Common-Level Variations Between 50-450MHz (VCMTX(LF))

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 17, CTS v1.00(Test 1.4.9)

1.4.4 HS Clock TX Differential Voltage(VOD0 Pulse)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.4.4)

1.4.4 HS Clock TX Differential Voltage(VOD0 Pulse)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.4.4)

1.4.4 HS Clock TX Differential Voltage(VOD1 Pulse)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.4.4)

1.4.4 HS Clock TX Differential Voltage(VOD1 Pulse)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.4.4)

1.4.5 HS Clock TX Differential Voltage Mismatch (Pulse)

Reference:

D-PHY Specification v1.01 Section 9.1.1 Table 16, CTS v1.00(Test 1.4.5)

1.4.5 HS Clock TX Differential Voltage Mismatch (Pulse)

Reference:

D-PHY Specification v1.01 Section 9.1.1 Table 16, CTS v1.00(Test 1.4.5) 1.4.6 HS Clock TX Single Ended Output High Voltage(VOHHS Pulse)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.4.6)

1.4.6 HS Clock TX Single Ended Output High Voltage(VOHHS Pulse)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 16, CTS v1.00(Test 1.4.6)

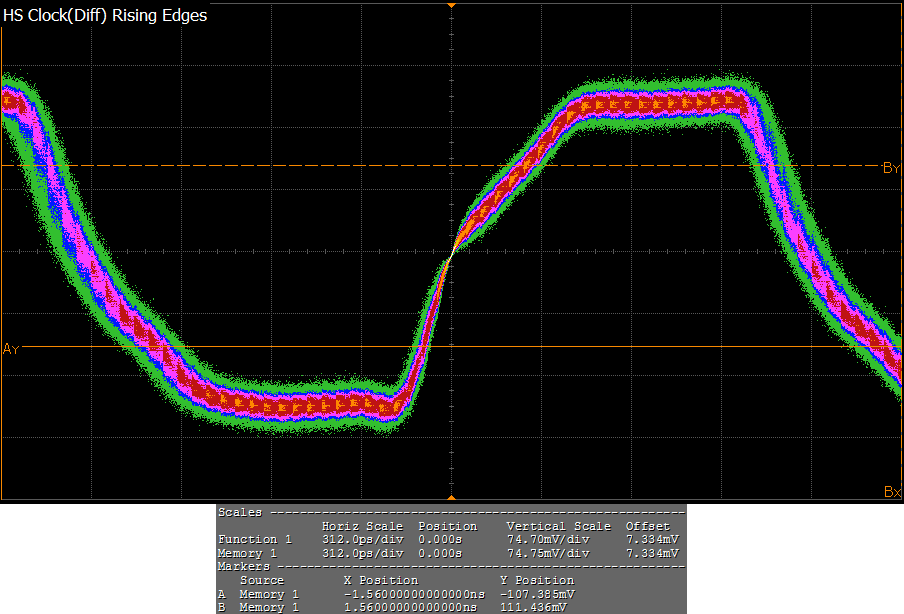

1.4.11 HS Clock TX 20%-80% Rise Time (tR)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 17, CTS v1.00(Test 1.4.11)

1.4.11 HS Clock TX 20%-80% Rise Time (tR)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 17, CTS v1.00(Test 1.4.11)

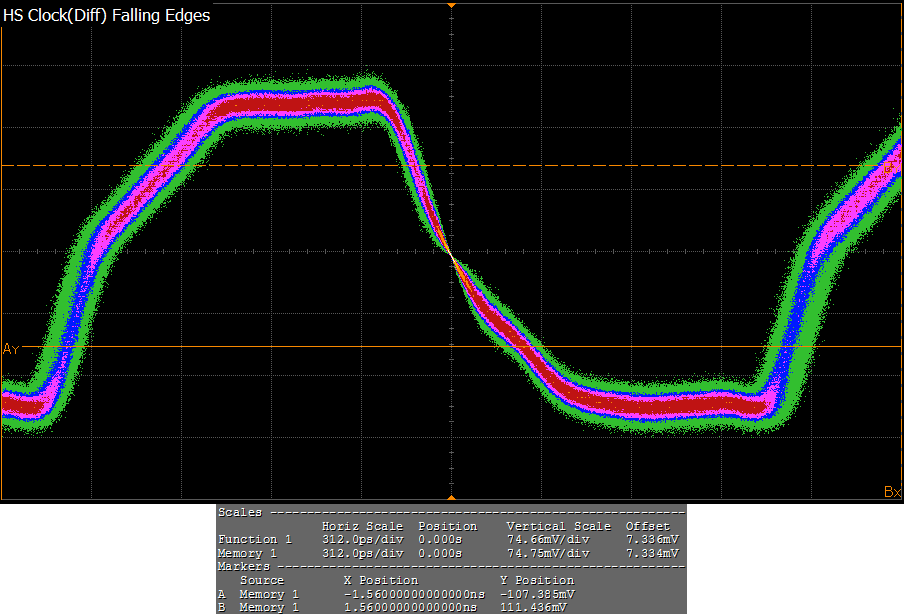

1.4.12 HS Clock TX 20%-80% Fall Time (tF)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 17, CTS v1.00(Test 1.4.12)

1.4.12 HS Clock TX 20%-80% Fall Time (tF)

Reference:

D-PHY Specification v1.1 Section 9.1.1 Table 17, CTS v1.00(Test 1.4.12)

1.3.1 LP Exit: DATA TLPX

Reference:

D-PHY Specification v1.1 Section 6.9 Table 14, CTS v1.00(Test 1.3.1)

1.3.1 LP Exit: DATA TLPX

Reference:

D-PHY Specification v1.1 Section 6.9 Table 14, CTS v1.00(Test 1.3.1)

1.3.3 LP Exit: DATA TX THS-PREPARE+THS-ZERO

Reference:

D-PHY Specification v1.1 Section 6.9 Table 14, CTS v1.00(Test 1.3.3)

1.3.3 LP Exit: DATA TX THS-PREPARE+THS-ZERO

Reference:

D-PHY Specification v1.1 Section 6.9 Table 14, CTS v1.00(Test 1.3.3)

1.3.13 HS Exit: DATA TX THS-TRAIL

Reference:

D-PHY Specification v1.1 Section 6.9 Table 14, CTS v1.00(Test 1.3.13)

1.3.13 HS Exit: DATA TX THS-TRAIL

Reference:

D-PHY Specification v1.1 Section 6.9 Table 14, CTS v1.00(Test 1.3.13)

1.3.14 HS Exit: DATA TX TREOT

Reference:

D-PHY Specification v1.1 Section 9.1.2 Table 19, CTS v1.00(Test 1.3.14)

1.3.14 HS Exit: DATA TX TREOT

Reference:

D-PHY Specification v1.1 Section 9.1.2 Table 19, CTS v1.00(Test 1.3.14)

1.3.15 HS Exit: DATA TX TEOT

Reference:

D-PHY Specification v1.1 Section 6.9 Table 14, CTS v1.00(Test 1.3.15)

1.3.15 HS Exit: DATA TX TEOT

Reference:

D-PHY Specification v1.1 Section 6.9 Table 14, CTS v1.00(Test 1.3.15)

1.3.16 HS Exit: DATA TX THS-EXIT

Reference:

D-PHY Specification v1.6 Section 6.9 Table 14, CTS v1.00(Test 1.3.16)

1.3.16 HS Exit: DATA TX THS-EXIT

Reference:

D-PHY Specification v1.6 Section 6.9 Table 14, CTS v1.00(Test 1.3.16)

1.4.17 HS Clock Instantaneous (UIinst)

Reference:

D-PHY Specification v1.1 Section 10.1 Table 26, CTS v1.00(Test 1.4.17)

1.4.17 HS Clock Instantaneous (UIinst)

Reference:

D-PHY Specification v1.1 Section 10.1 Table 26, CTS v1.00(Test 1.4.17)

1.5.3 HS Clock Rising Edge Alignment to First Payload Bit

Reference:

D-PHY Specification v1.1 Section 10.2, CTS v1.00(Test 1.5.3)

1.5.3 HS Clock Rising Edge Alignment to First Payload Bit

Reference:

D-PHY Specification v1.1 Section 10.2, CTS v1.00(Test 1.5.3)

1.5.4 Data-to-Clock Skew (TSKEW(TX))

Reference:

D-PHY Specification v1.1 Section 10.2.1 Table 27, CTS v1.00(Test 1.5.4)

1.5.4 Data-to-Clock Skew (TSKEW(TX))

Reference:

D-PHY Specification v1.1 Section 10.2.1 Table 27, CTS v1.00(Test 1.5.4)

1.3.2 LP Exit: DATA TX THS-PREPARE

Reference:

D-PHY Specification v1.1 Section 6.9 Table 14, CTS v1.00(Test 1.3.2)

1.3.2 LP Exit: DATA TX THS-PREPARE

Reference:

D-PHY Specification v1.1 Section 6.9 Table 14, CTS v1.00(Test 1.3.2)