# Dakar F5 Carrier Board User Guide

Document Number 500-00354

Revision 2.11

October 1998

| Dakar User Guide Customer Feedback                                                                                                                                              | Spectrum Signal Processing        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|                                                                                                                                                                                 |                                   |

|                                                                                                                                                                                 |                                   |

|                                                                                                                                                                                 |                                   |

|                                                                                                                                                                                 |                                   |

|                                                                                                                                                                                 |                                   |

|                                                                                                                                                                                 |                                   |

|                                                                                                                                                                                 |                                   |

|                                                                                                                                                                                 |                                   |

|                                                                                                                                                                                 |                                   |

|                                                                                                                                                                                 |                                   |

|                                                                                                                                                                                 |                                   |

|                                                                                                                                                                                 |                                   |

|                                                                                                                                                                                 |                                   |

|                                                                                                                                                                                 |                                   |

|                                                                                                                                                                                 |                                   |

|                                                                                                                                                                                 |                                   |

| Copyright © 1998 Spectrum Signal Processing Inc. All rights reserved, including those to reproduce this document or parts thereof in any form w Spectrum Signal Processing Inc. | ithout permission in writing from |

| All trademarks are registered trademarks of their respective owners.  Spectrum Signal Processing reserves the right to change any of the information contained he               | erein without notice.             |

|                                                                                                                                                                                 |                                   |

# **Customer Feedback**

At Spectrum, we recognize that product documentation that is both accurate and easy to use is important in aiding you in your new product development. We appreciate hearing your comments on how our product's documentation could be improved.

If you wish to comment on any Spectrum documentation then please fax or e-mail a

completed copy of this page to us. Full Name of Document: Document Number: \_\_\_\_\_\_ Version Number: \_\_\_\_\_ If you have found a technical inaccuracy please describe it here: If you particularly liked or disliked an aspect of the manual then please describe it here: It may be helpful for us to call you to discuss your comments. If this would be acceptable please provide the following details: Name: \_\_\_\_\_\_ Telephone #: \_\_\_\_\_ Organization: Thank you for your time, Spectrum Signal Processing Documentation Group Fax: (604) 421-1764

documentation@spectrumsignal.com

Email:

# Contacting Spectrum...

Spectrum's team of dedicated Applications Engineers are available to provide technical support to you for this product. Our office hours are Monday to Friday, 8:00 AM to 5:00 PM, Pacific Standard Time.

Telephone 1-800-663-8986 or (604) 421-5422

Fax (604) 421-1764

Email support@spectrumsignal.com

Internet http://www.spectrumsignal.com

When you contact us, please have the following information on hand:

- A concise description of the problem

- The name of all Spectrum hardware components

- The name and version number of all Spectrum software components

- The minimum amount of code that demonstrates the problem

- The version number of all software packages, including compilers and operating systems

### **Preface**

Spectrum Signal Processing offers a complete line of DSP hardware, software and I/O products for the DSP Systems market based on the latest DSP microprocessors, bus interface standards, I/O standards and software development environments. By delivering quality products, and DSP expertise tailored to specific application requirements, Spectrum can consistently exceed the expectations of our customers. We pride ourselves in providing unrivaled pre and post sales support from our team of application engineers. Spectrum has excellent relationships with third party vendors which allows us to provide our customers with a more diverse and top quality product offering.

Spectrum achieved ISO 9001 quality certification in 1994.

As Spectrum's hardware products are static sensitive, please take precautions when handling and make sure they are protected against static discharge.

# **Table of Contents**

| 1 Introd | duction                                                | 1  |

|----------|--------------------------------------------------------|----|

|          | 1.1. Purpose of This Manual                            | 1  |

|          | 1.2. Reference Documents                               | 1  |

|          | 1.3. Conventions Used in This Manual                   | 1  |

| 2 Hard   | ware Overview                                          | 3  |

|          | 2.1. Features of the F5 Carrier Board                  | 3  |

|          | 2.1.1. Scaleable Modular Architecture                  | 4  |

|          | 2.1.2. PCI Interface                                   | 4  |

|          | 2.1.3. TMS320C4x Communication Port Interfaces         | 4  |

|          | 2.1.4. Shared Memory Resources                         | 5  |

|          | 2.1.5. Node A Memory Resources                         | 5  |

|          | 2.1.6. DSP~LINK3 Interface                             | 5  |

|          | 2.1.7. JTAG Interface Debug Support                    | 5  |

|          | 2.2. Memory Configurations Available                   | 6  |

|          | 2.3. Bus Architecture                                  | 6  |

|          | 2.4. 'C4x Communication Port Architecture              | 8  |

|          | 2.5. Resetting the F5 Carrier Board                    | 8  |

|          | 2.5.1. Power Up Reset                                  | 9  |

|          | 2.5.2. PCI Software Reset                              | 9  |

|          | 2.5.3. JTAG Reset                                      | 10 |

|          | 2.6. Booting the F5 Board                              | 10 |

| 3 Softw  | vare Overview                                          | 11 |

|          | 3.1. Hardware and Software Requirements                | 12 |

|          | 3.2. F5 Host Program Structure                         | 13 |

|          | 3.2.1. F5 Windows Host Application Libraries           | 13 |

|          | 3.2.2. F5 Windows 95 and NT Device Drivers             | 14 |

|          | 3.3. F5 C4x Application Library                        | 14 |

|          | 3.4. Data Type Definitions                             |    |

|          | 3.5. Calling Conventions for Windows 95 and Windows NT | 15 |

|          | 3.6. Example Programs                                  | 15 |

|          | 3.7. Manuals Provided With the F5 SDK                  | 15 |

|          | 3.8. Utilities Provided With the F5 SDK                | 16 |

| 4 Hardware and Software Installation                                   | 17     |

|------------------------------------------------------------------------|--------|

| 4.1. Configuring the F5 Carrier Board                                  | 17     |

| 4.2. Module Installation                                               | 18     |

| 4.2.1. Installing DSP~LINK3 Modules                                    |        |

| 4.2.2. Installing TIM-40 Modules                                       |        |

| 4.3. Installation into PCI Slot and Cabling                            | 19     |

| 4.4. Windows NT Installation Notes                                     | 20     |

| 4.5. Windows 95 Installation Notes                                     | 20     |

| 4.6. Installing Multiple F5 Carrier Boards                             | 21     |

| 4.7. Installing the Software Development Kit (Windows NT)              | 22     |

| 4.8. Installing the Software Development Kit (Windows 95)              | 23     |

| 4.9. Directory Contents After Installation of the SDK                  | 24     |

| 4.10. Installing Toolbox                                               | 26     |

| 4.11. Verifying the Software Development Kit Installation              | 26     |

| 4.12. Uninstalling the Software Development Kit (Windows NT)           | 27     |

| 4.13. Uninstalling the Software Development Kit (Windows 95)           | 27     |

| 5 JTAG Debugging Software                                              |        |

| 5.1. Using Code Composer                                               | 30     |

| 5.1.1. Setup for Back-plane Debugging                                  |        |

| 5.1.2. Setup for Debugging with the Mountain-510 Emulator              |        |

| 5.1.3. Editing the Sample GEL File                                     |        |

| 5.1.4. Loading and Running Files                                       |        |

| 6 Development of Host Applications                                     | <br>35 |

| 6.1. Architectural Overview                                            | 35     |

| 6.2. Calling Host Functions                                            |        |

| 6.2.1. Obtaining Error Information                                     |        |

| 6.3. Including F5 ALIB Functionality                                   |        |

| 6.4. Defining your System's Hardware Configuration                     |        |

| 6.5. Changing your System's Hardware Configuration                     |        |

| 6.5.1. Changing an F5 Board ID                                         | 40     |

| 6.6. Defining the DSP Code to Download                                 | 40     |

| 6.6.1. Load Definition File (LDF) Example                              | 40     |

| 6.7. Defining your System's Configuration for a Standalone Application |        |

| 6.7.1. Generating a Resource Definition File (RDF)                     |        |

| 6.7.2. Resource Definition File (RDF) Example                          |        |

| 6.8. Using Handles to Access Systems and Resources                     |        |

| 6.9. Viewing Debug Messages (Windows 95)                               | 43     |

| 7 Host Software Functions                                       | 45 |

|-----------------------------------------------------------------|----|

| F5_AllocHostMem (Windows 95)                                    | 46 |

| F5_AllocHostMem (Windows NT)                                    | 47 |

| F5_Control                                                      | 48 |

| F5_ErrorMessage                                                 | 51 |

| F5_FreeHostMem (Windows 95)                                     | 52 |

| F5_FreeHostMem (Windows NT)                                     | 53 |

| F5_GetHandle                                                    | 54 |

| F5_InstCallback                                                 | 55 |

| F5_InterruptProc                                                | 59 |

| F5_Read                                                         | 60 |

| F5_SystemClose                                                  | 62 |

| F5_SystemLoad                                                   | 63 |

| F5_SystemOpen                                                   | 65 |

| F5_Write                                                        | 67 |

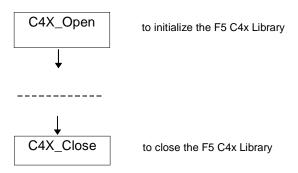

| 8 Development of DSP Applications                               | 69 |

| 8.1. Calling F5 ALIB_C4x Functions                              | 69 |

| 8.2. Including F5 ALIB_C4x Functionality                        |    |

| 8.3. Transferring Data Between DSPs Shared SRAM and the PCI Bus |    |

| 8.4. Running F5 DSP Code via a Debugger                         |    |

| 8.4.1. board.cfg                                                |    |

| 8.4.2. init.cmd                                                 |    |

| 8.4.3. Testing the Software Setup                               |    |

| 9 DSP Software Functions                                        |    |

| C4X_Close                                                       | 76 |

| C4X Control                                                     |    |

| C4X_Open                                                        |    |

| C4X Read                                                        |    |

| C4X_Write                                                       |    |

| 10 Example Programs                                             | 85 |

| 10.1. Purpose of Each Program                                   | 85 |

| 10.2. How to Run the Example Programs                           |    |

| 10.3. Screen Displays of the Example Programs                   |    |

| 10.4. Verifying the Device Driver and Host Library Installation |    |

| 10.5. Tips and Troubleshooting                                  |    |

| 10.6. How to Rebuild the Host Library                           |    |

| 10.7. How to Rebuild the Example Programs                       |    |

|                                                                 |    |

| Appendix A: Status Codes                                    | 95  |

|-------------------------------------------------------------|-----|

| Appendix B: Sample Linker Command File                      | 99  |

| Appendix C: System Definition File: Description and Example | 101 |

| Appendix D: Definitions and Acronyms                        | 109 |

| Index                                                       | 111 |

#### List of Figures

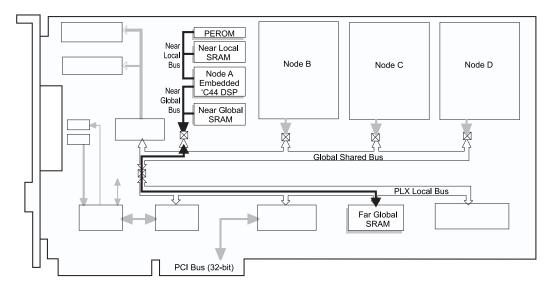

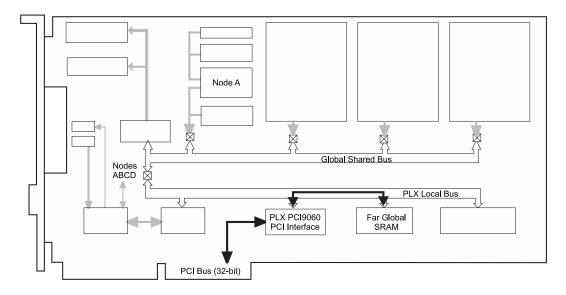

| Figure 1 F5 Block Diagram                                  | 6  |

|------------------------------------------------------------|----|

| Figure 2 F5 COMM Port Architecture                         | 8  |

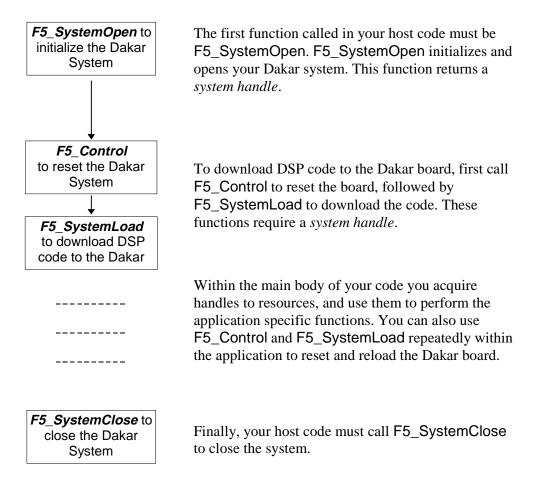

| Figure 3 F5 Host Program Flow                              | 13 |

| Figure 4 F5 Connector and Jumper Locations                 | 17 |

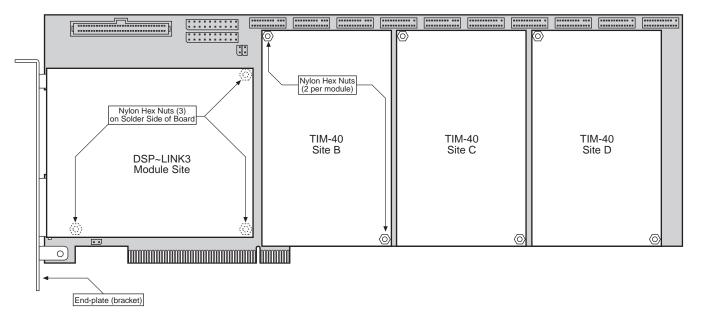

| Figure 5 F5 Module Locations                               | 18 |

| Figure 6 JTAG Debugging Configurations                     | 29 |

| Figure 7 Dakar Host Software Architecture                  | 36 |

| Figure 8 Host Program Flow                                 | 37 |

| Figure 9 Order of DSP Function Calls                       | 69 |

| Figure 10 Near Memory /Far Global SRAM Transfers           | 70 |

| Figure 11 PCI/Far Global SRAM Transfers                    | 71 |

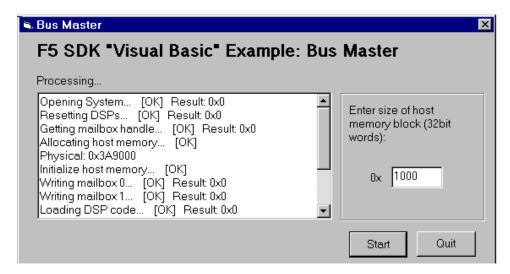

| Figure 12 Screen Display of the "busmastr" Example Program | 87 |

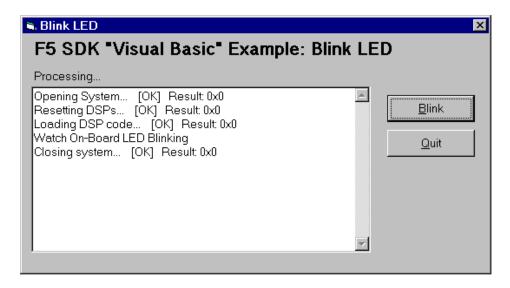

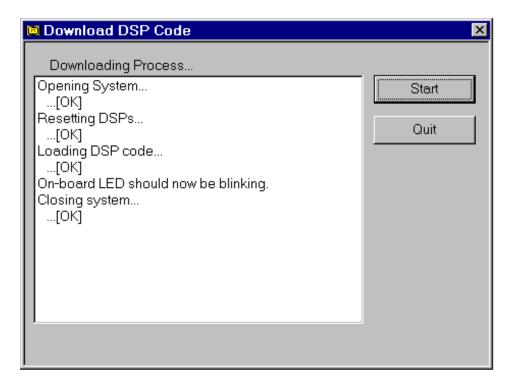

| Figure 13 Screen Display of the "dspload" Example Program  | 88 |

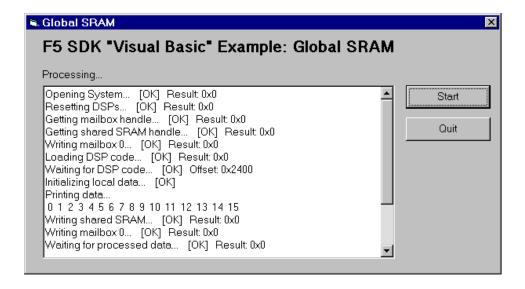

| Figure 14 Screen Display of the "glbsram" Example Program  | 88 |

| Figure 15 Screen Display of the "guisamp" Example Program  | 89 |

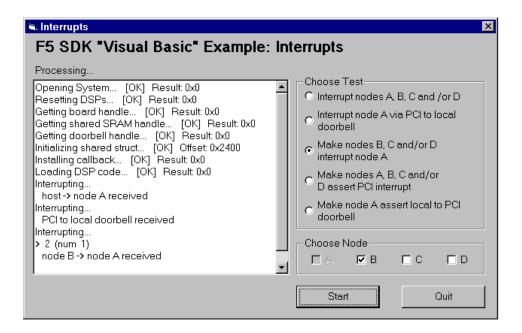

| Figure 16 Screen Display of the "intrupts" Example Program | 89 |

| Figure 17 Screen Display of F5 SDK Tester                  | 90 |

|                                                            |    |

#### List of Tables

| Table 1  | Memory Device Sizes (in 32-bit words)                 | 6    |

|----------|-------------------------------------------------------|------|

| Table 2  | Reset Summary                                         | 8    |

| Table 3  | F5 Hardware and Software Requirements                 | 12   |

| Table 4  | Calling Conventions for Windows 95 and Windows NT     | 15   |

| Table 5  | F5 Jumper Summary                                     | 18   |

| Table 6  | Directory Contents After Installing the SDK           | 25   |

| Table 7  | F5 ALIB Host Functions                                | . 45 |

| Table 8  | F5 ALIB DSP Functions                                 | . 75 |

| Table 9  | Troubleshooting - Messages Displayed by F5 SDK Tester | . 91 |

| Table 10 | Status Codes for Host Library Functions               | . 95 |

| Table 11 | Status Codes for DSP Library Functions                | 97   |

# 1 Introduction

#### 1.1. Purpose of This Manual

This manual describes the F5 Software Development Kit (SDK) that's used to develop applications for the F5 Carrier Board. It describes how to install the SDK and how to use the F5 Host and C4x DSP libraries.

A second manual, the *Dakar F5 Carrier Board Technical Reference*, describes the features, architecture, and specifications of the F5 Carrier Board, and is the primary hardware reference.

#### 1.2. Reference Documents

This guide is meant to be used in conjunction with the following documents:

- Dakar F5 Carrier Board Technical Reference from Spectrum

- Toolbox Configuration Utilities User Guide available from Spectrum

- TMS320C4x User's Guide available from Texas Instruments

- TMS320C4x C Source Debugger User's Guide available from Texas Instruments

- TMS320 Floating-Point DSP Assembly Language Tools User's Guide available from Texas Instruments

- TMS320 Floating-Point DSP Optimizing C Compiler User's Guide available from Texas Instruments

#### 1.3. Conventions Used in This Manual

This manual uses the following conventions:

• *Italic* font is used to designate placeholder names, such as command parameter names, cross-references, and references to other documents. For example:

The value passed to *phResc* must be a valid pointer to an F5 resource.

• **Bold** font is used to emphasize text, filenames, and command names within paragraphs. For example:

Refer to the **readme.txt** file for the most current information.

• This font is used to designate program code, examples, text that appears on the screen, and commands that you must enter in an interactive display. For example:

In the Run dialog box enter:

```

a:\install.exe

```

- < F5RootDirectory> is used to indicate the location of your F5 SDK files on your hard drive. It specifies the directory on your hard drive from which your F5 SDK files branch, and is most likely the directory you chose during installation.

- "0x" before a number indicates that this is hexadecimal notation (base 16). For example:

Set the Reload Configuration Registers Bit (bit 29) in the PCI9060/9080 EEPROM control register (PCI offset 0x6C, local bus offset 0xEC) to "0".

• An "h" after a number indicates that this is hexadecimal notation (base 16). For example:

```

IRAM0: origin = 002FF800h length = 0400h /* Internal RAM

```

• Wherever possible, the following side-by-side shaded boxes have been used to indicate information that is different for a Windows 95 or Windows NT environment. If you are using a Windows NT environment, for example, you can disregard the information in the Windows 95 column throughout the manual. For example:

The F5 Software Development Kit (SDK) consists of the following:

| Windows 95:                                             | Windows NT:                                         |

|---------------------------------------------------------|-----------------------------------------------------|

| F5 Windows 95 Host<br>Application Library<br>(ALIB_W95) | F5 Windows NT Host<br>Application Library (ALIB_NT) |

# 2 Hardware Overview

The F5 Carrier Board is a TIM-40 carrier board for use within computers equipped with a PCI bus. The full-length PCI board features one embedded Texas Instruments TMS320C44 Digital Signal Processor (DSP) and three TIM-40 module sites. TIM-40 modules define a family of DSP modules, based on TMS320C4x processors, designed for use in multiple DSP systems. Spectrum offers a range of single and dual processor TIM-40 modules that can be used with the F5 Carrier Board.

#### 2.1. Features of the F5 Carrier Board

The F5 Carrier Board offers the following features:

- Flexible architecture consisting of up to seven TMS320C4x-based processor nodes

- One embedded TMS320C44 ('C44) processor with associated memory devices to form a virtual TIM-40 site for Node A

- Three TIM-40 sites supporting single or double width TIM-40 modules

- Up to 420 MFLOPS performance, by using three dual-processor TIM-40 modules and the embedded 'C44 for a total of seven 50/60 MHz TMS320C4x processors

- Internal TMS320C4x communication port (COMM Port) connections between processor nodes

- Ten external COMM Port connectors from the processor nodes

- 132 MBytes/s peak transfer rates from 32-bit PCI (Master/Slave) Bus

- One on-board DSP~LINK3 module site

- One external DSP~LINK3 connector

- Non-intrusive multi-processor debugging in real-time using JTAG interface

- External connector on end-plate which provides access to TIM-40 Application Specific Pins for nodes B, C, and D

- Up to 512k x 32-bit 1 wait-state SRAM shared between all processor nodes

- Up to 1M x 32-bit 0 wait-state SRAM for the Node A embedded processor

- Programmable Erasable ROM (PEROM) for the Node A embedded processor which provides TIM-40 compliant code boot-strapping and board identification

#### 2.1.1. Scaleable Modular Architecture

With its embedded 'C44 processor and its three module sites that are compatible with Texas Instruments' TIM-40 specification, the F5 Carrier Board can be configured with one to seven 'C4x DSPs. This results in an architecture that can be scaled from 60 to 420 MFLOPS of processing power with varying memory capacity. A wide range of modules are available from Spectrum providing the flexibility of different memory and analog I/O combinations for each TIM-40 site. Single or double width TIM-40 modules can be accommodated.

#### 2.1.2. PCI Interface

Any PCI master on the PCI bus can access the following devices on the F5 Carrier Board via the PCI slave interface:

- Test Bus Controller

- PLX PCI9060/9080 PCI interface chip registers

- Far Global SRAM (for shared memory communication)

- Interrupt registers

- Bus Control registers

The Node A embedded 'C44 can master the PCI bus through the DMA channels of the PLX PCI9060/9080 PCI interface chip. This allows the F5 Carrier Board to access the resources on the host computer through DMA transfers initiated by Node A.

**Note:** The Intel® 430FX chipset does not support DMA Bus Mastering. If your computer is equipped with this chipset, the F5 Carrier Board cannot initiate a DMA transfer to the PCI bus as a PCI master.

#### 2.1.3. TMS320C4x Communication Port Interfaces

The TMS320C4x communication ports (COMM Ports) are used for inter-processor communication both internally and externally to the F5 Carrier Board. The COMM Ports provide bi-directional asynchronous communication between TMS320C4x processors. They are ideal for passing large data sets between processors without loading any shared resource, such as the Far Global SRAM. All four nodes are connected to each other internally and there are 10 external COMM Port connections shared amongst the nodes.

Intel is a registered trademark of Intel Corporation.

#### 2.1.4. Shared Memory Resources

The shared bus architecture allows the on-board DSP, the TIM-40 module sites, and the PCI interface to access a shared bank of on-board SRAM. The F5 Carrier Board will have either 0.5 MB or 2 MB of SRAM.

#### 2.1.5. Node A Memory Resources

Node A memory resources consist of a local bus PEROM, local bus SRAM and global bus SRAM in accordance to the TIM-40 specification. These resources are only accessible from the Node A 'C4x. The PEROM device is a 32Kx 8-bit device used for TIM-40 IDROM and, optionally, for the loading of boot-code. The local and global busses of Node A contain either both 0.5 MB or both 2 MB zero wait-state 15 ns SRAM banks.

#### 2.1.6. DSP~LINK3 Interface

DSP~LINK3 modules can be used with the F5 Carrier Board via the DSP~LINK3 interface. The DSP~LINK3 module site allows Spectrum DSP~LINK3 modules to be installed right on the F5 Carrier Board while the DSP~LINK3 ribbon cable connector allows external DSP~LINK3 modules to be connected to the F5 Carrier Board. The interface is directly accessible to all processors nodes.

Spectrum offers a range of modules with DSP~LINK3 interfaces that can be used with the F5 Carrier Board, including IndustryPack® modules.

The DSP~LINK3 interface is an open standard for Spectrum's I/O interface. It defines a 32-bit wide, 40 Mbyte-per-second I/O interface with low interrupt latency. The full DSP~LINK3 specification is available from Spectrum upon request. DSP~LINK3 is electrically compatible the DSP~LINK2 specification and may be used with DSP~LINK2 with the appropriate mechanical adapter available from Spectrum.

#### 2.1.7. JTAG Interface Debug Support

An on-board JTAG Test Bus Controller (TBC) is mapped to the PCI Local Bus to provide multiprocessor, C source, debug capability in conjunction with support software applications. JTAG-based debugging uses the 'C4x's dedicated debug port to minimize the intrusiveness of the debugger on your application.

#### 2.2. Memory Configurations Available

The F5 Carrier Board is available in the memory configurations shown in the following table. Each SRAM bank consists of four 8-bit SRAM memory devices.

Table 1 Memory Device Sizes (in 32-bit words)

| Total SRAM<br>(Bytes) | Local<br>SRAM<br>Bank 1 | Local<br>SRAM<br>Bank 0 | Global<br>SRAM<br>Bank 1 | Global<br>SRAM<br>Bank 0 | Far<br>Global<br>SRAM |

|-----------------------|-------------------------|-------------------------|--------------------------|--------------------------|-----------------------|

|                       | 15 ns                   | 15 ns                   | 15 ns                    | 15 ns                    | 20 ns                 |

| 1.5 Mbytes            | empty                   | 128K                    | empty                    | 128K                     | 128K                  |

| 6 Mbytes              | empty                   | 512K                    | empty                    | 512K                     | 512K                  |

| 10 Mbytes             | 512K                    | 512K                    | 512K                     | 512K                     | 512K                  |

#### 2.3. Bus Architecture

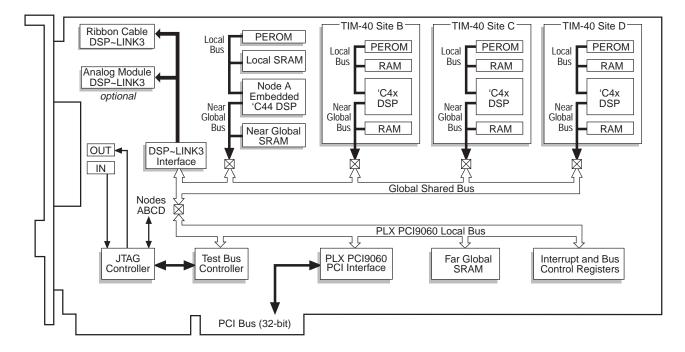

Several different communication buses are used on the F5 Carrier Board to connect the embedded 'C44 processor, TIM-40 sites, memory devices, and interface circuitry as shown in the following diagram.

Figure 1 F5 Block Diagram

The internal busses of the F5 Carrier Board are described in the following passage.

#### **Local Bus**

The Local Bus address range is specific to a single 'C4x DSP, and is therefore not shared with other processors or nodes. It is a private memory bus of a particular 'C4x.

#### Near Global Bus

The Near Global Bus refers to the Global Bus of each TIM-40 site and the embedded 'C4x node. The SRAM located on 'C44 Global Bus is zero wait state. The Near Global Bus SRAM of a node cannot be accessed by the DSPs of any other nodes.

#### Global Shared Bus

The Global Shared Bus interconnects the:

- Buffered Global Buses of each TIM-40 site via the Global Connectors

- Buffered Global Buses of the embedded 'C44 node A

- DSP~LINK3 Interface

- Interface between the PLX PCI9060/9080 Local Bus and the Global Shared Bus

32-bit buffers isolate the Global Shared Bus from the 'C4x node Global Buses. An analog quickswitch connects the data and address lines of the Interface between the PLX PCI9060/9080 Local Bus and the Global Shared Bus; the interface control lines are buffered.

#### PLX PCI9060/90 80 Local Bus

The PLX PCI9060/9080 Local Bus of the PLX PCI9060/9080 chip is connected to the

- Global Shared Bus interface buffer

- Far Global SRAM

- Interrupt Controller

- Registers for the Interrupt Controller and Bus Arbitration

- JTAG Controller

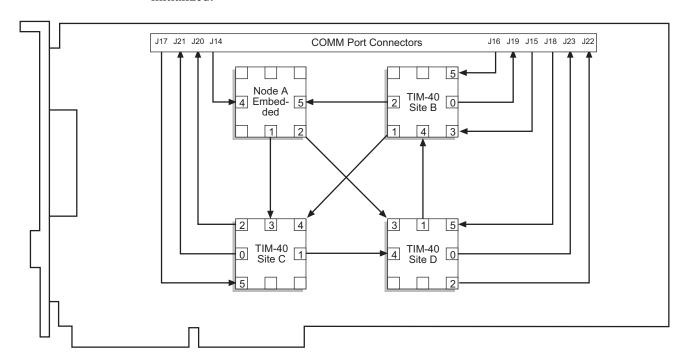

#### 2.4. 'C4x Communication Port Architecture

Routing of the 'C4x COMM ports to the 10 external COMM port connectors is shown in the following diagram. Arrows indicate the default port direction after the board is initialized.

Figure 2 F5 COMM Port Architecture

#### 2.5. Resetting the F5 Carrier Board

The F5 Carrier Board is reset upon system power up. Resets can also be performed from host software on the PCI bus and from JTAG. The following table shows which F5 Carrier Board hardware is initialized by each type of reset.

**Table 2 Reset Summary**

| F5 Carrier Board Hardware Reset                                              | Power Up | PCI Software | JTAG |

|------------------------------------------------------------------------------|----------|--------------|------|

| All CPU Nodes                                                                | ✓        | ✓            | ✓    |

| DSP~LINK3 Slave Devices                                                      | ✓        | ✓            |      |

| JTAG devices connected to the JTAG<br>Out connector /GRESET pin (J11 pin 20) | ✓        | ✓            | ✓    |

| PCI bus Interface Logic                                                      | ✓        |              |      |

| PCI9060/9080 Local Bus Logic                                                 | ✓        | <b>√</b>     |      |

| Support Logic                                                                | ✓        | ✓            | ✓    |

When the processor nodes are reset with any of the above methods, the 'C4x processor IIOF lines are tristated as per the TIM-40 specification to allow the boot mode selection jumpers to be read by the C4X processor. To enable its IIOF signals, a 'C4x must then execute an IACK cycle.

#### 2.5.1. Power Up Reset

The PCI bus RST# signal resets all F5 Carrier Board hardware when it is asserted. It is asserted upon system power up and typically when the operating system is started.

The system must issue PCI bus configuration cycles after RST# to configure the F5 Carrier Board PCI bus interface. Usually the host BIOS or operating system will do this automatically.

The F5 Carrier Board remains in a reset state for approximately 30 milliseconds after power on for on board initialization. Once this is complete, the on board reset logic is released.

#### 2.5.2. PCI Software Reset

Any PCI master (usually the host) can reset all F5 Carrier Board hardware *except* the PCI bus interface logic, using the following procedure on the PLX PCI9060/9080 PCI interface chip.

- 1. Set the PCI Adapter Software Reset Bit (bit 30) in the PCI9060/9080 EEPROM control register (PCI offset 0x6C, local bus offset 0xEC) to "1". This places the F5 Carrier Board in the reset state.

- 2. Set this same bit to "0". This releases the F5 Carrier Board from reset.

- 3. Set the Reload Configuration Registers Bit (bit 29) in the PCI9060/9080 EEPROM control register (PCI offset 0x6C, local bus offset 0xEC) to "0".

- 4. Set this same bit to "1". This reloads the PCI9060/9080 configuration registers from EEPROM. The transition from 0 to 1 causes the reload to occur.

PCI bus configuration registers in the PCI9060/9080 are *not* affected by this reset, therefore PCI bus configuration cycles do not need to be issued.

After reset the PCI9060/9080 EEPROM needs to be reloaded as described above. The PCI9060/9080 EEPROM enable jumper J25 must be installed, and the EEPROM loaded with the correct values.

**Note:** The PLX PCI9060/9080 can be reset and then initialized from its EEPROM by using the **F5\_Control** function with the F5\_CTL\_RESET action parameter. Refer to the function description in this guide and to the source code examples for complete details.

#### 2.5.3. JTAG Reset

Setting the /GRESET input of the JTAG IN connector (J10 pin 20 ) to 0 volts resets:

- All processor nodes

- JTAG Out

- Support logic

The /GRESET signal is a TRISTATE line that is shared across all F5 Carrier Board boards connected by a 20 pin JTAG connector. All F5 Carrier Boards that are connected together through a JTAG chain can be simultaneously reset by asserting this line. This ensures that all F5 Carrier Boards that are connected together via COMM PORT cables are reset simultaneously to avoid any damage due to contention on the COMM PORT direction settings.

To resume normal operation, the /GRESET signal must be tristated by an external driver. Pull up resistors on the board can then place the line at 5 volts.

#### 2.6. Booting the F5 Board

Jumper J28 is used to select the boot mode of the embedded 'C44. When installed, the 'C44 boots from its PEROM; when removed, the COMM port boots the 'C44. (See *section 4.1* for the location of J28.)

If PEROM is used to boot the 'C44, Spectrum's "Bootloader" will automatically be loaded from Node A's PEROM to the 'C44 when the board is powered up or RESET.

# 3 Software Overview

The F5 Software Development Kit (SDK) consists of the following items:

#### Windows 95:

- F5 Windows 95 Host Application Library (ALIB W95)

- F5 Windows 95 Device Driver

- F5 C4x Application Library (ALIB\_C4x)

- Examples

- Utilities

- Toolbox Utility

- Manuals

#### Windows NT:

- F5 Windows NT Host Application Library (ALIB\_NT)

- F5 Windows NT Kernel Interface Library and Device Driver

- F5 C4x Application Library (ALIB\_C4x)

- Examples

- Utilities

- Toolbox Utility

- Manuals

**Note:** A complete set of source code and make files for the Windows device drivers and Windows host application libraries are **not** provided with the F5 SDK.

The Host SDK includes only certain source code files, such as ALIB\_W95 and ALIB\_NT; these are provided for reference only and do not form a complete set. You won't be able to successfully compile and link these programs.

#### 3.1. Hardware and Software Requirements

The following table lists the F5 software installation and development requirements.

#### **Table 3 F5 Hardware and Software Requirements**

# A x486 (or higher) PC computer with a free PCI slot and at least 16MB of RAM, 2MB of free hard drive space An F5 PCI Carrier Board

#### **Software**

- Windows 95 or NT 4.0 operating system

- Texas Instruments' TMS320C4x DSP C Compiler, Assembler, and Linker

- A TMS320C4x debugging system (recommended)

- Windows NT: Visual Basic, version5.0 (to run the example programs).

- A 32-bit Windows C compiler (for host code development). We recommend Microsoft Visual C/C++:

Windows 95: version 5.0 Windows NT: version 5.0

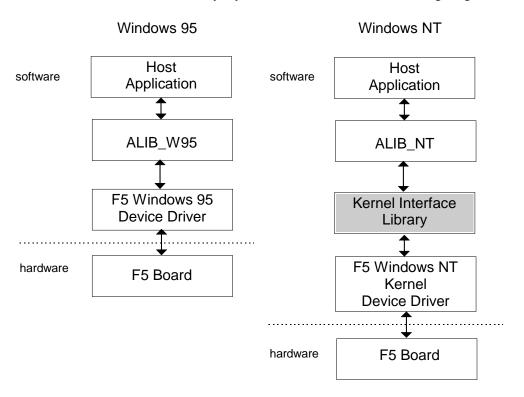

#### 3.2. F5 Host Program Structure

The main difference between the Windows 95 and the Windows NT Host Program Flow lies in the Device Driver layer; the Windows NT version of the F5 SDK has an additional Kernel Interface Library layer, as can be seen in the following diagram.

Figure 3 F5 Host Program Flow

#### 3.2.1. F5 Windows Host Application Libraries

Both the ALIB\_W95 and the ALIB\_NT are high level 32-bit Dynamic Link Libraries (DLLs) that provide your host system with functions for initializing, downloading code to, and performing I/O operations on an F5 board. Both ALIBs support multiple processes and/or threads and can access multiple F5 boards concurrently.

ALIB\_W95 runs under Windows 95, and ALIB\_NT runs under Windows NT 4.0. ALIB\_NT supports Visual Basic version 5.0.

**Note:** The application libraries are described further in *chapters 5* and 7.

#### 3.2.2. F5 Windows 95 and NT Device Drivers

#### Windows 95:

The F5 Windows 95 Device Driver (vf5d.vxd) provides (through ALIB\_W95) the lowest level software interface to basic control and I/O routines. The device driver functions are actually hidden behind the provided F5 Host Application Library (ALIB\_W95). That is, your application calls the ALIB\_W95 functions, which in turn call the "lower-level" device driver functions, as illustrated in *Figure 3*.

**Note:** Although you can access the device driver functions directly, we recommend that you use the provided ALIB\_W95 host functions to communicate with the F5 board.

#### Windows NT:

The F5 Windows NT Kernel Device Driver (**udrv.sys**) provides the lowest level software interface to basic control and I/O routines. The device driver functions are actually hidden behind the provided F5 Host Application Library (ALIB\_NT). That is, your application calls the ALIB\_NT functions, which in turn call the "lower-level" device driver functions, as illustrated in *Figure 3*.

The Kernel Interface Library (kintssp.dll) provides a standard interface for the ALIB\_NT to access the Windows NT Kernel Device Driver.

#### 3.3. F5 C4x Application Library

The F5 C4x Application Library (ALIB\_C4x) provides your DSP application with routines to configure and transfer data to F5 resources (Shared SRAM and PCI). You can develop C4x DSP application code for the F5 on any platform which supports Texas Instruments' TMS320C4x development tools.

The ALIB\_C4x is described further in *chapter 8 Development of DSP Applications*, and the functions are detailed in *chapter 9 DSP Software Functions*.

#### 3.4. Data Type Definitions

Data types used in F5 Host and DSP code are defined in two header files:

- **f5user.h** defines data types used in F5 Host code

- **f5\_c4x.h** defines data types used in F5 DSP code

The most common data type used in both host and DSP code is UINT32. UINT32 is defined as a 32-bit wide unsigned integer.

#### 3.5. Calling Conventions for Windows 95 and Windows NT

| Windows 95:                                      | Windows NT:                                                                               |

|--------------------------------------------------|-------------------------------------------------------------------------------------------|

| uses C calling convention (-cdecl). For example: | uses standard calling convention (-stdcall). For example:                                 |

| F5API RESULT F5_Control ()                       | F5API RESULT CCC F5_Control ()                                                            |

|                                                  | CCC - C calling convention macro - used for Application Library (ALIB) exported functions |

Table 4 Calling Conventions for Windows 95 and Windows NT

**Note:** The syntax for the functions described in *chapter 7 Host Software Functions* and *chapter 9 DSP Software Functions* is shown using the C calling convention. For Windows NT, use the calling convention as shown in the above table.

#### 3.6. Example Programs

The F5 SDK provides example programs that demonstrate how to use the various F5 application library functions. Most of the programs are provided in both C and Visual Basic versions.

The examples can be found in the *<F5RootDirectory>\examples* subdirectories. See *chapter 10* for a description of the programs and details on running and rebuilding the example programs.

**Note:** The Visual Basic (VB) examples are for the Windows NT environment only. To run the Visual Basic examples, the user must have Visual Basic version 5.0 and must possess a working knowledge of VB 5.0 development environment and programming.

#### 3.7. Manuals Provided With the F5 SDK

The manuals provided with the F5 SDK are:

- Dakar F5 Carrier Board Technical Reference

- Dakar F5 Carrier Board User Guide (this manual)

- Toolbox Configuration Utilities User Guide

#### 3.8. Utilities Provided With the F5 SDK

Utilities are provided with the F5 SDK to allow you to do the following:

| То                                                                                                                                                                                                          | Use:                 | Filename     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------|

| List all F5 boards on a host system, including their hardware configurations.                                                                                                                               | F5 List<br>Inspector | f5list.exe   |

| Test the F5 ALIB. Each function can be tested separately. (See <i>section 4.10</i> for more details.)                                                                                                       | F5 SDK<br>Tester     | f5lb_t.exe   |

| Windows 95 only: Display debug messages from both the Windows 95 Device Driver and the F5 Host ALIB functions in debug mode. (See <i>section 6.9 Viewing Debug Messages (Windows 95)</i> for more details.) | DBGMON               | dbgmon.exe   |

| Windows NT only: Read and Write directly to/from the board. (Use the About button for more details.)                                                                                                        | F5 IO Tester         | f5io.exe     |

| Toolbox is used to generate System Definition Files (SDF). See appendix C for more information on SDF. Refer to the "Toolbox Configuration Utilities User Guide" for installation and usage of toolbox.     | Toolbox              | toolbox.exe  |

| GNU utilities are used to rebuild DSP-based examples.                                                                                                                                                       | PC GNU<br>Utilities  | mkdepend.exe |

All of the above utilities, except Toolbox and GNU, can be found in your *<F5RootDirectory>\bin* directory. Utilities can be run by double-clicking on the utility's filename (in Explorer) or by going to the **F5 SDK** Program Folder in the **Start > Programs** menu.

The Toolbox and GNU utilities are located on separate disks shipped with the **F5 SDK** package.

# 4 Hardware and Software Installation

This chapter describes how to configure and install the F5 Carrier Board into a computer. It also describes how to install the Software Development Kit (SDK) for the F5 Carrier Board. The F5 Carrier Board host and DSP libraries, device driver, example programs, and utilities are all part of the SDK.

**Caution:** Before handling the F5 Carrier Board or a module, ensure that you and the components are properly grounded to prevent damage from electrostatic discharge.

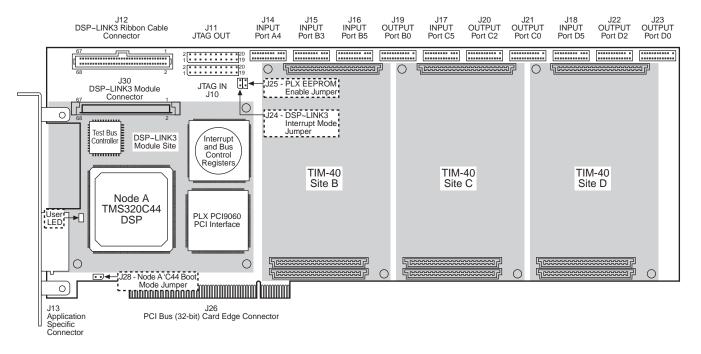

#### 4.1. Configuring the F5 Carrier Board

Configure the on board jumpers to suit your application. Refer to the following figure and table for information on the jumper settings.

Figure 4 F5 Connector and Jumper Locations

**Table 5 F5 Jumper Summary**

| Jumper | Description                       | Installed                                | Not Installed                                |

|--------|-----------------------------------|------------------------------------------|----------------------------------------------|

| J24    | DSP~LINK3 Interrupt<br>Mode       | All DSP~LINK3 interrupts to Node A IIOF0 | DSP~LINK3 interrupt<br>IRQ0 to Node A IIOF0* |

| J25    | PLX PCI9060/9080<br>EEPROM Enable | Enabled*                                 | Disabled                                     |

| J28    | Node A 'C44 Boot Mode             | Boot from PEROM*                         | Boot from COMM Port                          |

<sup>\*</sup>Default

#### 4.2. Module Installation

Your F5 Carrier Board may already contain DSP~LINK3 or TIM-40 modules. If it doesn't, or you are adding modules to it, follow these instructions to install them on the F5 Carrier Board.

**Caution:** Before handling the F5 Carrier Board or module, ensure that you and the components are properly grounded to prevent damage from electrostatic discharge.

The following figure shows the location of the modules on the F5 Carrier Board and the mounting hardware for the sites.

Figure 5 F5 Module Locations

#### 4.2.1. Installing DSP~LINK3 Modules

To install a DSP~LINK3 module onto the F5 Carrier Board:

- 1. If the module that you are installing has its own end plate bracket, remove the end plate bracket that is attached to the F5 Carrier Board.

- 2. Place the DSP~LINK3 module on the F5 Carrier Board. Align the three nylon mounting posts on the DSP~LINK3 module with their corresponding holes on the F5 Carrier Board.

- 3. Hand tighten the three 3mm nylon hex nuts to the mounting posts on the solder side of the F5 Carrier Board to secure the module in place.

- 4. Screw the end plate of the module to the F5 Carrier Board.

#### 4.2.2. Installing TIM-40 Modules

To install a TIM-40 module onto the F5 Carrier Board:

- 1. Use the nylon mounting posts on the TIM-40 sites to position the TIM-40 module.

- 2. Press down on the module to mate the top, bottom, and global connectors.

- 3. Secure the module on to the F5 Carrier Board by hand-tightening the nylon hex nuts that came with the module on to the mounting posts.

#### 4.3. Installation into PCI Slot and Cabling

After the jumpers on the F5 Carrier Board have been configured, it can be installed in a PC and any other connections can be made.

**Caution:** Use the keyed COMM Port cables from Spectrum to prevent damage to the F5 Carrier Board when making COMM Port connections. These cables are keyed to prevent accidental connection of outputs to outputs, or inputs to inputs. If you use other cables, be careful to avoid connecting a default output to a default input COMM Port.

- 1. Ensure that all hardware is powered off.

- 2. Attach the JTAG, DSP~LINK3 module, and/or DSP~LINK3 cables to the board if you are using them.

- 3. Install the F5 Carrier Board into an empty PCI slot of the PC computer.

- 4. Attach the COMM Port and Application Specific Connector cables to the board if you are using them.

- 5. Do **not** power on the system at this time. Go to the next section..

#### 4.4. Windows NT Installation Notes

**Note:** This section is only applicable if you are installing the F5 SDK onto a Windows NT platform.

Before installing the F5 SDK make sure the Plug and Play BIOS is disabled.

#### 4.5. Windows 95 Installation Notes

**Note:** This section is only applicable if you are installing the F5 SDK onto a Windows 95 platform. If you are not installing onto a Windows 95 platform, go to *section 4.6*.

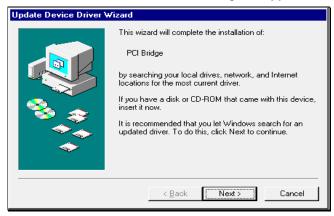

The first time you plug an F5 Carrier Board into a computer running the Windows 95 operating system, Windows 95 will prompt you to set up the new hardware. This section describes how to correctly perform this initialization procedure. If not done properly, the Plug and Play component of Windows 95 will not initialize the F5 Carrier Board correctly.

**Note:** The initialization procedure will vary slightly depending upon which particular build of Windows 95 you have running on your machine.

- 1. If the F5 Carrier Board is not installed in the computer, turn off the computer and install the F5 Carrier Board. For information on how to do this, see the previous section.

- 2. Turn on the power. Windows 95 should automatically launch.

- 3. Depending upon which build of Windows 95 your computer is running, one of two dialog boxes will appear:

- New Hardware Found dialog box (for build 4.00.950a)

- Install Device Driver Wizard dialog box (for build 4.00.950b)

- 4. Perform the steps corresponding to the dialog box that is displayed on your system.

# If the New Hardware Found PCI Bridge Select which driver you want to install for your new bardware; Windows default thiorr Driver from disk provided by hardware manufacturer Do not install a driver (Windows will not prompt you again) Select from a list of alternate drivers OK Cancel Help

Windows 95 Build 4.00.950a

- 1. Click **Do not install a device driver...**

- 2. Click **OK**.

#### If the Install Device Driver Wizard dialog box appears...

Windows 95 Build 4.00.950b

- 1. Ensure that drive A: and the CD-ROM drive are empty.

- 2. Click Next.

- 3. Windows 95 will search drive A: and the CD-ROM drive for a driver file. When Windows 95 is finished you will be prompted for Other Locations.

- 4. Click Finish.

Windows 95 is now configured for the F5 Carrier Board to work on the PCI bus and will not ask you to install drivers again for the F5 Carrier Board on this computer.

**Note:** You can also determine the build of Windows 95 that you have as follows. From the Explorer window in Windows 95, right-mouse click on the My Computer icon. Select Properties. Select the General tab. The System list will indicate the Windows 95 build version.

#### 4.6. Installing Multiple F5 Carrier Boards

If multiple F5 Carrier Boards are installed on one PCI bus, then each board must have a unique identification (ID). This ID is stored in the PEROM of Node A of each F5 Carrier Board. By default, all F5 boards are shipped with an ID of 0x1.

Refer to *section 6.5 Changing your System's Hardware Configuration* for information on setting the F5 Carrier Board ID value.

#### 4.7. Installing the Software Development Kit (Windows NT)

**Note:** If you already have a version of the F5 Software Development Kit (SDK) installed on your system, ensure that you first uninstall it. See *section 4.12 Uninstalling the Software Development Kit (Windows NT)* for instructions on uninstalling the SDK.

When installing the SDK, you must install both the Host SDK and the DSP SDK We recommend you install the Host SDK first, then the DSP SDK. The steps are identical for each installation.

To install the Software Development Kit (SDK) for the F5 Carrier Board onto a Windows NT platform, follow these steps:

- 1. Ensure that you have administrative privileges.

- 2. Insert the installation disk into the 3.5 inch floppy disk drive of your development PC.

| To install the Host SDK, use: | To install the DSP SDK, use: |

|-------------------------------|------------------------------|

| "DAKAR WinNT Host SDK" disk   | "DAKAR WinNT C4x DSP SDK"    |

|                               | disk                         |

3. From the **Start** menu, select **Run**, and, in the Run dialog box, type:

```

a:\setup.exe

```

where a:\ is the floppy disk drive containing the installation disk.

4. Select **OK** and wait for the computer to display instructions on the screen. The InstallShield® Wizard will guide you through the setup process. Follow the instructions.

**Note:** We recommend you accept the default installation directory.

5. When the screen titled

```

"Dakar (F5) Host Software Development Kit Setup Complete" or

```

"Dakar (F5) DSP Software Development Kit Setup Complete"

appears, select Yes, I want to restart my computer now.

- 6. Click **Finish**. The computer will reboot.

- 7. Repeat steps 2 to 6, until you have installed first the Host SDK and second the C4x DSP SDK.

- 8. Insert the PC GNU Utilities floppy into the 3.5" floppy drive. Repeat steps 2 to 4 to install the PC GNU Utilities. Once complete remove the floppy from the disk drive.

During the installation process, the F5 SDK files are copied into the specified directory on your hard drive (the default directory is **C:\F5SDK**). In addition:

- The F5 Host Application Library file (**F5alib.dll**) and the F5 Windows NT Kernel Interface Library file (**kintssp.dll**) are copied to your *c:\windows* directory.

- The F5 Windows NT Kernel Device Driver file (**udrv.sys**) is copied to your *c:\windows\system32\drivers* directory (this is where Windows NT looks for this file).

- The installation program makes the appropriate changes in the Windows NT Registry so that udrv.sys can be loaded automatically when Windows NT reboots. After a successful installation, Windows NT is configured for the F5 board to work on the PCI bus.

- The following Environment Variable is automatically set in the Windows NT Registry:

SET SSP\_PATH=<F5RootDirectory>\BIN;<F5RootDirectory>\EXAMPLES\DSPLOAD

#### 4.8. Installing the Software Development Kit (Windows 95)

**Note:** If you already have a version of the F5 Software Development Kit (SDK) installed on your system, ensure that you first uninstall it. See *section 4.13 Uninstalling the Software Development Kit* for instructions on uninstalling the SDK.

To install the Software Development Kit (SDK) for the F5 Carrier Board onto a Windows 95 platform, follow these steps:

- 1. Insert the "Dakar Win95 SDK" installation disk into the 3.5 inch floppy disk drive of your development PC.

- 2. From the **Start** menu, select **Run**, and, in the Run dialog box, type:

a:\setup.exe

where a:\ is the floppy disk drive containing the installation disk.

3. Select **OK** and wait for the computer to display instructions on the screen. The InstallShield® Wizard will guide you through the setup process. Follow the instructions.

**Note:** We recommend you accept the default installation directory.

- 4. When the "Setup Complete" screen appears, select Yes, I want to restart my computer now.

- 5. Click **Finish** and remove the installation disk from the floppy drive. The computer will reboot.

6. Insert the PC GNU Utilities floppy into the 3.5" floppy drive. Repeat steps 2 and 3 to install the PC GNU Utilities. Once complete remove the floppy from the disk drive.

During the installation process, the F5 SDK files are copied into the specified directory on your hard drive (the default directory is **C:\F5SDK**). In addition:

- The F5 Host Application Library file (**f5alib.dll**) is copied to your *c:\windows* directory.

- The F5 Windows 95 Device Driver file (**vf5d.vxd**) is copied to your *c:\windows\system* directory (this is where Windows looks for this file).

- The following DOS command is automatically inserted into your autoexec.bat file:

SET SSP\_PATH=<F5RootDirectory>\EXAMPLES\DSPLOAD

#### 4.9. Directory Contents After Installation of the SDK

After you've installed the Software Development Kit for the F5 Carrier Board, the destination root directory that you specified during installation will contain the directories listed in the following table. Refer to any installed **readme.txt** files for the most current information on the F5 Carrier Board SDK.

Table 6 Directory Contents After Installing the SDK

| Windows NT - Contents |                                                                                                                                         | Windows 95 - Contents |                                                                                                                   |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------|--|

| Directory             | Description                                                                                                                             | Directory             | Description                                                                                                       |  |

| <f5 root=""></f5>     |                                                                                                                                         | <f5 root=""></f5>     |                                                                                                                   |  |

| bin                   | Executable files for the DSP and Host (supplied by Spectrum)                                                                            | □bin                  | Executable files for the DSP and Host (supplied by Spectrum)                                                      |  |

| dev                   |                                                                                                                                         | alib                  | Some folders under <i>alib\host</i> are empty until code is built,<br>See <i>section 10.6</i> for details         |  |

|                       |                                                                                                                                         | shared                |                                                                                                                   |  |

|                       |                                                                                                                                         | include               | Contains header files                                                                                             |  |

| □dsp                  |                                                                                                                                         | host                  |                                                                                                                   |  |

| bin                   | Output files - DSP binary<br>files after you compile and<br>link your DSP programs                                                      | □bin                  |                                                                                                                   |  |

|                       |                                                                                                                                         | debug<br>release      | Contains f5alib.dll                                                                                               |  |

| include               | DSP Include files                                                                                                                       | build                 | Contains make file f5alib.mak                                                                                     |  |

| □lib                  | DSP application library file                                                                                                            | include               | Host include files                                                                                                |  |

| □src                  | DSP source code                                                                                                                         | □src                  | F5Alib source code                                                                                                |  |

|                       | dev\dsp\src contains different<br>subdirectories for different<br>modules                                                               |                       |                                                                                                                   |  |

|                       |                                                                                                                                         | □lib                  | Contains cofflib.lib, sdflib.lib                                                                                  |  |

|                       |                                                                                                                                         | debug<br>release      | Contains f5alib.lib                                                                                               |  |

| drv                   | F5 Windows NT Kernel<br>Device Driver                                                                                                   | driver                | F5 Windows 95 Device<br>Driver                                                                                    |  |

| examples              | Source code example programs.                                                                                                           | examples              | Source code example programs.                                                                                     |  |

|                       | Each example is in a subdirectory of <i>examples</i> . For example, <b>dspload</b> program is in <i>lexamplesldspload</i> subdirectory. |                       | Each example is in a subdirectory of examples. For example, dspload program is in lexamples\dspload subdirectory. |  |

| include               | DSP and Host Include files.<br>SDF files.                                                                                               | include               | DSP and Host Include files. SDF files.                                                                            |  |

| lib                   | DSP and Host application library files (supplied by Spectrum)                                                                           | □lib                  | DSP and Host application library files (supplied by Spectrum)                                                     |  |

| src                   | Host source code for the application library.                                                                                           |                       |                                                                                                                   |  |

|                       | See note at the beginning of chapter 3.                                                                                                 |                       |                                                                                                                   |  |

### 4.10. Installing Toolbox

Refer to the Toolbox Configuration Utilities User Guide for complete information on installing Toolbox.

#### 4.11. Verifying the Software Development Kit Installation

There are a number of programs that can be run to ensure that the F5 SDK is functioning properly. If you are just becoming familiar with the F5 SDK, we recommend to run the **dspload** example program.

Make sure your system configuration corresponds to the SDF used by the examples. All examples use the **F5.sdf** System Definition File (SDF) that's in < *F5RootDirectory*>\include. This SDF defines the following default system configuration:

- a single board system

- board ID = 0x1

- one embedded processor, no TIM modules

To run the **dspload** example program:

- 1. Go to the command prompt.

- 2. Change the directory to <*F5RootDirectory*>\examples\dspload

where *<F5RootDirectory>* is the location of the F5 SDK files on your hard drive. It specifies the directory on your hard drive from which your F5 SDK files branch, and is most likely the directory you chose during installation.

3. Type dspload

Your screen should resemble the following:

```

c:\f5sdk\Examples\Dspload\dspload

Opening system. . [OK]

Resetting DSPs. . [OK]

Loading DSP code . . [OK]

on-board LED should now be blinking.

Closing system. . [OK]

c:\f5sdk\Examples\Dspload>

```

If the test is successful, the on-board LED will be blinking.

For information on other example programs, see *chapter 10 Example Programs*.

If you wish to do more detailed testing, see section 10.4 Verifying the Device Driver and Host Library Installation.

For troubleshooting information, see section 10.5 Tips and Troubleshooting.

# 4.12. Uninstalling the Software Development Kit (Windows NT)

To uninstall the F5 SDK:

- 1. Click the **Start** button, then point to **Settings**.

- 2. Click Control Panel.

- 3. Double-click Add/Remove Programs.

- 4. With the **Install/Uninstall** tab selected, a list of programs will be displayed.

- 5. Click Dakar (F5) DSP Software Development Kit, then click Add/Remove.

- 6. Click Dakar (F5) Host Software Development Kit, then click Add/Remove.

Note that if you use the "Un-install F5 SDK" option (Start > Programs > F5 SDK **Program Folder**), only the Host SDK will be uninstalled.

If the SDK has been successfully uninstalled, all components of the F5 SDK (except the files udrv.sys and kintssp.dll) will be removed from your computer. If you are using other Spectrum products on your computer system, do not remove these files. If you are not using other Spectrum products, you may manually delete these two files.

# 4.13. Uninstalling the Software Development Kit (Windows 95)

To uninstall the F5 SDK:

- 1. Click **Start**, then point to **Programs**.

- 2. Point to **F5 SDK**, then click **F5 Uninstall**.

Another way to uninstall the F5 SDK is through the Windows Control Panel (see your Windows documentation for more information).

The Uninstall program does not delete changes made by the installation program to autoexec.bat: PATH and SET SSP PATH. You will have to manually delete these changes.

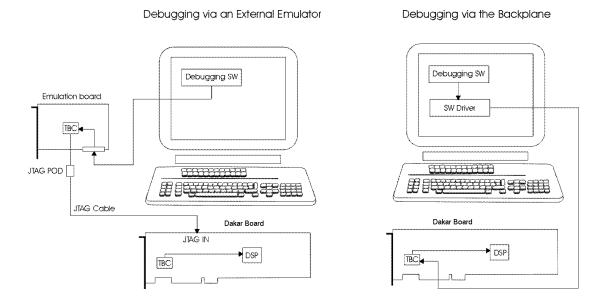

# 5 JTAG Debugging Software

The F5 Carrier Board supports JTAG emulation using the on-board Test Bus Controller (TBC), otherwise known as back-plane debugging, or using an external emulation board from White Mountain (the Mountain-510 Universal Emulator). The debugging application supported for both back-plane and external emulation is GO DSP's Code Composer<sup>TM</sup>.

The following diagram illustrates the two types of debugging that can be performed.

**Figure 6 JTAG Debugging Configurations**

**Note:** If a JTAG IN connection with a clock signal is present, the Test Bus Controller (TBC) will be automatically disconnected.

Refer to the JTAG Debugging section of the *F5 Carrier Board Technical Reference* manual for further information about JTAG debugging and setting up a JTAG chain for multiple board debugging.

#### 5.1. Using Code Composer

This section describes how to set up Code Composer for use with the F5 Carrier Board and how to load and run files using Code Composer. For further details, refer to the *Code Composer User's Guide* from GO DSP.

# 5.1.1. Setup for Back-plane Debugging

Follow this procedure to set up Code Composer for back-plane debugging.

- 1. Ensure that you've installed the Dakar Win NT Host SDK (Dakar Win 95 Host SDK, for Windows 95) and the C4x DSP SDK.

- 2. Install Code Composer.

- 3. Insert the Spectrum *Code Composer C4x MSTR* disk into the 3.5 inch floppy disk drive of your PC. This disk contains a sample GEL file and the DLLs that are required by Code Composer to access Dakar devices. Read the readme file provided on this disk for the most current information about the disk.

- 4. Copy the ssf5\_4xnt.dll (ssf5\_win95.dll for Windows 95) and the f5\_cpu\_a.gel files that are on the Spectrum *Code Composer C4x MSTR* disk to the <*CodeComposerRoot>* directory, where <*CodeComposerRoot>* is the base directory containing your Code Composer files.

- 5. Ensure that the f5\_cpu\_a.gel file properly reflects the memory maps of your system's processor. See *Section 5.1.3* for information about editing GEL files and the *Code Composer User's Guide* for more information about GEL files.

- 6. Run the Code Composer Setup program by choosing Start→Programs→Code Composer→Setup Code Composer.

- 7. Within the General Setup tab, click on Add Driver and from the list of files, select the ssf5\_4xntnt.dll (SSF5\_4xwin95.dll for Windows 95) file in the <CodeComposerRoot> directory.

- 8. Enter the Board ID of the Dakar board in the I/O Port text box. For a single board system, enter 0x1 as the I/O Port address.

For systems with more than one Dakar board, enter the Board ID of the first F5 Carrier Board that is in the JTAG scan chain. You should only have one instance of Code Composer running for all boards in your system.

**Note:** Refer to Section 6.5 *Changing your System's Hardware Configuration* for information on setting the F5 Carrier Board ID value.

9. Click on the MultiProcessor tab and enter a processor name for each DSP in your Dakar system.

For example, type cpu\_a and click Insert.

10. Click on OK. Setup creates a board.cfg file that lists the names and types of processors in the JTAG scan path and also creates a board.dat file which is a binary file containing JTAG scan path information.

# 5.1.2. Setup for Debugging with the Mountain-510 Emulator

Follow this procedure to set up for debugging with the Mountain-510 emulator:

- 1. Ensure that you've installed the Dakar Win NT Host SDK (Dakar Win 95 Host SDK for Windows 95) and the C4x DSP SDK.

- 2. Install Code Composer.

- 3. Insert the Spectrum *Code Composer C4x MSTR* disk into the 3.5 inch floppy disk drive of your PC.

- 4. Copy the f5\_cpu\_a.gel file that's on the Spectrum *Code Composer C4x MSTR* disk to the *<CodeComposerRoot>* directory, where *<CodeComposerRoot>* is the base directory containing your Code Composer files.

- 5. Install the following:

- The Mountain-510 emulator board

- The White Mountain DSP Code Composer Support Disk

See White Mountain DSP's documentation for installation instructions.

- Run the Code Composer Setup program by choosing

Start→Programs→Code Composer→Setup Code Composer.

- 7. Within the General Setup tab, click on Add Driver and from the list of files, select the wm510c4x32.dll file that's in the <CodeComposerRoot> directory.

- 8. Enter the base address of the Mountain-510 emulator in the I/O Port text box. Refer to the documentation provided by White Mountain DSP for the correct address (normally, the default address is 0x240).

- 9. Click on the MultiProcessor tab and enter a processor name for each DSP in your Dakar system.

For example, type cpu\_a and click Insert.

10. Click on OK. Setup creates a board.cfg file that lists the names and types of processors in the JTAG scan path and also creates a board.dat file which is a binary file containing JTAG scan path information.

#### 5.1.3. Editing the Sample GEL File

A GEL file is used to define memory mapped resources for the C4x processor. These registers have to be correctly set in the GEL file in order for your program to load and for the C4x to access its memory correctly. Refer to the F5 Carrier Board *Technical Reference* manual for information on memory resources.

**Note:** The GEL file will have to be modified if a TIM-40 module is added to the board.

Use a text editor to edit Spectrum's sample GEL file (f5\_cpu\_a.gel) file. Note that you can also edit GEL files from within Code Composer (see the *Code Composer User's Guide* for more details). Refer to the *Code Composer User's Guide* for further information about GEL files.

#### 5.1.4. Loading and Running Files

This section describes how to load and run files, such as DSP code, on the Dakar board using GO DSP's Code Composer.

1. If you are loading and running files via the back-plane of the Dakar board, ensure that there is **no** external cable connected to the front-panel JTAG IN of the Dakar board.

**Note:** You cannot use the Dakar's TBC (back-plane debugging) at the same time that you are using an external emulator. In addition, the F5 Carrier Board must be powered off before switching between back-plane and external emulation, and before attaching or removing an external emulator.

- 2. If you are using the Mountain-510 emulator, power down your system and connect the emulator board to the JTAG IN connector of the Dakar board. Follow the installation instructions provided by White Mountain DSP.

- 3. Ensure that the f5\_cpu\_a.gel file found in the <CodeComposerRoot> directory properly reflects the memory map of the Dakar processor. See Section 5.1.3 for more information about editing GEL files.

- 4. Ensure that the board.cfg file, created during Code Composer Setup, properly reflects the JTAG scan path of your system. These files can be found in the Code Composer root directory.

- Start Code Composer by selecting

Start → Programs → Code Composer → C4x Code Composer.

- 6. In the Processor Window, select File \rightarrow Load GEL and from the list of files, select the f5\_cpu\_a.gel file from the Code Composer root directory.

- 7. Load the DSP application file by selecting File \(\rightarrow\) Load Program and from the list of files, select the file that you want to load.

For example, to load blink.out, select the blink.out file from the <F5 Carrier BoardRoot>\examples\dspload directory.

8. To run the DSP application file, select Debug→Run Free from the Code Composer Main Menu.

If you loaded blink.out, the front panel LEDs should flash on and off.

9. Quit the debugger.

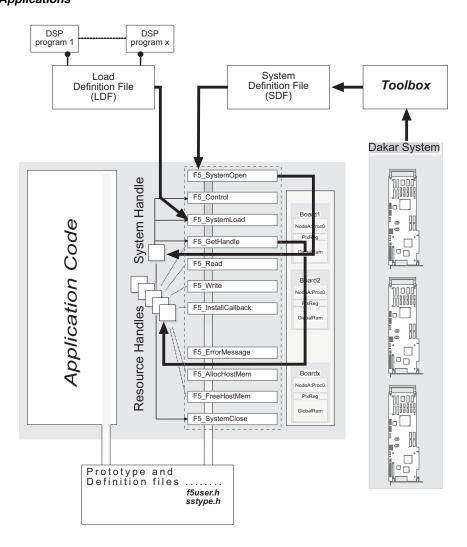

#### Development of Host Applications 6

The F5 ALIB W95 and ALIB NT provide the functions that you need to initialize, download code to, control, and perform I/O operations on an F5 board. This chapter discusses some of the functions that are used to perform these tasks and some important concepts that you should understand before using the Application Library (ALIB) functions.

#### **Architectural Overview** 6.1.

The architecture of HOST\_ALIB is grounded in the concept of resource management and manipulation. Figure 7 is a graphical representation of the architecture of HOST ALIB, and illustrates how your application code may integrate easily with the library.

The essential elements of the architecture to take note of are:

- the representation of the hardware components in a System Definition File

- generation of the SDF with Spectrum's Toolbox utility

- specification of downloadable DSP code in a Load Definition File

- common sharing of prototypes and definitions (.h files) between ALIB\_HOST and your application code

In any application there are four unique components:

- your application code

- a system handle and a collection of resource handles which your code acquires and uses for communication with the hardware

- the HOST\_ALIB functions which translate your requests into specific actions on the hardware

- the system configuration and resources which HOST\_ALIB manages on your behalf

Note that Toolbox is not a part of your application. It is a tool to be used when you initially install, or make a hardware modification to your Dakar system. The prototype and definition files are only required to build your application. The run-time system consists of your application, the Load and System Definition Files, and the Dakar hardware.

**Figure 7 Dakar Host Software Architecture**

#### 6.2. Calling Host Functions

HOST\_ALIB requires that you follow a simple rule for successful applications:

**Important!** always <u>acquire</u> a resource <u>before</u> you call functions that <u>use</u> that resource.