# **HP E2749**

# Fibre Channel Interface Module

# **User's Guide**

HP Part Number E2749-90000

Printed in U.S.A Print Date: July 1997

This document was published with CorelDraw! software. CorelDraw! is a trademark of the Corel corporation.

©Hewlett-Packard Company, 1997. All rights reserved. 8600 Soper Hill Road Everett, Washington 98205-1298 U.S.A.

i

#### **NOTICE**

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MANUAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or direct, indirect, special, incidental or consequential damages in connection with the furnishing, performance, or use of this material.

#### WARRANTY

A copy of the specific warranty terms applicable to your Hewlett-Packard product and replacement parts can be obtained from your local Sales and Service Office.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another language without the prior written consent of Hewlett-Packard Company. This information contained in this document is subject to change without notice.

Use of this manual is restricted to this product only.

#### **TRADEMARKS**

FibreXpress<sup>TM</sup> is a trademark of Systran Corporation.

Tachyon<sup>TM</sup> is a trademark of Hewlett-Packard Company.

#### RESTRICTED RIGHTS LEGEND

Use, duplication or disclosure is subject to HP standard commercial license terms or to the following restrictions whichever is applicable:

- 1) for non-DoD Departments and Agencies of the U.S. Government, as set forth in FAR 52.227-19(c)(1-2)(Jun 1987);

- 2) for the DoD Departments and its Agencies, as set forth in DFARS 252.227-7013(c)(1)(ii) (Oct 1988), DFARS 252.211-7015(c)(May 1991), whichever is applicable.

# HEWLETT-PACKARD COMPANY 3000 Hanover St.

Palo Alto, CA 94304 U.S.A.

Copyright (c) 1997 Hewlett-Packard Company. All rights Reserved.

## Registration Card

Make sure you send in the product registration card located in the red brochure included in your shipping carton. This assures that you will hear about future product and service updates. If the brochure has been misplaced, simply mail or fax the following information to the indicated address/fax number.

- Your Name:

- Position:

- Company Name:

- Division:

- Mail Stop:

- Street:

- City:

- State or Province:

- Postal Code:

- Country:

- Telephone: ( )

- Model:

- Serial Number:

### Mail to:

ATTN: Customer Support MS 500 Hewlett-Packard Company Lake Stevens Instrument Division 8600 Soper Hill Rd. Everett, WA 98205-1298

#### Or FAX:

(206)335-2828 No cover sheet is required. Customer Support MS 500

## In This Book

The HP E2749 Fibre-Channel Interface Module provides high-speed data transfer between a VXI mainframe and other devices. The module plugs into one C-size slot in a VXI mainframe.

This book documents the HP E2749 module. It provides:

- installation and service information

- operational information

- information on using Sequences with the HP E2749

- SCPI command reference materials

- $\bullet$  Information on using the HP E2749A with SYSTRAN Corporation's FibreXpress  $^{\text{TM}}$  products

## TABLE OF CONTENTS

## 1 Installing the HP E2749

Installing the HP E2749 1-2

To inspect the HP E2749 1-2

What you get with the HP E2749 1-3

To install the HP E2749 1-4

To store the module 1-7

To transport the module 1-7

## 2 Verifying the HP E2749

To verify the HP E2749 2-2

## 3 Replacing Assemblies

Replaceable Parts 3-2

To remove the top and bottom covers 3-6

To remove the front panel 3-8

To remove the A72/A53 assembly (GLM) 3-11

To remove the A1 main assembly 3-12

## 4 Backdating

Backdating 4-2

## **5 Hardware Description**

General description 5-2 Circuit description 5-3 HP E2749 front-panel description 5-4

## 6 Using the HP E2749

Introduction 6-2 HP E2749 and SCPI 6-3 Fibre Channel overview 6-5

## 7 Using Sequence Operations with the HP E2749

Sequence overview 7-2 Sequence quick reference 7-6 HP E2749 Sequence operations 7-12

## 8 Programming the HP E2749 with SCPI

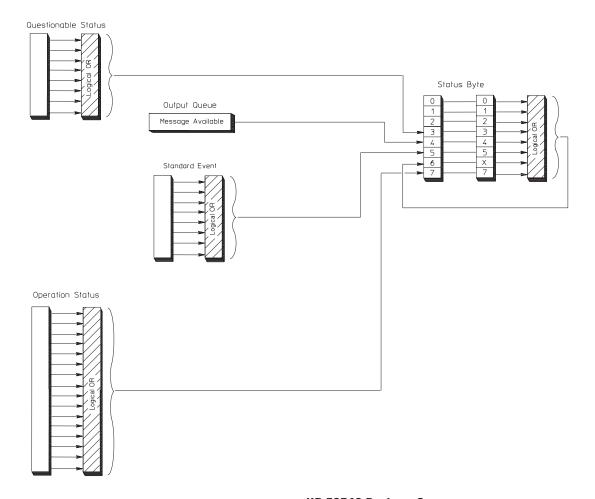

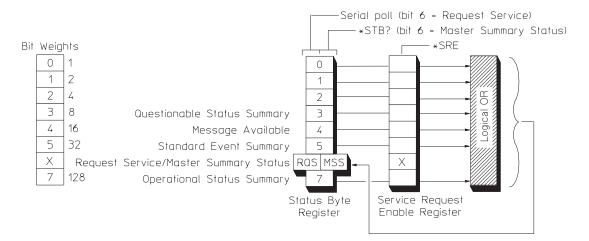

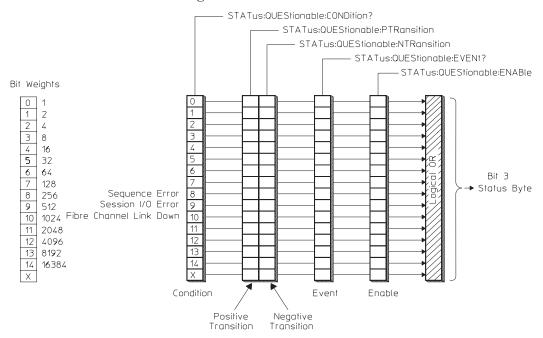

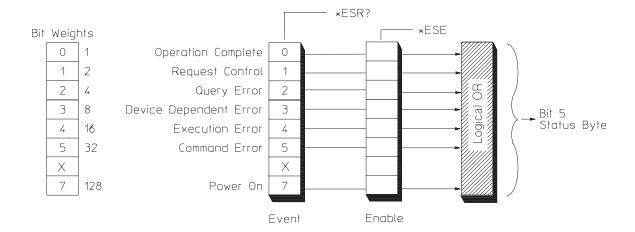

Getting started 8-2 Using the status registers 8-4 The HP E2749 registers sets 8-9 Addressing the HP E2749 8-18

### 9 SCPI Command Reference

SCPI Command Fields 9-2 Finding the Right Command 9-3 Command Syntax 9-4 HP E2749 SCPI Quick Reference 9-7 HP E2749 SCPI Commands 9-9 Errors 9-50

# 10 Using the HP E2749A with Systran FibreXpress $^{\rm TM}$ Products

Getting Started 10-2 Transmitting Data From the HP E2749A 10-4 Receiving Data From a Computer With The HP E2749A 10-6

## **Glossary**

1

Installing the HP E2749

## Installing the HP E2749

This chapter contains instructions for installing, transporting, and storing the HP E2749 Fibre Channel Interface Module. For information on verifying module operation, see chapter 2, "Verifying the HP E2749."

## To inspect the HP E2749

The HP E2749 Fibre Channel Interface Module was carefully inspected both mechanically and electrically before shipment. It should be free of marks or scratches, and it should meet its published specifications upon receipt.

If the module was damaged in transit, do the following:

- Save all packing materials.

- File a claim with the carrier.

- Call your Hewlett-Packard sales and service office.

## What you get with the HP E2749

The following items are included with your HP E2749:

#### Standard HP E2749A:

- HP E2749A Fibre Channel Interface Module C-size 1-slot VXI module, coaxial copper interface, 9-pin D-type connector

- HP E2749 User's Guide (this book)

#### **HP E2749A Option 001:**

• HP E2749A Fibre Channel Interface Module – C-size 1-slot VXI module, optical interface, duplex SC connectors

#### Note

This module includes a Class 1 Laser Product which complies with 21 Code of Federal Regulations (USA, CFR), chapter 1, subchapter J.

• HP E2749 User's Guide (this book).

#### Option 010:

• 2-meter optical cable

#### Option 011:

• 2-meter coaxial copper cable with 9-pin D-type connector

#### **Option 0B1:**

• additional HP E2749 User's Guide

#### Accessories available from other suppliers:

• Longer Fibre Channel cables are available from:

AMP, 800-522-6752 or W.L. Gore & Associates, 800-531-6064

The following length restrictions apply:

Optical cables up to 500 m (850 nm multimode laser,  $50\mu m$  core diameter) Coaxial copper cables up to 30 m ( $150\Omega$  STP connector)

• Compatible Fibre Channel products are available from Systran Corporation, 800-252-5601. Systran Corporation also has a Web site at www.systran.com (For more information on Systran products, see the chapter "Using the HP E2749A with Systran FibreXpress Products.")

## To install the HP E2749

#### Caution

To protect circuits from static discharge, observe anti-static techniques whenever handling the HP E2749 Fibre Channel Interface Module.

The HP E2749 Fibre Channel Interface can be used in a wide variety of VXI system configurations. The VXI system may use an embedded controller (PC or UNIX), or an external controller connected to the VXI system using an HP-IB, VXLink, or MXIbus interface. Your application program controlling the system may be written in HP-VEE, HP-BASIC, C, Visual Basic, or some other language.

To verify the installation of the HP E2749 module, you must send the "\*TST?" query command to the module and read the module's response. Refer to the documentation provided with your application programming language for information on sending commands and reading responses from the module.

- 1 Set up your VXI mainframe. See the installation guide for your mainframe.

- **2** Select a slot in the VXI mainframe for the HP E2749 module.

The HP E2749 module receives local bus ECL-level data from the module immediately to its left. If you will be transmitting data from other modules, place the HP E2749 immediately to the right of those modules. If you will be receiving data to be used by other modules, place the HP E2749 immediately to the left of those modules.

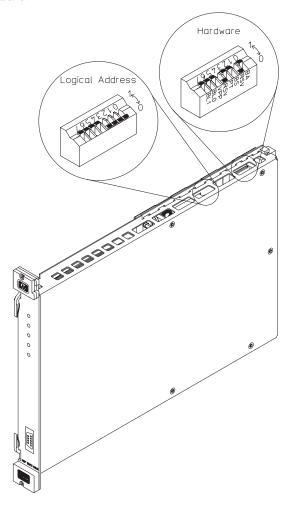

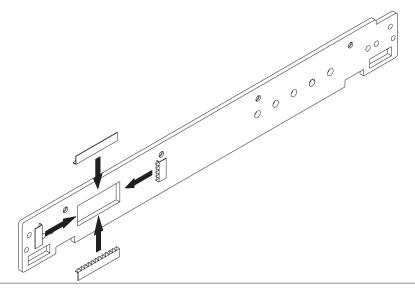

**3** Using a small screwdriver or similar tool, set the Logical Address configuration switch on the HP E2749.

(See the illustration on previous page.) Each module in the system must have a unique logical address. The factory default setting is 1111 0000 (240). If an HP E1485A Signal Processor Module will be controlling the HP E2749 module, select an address within the HP E1485A module's servant area. If an HP-IB command module will be controlling the HP E2749 module, select an address that is a multiple of 8.

**4** Using a small screwdriver or similar tool, set the switches in the Hardware switchpack to 11101101.

(See the illustration on previous page.) The firmware uses switch BA to configure the Fibre Channel data buffers. If the HP E2749A will be primarily transmitting data, set switch BA to ON (1) to allocate more memory for output buffers and less memory to input buffers. Conversely, if the HP E2749A will be primarily receiving data, set switch BA to OFF (0) to allocate more memory for receive buffers.

The BS (boot source) switch determines the behavior of the module's firmware at power-up. BS must be in the ON (normal) position for proper operation.

VPP enables the programming power supplies to programmable ROMs in the module. VPP must be in the ON (service) position to set the module's Fibre Channel WWN. See the chapter titled "SCPI Command Reference" for more information (SYST:COMM:WWN[:SELF]:ADDR command).

RSV (reserved) switches must be set to 0.

| <b>Buffer Allocation Optimiz</b> | Power-On Test |                               | Bus Request Level |         |     |     |

|----------------------------------|---------------|-------------------------------|-------------------|---------|-----|-----|

|                                  | BA            |                               | PT                |         | BLO | BL1 |

| Transmit                         | 1             | Long                          | 1                 | Level 0 | 0   | 0   |

| Receive                          | 0             | Short                         | 0                 | Level 1 | 0   | 1   |

| Boot Source                      |               | <b>ROM Programming Enable</b> |                   | Level 2 | 1   | 0   |

|                                  | BS            |                               | VPP               | Level 3 | 1   | 1   |

| Normal                           | 1             | Service                       | 1                 |         |     |     |

| Service                          | 0             | Normal                        | 0                 |         |     |     |

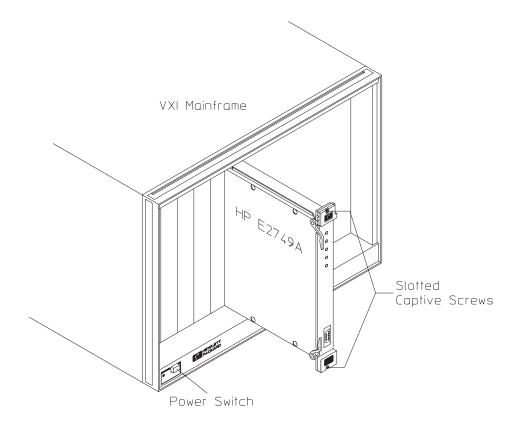

**1** Set the mainframe's power switch to standby or off( $\delta$ ).

### Caution

Installing or removing the module with the power on may damage components in the module.

- **2** Place the module's card edges (top and bottom) into the module guides in the slot.

- **3** Slide the module into the mainframe until the module connects firmly with the backplane connectors. Make sure the module slides in straight.

- **4** Attach the module's front panel to the mainframe chassis using the module's captive mounting screws.

## To store the module

Store the module in a clean, dry, and static free environment.

For other requirements, see storage and transport restrictions in the document: *HP E2749 Fibre Channel Interface Module Technical Specifications*.

## To transport the module

# Package the module using the original factory packaging or packaging identical to the factory packaging.

Containers and materials identical to those used in factory packaging are available through Hewlett-Packard offices.

# If returning the module to Hewlett-Packard for service, attach a tag describing the following:

- Type of service required

- Return address

- Model number

- Full serial number

In any correspondence, refer to the module by model number and full serial number.

#### Mark the container FRAGILE to ensure careful handling.

# If necessary to package the module in a container other than original packaging, observe the following (use of other packaging is not recommended):

- Wrap the module in heavy paper or anti-static plastic.

- Protect the front panel with cardboard.

- Use a double-wall carton made of at least 350-pound test material.

- Cushion the module to prevent damage.

#### Caution

Do not use styrene pellets in any shape as packing material for the module. The pellets do not adequately cushion the module and do not prevent the module from shifting in the carton. In addition, the pellets create static electricity which can damage electronic components.

2

Verifying the HP E2749

## To verify the HP E2749

You can perform a quick verification of the basic functions of the HP E2749 using the built-in self-test function.

The test uses the command «ff-ff"

See the chapter titled "SCPI Command Reference" for syntax and details.

If the test fails, the A1 assembly is probably faulty. See the chapter titled "Replacing Assemblies," for information on replacing the module.

The "\*TST?\*" test does not test the module's ability to transmit and receive over Fibre Channel. When the HP E2749 has been connected to the Fibre Channel loop or fabric, you can verify the ability to transmit and receive using the "DIAGNOSTIC:FIBRE:LOOPBACK" command. This command performs a loopback test. See the chapter titled "SCPI Command Reference" for more information.

3

Replacing Assemblies

## Replaceable Parts

For information on upgrading your module or replacing parts, contact your local Hewlett-Packard sales and service office. See the inside back cover of this guide for a list of office locations and addresses.

### **Ordering Information**

To order a part listed in the table, quote the Hewlett-Packard part number (HP Part Number) and the check digit (CD). Indicate the quantity required and address the order to the nearest Hewlett-Packard sales and service office (see the inside back cover of this guide). The check digit verifies that an order has been transmitted correctly, ensuring accurate and timely processing of the order. The first time a part is listed in the table, the quantity column (Qty) lists the total quantity of the part used in the module. For the corresponding name and location of the manufacturer's codes shown in the tables, see "Code Numbers."

#### Caution

The module is static sensitive. Use the appropriate precautions when removing, handling, and installing to avoid unnecessary damage.

#### **Direct Mail Order System**

Within the U.S.A., Hewlett-Packard can supply parts through a direct mail order system. Advantages of the Direct Mail Order System are:

- Direct ordering and shipment from the HP Parts Center.

- No maximum or minimum on any mail order. There is a minimum order for parts ordered through a local HP sales and service office when the orders require billing and invoicing.

- Transportation charges are prepaid. A small handling charge is added to each order.

- No invoicing. A check or money order must accompany each order.

- Mail order forms and specific ordering information are available through your local Hewlett-Packard sales and service office. See the inside back cover of this guide for a list of Hewlett-Packard sales and service office locations and addresses.

#### **Code Numbers**

The following table provides the name and location for the manufacturers' code numbers (Mfr Code) listed in the replaceable parts tables.

| Mfr No. | Mfr Name                        | Location                 |  |

|---------|---------------------------------|--------------------------|--|

| 28480   | Hewlett-Packard Company         | Palo Alto, CA U.S.A.     |  |

| 30817   | Instrument Specialties Co. Inc. | Placentia, CA U.S.A.     |  |

| 03647   | Instrument Specialties Co. inc. | Del Water Gap, GA U.S.A. |  |

| 01380   | Amp Inc.                        | Harrisburg, PA U.S.A.    |  |

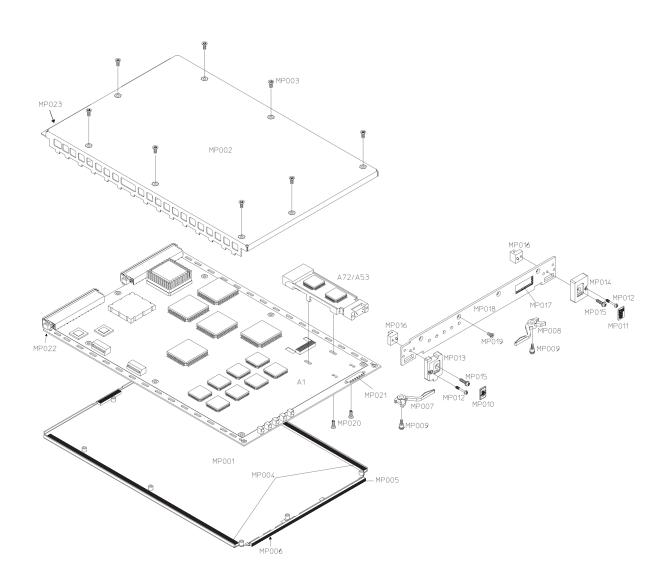

## Assemblies

| Ref<br>Des | HP Part<br>Number | CD | Qty | Description              | Mfr<br>Code | Mfr Part<br>Number |

|------------|-------------------|----|-----|--------------------------|-------------|--------------------|

| A1         | E2749-66501       | 5  | 1   | PC ASSEM, EXCHANGE BRD.  | 28480       | E2749-66501        |

| A72        | 1005-0372         | 2  | 1   | CON-MODULE COAX          | 28480       | 1005-0372          |

| A53        | 1005-0353         | 9  | 1   | CON-MODULE FIBER OP.     | 28480       | 1005-0353          |

| MP001      | E1437-00203       | 7  | 1   | SHTF CVR-BTTM            | 28480       | E1437-00203        |

| MP002      | E2749-00201       | 4  | 1   | SHTF CVR-TOP             | 28480       | E2749-00203        |

| MP003      | 0515-1135         | 7  | 8   | SCR-MCH M3.0 25M         | 28480       | 0515-1135          |

| MP004      | E1485-40601       | 1  | 2   | GSKT-RFI, BOTTOM COVER   | 28480       | E1485-40601        |

| MP005      | E1485-40602       | 2  | 2   | GSKT RFI-FRONT PANEL     | 28480       | E1485-40602        |

| MP006      | 8160-0686         | 6  | 2   | STMP FINGERS-RFI         | 30817       | 786-185            |

| MP007      | E1400-45101       | 5  | 1   | MOLD, HANDLE LEFT        | 28480       | E1400-45101        |

| MP008      | E1400-45102       | 6  | 1   | MOLD, HANDLE RIGHT       | 28480       | E1400-45102        |

| MP009      | E1400-00610       | 7  | 2   | SCR-ASM SHLDR            | 28480       | E1400-00610        |

| MP010      | E1400-84308       | 6  | 1   | LABEL-HP, LOGO           | 28480       | E1400-84308        |

| MP011      | E1400-84307       | 5  | 1   | LABEL-VXI, LOGO          | 28480       | E1400-84307        |

| MP012      | 0515-2733         | 3  | 2   | SCR-MCH M2.5 17          | 28480       | 0515-2733          |

| MP013      | E1400-45011       | 6  | 1   | MOLD LBUT-ECL            | 28480       | E1400-45011        |

| MP014      | E1400-45008       | 1  | 1   | MOLD BOTTOM-LOGO         | 28480       | E1400-45008        |

| MP015      | 0515-0664         | 5  | 2   | SCR-MCH M3.0 12M         | 28480       | 0515-0664          |

| MP016      | E1400-40104       | 8  | 2   | CAST                     | 28480       | E1400-40104        |

| MP017      | 8160-0683         | 3  | 4   | STMP STRP-SPNG F         | 03647       | 0097-551-17-X      |

| MP018      | E2749-00203       | 6  | 1   | PANEL-FRONT,"E2749A"     | 28480       | E2749-00204        |

| MP019      | 0515-1946         | 8  | 4   | SCR-MCH M3.0 6MM         | 28480       | 0515-1946          |

| MP020      | 0515-2508         | 0  | 2   | SCR-TAP                  | 28480       | 0515-2508          |

| MP021      | 8160-0467         | 1  | 2   | STMP RFI FNGRS 8         | 28480       | 8160-0467          |

| MP022      | E1450-01202       | 5  | 4   | STMP SHLD-RFI GRND       | 28480       | E1450-01202        |

| MP023      | 8160-0634         | 4  | 2   | STMP BE/CU GROUND        | 03647       | 0097-0611-17       |

|            | 8120-8640         | 4  | 1   | CBL-ASM DUPLX OPTION 010 | 01380       | 504971-2           |

|            | 8120-8639         | 1  | 1   | CBL-ASM CXL OPTION 011   | 01380       | 621771-3           |

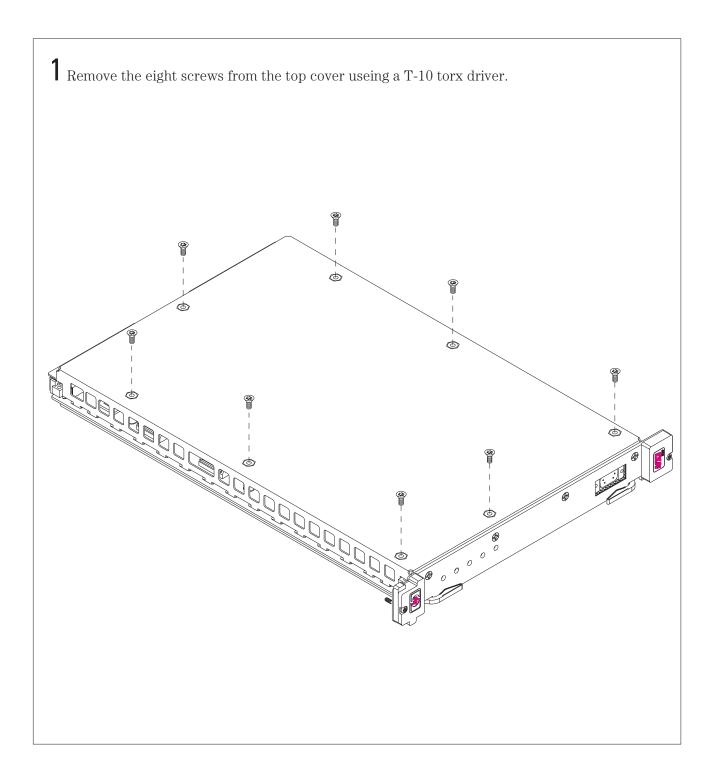

# To remove the top and bottom covers

Remove the four screws that attach the top cover to the front panel using a T-10 torx driver. Remove covers.

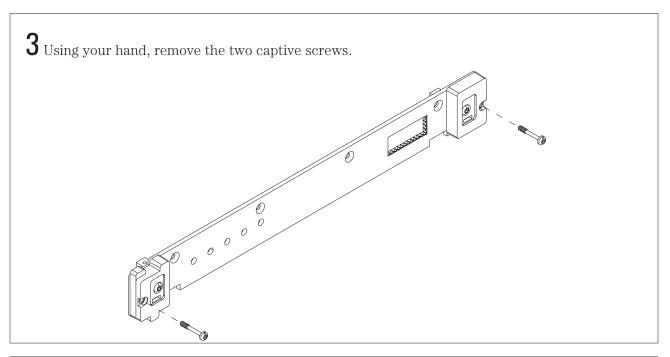

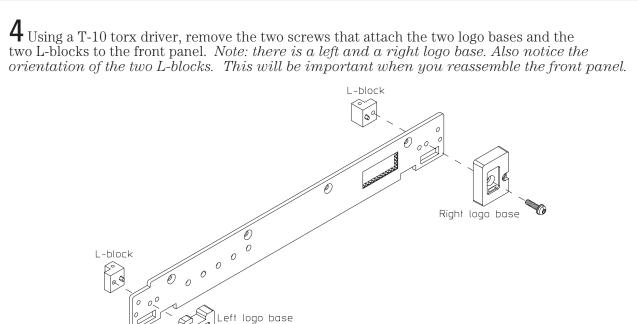

# To remove the front panel

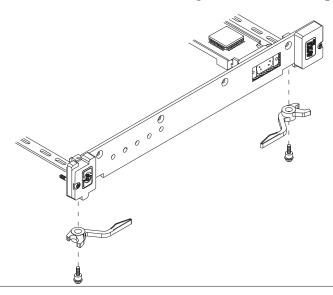

1 Remove covers (see "To remove the top and bottom covers"). Using a T-8 torx driver, remove the two screws that attach the handles to the assembly. Note: be sure to label the two handles, which are different from each other. This will aid you in reassembling the module.

**2** Note: steps 2, 3, 4, and 5 are only necessary if you need to replace the front panel or any of its components. Using an X-acto knife, gently pry the labels from the two keys

**5** Using an X-acto knife, gently pry the RFI Strips from the rear of the front panel. Note: there are 12 sections on the top and bottom and 5 sections on each side. This may be important when ordering new strips.

# To remove the A72/A53 assembly (GLM)

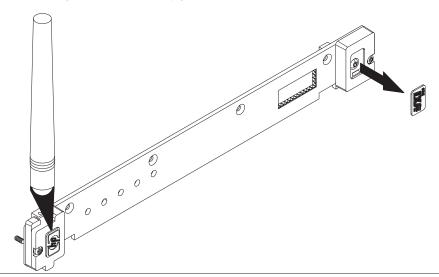

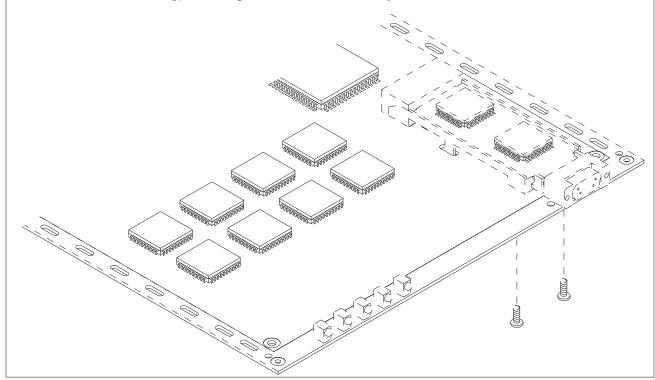

1 Remove covers (see "To remove the top and bottom covers"). Remove the front panel (see step 1 of "To remove the front panel"). Using a T-8 torx driver remove the 2 screws that attach the A72/A53 (GLM) assembly to the A1 main assembly. Remove assembly. Note: the illustration shows the A72 assembly, but the procedure is the same for both.

# To remove the A1 main assembly

1 Remove covers (see "To remove the top and bottom covers"). Remove the front panel (see step 1 of "To remove the front panel"). Remove the A72/A53 assembly (see "To remove the A72/A53 assembly).

4

Backdating

# Backdating

This chapter will document modules that differ from those currently being produced. With the information provided in this chapter, this guide can be modified so that it applies to any earlier version or configuration of the module.

5

Hardware Description

# General description

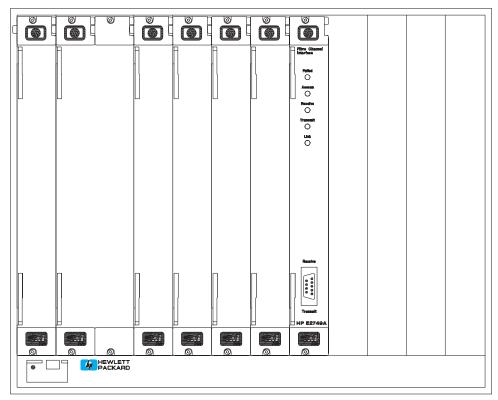

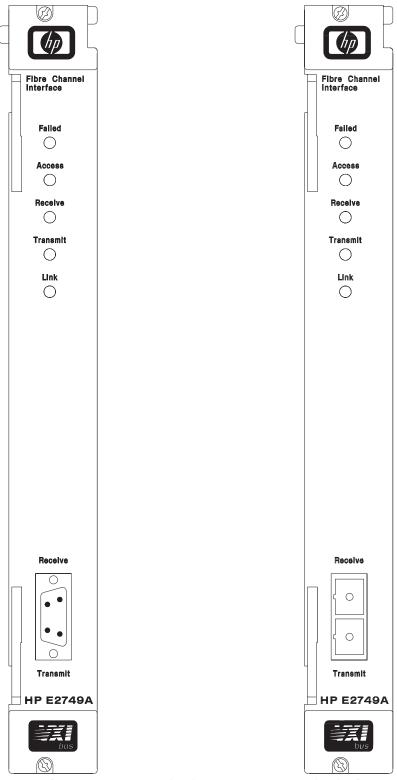

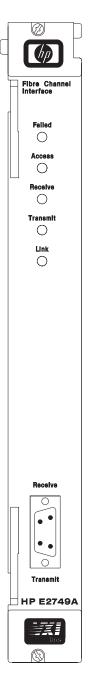

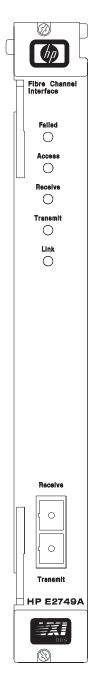

The HP E2749 Fibre Channel Interface Module occupies a single-wide C-size slot in a VXI mainframe. The module is available with either coaxial copper (standard) or optical (option 001) front panel connectors.

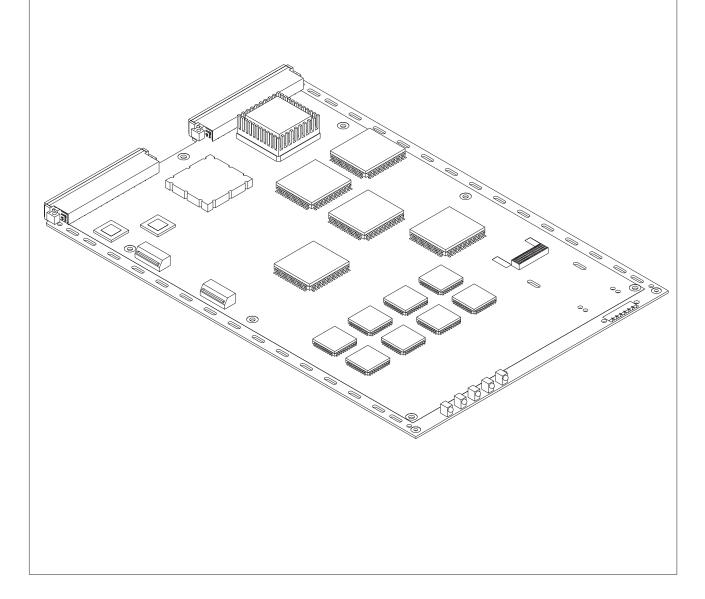

Figure 5-1: HP E2749 Fibre Channel Interface Module

## Circuit description

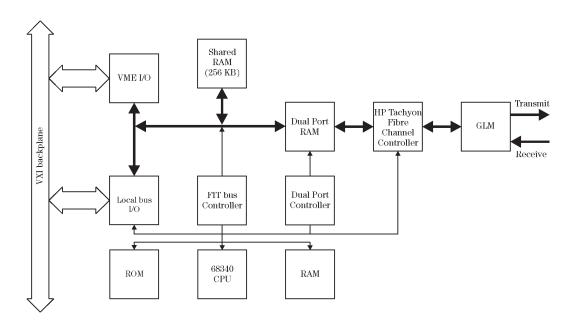

The HP E2749 includes an HP Tachyon Fibre Channel Controller chip, an interface between the Tachyon chip and the local (P2) and VXI (P1) buses, and a CPU to direct the data transfer operations. The module receives and transmits data through a Gigabit Link Module (GLM) with either coaxial copper (standard) or optical (option 001) connectors. The GLM provides the Fibre Channel FC-0 layer solution (see "Fibre Channel Overview" for more information).

Data to be transferred over Fibre Channel can come from either the local bus, the VXI bus, via VME shared memory, or any combination of these sources, under control of a programmable sequencer built into the HP E2749. Dedicated hardware in the HP E2749 moves this data into a high-speed, dual port memory. From dual-port memory, the data goes to the HP Tachyon Fibre Channel chip, where data is encoded from 8-bit internal bytes into 10-bit Fibre Channel transmission characters. The encoded data passes through the GLM to Fibre Channel.

Data coming into the HP E2749 from Fibre Channel enters through the GLM to the HP Tachyon chip, where the data is decoded from 10-bit Fibre Channel characters into 8-bit internal bytes. From there the data goes to dual-port memory, then to the local bus, the VXI bus, or VME shared memory.

Figure 5-2: Block diagram of the HP E2749

## HP E2749 front-panel description

#### **Status LEDs**

- Failed lights briefly when powering up and normally goes out after a few seconds. If it stays on it indicates a hardware failure in the module.

- Access lights when the module is being accessed via the VXI backplane.

- Receive lights when the module is receiving data via Fibre Channel.

- Transmit lights when the module is transmitting data via Fibre Channel.

- *Link* lights when a connection has been established between the module and another Fibre Channel device.

#### **Receive/Transmit Connectors**

The Receive/Transmit connectors on the HP E2749 are part of the gigabit per second link module (GLM) which interfaces between the Fibre Channel network and the main board.

The standard GLM has a coaxial copper interface with a 9-pin D-type connector.

The option 001 GLM has an optical interface with a duplex SC connector.

Figure 5-3: Front panel - HP E2749A standard and HP E2749A Option 001

6

Using the HP E2749

### Introduction

One of the key features of VXI systems is the high-speed transfer of data (up to 100 Mbytes/s) over the local bus between modules in the same mainframe. Until recently, transferring data between VXI mainframes and other devices was considerably slower. A typical data transfer rate for a module on the VXIbus or MXI bus is 2 to 4 Mbytes/s. HP-IB has a maximum data transfer rate of about 1 Mbyte/sec, and the transfer rate might be even slower because HP-IB protocol limits the transfer speed to that of the slowest device on the bus.

The HP E2749 Fibre Channel Interface module provides rapid transfer of broadband data to and from a VXI mainframe. Now you can perform external data transfers at rates up to 41 Mbytes/sec. For example, the HP E2749A can transfer full-speed 16-bit data from an HP E1437A sampling at 20 Msamples/sec. This is equivalent to a transfer rate of 40 Mbytes/sec.

Some typical applications are transferring data between VXI mainframes, from a VXI mainframe to VME, or from a VXI mainframe to a PC.

#### Note

If you will be transferring data between VXI mainframes, each mainframe must include a controller in slot 0.

This chapter gives you a brief introduction to SCPI, VXI, and Fibre Channel. If you would like more information, here are a few publications you might find useful:

- Feeling Comfortable with VXI, available from Hewlett-Packard, publication number 5965-6497E.

- "An Introduction to Fibre Channel," Meryem Primmer, *HP Journal*, October 1996, 94-98.)

- Fibre Channel: A Technical Description, Fibre Channel Association, available from Systran Corporation, 4126 Linden Avenue, Dayton, OH 45432.

- Fibre Channel Association's Web site, http://www.amdahl.com/ext/CARP/FCA/FCA.html

- "Fibre Channel: Gigabit Communications and I/O for Computer Networks," Alan F. Benner, McGraw-Hill, ISBN 0-07-005669-2.

- Feeling Comfortable with VXI, available from Hewlett-Packard, publication number 5965-6497E.

### HP E2749 and SCPI

You control the HP E2749 by sending commands using a language called *Standard Commands for Programmable Instruments*, or *SCPI*. SCPI is a closely defined, but broadly accepted, standard instrument command language. See chapter 8, "Programming the HP E2749 with SCPI," and chapter 9, "SCPI Command Reference," for detailed information on how to use SCPI to control the HP E2749.

#### **SCPI** commands

The following is an overview of the some of the capabilities of the HP E2749 controlled by SCPI commands. See chapter 8, "Programming the HP E2749 with SCPI" and chapter 9, "SCPI Command Reference" for details.

#### **Sequence**

The SEQuence subsystem, SEQuence[1|2|3|4], specifies the order of operations for transmitting or receiving data. Synchronization and control operations are provided for both transmit and receive.

The fields contained in every element of the Sequence list are: operation, count, address, and miscellaneous. The operation field specifies the action to be done: data transfer, synchronization, or control. The count field is used by many operations to indicate the size of the transfer. The unit of count is sometimes bytes and sometimes blocks — see the description of the operation to determine which. The address field is used by operations which do VME data transfers. The value of address is an offset from the beginning of one of the address spaces. The miscellaneous field has various meanings depending upon the operation. Not every operation uses all fields, but every Sequence element contains all four fields. Fields which are not used should be set to zero.

The Sequence operations labeled as synchronization or control may be used in either receive or transmit Sequences. They are intended to help provide synchronization between the Sequence and the devices or application program which generate/receive the data.

See the chapter titled "Using Sequence Operations with the HP E2749" for details on using Sequence commands.

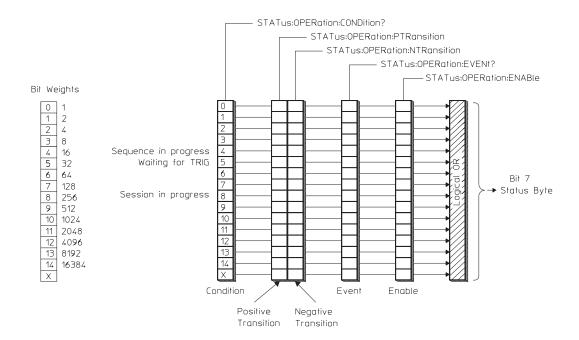

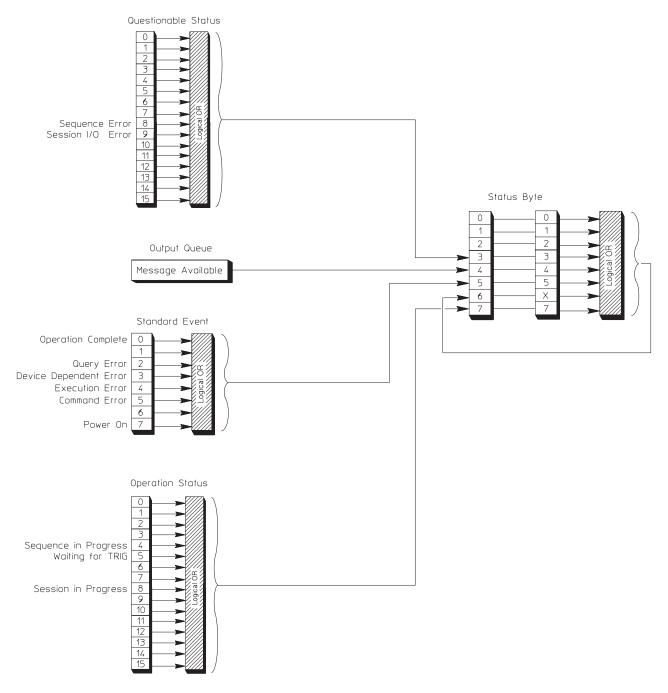

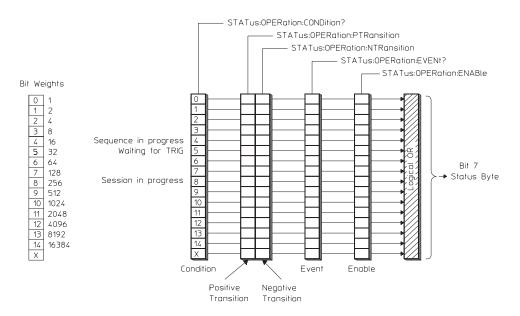

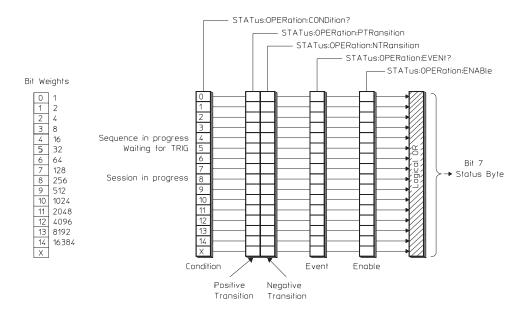

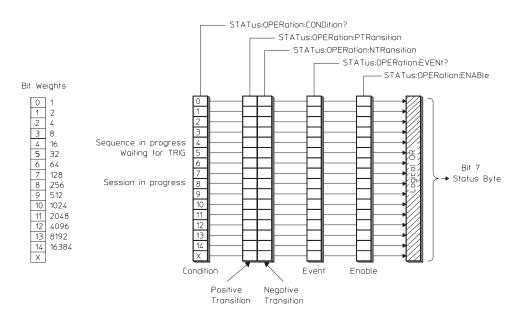

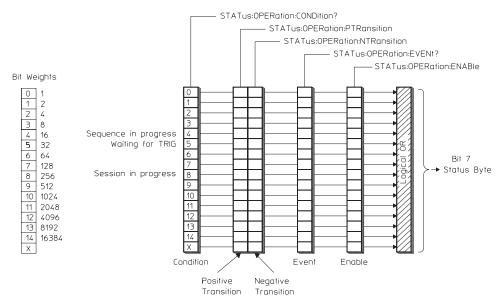

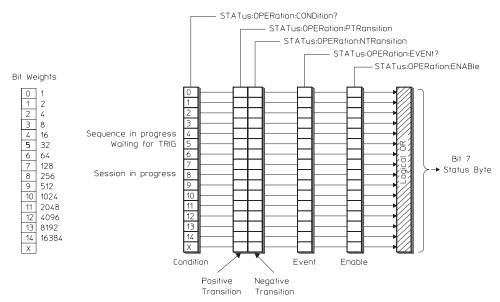

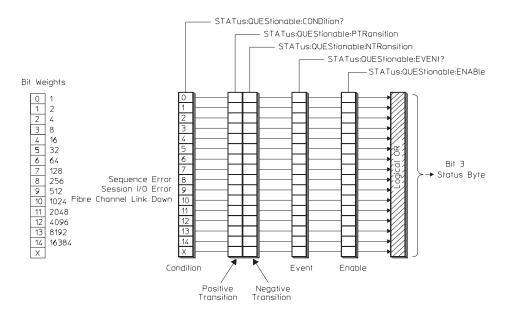

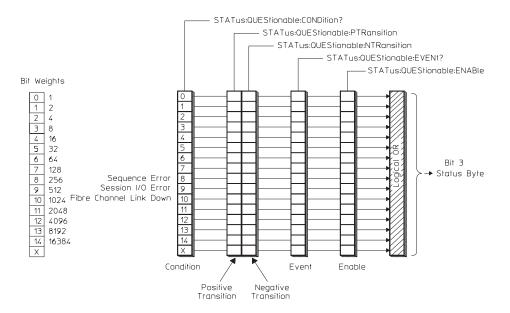

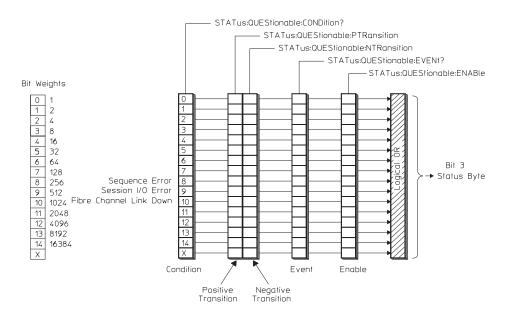

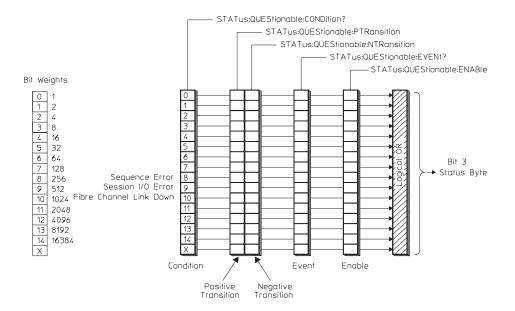

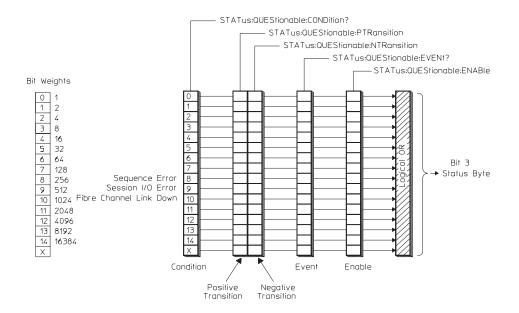

#### Operation status register

The subsystem which refers to the operation status register is STATus:OPERation. These commands provide the necessary commands to interface with the operation register.

For more information about the operation status register and other status registers, see the chapter titled "Programming the HP E1562 with SCPI."

#### Address space

The VXI system architecture defines three types of address space. A16 space consists of 64 KBytes, A24 is 16 MBytes, and A32 is 4 GBytes.

The HP E2749 has access to A16, A24, and A32 space through a 16-bit port. Or, if devices support it, it can also use a 32-bit port using D32.

#### **Shared memory**

Shared memory provides a way for the HP E2749 to transfer data to a controller. The shared memory in the HP E2749 is mapped to the A24 VXI address space. The controller can then access that same address space to receive or write data. Note that if SCPI commands or Sequences refer to shared memory in the HP E2749, the addresses begin at zero. However if they refer to shared memory in the A24 space, they may begin at a different value, depending on how the A24 memory has been allocated among devices.

#### The VXI registers

The HP E2749 uses the following VXI registers:

- Offset Register

- Status/Control Register

- Device Type Register

- ID/Logical Address Register

- Data Low Register

- Response/Data Extended Register

- Protocol/Signal Register

These registers are common to all message-based VXI devices. Refer to Chapter 8, "Programming the HP E2749 with SCPI," or to VXI documentation for more information.

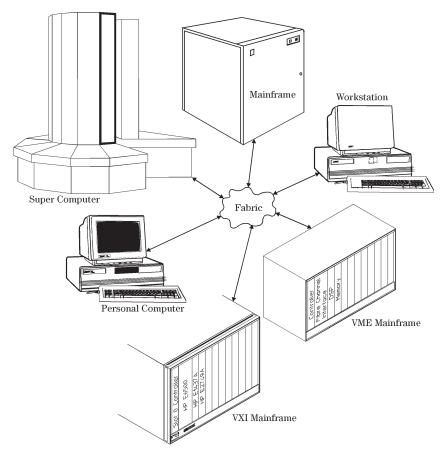

### Fibre Channel overview

Fibre Channel is a standard, efficient, generic transport mechanism whose primary task is to transport data at the fastest possible speeds and with the least possible delay. It provides high-speed interconnection, communication, and data transfer among heterogeneous systems and peripherals, including workstations, mainframes, supercomputers, desktop computers, and storage devices. Fibre Channel handles both networking and peripheral I/O communication over a single channel using the same drivers, ports, and adapters for both types of communication.

Fibre Channel is structured as a set of hierarchical functions that support a number of existing protocols, but it does not have a native I/O command set. It is not a high-level protocol, but does contain a low-level protocol for managing link operations. Fibre Channel is not concerned with the content of user data being transported. Networking and I/O protocols are mapped to Fibre Channel constructs, then encapsulated and transported within Fibre Channel frames. The main purpose of Fibre Channel is to have any number of existing protocols operate over a variety of physical media and existing cable plants.

Fibre Channel has many advantages over existing communication systems:

- High speed—from 2.5 to 250 times faster than existing communications interfaces.

- Small connectors.

- Longer-distance operation—up to 500 m for the HP E2749.

- Multi-user—an addressing limit of  $2^{24}$ , more than 16 million addresses.

- Protocol independent.

The next few pages contain an overview of Fibre Channel. For more detailed information, see the Fibre Channel publications listed in the introduction to this chapter.

### Fibre Channel topologies

Fibre Channel supports three types of interconnection topologies: point-to-point, arbitrated loop, and fabric.

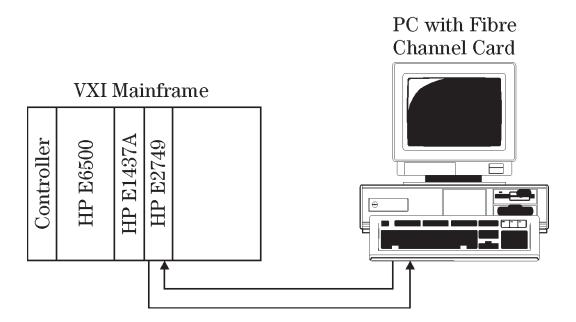

Point-to-point is a direct connection between two ports, such as between a VXI mainframe and a PC controller. This is the default interconnection.

Suppose you want to transfer data from an HP E1437 to a PC for post-processing. You would connect the VXI mainframe directly to a PC, a point-to-point connection.

Figure 6-1: Fibre Channel point-to-point connection

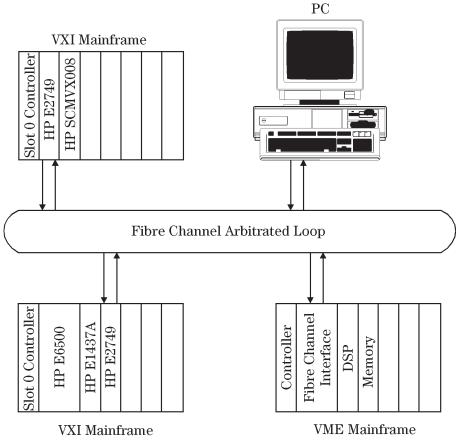

An arbitrated loop connects multiple (up to 127) devices without hubs or switches. Each device makes a request for use of the loop when it needs to communicate with another device on the loop. When the loop is free, a bidirectional connection is established between the two devices. This is the most common type of Fibre Channel interconnection.

A Fibre Channel arbitrated loop might include a personal computer, a VME mainframe, and two VXI mainframes.

Data is transmitted from the source Fibre Channel module to Fibre Channel and received by the destination Fibre Channel module. Suppose you want to transfer data from the HP E1437 module in the lower VXI mainframe to the VME DSP module for post-processing. The HP E1437 data would pass through the HP E2749 module in the VXI mainframe, onto the arbitrated loop, and through the VME Fibre Channel module to the DSP module.

Figure 6-2: Fibre Channel arbitrated loop

HP E2749 User's Guide Using the HP E2749

The third topology is called a fabric. The fabric is one or more switching elements that operate much like a telephone exchange. Each device on the system connects to the fabric at a node, and the fabric manages the connections between nodes. A fabric theoretically can have up to  $2^{24}$  nodes, so the fabric is the best topology for connecting large numbers of devices or for complex configurations.

Figure 6-3: Fibre Channel fabric

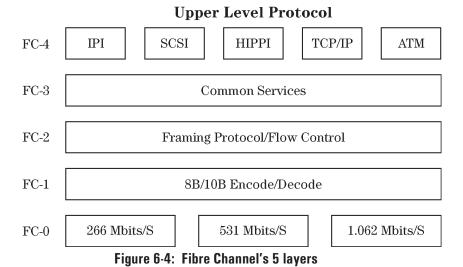

#### Fibre Channel's multilevel structure

Fibre Channel is organized into five functional levels:

- FC-0 defines physical characteristics of the media for various signaling rates.

- FC-1 defines the transmission protocol, including data encoding and decoding, byte synchronization, and character-level error control.

- FC-2 defines the signaling protocol, including the hierarchical structure of frames, sequences, and exchanges, which is the data transport mechanism used by Fibre Channel. This level also manages the three classes of service provided by Fibre Channel.

- FC-3 defines a set of common services. This layer is still being formulated.

- FC-4 defines the mapping of upper level protocol (ULP) to services of the lower three layers. For example, the Fibre Channel protocol for SCSI, known as FCP, defines a Fibre Channel mapping layer that uses the services of the lowest three Fibre Channel layers to transmit SCSI command, data, and status information between a SCSI initiator and a SCSI target.

The lowest three levels define the Fibre Channel Physical standard (FC-PH). FC-3 and FC-4 handle interfaces between FC-PH and other network protocols and applications. The HP E2749 provides all of FC-PH and layer FC-4.

The HP E2749A supports only one upper level protocol—Systran Corporation's FibreXpress Lightweight Protocol (FXLP).

7

Using Sequence Operations with the HP E2749

# Sequence overview

### What is a Sequence?

A Sequence is a list of data transfer, control, and synchronization operations. Each data transfer operation identifies the source or destination of data in the VXI chassis and the amount of data to be transferred. Control and synchronization operations are used to coordinate the activity of Sequence with the application program or with hardware modules installed in the VXI chassis.

Transmit Sequences are used to collect data from modules in the VXI chassis using the VXI bus or the Local Bus and transmit the data over Fibre Channel to a receiving application.

Receive Sequences are used to distribute data received from a transmitting application over Fibre Channel to modules in the VXI chassis using the VXI bus or the Local Bus. A receive Sequence can be used to either distribute received data over the Local Bus or the VXI bus but not both.

A Sequence may perform either transmit or receive operations; transmit and receive operations cannot be mixed within the same sequence. The behavior of a receive operation encountered when using the sequence to transmit is undefined. Conversely, the behavior of a transmit operation encountered when using the sequence to receive is undefined. The behavior of a receive sequence is also undefined if it contains both VXI bus and Local Bus operations. Both transmit and receive Sequences may contain control, and synchronization operations.

### **Loading and starting Sequences**

Up to four Sequences may be loaded into the HP E2749 but only one can run at a time. A Sequence is loaded into the HP E2749 using the "SEQuence:ADD" SCPI command. The Sequence is started using the "SEQuence:BEGin" SCPI command. The first parameter of the "SEQ:BEG" command determines whether the sequence is being used to transmit or receive data and the second parameter identifies the total number of bytes to transfer. If the total number of bytes to transfer specified in the "SEQ:BEG" command is greater than the total number of bytes specified in the list of data transfer operations in the sequence, the sequence will be executed multiple times until the transfer count from "SEQ:BEG" command is satisfied.

#### **Creating Sequences**

#### **Adding Sequence elements**

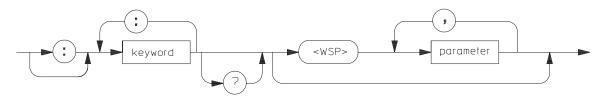

Sequence operations are loaded into the HP E2749 by using the SCPI command:

```

\rightarrow \Box^{V}_{T}5/8 - \frac{1}{8}5/8F_{T}{}^{O} - \frac{1}{2} + \frac{1}{4} + \frac{1

```

Each time this command is issued an element representing one operation is added to the end of the Sequence queue in memory. The maximum number of operations in a single sequence is 100.

If the Sequence number [1|2|3|4] is not specified the Sequence element is added to Sequence 1.

#### Required fields

Every Sequence element requires that all four fields: (<Operation>,<Count>,<Address>,<Misc>) be filled though not every operation uses all fields. For some Sequence operations certain fields represent two pieces of information as indicated in the Sequence operation descriptions.

The <Operation> field specifies what type of action will take place: data transfer, synchronization, or control. This value corresponds to the code listed in the programming reference section of this chapter for the specific type of operation.

The <Count> field is used by many operations to indicate how many units will be transferred. The unit of <Count> may be either bytes or blocks, as indicated in the description of each operation. For some Sequence operations this field represents two pieces of information as indicated in the Sequence operation descriptions.

The <Address> field is used mainly by operations which transfer data over the VXI System Bus. The value of <Address> is an offset from the beginning of one of the address spaces. The Shared RAM space is local to the HP E2749.

The miscellaneous <Misc> field has various meanings depending on the operation.

#### **Accepted Field Values**

Field values must be specified as numeric values. All decimal representations, including signs, decimal points, and scientific notation are accepted as field values:

123, 123E2, -123, -1.23E2, .123, 1.23E-2, 1.23000E-01

Note, however, that negative numbers will generate an error and fractional values will be automatically rounded to the nearest integer.

The fields may be specified in decimal, hex (#h prefix), octal (#q prefix), or binary (#b prefix):

123, #h7B, #q173, #b1111011

#### **Related SCPI commands**

Other SCPI commands in addition to SEQuence:ADD which can or must be used with relation to Sequence operations are documented in detail in the SCPI programming section of this book. These commands include:

- MMEMory:SESSion:PROTocol which selects the communication protocol to be used for the data transfer.

- SEQuence:BEGin which starts Sequence execution.

- SEQuence:DELete:ALL which deletes all operations from the current Sequence list. This command should be sent before adding elements to a Sequence.

- SEQuence:SIZE? which returns the number of elements in the Sequence.

# Sequence quick reference

|                    | Operation                 | Code<br>(hex) | Count        | Address     | Misc       |

|--------------------|---------------------------|---------------|--------------|-------------|------------|

| Control operations | 3                         |               |              |             |            |

|                    | Do nothing                | 0000          | N/A          | N/A         | N/A        |

|                    | Terminate Sequence        | 0001          | N/A          | N/A         | N/A        |

|                    | Pause N msec              | 0002          | Milliseconds | N/A         | N/A        |

|                    | Pause N loops             | 000a          | Loops        | N/A         | N/A        |

|                    | Execute new Sequence      | 0004          | Seq nbr      | N/A         | N/A        |

|                    | New Sequence if count     | 0005          | Seq nbr      | MSB         | LSB        |

|                    | TTLTRG control            | 0003          | Bit field    | N/A         | N/A        |

|                    | TTLTRG arm                | 0006          | Bit field    | N/A         | N/A        |

|                    | TTLTRG wait               | 0007          | Bit field    | N/A         | N/A        |

|                    | IRQ arm                   | 0008          | Bit field    | N/A         | N/A        |

|                    | IRQ wait                  | 0009          | Bit field    | N/A         | N/A        |

|                    | Test shared RAM Skip      | 7000          | N/A          | RAM address | Skip count |

| Synchronization o  | perations                 |               |              |             |            |

|                    | Wait Bit Set A16          | 6000          | Bit mask     | A16 address | Loops      |

|                    | Wait Bit Clear A16        | 6001          | Bit mask     | A16 address | Loops      |

|                    | Wait Bit Set A24          | 6002          | Bit mask     | A24 address | Loops      |

|                    | Wait Bit Clear A24        | 6003          | Bit mask     | A24 address | Loops      |

|                    | Wait Bit Set A32          | 6004          | Bit mask     | A32 address | Loops      |

|                    | Wait Bit Clear A32        | 6005          | Bit mask     | A32 address | Loops      |

|                    | Wait Bit Set Shared RAM   | 6006          | Bit mask     | RAM address | Loops      |

|                    | Wait Bit Clear Shared RAM | 6007          | Bit mask     | RAM address | Loops      |

|                    | Wait A16 Count 16         | 6008          | 16 bit value | A16 address | Loops      |

|                    | Wait A24 Count 16         | 6009          | 16 bit value | A24 address | Loops      |

|                    | Wait A32 Count 16         | 600A          | 16 bit value | A32 address | Loops      |

|                    | Wait Count Shared RAM 16  | 600B          | 16 bit value | RAM address | Loops      |

| Wait A16 Count 32                       | 0000 |                |              |                           |

|-----------------------------------------|------|----------------|--------------|---------------------------|

|                                         | 600C | 32 bit value   | A16 address  | Loops                     |

| Wait A24 Count 32                       | 600D | 32 bit value   | A24 address  | Loops                     |

| Wait A32 Count 32                       | 600E | 32 bit value   | A32 address  | Loops                     |

| Wait Count Shared RAM 32                | 600F | 32 bit value   | RAM address  | Loops                     |

| Control A16 Reg16                       | 6018 | N/A            | A16 address  | Value                     |

| Control A24 Reg16                       | 6019 | N/A            | A24 address  | Value                     |

| Control A32 Reg16                       | 601A | N/A            | A32 address  | Value                     |

| Control Reg Shared RAM 16               | 601B | N/A            | RAM address  | Value                     |

| Control A16 Reg 32                      | 601C | N/A            | A16 address  | Value                     |

| Control A24 Reg 32                      | 601D | N/A            | A24 address  | Value                     |

| Control A32 Reg 32                      | 601E | N/A            | A32 address  | Value                     |

| Control Reg Shared RAM 32               | 601F | N/A            | RAM address  | Value                     |

| Dump A24 Seq Bytes                      | 6020 | N/A            | A24 address  | N/A                       |

| Dump A32 Seq Bytes                      | 6021 | N/A            | A32 address  | N/A                       |

| Dump Shared RAM Seq Bytes               | 6022 | N/A            | RAM address  | N/A                       |

| ransmit local bus data to Fibre Channel |      |                |              |                           |

| Lbus Consume                            | 1000 | Lbus blocks    | N/A          | Lbus width<br>Bytes/block |

| Lbus Eavesdrop                          | 1001 | Lbus blocks    | N/A          | Lbus width<br>Bytes/block |

| Fransmit VXI bus data to Fibre Channel  |      |                |              |                           |

| Read A16 Buff 16                        | 3000 | Transfer bytes | A16 address  | N/A                       |

| Read A16 Buff 32                        | 3001 | Transfer bytes | A 16 address | N/A                       |

| Read A16 Buff D32                       | 3002 | Transfer bytes | A16 address  | N/A                       |

| Read A24 Buff 16                        | 3003 | Transfer bytes | A24 address  | N/A                       |

| Read A24 Buff 32                        | 3004 | Transfer bytes | A24 address  | N/A                       |

| Read A24 Buff D32                       | 3005 | Transfer bytes | A24 address  | N/A                       |

| Read A32 Buff 16                        | 3006 | Transfer bytes | A32 address  | N/A                       |

| Read A32 Buff 32                        | 3007 | Transfer bytes | A32 address  | N/A                       |

HP E2749 User's Guide Using Sequence Operations with the HP E2749

| Operation                                                     | Code<br>(hex) | Count          | Address     | Misc                      |

|---------------------------------------------------------------|---------------|----------------|-------------|---------------------------|

| Read A32 Buff D32                                             | 3008          | Transfer bytes | A32 address | N/A                       |

| Read A16 FIFO 16                                              | 3009          | Transfer bytes | A16 address | N/A                       |

| Read A16 FIFO 32                                              | 300A          | Transfer bytes | A16 address | N/A                       |

| Read A16 FIFO D32                                             | 300B          | Transfer bytes | A16 address | N/A                       |

| Read A24 FIFO 16                                              | 300C          | Transfer bytes | A24 address | N/A                       |

| Read A24 FIFO 32                                              | 300D          | Transfer bytes | A24 address | N/A                       |

| Read A24 FIFO D32                                             | 300E          | Transfer bytes | A24 address | N/A                       |

| Read A32 FIFO 16                                              | 300F          | Transfer bytes | A32 address | N/A                       |

| Read A32 FIFO 32                                              | 3010          | Transfer bytes | A32 address | N/A                       |

| Read A32 FIFO D32                                             | 3011          | Transfer bytes | A32 address | N/A                       |

| Read Shared RAM                                               | 3012          | Transfer bytes | RAM address | N/A                       |

| Dummy Bytes                                                   | 3100          | Pad bytes      | N/A         | N/A                       |

| ransmit local bus data to Fibre Channel, and monitor the data |               |                |             |                           |

| Lbus Consume Monitor Shared RAM                               | 5000          | Lbus blocks    | RAM address | Lbus width<br>Bytes/block |

| Lbus Eavesdrop Monitor Shared RAM                             | 5001          | Lbus blocks    | RAM address | Lbus width<br>Bytes/block |

| Lbus Consume Monitor A24                                      | 5014          | Lbus blocks    | A24 address | Lbus width<br>Bytes/block |

| Lbus Eavesdrop Monitor A24                                    | 5015          | Lbus blocks    | A24 address | Lbus width<br>Bytes/blocl |

| ransmit VXI bus data to Fibre Channel, and monitor the data   |               |                |             |                           |

| Read Shared RAM Monitor Shared RAM                            | 3812          | Monitor bytes  | RAM address | RAM addres                |

| Read Shared RAM Monitor A24 Buff D32                          | 3912          | Monitor bytes  | RAM address | A24 addres                |

| Read Shared RAM Monitor A24 Buff                              | 3a12          | Monitor bytes  | RAM address | A24 addres                |

| Read A16 FIFO D32 Monitor Shared RAM                          | 380b          | Monitor bytes  | A16 address | RAM addres                |

| Read A16 FIFO D32 Monitor A24 Buff D32                        | 390b          | Monitor bytes  | A16 address | A24 addres                |

| Read A16 FIFO D32 Monitor A24 Buff                            | 3a0b          | Monitor bytes  | A16 address | A24 addres                |

| Read A16 FIFO16 Monitor Shared RAM                            | 3809          | Monitor bytes  | A16 address | RAM addre                 |

| Read A16 FIFO16 Monitor A24 Buff D32                          | 3909          | Monitor bytes  | A16 address | A24 addres                |

| Operation                                              | Code<br>(hex) | Count          | Address     | Misc                       |

|--------------------------------------------------------|---------------|----------------|-------------|----------------------------|

| Read A16 FIFO16 Monitor A24 Buff                       | 3a09          | Monitor bytes  | A16 address | A24 address                |

| Read A16 Buff 16 Monitor Shared RAM                    | 3800          | Monitor bytes  | A16 address | RAM address                |

| Read A16 Buff 16 Monitor A24 BuffD32                   | 3900          | Monitor bytes  | A16 address | A24 address                |

| Read A16 Buff 16 Monitor A24 Buff                      | 3a00          | Monitor bytes  | A16 address | A24 address                |

| Read A16 Buff D32 Monitor Shared RAM                   | 3802          | Monitor bytes  | A16 address | RAM address                |

| Read A16 Buff D32 Monitor A24 Buff D32                 | 3902          | Monitor bytes  | A16 address | A24 address                |

| Read A16 Buff D32 Monitor A24 Buff                     | 3a02          | Monitor bytes  | A16 address | A24 address                |

| Read A24 FIFO D32 Monitor Shared RAM                   | 380e          | Monitor bytes  | A24 address | RAM address                |

| Read A24 FIFO D32 Monitor A24 Buff D32                 | 390e          | Monitor bytes  | A24 address | A24 address                |

| Read A24 FIFO D32 Monitor A24 Buff                     | 3a0e          | Monitor bytes  | A24 address | A24 address                |

| Read A24 FIFO 16 Monitor Shared RAM                    | 380c          | Monitor bytes  | A24 address | RAM address                |

| Read A24 FIFO 16 Monitor A24 Buff D32                  | 390c          | Monitor bytes  | A24 address | A24 address                |

| Read A24 FIFO 16 Monitor A24 Buff                      | 3a0c          | Monitor bytes  | A24 address | A24 address                |

| Read A24 Buff 16 Monitor Shared RAM                    | 3803          | Monitor bytes  | A24 address | RAM address                |

| Read A24 Buff 16 Monitor A24 Buff D32                  | 3903          | Monitor bytes  | A24 address | A24 address                |

| Read A24 Buff 16 Monitor A24 Buff                      | 3a03          | Monitor bytes  | A24 address | A24 address                |

| Read A24 Buff D32 Monitor Shared RAM                   | 3805          | Monitor bytes  | A24 address | RAM address                |

| Read A24 Buff D32 Monitor A24 Buff D32                 | 3905          | Monitor bytes  | A24 address | A24 address                |

| Read A24 Buff D32 Monitor A24 Buff                     | 3a05          | Monitor bytes  | A24 address | A24 address                |

| Receive data from Fibre Channel and write to local bus |               |                |             |                            |

| Lbus Generate                                          | 2000          | Lbus blocks    | N/A         | Lbus width-<br>Bytes/block |

| Lbus Append                                            | 2001          | Lbus blocks    | N/A         | Lbus width-<br>Bytes/block |

| Receive data from Fibre Channel and write to VXI bus   |               |                |             |                            |

| Write A16 Buff 16                                      | 4000          | Transfer bytes | A16 address | N/A                        |

| Write A16 Buff 32                                      | 4001          | Transfer bytes | A16 address | N/A                        |

| Write A16 Buff D32                                     | 4002          | Transfer bytes | A16 address | N/A                        |

| Write A24 Buff 16                                      | 4003          | Transfer bytes | A24 address | N/A                        |

HP E2749 User's Guide Using Sequence Operations with the HP E2749

| Operation          | Code<br>(hex) | Count          | Address     | Misc |

|--------------------|---------------|----------------|-------------|------|

| Write A24 Buff 32  | 4004          | Transfer bytes | A24 address | N/A  |

| Write A24 Buff D32 | 4005          | Transfer bytes | A24 address | N/A  |

| Write A32 Buff 16  | 4006          | Transfer bytes | A32 address | N/A  |

| Write A32 Buff 32  | 4007          | Transfer bytes | A32 address | N/A  |

| Write A32 Buff D32 | 4008          | Transfer bytes | A32 address | N/A  |

| Write A16 FIFO 16  | 4009          | Transfer bytes | A16 address | N/A  |

| Write A16 FIFO 32  | 400A          | Transfer bytes | A16 address | N/A  |

| Write A16 FIFO D32 | 400B          | Transfer bytes | A16 address | N/A  |

| Write A24 FIFO 16  | 400C          | Transfer bytes | A24 address | N/A  |

| Write A24 FIFO 32  | 400D          | Transfer bytes | A24 address | N/A  |

| Write A24 FIFO D32 | 400E          | Transfer bytes | A24 address | N/A  |

| Write A32 FIFO 16  | 400F          | Transfer bytes | A32 address | N/A  |

| Write A32 FIFO 32  | 4010          | Transfer bytes | A32 address | N/A  |

| Write A32 FIFO D32 | 4011          | Transfer bytes | A32 address | N/A  |

| Write Shared RAM   | 4012          | Transfer bytes | RAM address | N/A  |

| Bit Bucket         | 4100          | Discard bytes  | N/A         | N/A  |

|                    |               |                |             |      |

# HP E2749 Sequence operations

The following pages contain detailed descriptions of each sequence operation. The operations are listed in numerical (code) order. If you do not know the operation code, there are two ways to find the operation description:

- Scan through the quick reference tables beginning on page 7-6. The operations are listed by type, and the code is in the second column.

- Look up the operation name in the index, which will refer you to the correct page in this chapter.

Do Nothing 0000

No Sequence operation is performed

**Sequence Syntax:** #h0000,<Count>,<Address>,<Misc>

<Count> ::= 0

<Address> ::= 0

<Misc> ::= 0

SCPI example: SEQ:ADD #h0000,0,0,0

**Description:** No fields are used.

# **Terminate Sequence**

0001

The Sequence stops executing.

**Sequence Syntax:** #h0001,<Count>,<Address>,<Misc>

<Count> ::= 0

<Address> ::= 0

<Misc> ::= 0

SCPI example: SEQ:ADD #h0001,0,0,0

**Description:** This operation terminates the Sequence even if the final count has not been met.

This is useful only for creating a non-looping or one-time Sequence. No fields are

used.

Pause N msec 0002

The Sequence stops executing for a designated period of time.

**Sequence Syntax:** #h0002,<Count>,<Address>,<Misc>

<Count> ::= 10:4294967295

<Address> ::= 0

<Misc> ::= 0

**SCPI example:** SEQ:ADD #h0002,40,0,0

**Description:** This operation causes the Sequence to stop executing for the number of

milliseconds designated by <Count>. The resolution of the clock is only  $10~\rm msec$ , therefore the specified count is rounded to the nearest  $10~\rm msec$  value. For a pause

of shorter duration see the 'Pause N loops' operation (000a).

### **TTLTRG Control**

0003

Controls the assertion of the TTLTRG lines.

**Sequence Syntax:** #h0003,<Count>,<Address>,<Misc>

<Count> ::= 0:#b11111111

<Address> ::= 0

<Misc> ::= 0

**SCPI example:** SEQ:ADD #h0003,#b1010101,0,0

**Description:** All TTLTRG lines are controlled simultaneously. Therefore, one (or more) lines may

be set while all others are cleared. Any bits set to 1 in bits 0-7 of <Count> represent

corresponding TTLTRG lines which are asserted.

<Address> and <Misc> are not used.

See the related TTLTRG Arm (0006) and TTLTRG Wait (0007) operations.

# **Execute New Sequence**

0004

Begins executing a new logical Sequence.

**Sequence Syntax:** #h0004,<Count>,<Address>,<Misc>

<Count> ::= 1:4

<Address> ::= 0

<Misc> ::= 0

SCPI example: SEQ:ADD #h0004,3,0,0

**Description:** This operation begins executing the new logical Sequence specified by <Count>.

The new Sequence inherits the Sequence type and total bytes remaining from the currently executing Sequence. This operation is useful in situations which require a one-time set of operations at the beginning of a transmit followed by a looping set of data acquisition operations. An example of such a one-time action is writing a

header at the beginning of a data stream.

# **New Sequence If Count**

0005

Begins executing a new logical Sequence if the remaining byte count is less than the value specified.

**Sequence Syntax:**

#h0005,<Count>,<Address>,<Misc>

<Count> ::= 1:4

<Address> ::= 0:#hFFFFFFF

<Misc> ::= 0:#hFFFFFFFF

**SCPI** example:

SEQ:ADD #h0005,2,#hAEC,#h33E1F671

**Description:**

This operation begins executing the new logical Sequence number specified by <Count> if the remaining byte count is less than that specified by <Address> and <Misc>. Since the byte count is a 64-bit value and the Sequence fields are only 32-bit values, both the <Address> and <Misc> are used to specify the byte count. The most significant 32 bits are specified in the <Address> field and the least significant 32 bits are specified in the <Misc> field. The new Sequence inherits the Sequence type and total bytes remaining from the currently executing Sequence.

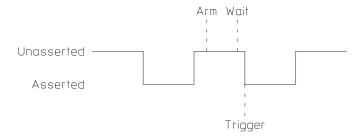

TTLTRG Arm 0006

Clears a set of latched TTLTRG assertions.

**Sequence Syntax:** #h0006,<Count>,<Address>,<Misc>

<Count> ::= 0:#b11111111

<Address> ::= 0

<Misc> ::= 0

**SCPI example:** SEQ:ADD #h0006,#b11011101,0,0

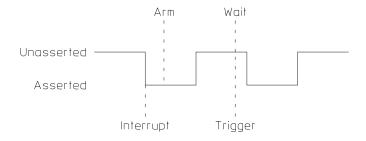

**Description:**

Clearing latched TTLTRG assertions guarantees that any subsequent TTLTRG Wait will not be satisfied by an old latched TTLTRG assertion. Any bits set to 1 in bits 0-7 of <Count> clear assertions for corresponding to TTLTRG lines. The diagram below illustrates the effect of TTLTRG Arm and TTLTRG Wait on triggering in response to TTLTRG line assertion:

A perceived exception occurs if the trigger line is already asserted (set to the low voltage level) when the TTLTRG arm command is issued. In this case a subsequent TTLTRG Wait will result in no delay because the assertion requirement was previously fulfilled by the interrupt generated prior to TTLTRG Arm:

<Address> and <Misc> are not used.

See the related TTLTRG Control (0003) and TTLTRG Wait (0007) operations.

TTLTRG Wait 0007

Waits for a set of TTLTRG lines to be asserted.

**Sequence Syntax:** #h0007,<Count>,<Address>,<Misc>

<Count> ::= 0:#b11111111

<Address> ::= 0

<Misc> ::= 0

**SCPI example:** SEQ:ADD #h0007,#b10101010,0,0

**Description:** Because TTLTRG assertions are latched, it is not necessary that all of the specified

lines be set at the same time; only that each specified line undergo an

unasserted-to-asserted transition since the last TTLTRG Wait or TTLTRG Arm operation. Any bits set to 1 in bits 0-7 of <code><Count></code> represent corresponding

TTLTRG lines which await assertion. <Address> and <Misc> are not used.

See the related TTLTRG Control (0003) and TTLTRG Arm (0006) operations.

**IRQ Arm** 0008

Clears a set of latched IRQ assertions from a specified logical address.

**Sequence Syntax:** #h0008,<Count>,<Address>,<Misc>

<Count> ::= 0:255

<Address> ::= 0

<Misc> ::= 0

**SCPI example:** SEQ:ADD #h0008,86,0,0

**Description:** Clearing latched IRQ assertions guarantees that any subsequent IRQ Wait will not be

satisfied by an old latched IRQ assertion. The <Count> field indicates the logical

address for which the latched IRQ should be cleared.

IRQ Wait 0009

Waits for IRQ from a specific logical address.

**Sequence Syntax:** #h0009,<Count>,<Address>,<Misc>

<Count> ::= 1:255

<Address> ::= 0

<Misc> ::= 0

**SCPI example:** SEQ:ADD #h0009,222,0,0

**Description:** When a VXI system is configured, each IRQ line is assigned an IRQ Handler. The

IRQ Handler may be any device which supports this capability. In order for the HP E2749 to proceed after executing the IRQ Wait Sequence operation, it must receive and IRQ from the specific logical address on any IRQ line for which it has been assigned as IRQ Handler. See the documentation for your VXI Resource

Manager to determine how to assign IRQ Handlers.

# Pause N loops

000a

The Sequence stops executing for a designated number of loops.

**Sequence Syntax:** #h0002,<Count>,<Address>,<Misc>

<Count> ::= 1:4294967295

<Address> ::= 0

<Misc> ::= 0

SCPI example: SEQ:ADD #h000a,10,0,0

**Description:** This operation causes the Sequence to execute a delay loop for the number of

repetitions designated by <Count>. This operation may be used to pause a Sequence for a shorter duration of time than may be achieved with the 'Pause N milliseconds' (0002) operation for which the minimum time is 10 milliseconds. A <Count> of 1560927 results in a delay of  $\geq$  1 second. The actual delay time may be

longer due to the unpredictable nature of interrupts.

Lbus Consume 1000

A transmit operation which reads blocks of data from the local bus and transmits them to the Fibre Channel output.

**Sequence Syntax:** #h1000,<Count>,<Address>,<Misc>

<Count> ::= 1:256

<Address> ::= 0

<Misc> ::= 0:3 #h10:#hFFFF (see description below)

**SCPI example:** SEQ:ADD #h1000,8,0,#h03000800

**Description:** The Lbus Consume operation puts the local bus chip into a mode which acts as a sink for bytes on the local bus. In other words no bytes are passed to the next

module to the right.

<Count> indicates the number of local bus blocks to transfer.

<Address> is not used.

<Misc> contains two pieces of information: the lower 24 bits indicate the number of bytes in a local bus block; the upper 8 bits indicate the local bus width. The value indicating the local bus width is presented as the number of bytes minus 1:

| Bits 24-31 of I       | Misc parameter                          | Bits 0-23 of Misc parameter                                                                                     |

|-----------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| A local bus width of: | Is represented by a parameter value of: | This value represents the number of bytes in a local bus block. Every local bus block is assumed to be the same |

| 8                     | 0                                       | size and equal to the count specified here.                                                                     |

| 16                    | 1                                       |                                                                                                                 |

| 24                    | 2                                       |                                                                                                                 |

| 32                    | 3                                       |                                                                                                                 |

The bytes-per-block value is used to decrement the bytes-remaining count, thus determining when the final Sequence count has been met. The number of bytes per block must be specified correctly in order for the Sequence to terminate properly.

### Lbus Eavesdrop

1001

A transmit operation which reads blocks of data from the local bus and transmits them to the Fibre Channel output in addition to passing them along to the next local bus module to the right.

**Sequence Syntax:**

#h1001,<Count>,<Address>,<Misc>

<Count> ::= 1:256

<Address> ::= 0

<Misc> ::= 0:3 #h10:#hFFFF (see description below)

**SCPI example:**

SEQ:ADD #h1001,2,0,#h3004000

**Description:**

The Lbus Eavesdrop operation puts the local bus chip into a mode in which each byte received from the module to the left is transmitted through the HP E2749 to Fibre Channel and is also passed to the next module to the right.

<Count> indicates the number of local bus blocks to transfer.

<Address> is not used.

<Misc> contains two pieces of information: the lower 24 bits indicate the number of bytes in a local bus block; the upper 8 bits indicate the local bus width. The value indicating the local bus width is presented as the number of bytes minus 1:

| Bits 24-31 of N       | Aisc parameter                          | Bits 0-23 of Misc parameter                                                                                     |  |  |

|-----------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|

| A local bus width of: | Is represented by a parameter value of: | This value represents the number of bytes in a local bus block. Every local bus block is assumed to be the same |  |  |

| 8                     | 0                                       | size and equal to the count specified here.                                                                     |  |  |

| 16                    | 1                                       |                                                                                                                 |  |  |

| 24                    | 2                                       |                                                                                                                 |  |  |

| 32                    | 3                                       |                                                                                                                 |  |  |

The bytes-per-block value is used to decrement the bytes-remaining count, thus determining when the final Sequence count has been met. The number of bytes per block must be specified correctly in order for the Sequence to terminate properly.

# Lbus Generate 2000

A receive operation which reads blocks of data from the Fibre Channel input then writes them to the local bus.

**Sequence Syntax:** #h2000,<Count>,<Address>,<Misc>

**Description:**

<Count> ::= 1:256

<Address> ::= 0

<Misc> ::= 0:3 #h10:#hFFFC (see description below)

**SCPI example:** SEQ:ADD #h2000,16,0,#h03000c00

The Lbus Generate operation causes data to flow from the Fibre Channel input to the next module to the right of the HP E2749. This operation can only be used for local bus receive Sequences.

<Count> indicates the number of local bus blocks to transfer.

<Address> is not used.

<Misc> contains two pieces of information: the lower 24 bits indicate the number of bytes in a local bus block; the upper 8 bits indicate the local bus width. The value indicating the local bus width is presented as the number of bytes minus 1:

| Bits 24-31 of I       | Visc parameter                          | Bits 0-23 bits of Misc parameter                                                                                  |

|-----------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| A local bus width of: | Is represented by a parameter value of: | This value represents the number of bytes in a local bus block and must be a multiple of 4. Every local bus block |

| 8                     | 0                                       | is assumed to be the same size and equal to the count specified here.                                             |

| 16                    | 1                                       |                                                                                                                   |

| 24                    | 2                                       |                                                                                                                   |

| 32                    | 3                                       |                                                                                                                   |

A block marker is asserted on the local bus following every block-size number of bytes. A frame marker is placed following the last block written to the local bus by this Sequence operation.

# Lbus Append

2001

A receive operation which reads blocks of data from the Fibre Channel input then appends them to the local bus stream of blocks.

**Sequence Syntax:**

#h2001,<Count>,<Address>,<Misc>

<Count> ::= 1:256

<Address> ::= 0

<Misc> ::= 0:3 #h10:#hFFFC (see description below)

**SCPI** example:

SEQ:ADD #h2001,4,0,#h03000800

**Description:**

The Lbus Append operation causes data to flow from the Fibre Channel input and appends the data to the end of an Lbus frame as it passes to the next module to the right of the HP E2749. This operation can only be used for local bus receive Sequences.

<Count> indicates the number of local bus blocks to transfer.

<Address> is not used.

<Misc> contains two pieces of information: the lower 24 bits indicate the number of bytes in a local bus block; the upper 8 bits indicate the local bus width. The value indicating the local bus width is presented as the number of bytes minus 1:

| Bits 24-31 of 1       | Visc parameter                          | Bits 0-23 of Misc parameter                                                                                       |

|-----------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| A local bus width of: | ls represented by a parameter value of: | This value represents the number of bytes in a local bus block and must be a multiple of 4. Every local bus block |

| 8                     | 0                                       | is assumed to be the same size and equal to the count specified here.                                             |

| 16                    | 1                                       |                                                                                                                   |

| 24                    | 2                                       |                                                                                                                   |

| 32                    | 3                                       |                                                                                                                   |

A block marker is asserted on the local bus following every block-size number of bytes. A frame marker is placed following the last block written to the local bus by this Sequence operation.

### Read A16 Buff 16 – Read Shared RAM

3000-3012

Transmit operations which read data from a memory buffer or FIFO and transmit to the Fibre Channel output.

**Sequence Syntax:**

#h3000,<Count>,<Address>,<Misc>

through

#h3012, <Count>, <Address>, <Misc>

<Count> ::= 4:#hFFFFFFC

A16 <Address> ::= 0:#hFFFE

A24 <Address> ::= 0:#hFFFFE

A32 <Address> ::= 0:#hFFFFFFE

Shared RAM <Address> ::= 0:262144

<Misc> ::= 0

**SCPI** example:

SEQ:ADD #h300B,#h10000,#hD420,0

**Notes:**

Refer to the Sequence Quick Reference part of this chapter (beginning on page 7-6) for a list of all 19 operations included in this description.

${\bf Description:}$

This description covers 19 operations for which some essential properties are indicated in the operation name. Buff indicates a memory buffer whereas FIFO refers to reading from the same address as if reading from a FIFO. The buffer or FIFO corresponds to the address space specified in the name: A16, A24, A32, or Shared RAM. The last part of the operation name refers to an access type: a 16-bit access, a 32-bit access implemented as two 16-bit accesses, or a D32 access. The D32 access applies only to devices which support D32. Shared RAM is always accessed as a 16-bit buffer.

<Count> designates the number of bytes to transfer and must be a multiple of 4.

<Address> designates an offset in the specified memory space (A16, A24, A32, or Shared RAM) at which memory will be accessed. The value must be a multiple of 2.

<Misc> is not used.

# **Transmit Dummy Bytes**

3100

A transmit operation which places dummy bytes in the data stream.

**Sequence Syntax:** #h3100,<Count>,<Address>,<Misc>

<Count> ::= 0:#hFFFFFFFC

<Address> ::= 0

<Misc> ::= 0

**SCPI example:** SEQ:ADD #h3100,#h10000,0,0

**Description:** This operation is used to add padding to certain data structures in the data stream

to make it compatible with some post-processing programs which expect data in a

certain location.

<Count> designates the number of dummy bytes to place in the data stream and

must be a multiple of 4.

### Read Shared RAM Monitor Shared RAM -Read A24 Buff D32 Monitor A24 Buff

3812-3a05

Transmit operations which read data from the VXI bus and transmit to the Fibre Channel output while providing a means for the host computer to monitor the data.

**Sequence Syntax:**

#h3812, <Count>, <Address>, <Misc>

through

#h3a05,<Count>,<Address>,<Misc>

<Count> ::= 4:#hFFFFFFFF

A16 <Address> ::= 0:#hFFFF

A24 <Address> ::= 0:#hFFFFFF

Shared RAM <Address> ::= 0:262144

A24 <Misc> ::= 0:#hFFFFFF

Shared RAM < Misc > ::= 0:262144

**SCPI** example:

SEQ:ADD #h3a00,#h200,#h400,#h8000

Note:

Refer to the Sequence Quick Reference part of this chapter (beginning on page 7-6) for a list of all 27 operations included in this description.

**Description:**

This description covers 27 operations for which some essential properties are indicated in the operation name:

The address location indicated in the operation name before the word 'Monitor' represents the memory location from which to draw data. The address location indicated in the operation name after the word 'Monitor' represents the memory location to which to monitor data.

Buff indicates a memory buffer whereas FIFO refers to reading from the same address as if reading from a FIFO. The buffer or FIFO corresponds to the address space specified in the name: A16, A24, A32, or Shared RAM.

<Count> is the number of bytes to monitor

<Address> is the VXI address from which to read data.

<Misc> is the VXI address to which to monitor data

# Write A16 Buff 16 – Write Shared RAM

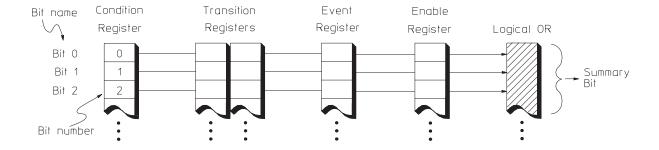

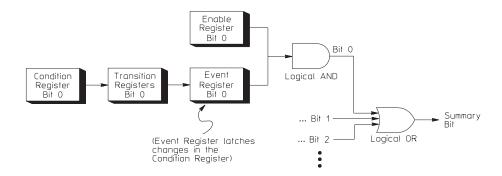

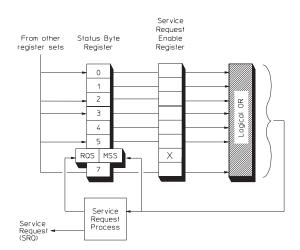

4000-4012