# **HP SCMVX008 Option 040**

## **4-Channel DDR TIM-40 Board**

## **Programmer's Guide**

Part Number VX008-90010+

Printed in U.S.A.

Print Date: TBD, 1998

© Hewlett-Packard Company 1997. All rights reserved.

8600 Soper Hill Road Everett, Washington 98205-1298 U.S.A.

## **NOTICE**

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MANUAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or direct, indirect, special, incidental or consequential damages in connection with the furnishing, performance, or use of this material.

### **Warranty**

*A copy of the specific warranty terms applicable to your Hewlett-Packard product and replacement parts can be obtained from your local Sales and Service Office.*

### **Restricted Rights Legend**

Use, duplication, or disclosure is subject to HP standard commercial license terms or to the following restrictions, whichever is applicable:

- For non-DoD Departments and Agencies of the U.S. Government, as set forth in FAR 52.227-19(c)(1-2)(Jun 1987);

- For the DoD and its Agencies, as set forth in DFARS 252.227-7013 (c) (1) (ii) (Oct 1988), or DFARS 252.221-7015(c) (May 1991), whichever is applicable.

HEWLETT-PACKARD COMPANY

3000 Hanover St.

Palo Alto, CA 94304

©Copyright 1997, 1998 Hewlett-Packard Company. All rights Reserved

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another language without the prior written consent of Hewlett-Packard Company. The information contained in this document is subject to change without notice.

Use of this manual and flexible disk(s) or tape cartridge(s) supplied for this pack is restricted to this product only. Additional copies of the programs can be made for security and back-up purposes only. Resale of the software in its present form or with alterations is expressly prohibited.

### **Printing History**

Edition 1: January, 1998

---

# Table of Contents

|                                 |    |

|---------------------------------|----|

| <b>Introduction</b>             | 1  |

| Overview .....                  | 2  |

| Requirements .....              | 2  |

| Terminology .....               | 3  |

| Definition of Terms .....       | 3  |

| Acronyms/Abbreviations .....    | 3  |

| <b>Hardware Installation</b>    | 4  |

| Installing TIM-40 Modules ..... | 4  |

| Jumpers .....                   | 5  |

| Clock Jumper .....              | 5  |

| Comm Port Jumper .....          | 5  |

| DDR Comm Port .....             | 6  |

| Comm Port Selection .....       | 6  |

| Audio (DAC) Outputs .....       | 7  |

| <b>Software Installation</b>    | 8  |

| Windows 95/NT .....             | 8  |

| HP-UX 9.0x .....                | 8  |

| Directories and Files .....     | 9  |

| Windows 95/NT Directories ..... | 9  |

| HP-UX Directories .....         | 10 |

| Example Program .....           | 11 |

| Hardware Configuration .....    | 11 |

| Running HP Radio .....          | 13 |

| DDR Groups .....                | 14 |

| Example Configurations .....    | 14 |

| 4-channel, 4ch/DSP .....        | 15 |

| 8-channel, 4ch/DSP .....        | 16 |

| 16-channel, 8ch/DSP .....       | 17 |

| 24-channel, 12ch/DSP .....      | 18 |

| 16-channel, 4ch/DSP .....       | 19 |

## Table of Contents

|                                                                                   |    |

|-----------------------------------------------------------------------------------|----|

| <b>System Software Development</b>                                                | 20 |

| Overview .....                                                                    | 20 |

| Software Requirements .....                                                       | 20 |

| Hardware Requirements .....                                                       | 21 |

| HPVX8 Library .....                                                               | 22 |

| Program Development .....                                                         | 23 |

| Grouping .....                                                                    | 23 |

| System Definition .....                                                           | 23 |

| Host $\leftrightarrow$ Target and Target $\leftrightarrow$ Target Messaging ..... | 24 |

| Host $\leftarrow$ target Commands .....                                           | 24 |

| Host Functions .....                                                              | 26 |

| Host Programming Example .....                                                    | 28 |

| Target Functions .....                                                            | 30 |

| Target Programming Example .....                                                  | 32 |

| DDR Interface Programming .....                                                   | 32 |

| DDR Programming Example .....                                                     | 40 |

| HP Radio Target Program .....                                                     | 43 |

| Reference Documentation .....                                                     | 43 |

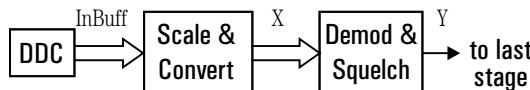

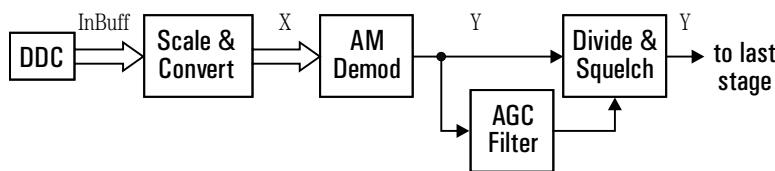

| Data Flow .....                                                                   | 44 |

| VX8 Shared Bus .....                                                              | 49 |

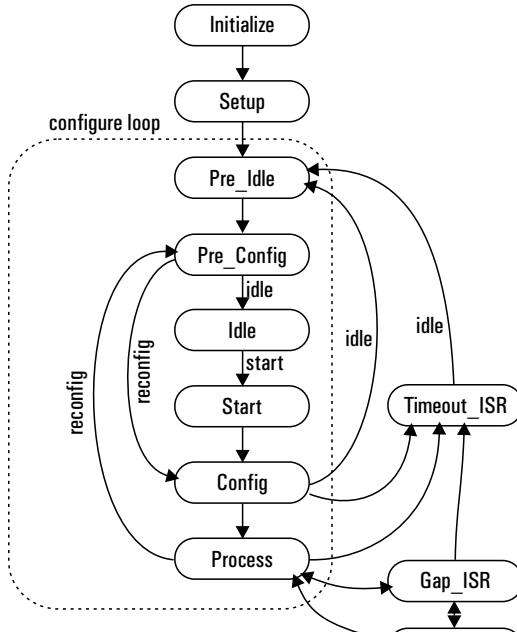

| Control Flow .....                                                                | 51 |

| Interrupt Service Routines .....                                                  | 58 |

| Synchronization .....                                                             | 59 |

| C4x Memory Utilization .....                                                      | 59 |

| Final Notes .....                                                                 | 60 |

| Building the Radio DSP Programs .....                                             | 61 |

| <b>Appendix A: Hardware Configuration</b>                                         | 63 |

| Introduction .....                                                                | 63 |

| SCMVX008/040 Example Configurations .....                                         | 63 |

| SCMVX008 Configuration: (1) 040, (0) 011, (0) 012 .....                           | 64 |

| SCMVX008 Configuration: (2) 040, (0) 011, (0) 012 .....                           | 65 |

| SCMVX008 Configuration: (4) 040, (0) 011, (0) 012 .....                           | 66 |

| SCMVX008 Configuration: (6) 040, (0) 011, (0) 012 .....                           | 67 |

| SCMVX008 Configuration: (4) 040, (2) 011, (0) 012 .....                           | 68 |

| SCMVX008 Configuration: (2) 040, (2) 011, (0) 012 .....                           | 69 |

| SCMVX008 Configuration: (2) 040, (0) 011, (2) 012 .....                           | 70 |

| SCMVX008 Configuration: (2) 040, (0) 011, (2) 012 .....                           | 71 |

| <b>Index</b> .....                                                                | 73 |

## Introduction

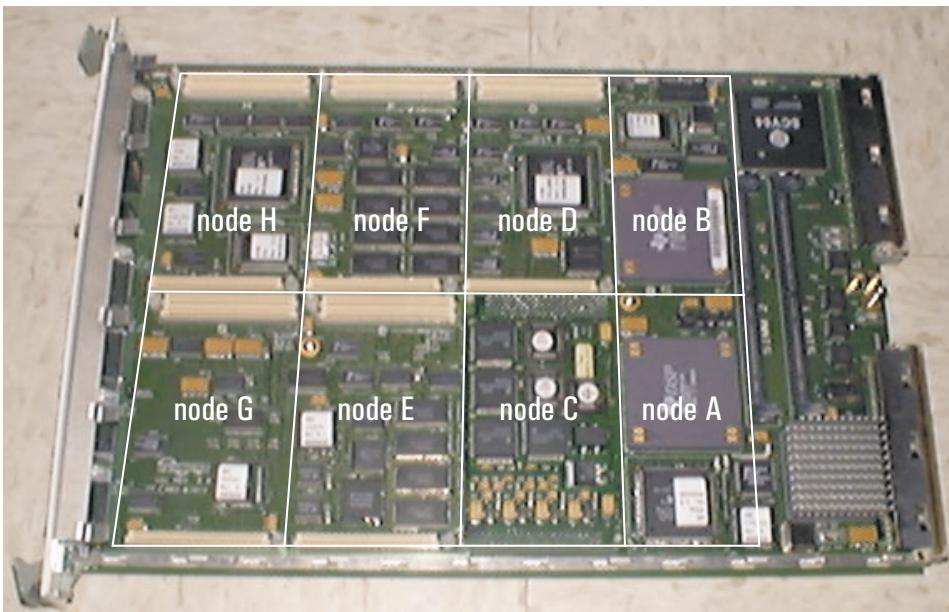

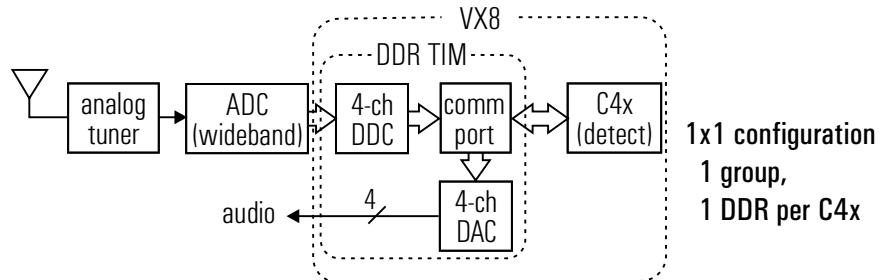

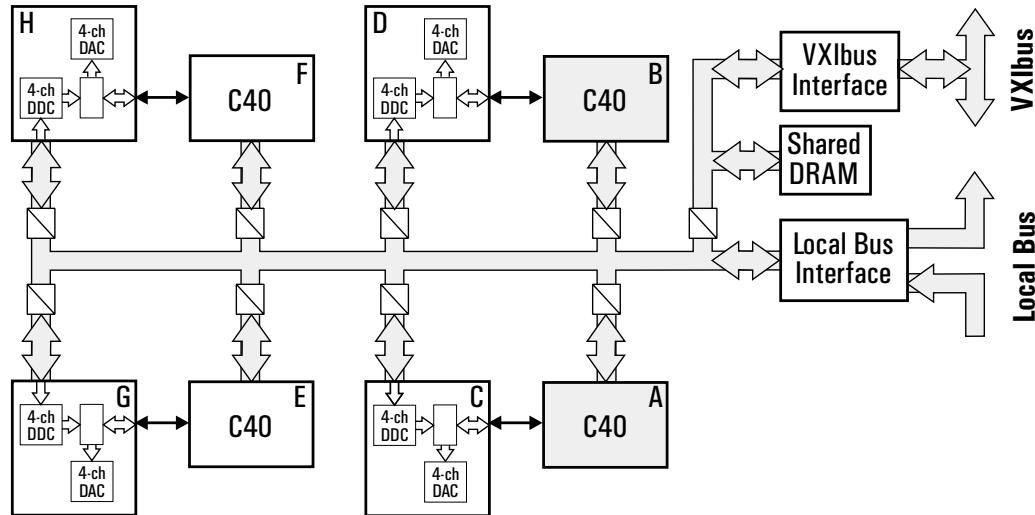

The SCMVX008<sup>1</sup> option 040 DDR TIM board is a 4-channel digital downconverter (DDC). It also provides 4 digital-to-analog converters (DAC). See figure below. This TIM-40 module is designed to be installed on the SCMVX008 carrier board (by Spectrum Signal Processing) and is referred to as the DDR TIM elsewhere in this document.

This discussion describes how to install the hardware and software, including a general description of the pieces, where they are located (i.e.. directory names), and how to run the demonstration program.

<sup>1</sup> The SCMVX008 is referred to elsewhere in this document simply as VX8.

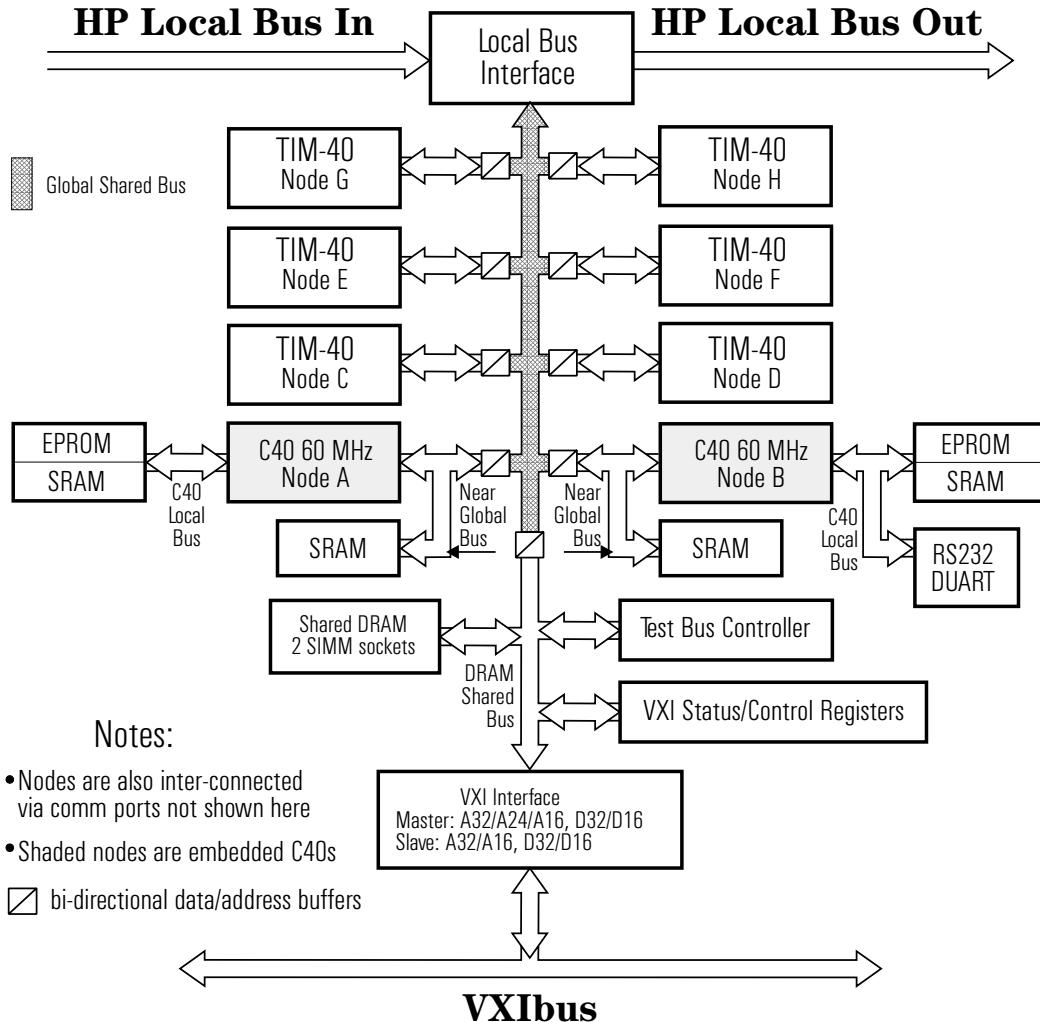

## Overview

This discussion describes how the DDR TIM and C40 modules may be used to create multi-channel, narrowband receiver systems.

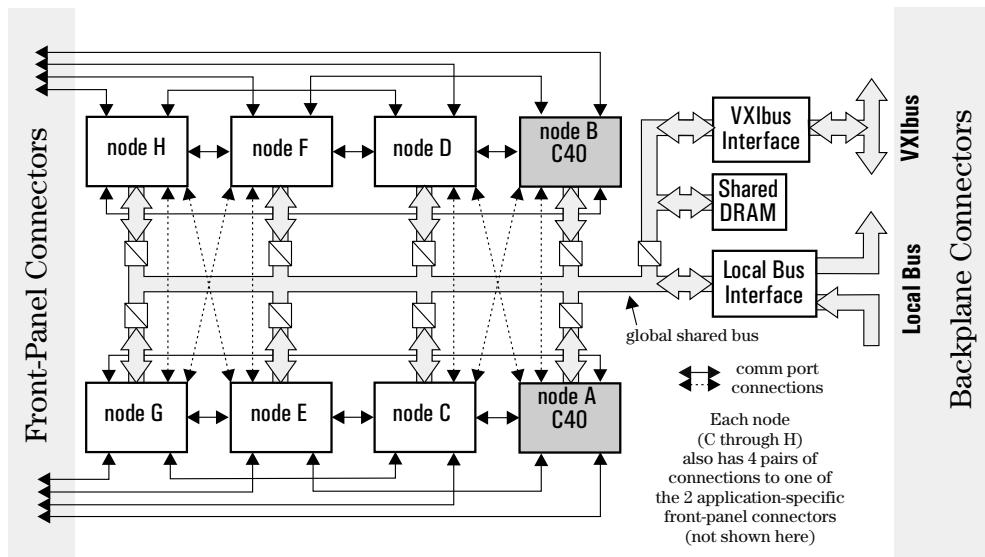

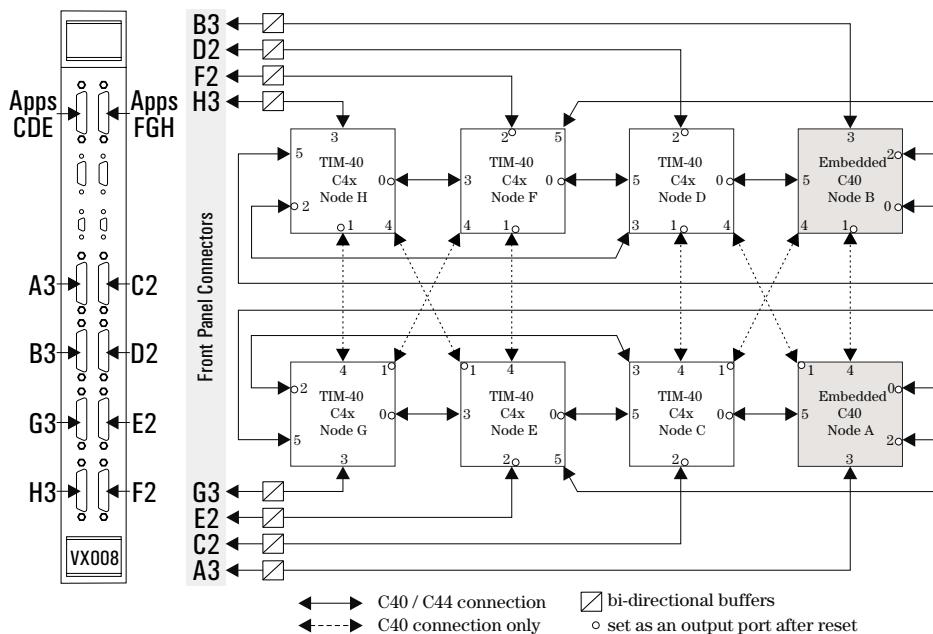

The VX8 Carrier Board has 2 TMS320C40 DSPs permanently installed on it and sites to install 6 TIM-40 plug-in boards. The TIM-40 boards may be either HP DDR TIMs or more C4x DSP TIMs. Default configurations are discussed on page 14.

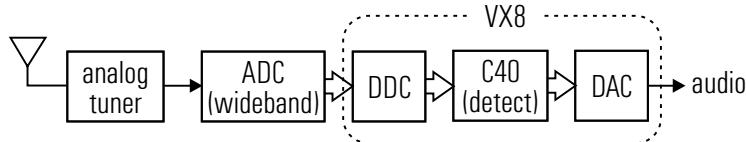

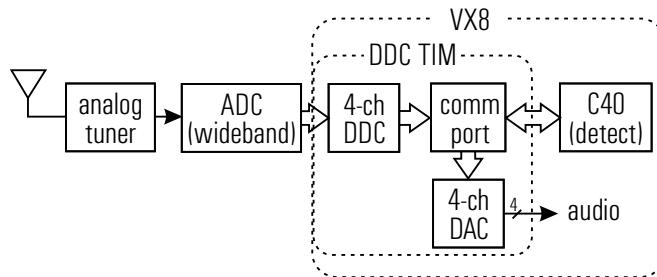

### Digital Drop Receiver

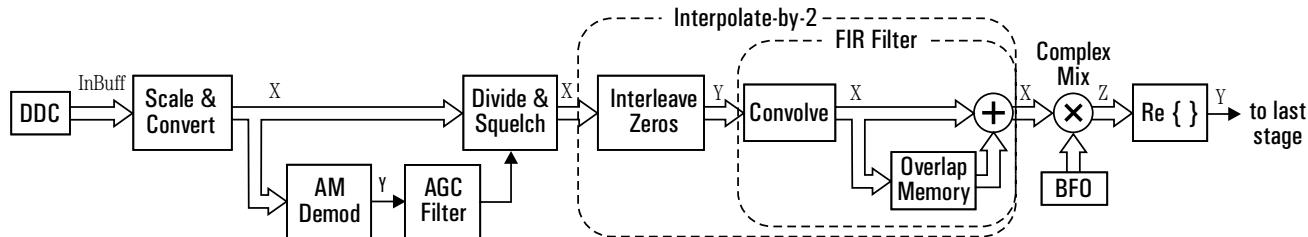

The following figure shows the generic block diagram of a *digital drop receiver* (DDR). Signal data flows through the system as follows:

1. An analog tuner (optional) downconverts the antenna signal to an IF near baseband.

2. A wideband analog-to-digital converter (ADC) digitizes the tuner's IF output.

3. The wideband digital data is transferred over the VXI Local Bus to the VX8 module where it is broadcast to one or more digital downconverter (DDC) modules. The DDC channelizes a signal (tunes to a specific narrowband frequency).

4. The channelized, lower-bandwidth digital signal is transferred to a C4x digital signal processor (DSP) module on the VX8 board via a comm port. The DSP performs detection/demodulation of the data, transforming it to audio information in digital format.

5. The digital audio data is transferred to a digital-to-analog converter (DAC) on the DDR TIM board via comm port and it is converted to analog format.

**Generic Digital Drop Receiver**

## Requirements

The software provided with this product supports Windows NT, Windows 95, and HP-UX 9.0x. There are some differences in the level of support for each as described in more detail later.

Supported system configurations:

- PC embedded slot-0 controller (e.g. HP E6233)

- PC connected via MXI-2 interface (National Instruments VXI-PCI8000 kit) to the VXI chassis

- HP-UX embedded slot-0 controller (e.g. E1498A)

- HP-UX workstation connected via MXI interface (E1482B) to the VXI chassis

Requirements for the HP Radio demonstration program:

- Runs on a PC controller, only.

- PC host/controller is Pentium or better

- VXI chassis

- One VX8 VXI module

- At least one DDR TIM installed on the VX8 board.

- For more detail see **Example Program** on page 11.

## Terminology

This topic defines the terms, abbreviations, and acronyms used in this document.

### Definition of Terms

- *Channelize* – to extract a narrowband signal at a specific center frequency from a wideband digital data stream. One DDR TIM board can *channelize* four signals at any four center frequencies within the ADC bandwidth.

- *Host* – the computer system which starts and controls the high-level processes in a narrowband receiver system; a PC or HP-UX workstation. The HP Radio program runs on the *host*. It downloads the `radio` program to the target system on the VX8 carrier board.

- *Target* – the VX8-based computer system which is started and controlled by the host system in a narrowband receiver system; also referred to as the *dsp* system. It is composed of one or more C4x DSPs on one or more VX8 carrier boards. The function of the target system is to manage the assets and perform the processes of the low-level narrowband receiver system. Commands and responses pass between the host and the *target* via a shared-memory messaging scheme.

- *Embedded* – installed directly in a system chassis or on a VXI module.

When used to describe a VXI controller, "embedded" means the computer system is, itself, a VXI module installed in slot 0 of a VXI chassis as opposed to an external (desktop) computer which could be used in conjunction with a MXI interface. Embedded controllers have front-panel connectors for a mouse, a keyboard, and a monitor as well as interfaces such as LAN, SCSI, and RS232.

When used to describe a C40 DSP, "embedded" refers to one of the two TI TMS320C40 DSP ICs installed permanently on the carrier board as opposed to TIM-40 boards which are plugged into node sites on the board. You can get 24 narrowband receiver channels on one VX8 board by installing 6 DDR TIM boards and grouping 3 each with the two *embedded* C40s.

- *Node* – one of the eight locations on the VX8 carrier board which may contain an embedded C40 or TIM-40 module. The nodes are identified by the letters of the alphabet, A through H; nodes A and B contain embedded C40 DSPs and nodes C through H are locations supporting the TIM-40 plug-in modules. See page 4.

- *Comm Port* – TMS320C4x high-speed interprocessor communication feature. The C40 has 6 comm ports and the C44 has 4. See page 6.

### Acronyms/Abbreviations

- VX8 – shorthand for Spectrum Signal Processing's SCMVX008 carrier board

- DDC – digital downconverter

- DSP – digital signal processor

- DAC – digital-to-analog converter

- DDR – digital drop receiver (DDC + DSP/detection + DAC/audio out). See **DDR Groups** on page 14.

- TIM – Texas Instruments Module, also used as TIM-40

- C40 – The Texas Instrument TMS320C40 DSP.

- C4x – Refers to either the TI C40 or C44 DSPs. The C40 may be either one of the two embedded ICs installed on the VX8 carrier board or additional TIM-40 boards.

- ISR - interrupt service routine

- EOB - end of block

## Hardware Installation

### Installing TIM-40 Modules

The DDR TIM modules are usually installed on the VX8 carrier board by Hewlett-Packard before they are shipped. They should be configured properly when you receive them. Checking or changing the configuration requires removal of the VX8 carrier board cover. To move, install, or remove a DDR TIM module on the VX8 carrier board, see Spectrum Signal Processing's *VX8 Carrier Board Installation Guide* provided with the VX8 VXI module. See also Appendix A on page 63.

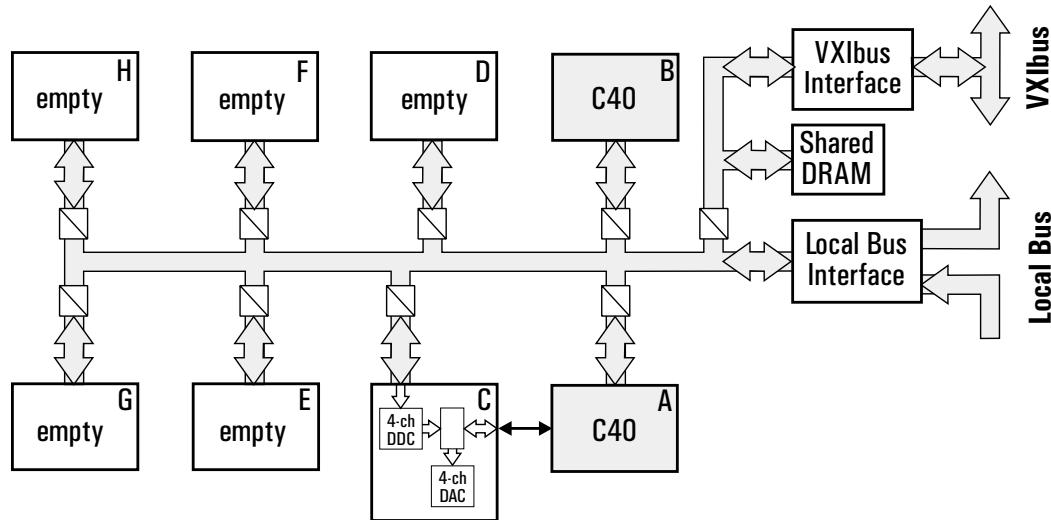

The following figure shows a VX8 with the cover off and one DDR TIM installed in node C (note that the connectors are visible in the other nodes).

## Jumpers

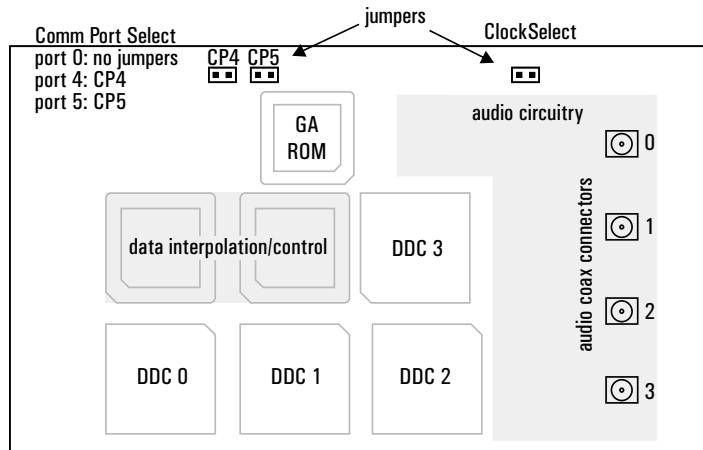

The jumpers on the DDR TIM module select the clock source and the module's single comm port as follows. The jumper settings for several example configurations are described in Appendix A: Hardware Configuration on page 63.

### Clock Jumper

The clock source may be either the ADCCLK signal from the VXIbus or a clock generated on the VX8 board (SYSCLK). Normally (using the default setting) the ADCCLK signal is selected so that the data processed by the DAC section stays in sync with the ADC that generates the digital information.

|             |                                                                                                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Note</b> | The ADC <i>must</i> be set to drive this clock over the ECLTRG1 line by becoming the clock master. DDR programming requires that the clock signal is present. |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

The SYSCLK is provided for the special case in which the DAC section is used and there is no ADCCLK signal; either there is no ADC module to provide it or it is not available on the ECLTRIG1 line of the VXIbus.

The clock selection is made with the Clock Select jumper as follows; see figure:

- **no jumper** selects the ADCCLK signal (default)

- **jumper** selects the SYSCLK signal

### Comm Port Jumper

The DDR TIM comm port is selected as follows:

- **Comm Port 0:** no jumper

- **Comm Port 4:** jumper at CP4

- **Comm Port 5:** jumper at CP5

|              |                                                                                                                                                                                                                                                                                      |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Notes</b> | There is no <i>default</i> setting for the comm port jumper. Since they come installed on the VX8 board and must be able to communicate with a C4x DSP, each board's comm port is set at the factory based on its node location and that of its C4x master. See the table on page 6. |

|              | If no jumper is needed, you may place a jumper on one of the two pins to keep it available for future changes.                                                                                                                                                                       |

## DDR Comm Port

Comm ports are used to pass data between nodes on the VX8 carrier board as shown in the following figure. The DDR TIM module has a single comm port interface which may be configured as either comm port 0, 4, or 5. The comm port determines which node the DDR TIM module uses to communicate with its C4x controller. The comm port selected depends on the node locations of both the DDR TIM module and the C4x.

The comm port on the DDR TIM is used for several purposes:

1. Channelized, lower-bandwidth data is passed from the DDR TIM to the C4x.

2. Detected/demodulated digital audio is passed from the C4x to the DDR TIM for conversion to analog format by the DACs.

3. Configuration/control information is passed from the C4x to the DDR TIM

## Comm Port Selection

The following table lists the comm port to use given the node location of the DDR TIM and the node location of the C4x DSP that will control it and process its data. For more information about group configurations, see **DDR Groups** on page 14.

| DDR<br>TIM<br>node | C4x<br>DSP<br>node | DDR<br>Comm<br>Port | DDR<br>TIM<br>node | C4x<br>DSP<br>node | DDR<br>Comm<br>Port | DDR<br>TIM<br>node | C4x<br>DSP<br>node | DDR<br>Comm<br>Port |

|--------------------|--------------------|---------------------|--------------------|--------------------|---------------------|--------------------|--------------------|---------------------|

| C                  | A                  | 0                   | D                  | B                  | 0                   | E                  | C                  | 0                   |

|                    | D*                 | 4                   |                    | A                  | 4                   |                    | F*                 | 4                   |

|                    | E                  | 5                   |                    | F                  | 5                   |                    | A                  | 5                   |

| F                  | D                  | 0                   | G                  | E                  | 0                   | H                  | F                  | 0                   |

|                    | G*                 | 4                   |                    | H*                 | 4                   |                    | E*                 | 4                   |

|                    | B                  | 5                   |                    | A                  | 5                   |                    | B                  | 5                   |

\* A DDR TIM cannot communicate with a C44 module in this position.

Also, the jumper settings for several example configurations are described in Appendix A: Hardware Configuration on page 63.

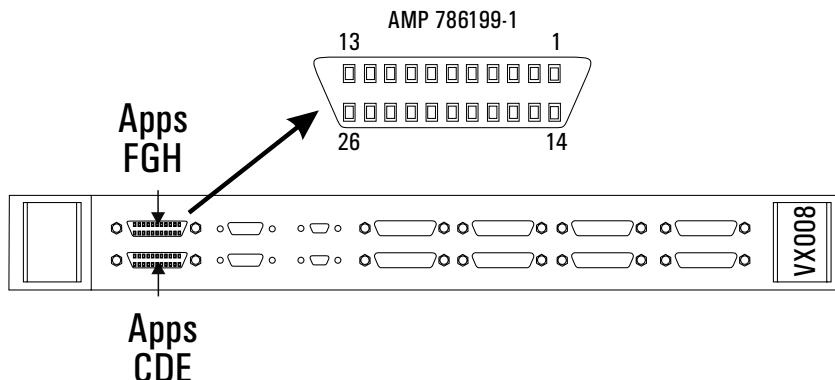

## Audio (DAC) Outputs

The audio outputs of each DDR TIM channel's DAC are routed to the VX8 application-specific connectors as given in the following table:

| Node | audio ch. # | Pin #  |        | BoB jack* | Node | audio ch. # | Pin #  |        | BoB jack* | Node | Audio Ch. # | Pin #  |        | BoB jack* |

|------|-------------|--------|--------|-----------|------|-------------|--------|--------|-----------|------|-------------|--------|--------|-----------|

|      |             | signal | return |           |      |             | signal | return |           |      |             | signal | return |           |

| C    | 0           | 15     | 14     | 1         | D    | 0           | 19     | 18     | 5         | E    | 0           | 23     | 22     | 9         |

|      | 1           | 3      | 4      | 2         |      | 1           | 7      | 8      | 6         |      | 1           | 11     | 12     | 10        |

|      | 2           | 2      | 1      | 3         |      | 2           | 6      | 5      | 7         |      | 2           | 10     | 9      | 11        |

|      | 3           | 16     | 17     | 4         |      | 3           | 20     | 21     | 8         |      | 3           | 24     | 25     | 12        |

| F    | 0           | 15     | 14     | 1         | G    | 0           | 19     | 18     | 5         | H    | 0           | 23     | 22     | 9         |

|      | 1           | 3      | 4      | 2         |      | 1           | 7      | 8      | 6         |      | 1           | 11     | 12     | 10        |

|      | 2           | 2      | 1      | 3         |      | 2           | 6      | 5      | 7         |      | 2           | 10     | 9      | 11        |

|      | 3           | 16     | 17     | 4         |      | 3           | 20     | 21     | 8         |      | 3           | 24     | 25     | 12        |

Pin # refers to the pin numbers as shown in the figure directly below.

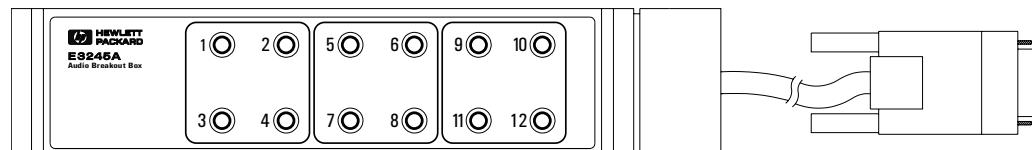

\* BoB jack refers to the jack number (1-12) of the audio breakout box (BoB) E3245A shown in the bottom figure. This accessory provides monaural connections.

The following figure shows the pin numbers for the application-specific connectors. The part numbers for the connector that fit the front panel connectors are:

- Cable connector, plug: AMP 750833-1

- Backshell kit: AMP 750850-3

### Audio Connections

### Note

The DDR TIM board also has 4 coax connectors mounted on the board which may be used to connect to the DAC outputs. See the figure on page 5. Your VX8 carrier board may have a number of small bulkhead connectors on the front panel to which these attach. The connector type is OSMT from M/A-COM. See series part number 9950-4100-xx for available cables.

### E3245A Audio Breakout Box Accessory

This accessory provides monaural miniature phone plug connections (3.5 mm as are commonly found on headphones) from the VX8 application-specific front-panel connectors. For connections, see the BoB jack column in the table above.

---

## Software Installation

The software provided with the SCMVX008 option 140 software development kit supports C language programming and includes libraries and header files for development in three environments:

- Windows 95

- Windows NT

- HP-UX 9.0x

---

### Windows 95/NT

To install the software on a PC, insert floppy disk #1 into drive A: and run A:\setup. Follow the instructions given by the installation program.

To run the `radio` demonstration program under Windows NT:

- Microsoft service pack 2 or greater should be installed. The installation program checks this and notifies you if the update is not installed. The NT service pack can be obtained from Microsoft's web site, [www.microsoft.com](http://www.microsoft.com).

- VXI plug&play support must be installed. The installation program verifies that `VISA32.DLL` exists in the Windows system directory.

- Spectrum Signal Processing's `ssvx8_32.dll` must be installed in the `\vxipnp\bin\winxx` directory. (`xx` depends on the operating system.)

- See the `readme.txt` file in `\vxipnp\winxx\hpradio` directory for information about the hardware required to run the HP radio demonstration program.

---

### HP-UX 9.0x

To install the software on an HP-UX workstation, insert the DAT (digital audio tape) in the DDS DAT drive and execute the following command as superuser (root):

```

/etc/update -s /dev/update.src "*"

```

This command assumes that the `/dev/update.src` device file refers to the DDS DAT drive. If this device file has not been pre-configured, use SAM (System Administration Manager) to create and configure the appropriate device file for the DDS DAT drive.

---

## Directories and Files

The files and directory names vary depending on the system type.

### Windows 95/NT Directories

All installed directories and files are placed in the default directory:

- `c:\vxipnp\winnt` for Windows NT systems

- `c:\vxipnp\win95` for Windows 95 systems

The drive letter may vary but we recommend that the `\vxipnp\winxx` directory is used. VISA library support and drivers for the VXIbus host controller interface should also be in this directory (`\vxipnp\winxx`) as should Spectrum Signal Processing's `ssvx8` host libraries for the SCMVX008 Carrier Board.

The following directories and files are installed for Window 95/NT systems:

- `include\` - library and VXI plug&play include files

- `hpvx8.h` - the main `hpvx8` library include file

- `lib\` - archive libraries

- `msc\` - the Microsoft-C compatible libraries

- `hpvx8.lib` - the `hpvx8` static library

- `hpvx8\` - top directory for the HP libraries and example programs

- `readme.txt` - describes files and directories installed

- `ddrifc\` - contains `digital drop receiver interface` code

- `readme.txt` - describes the `ddrifc` code

- `dsp\` - `ddrifc` target C code files

- `include\` - contains `ddrifc` target include files

- `src\` - contains the `ddrifc` target source files

- `hpvx8\` - contains the `hpvx8` code

- `readme.txt` - describes `hpvx8` code

- `dsp\` - `hpvx8` target C code

- `include\` - `hpvx8` target include files

- `src\` - `hpvx8` target source files

- `host\` - `hpvx8` host C code

- `build\` - `hpvx8` host build and library files

- `include\` - `hpvx8` host include files

- `src\` - `hpvx8` host source files

- `radio\` - host & target C programs for the example program

(more detail for this directory appears on page 50)

- `dsp\` - radio target C code

- `build\` - radio target build files

- `include\` - radio target include files

- `src\` - radio target source files

- `host\` - radio host C code

- `include\` - radio host include files

- `hpradio\` - GUI directory for the `radio` example code

- `readme.txt` - information about the HP Radio example code

- `resource\` - radio resource files

## HP-UX Directories

All directories and files are installed in `/opt/vxipnp`. SICL/VISA library support and drivers for the VXIbus host controller interface should be placed in the same directory (`/opt/vxipnp`) as should Spectrum Signal Processing's `ssvx8` host libraries for the SCMVX008 Carrier Board.

The following directories and files are installed for HP-UX systems:

- **bin/** – shared libraries

- **libhpvx8.s1** – the hpvx8 shared library

- **include/** – contains library and VXI plug&play include files

- **hpvx8.h** – the main hpvx8 library include file

- **lib/** – archive libraries

- **libhpvx8.a** – the hpvx8 static (archive) library

- **hpvx8/** – top directory for the HP libraries and example programs

- **readme.txt** – describes files and directories installed

- **ddrife/** – contains **digital drop receiver interface** code

- **readme.txt** – describes the ddrife code

- **dsp/** – ddrife target C code files

- **include/** – ddrife target include files

- **src/** – the ddrife target source files

- **hpvx8/** – the hpvx8 code

- **readme.txt** – describes hpvx8 code

- **dsp/** – hpvx8 target C code

- **include/** – hpvx8 target include files

- **src/** – hpvx8 target source files

- **host/** – hpvx8 host C code

- **build/** – hpvx8 host build and library files

- **include/** – hpvx8 host include files

- **src/** – hpvx8 host source files

- **radio/** – host & target C programs for the example program

- (more detail for this directory appears on page 50)

- **readme.pdf** – (this file) includes details about the radio example code

- **dsp/** – radio target C code

- **build/** – radio target build files

- **include/** – radio target include files

- **src/** – radio target source files

- **host/** – radio host C code

- **include/** – radio host include files

- **hpradio/** – GUI directory for the radio example code

- **readme.txt** – information about the HP Radio example code

- **resource/** – radio resource files

## Example Program

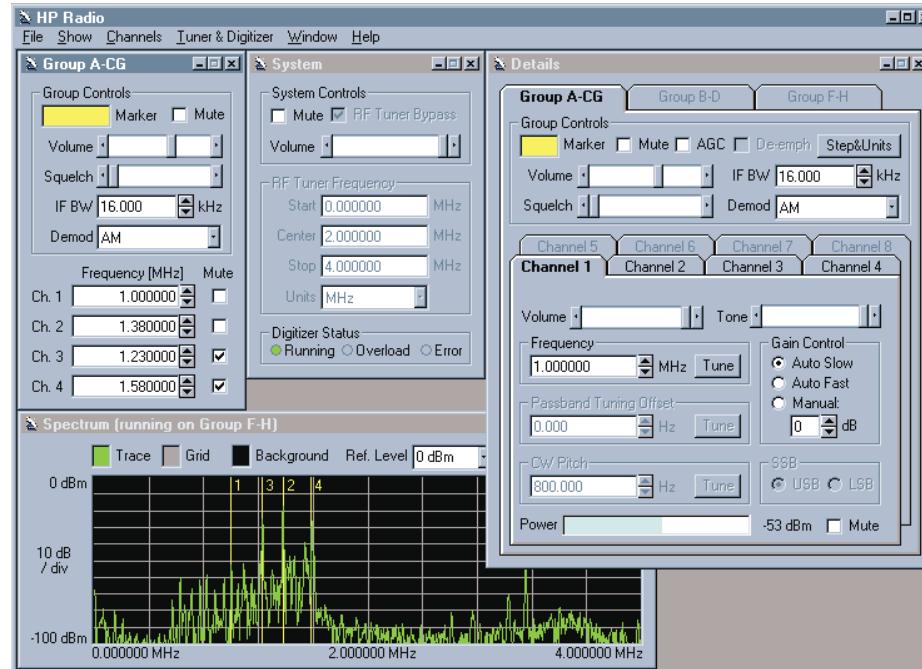

This discussion describes the hardware and software required to run the example program HP Radio. More information is available in the `readme.txt` file in the `hpradio` directory.

HP Radio uses the `hpvx8` library to create a multi-channel, narrowband receiver system. It provides a graphic user interface (GUI) which allows you to exercise the capabilities of the narrowband receiver system hardware.

## Hardware Configuration

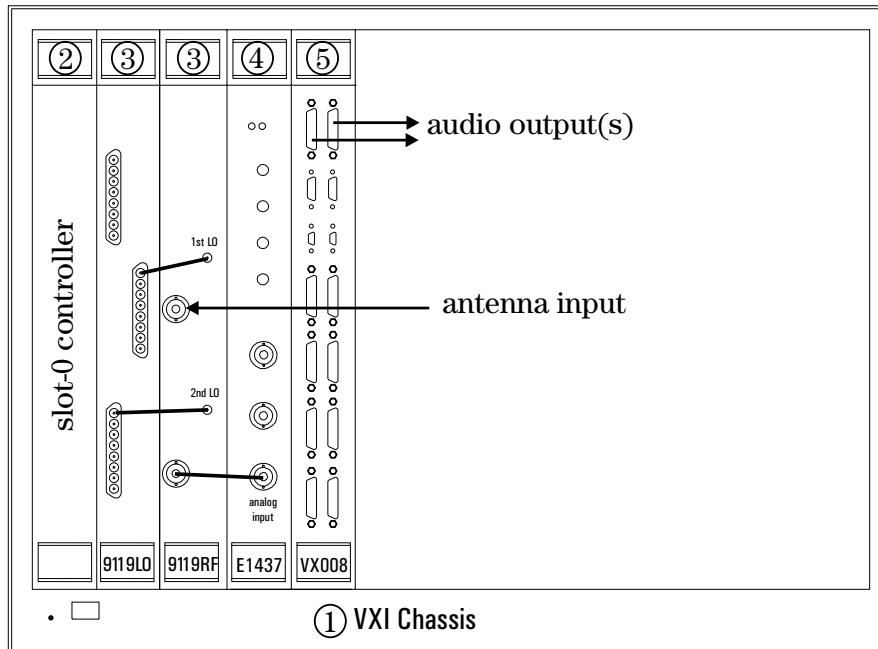

Before you can run the program, you must collect the required hardware and software and configure them correctly. The following figure shows an example hardware configuration.

## Installed Hardware

The numbers in the following list correspond to circled numbers in the figure above:

1. VXI chassis/mainframe

2. PC slot-0 controller (NI MXI-2 interface to a PC workstation)

3. Analog downconverter (optional; the WJ-9119 is an HF tuner; 100 kHz-32 MHz)

4. Wideband ADC (the E1437A has an 8 MHz BW)

5. VX008 is a VXI carrier board containing 2 embedded C40s and 6 sites (nodes) that accept TIM-40 plug-in modules such as the HP DDR TIM and the MDC40SS Super SRAM C40

- At least 4 MB DRAM installed on the VX008

- At least one DDR TIM installed on the VX008

### Note

The model type and configuration of the analog tuner and wideband ADC are declared/defined for the example program in the file `hpradio.cfg`. See **Resource Files** on page 12.

## VX8 Configuration

The system and VX8 hardware configuration must be defined in resource files that the software uses to define the elements it controls.

**Resource Files** There are four resource files required by the radio program. These files define the hardware configuration and are used by the libraries to initialize the system. They must match the hardware configuration used with radio.

- `hpradio.cfg` – system hardware configuration file

- `hpradio.grp` – `hpxv8` group resource file

- `hpradio.sdf` – `ssvx8` system definition file (for VX8 configuration)

- `hpradio.ldf` – `ssvx8` load definition file (for VX8 configuration)

These files are installed in the `\vxipnp\winxx\hpxv8\hpradio` directory. The resource subdirectory contains templates and examples for five different VX8 hardware configurations. The resource files listed above define a configuration consisting of one group composed of one C40 and one DDR TIM. The templates support  $1 \times 1$ ,  $2 \times 1$ ,  $2 \times 2$ ,  $2 \times 3$ , and  $4 \times 1$  configurations where, given  $n \times m$ ,  $n$  is the number of groups and  $m$  is the number of DDR TIMs per group. For example, to change resource files for a VX8 with DDR TIMs in nodes C and D, use the following command:

```

copy resource\2x1.* hpradio.*

```

If the files provided do not match your hardware exactly, select the closest configuration and edit the files as explained in the `readme.txt` file in the `hpradio` directory.

For more information about the various supported receiver configurations, see **DDR Groups** on page 14.

## Running HP Radio

When the hardware and resource files are properly configured, you can run the example program.

To start it, either:

- Click on the HP Radio menu item in the Start\Programs\HP VX8 Radio\ menu or

- In Explorer, double-click Hpradio in \vxiipnp\winxx\hpxv8\hpradio

The first time HP Radio is run, the interface shows one group window with two channels active. This group window is labeled Group A-C, which refers to a group consisting of a C40 in node A and a DDR TIM slave at node C. Node locations are shown in the figure on page 6.

With one DDR TIM installed, 4 channels are present in this group. In this case, the number of channels that may be selected from the Channels menu is either 1, 2, or 4. You may want to select a number less than 4, depending on the bandwidth and modulation type of the signals you plan to receive. Since all four channels are being processed by the same DSP, more channels means less processing power per channel. The maximum real-time IF bandwidth (IF BW) decreases when the number of active channels is increased.

To set the IF BW, either increment or decrement it with the spin buttons or enter a value in the text box. The amber User LED on the VX8 front panel will illuminate when the processing workload has become greater than the processor's ability to handle it *real time*. It will continue to process data but there will be gaps in it. See the discussion on page 47.

### Note

More information exists concerning the operation of HP Radio in the readme.txt file in the hpradio directory.

## DDR Groups

One, two, or three<sup>2</sup> DDR TIMs may be connected to a single C40 DSP<sup>3</sup> on the VX8 to form a *group*. A group is composed of one C4x (DSP) and the DDR-TIM(s) associated with it. The IF bandwidth is the same for all channels in a group. The DDC channels may be individually tuned to any frequency in the bandwidth of the wideband digital data stream created by the ADC. See **Grouping** on page 23.

The following figures are block diagrams showing data flow through the receiver system for various configurations. The group configuration for the example program HP Radio is defined in the file `hpradio.grp`. See **Resource Files** on page 12.

---

## Example Configurations

The default configurations available from Hewlett-Packard are:

- 1×1 – 1 group, 1 DDR TIM per group; 4 channels per VX8.

- 2×1 – 2 groups, 1 DDR TIM per group; 8 channels per VX8.

- 2×2 – 2 groups, 2 DDR TIMs per group; 16 channels per VX8.

- 2×3 – 2 groups, 3 DDR TIMs per group; 24 channels per VX8.

- 4×1 – 4 groups, 1 DDR TIM per group; 16 channels per VX8.

These configurations offer various numbers of channels per VX8 module and varying amounts of digital signal processing power per channel.

<sup>2</sup> Four DDR TIMs per C40 is also possible if you install them in nodes C, D, E, and G with a corresponding reduction in available processing power per DDR. See the figure on page 6.<sup>222222</sup>

<sup>3</sup> The number of channels that can be processed simultaneously by one C40 DSP is limited by the bandwidth and detection type. See the table on page 60.<sup>333333</sup>

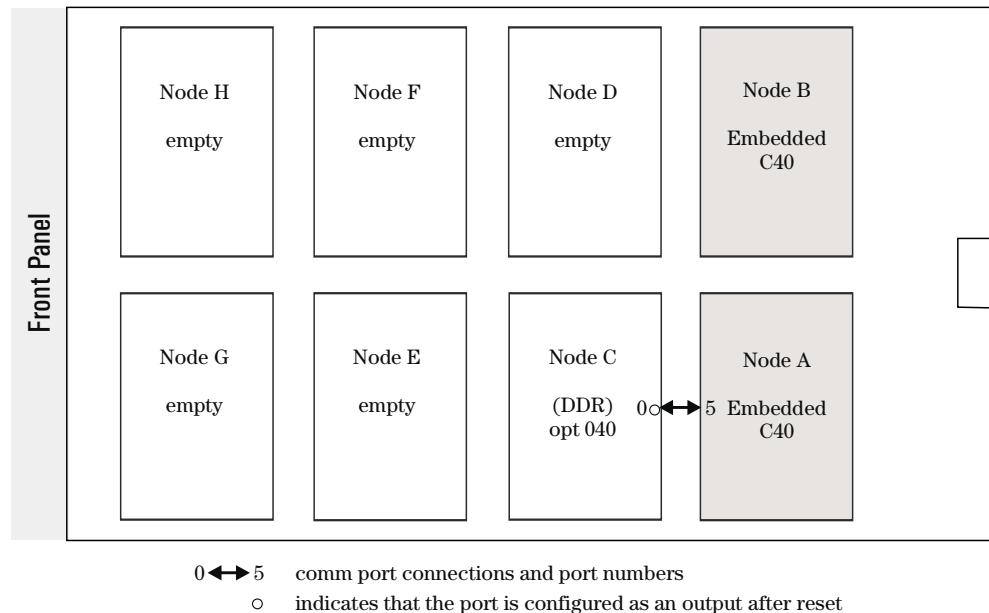

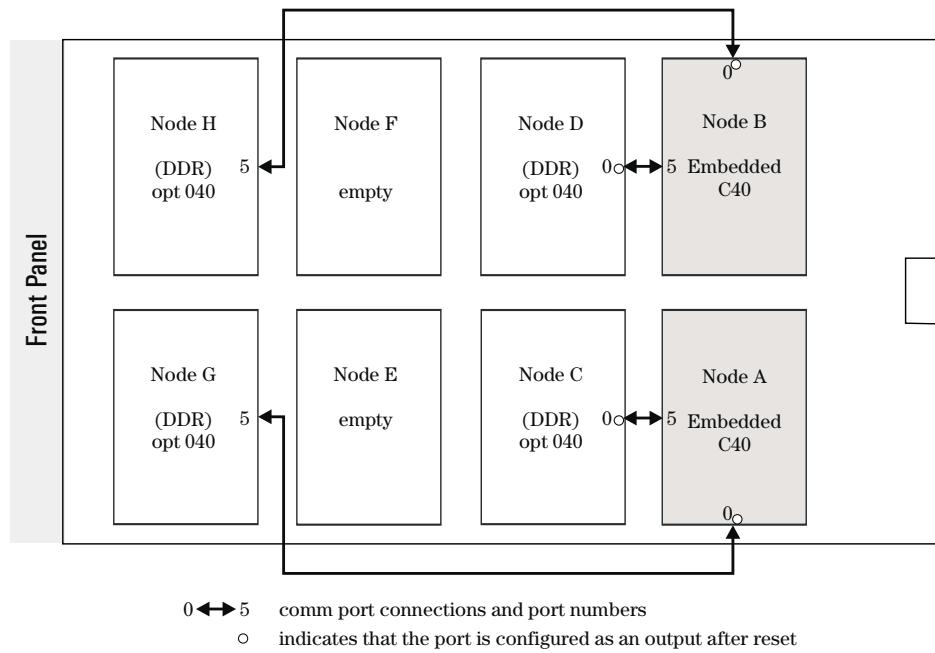

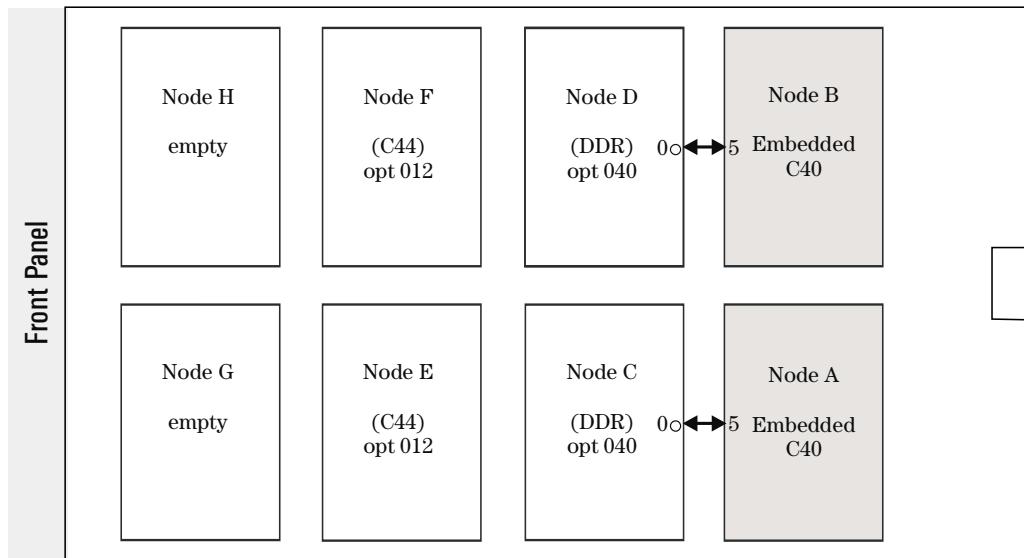

#### 4-channel, 4ch/DSP

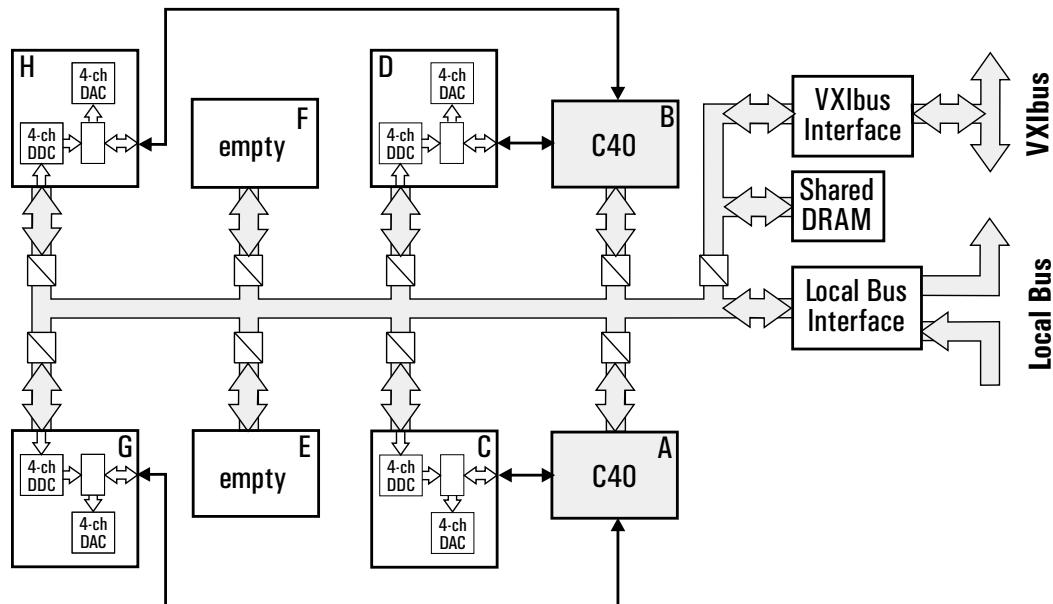

The configuration shown below could be created by installing a DDR TIM at node C and grouping it with the embedded C40 at node A. See bottom figure.

This configuration provides 4 high-performance receiver channels. The VX8 configuration layout is illustrated in the figure below.

Detailed installation information for this configuration exists on page 64.

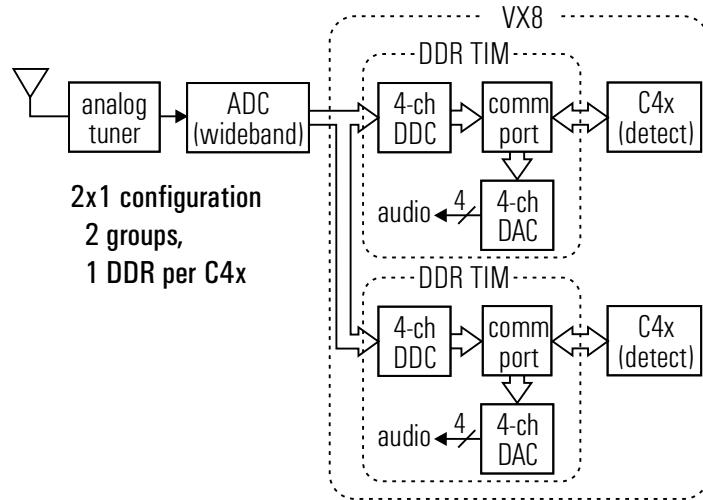

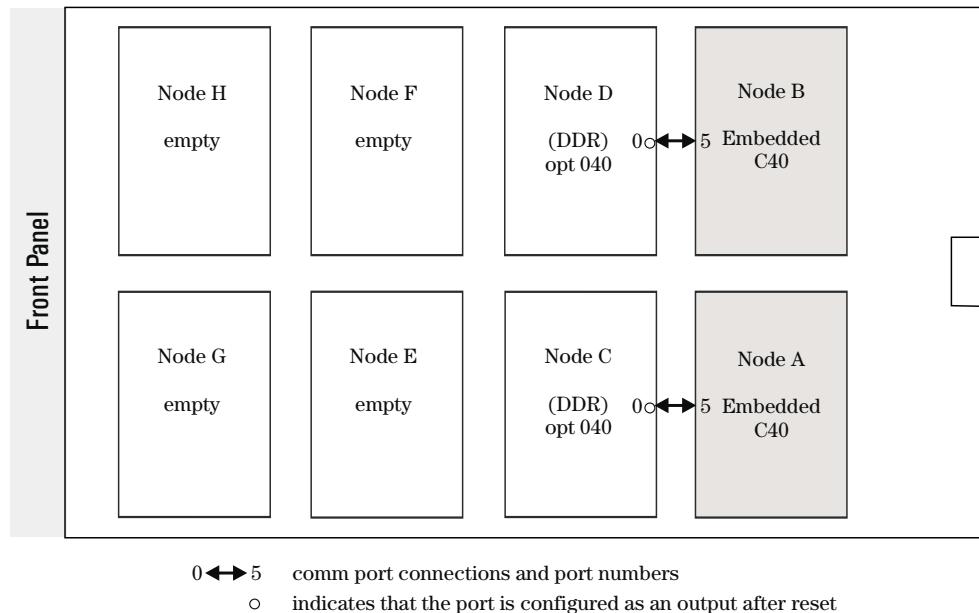

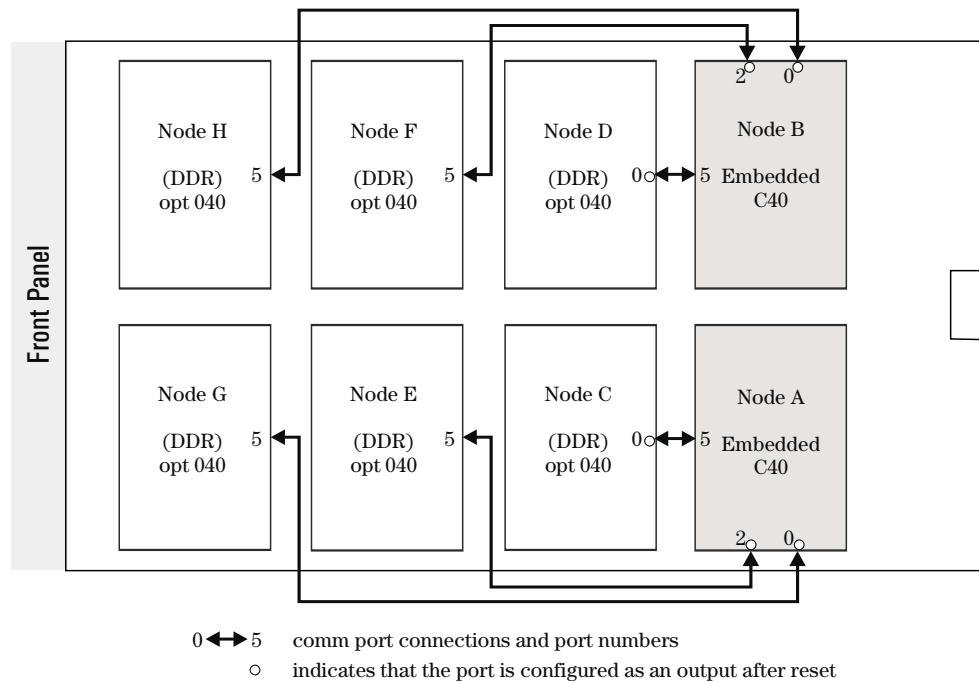

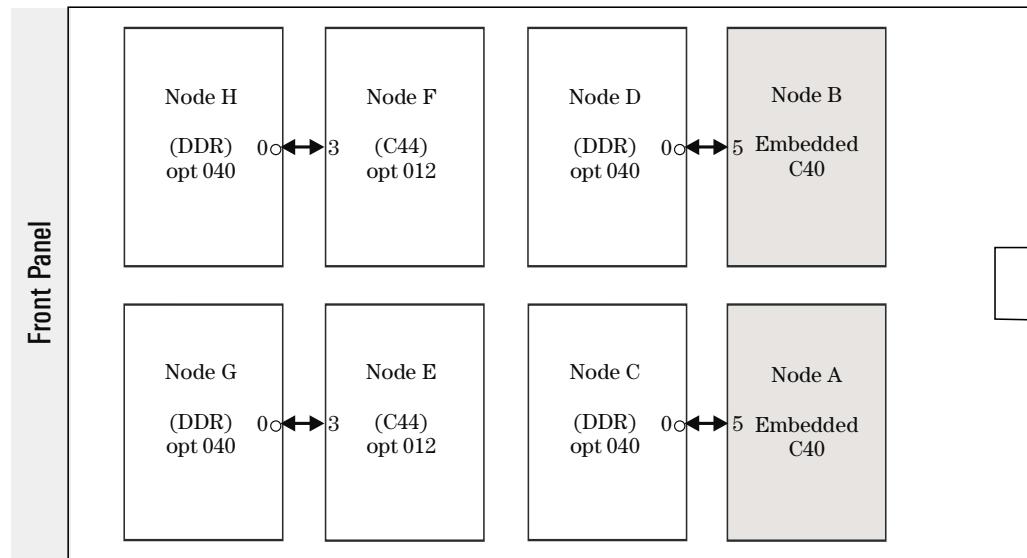

### 8-channel, 4ch/DSP

The configuration shown in the figure below could be created by installing DDR TIMs at nodes C and D (see bottom figure), grouping them with the embedded C40s at nodes A and B, respectively. These groups are identified as A-C and B-D.

This configuration has virtually the same performance as the 1x1 configuration (4 ch/DSP) with double the number of channels (8) and the ability to process 2 different bandwidths simultaneously.

The VX8 configuration layout is illustrated in the figure below.

Detailed installation information for this configuration exists on page 65.

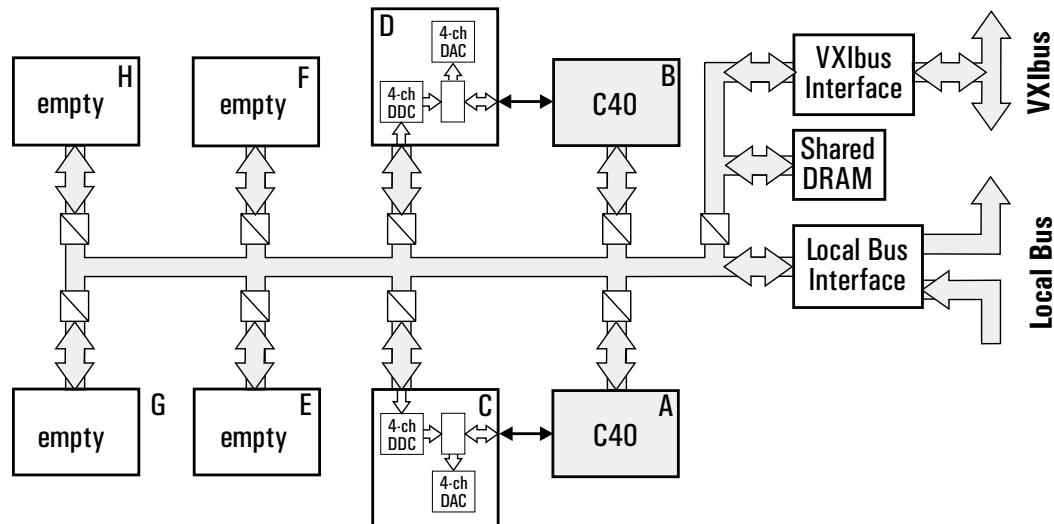

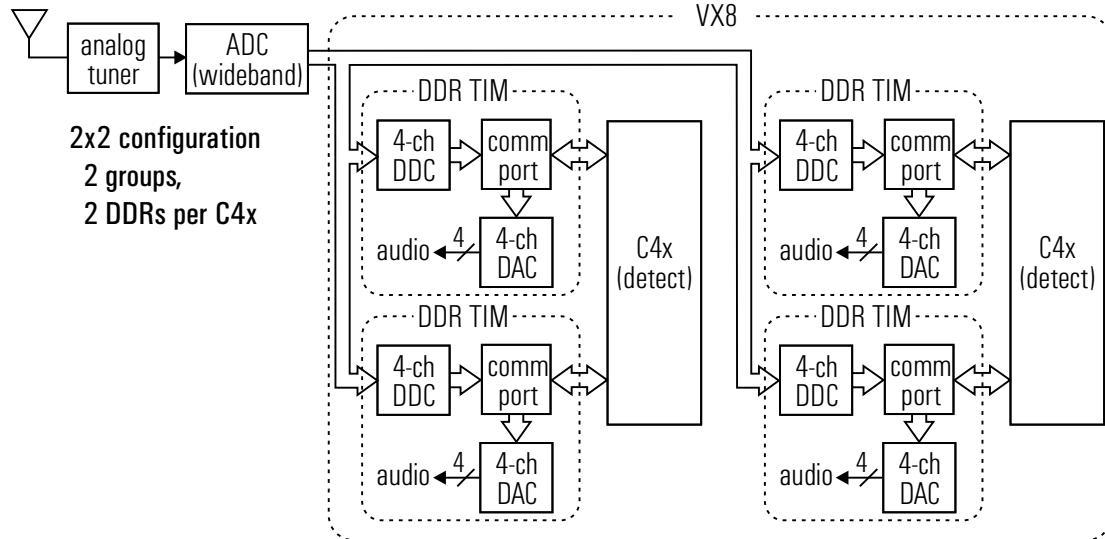

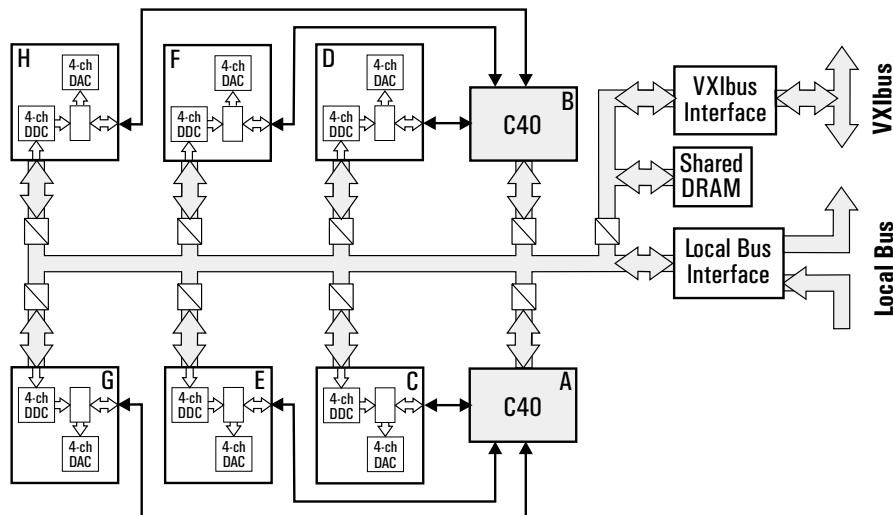

## 16-channel, 8ch/DSP

The configuration shown in the figure below could be created by installing DDR TIMs at nodes C, D, G and H (see bottom figure), grouping them with the embedded C40s at nodes A and B, respectively. These groups are identified as A-CG and B-DH.

This configuration provides 16 channels and 2 different simultaneous bandwidth settings. Its performance and cost/channel falls between the 2x3 and 4x1 configurations.

The VX8 configuration layout is illustrated in the figure below.

Detailed installation information for this configuration exists on page 66.

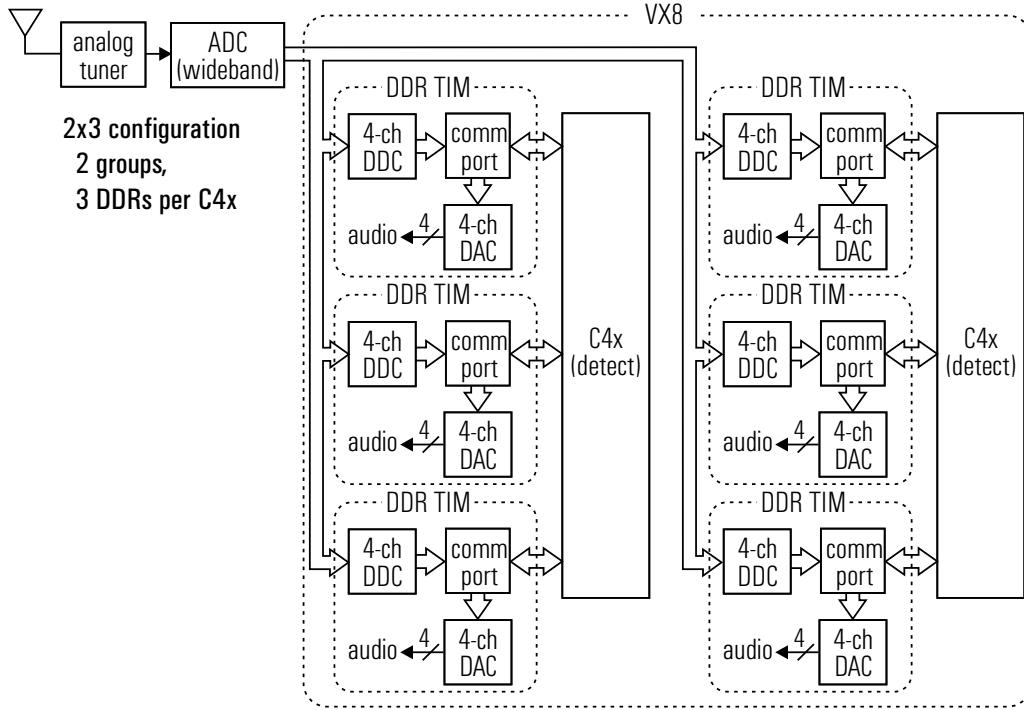

## 24-channel, 12ch/DSP

The configuration shown in the figure below could be created by installing DDR TIMs at nodes C, D, E, F, G, and H, grouped with the embedded C40s at nodes A and B, respectively. These groups are identified as A-CEG and B-DFH.

This configuration offers the highest channel-count per VX8 board (24) but also has the lowest DSP performance per channel. Possible applications include use for very narrow-bandwidth signals or for channelization-only, where the demodulation is performed on another system or VX8 board. In the latter case, the C40s would be used to multiplex the channel data onto one or two comm ports and pass it to connectors on the front panel where they are passed to the other system/board.

Detailed installation information for this configuration exists on page 67.

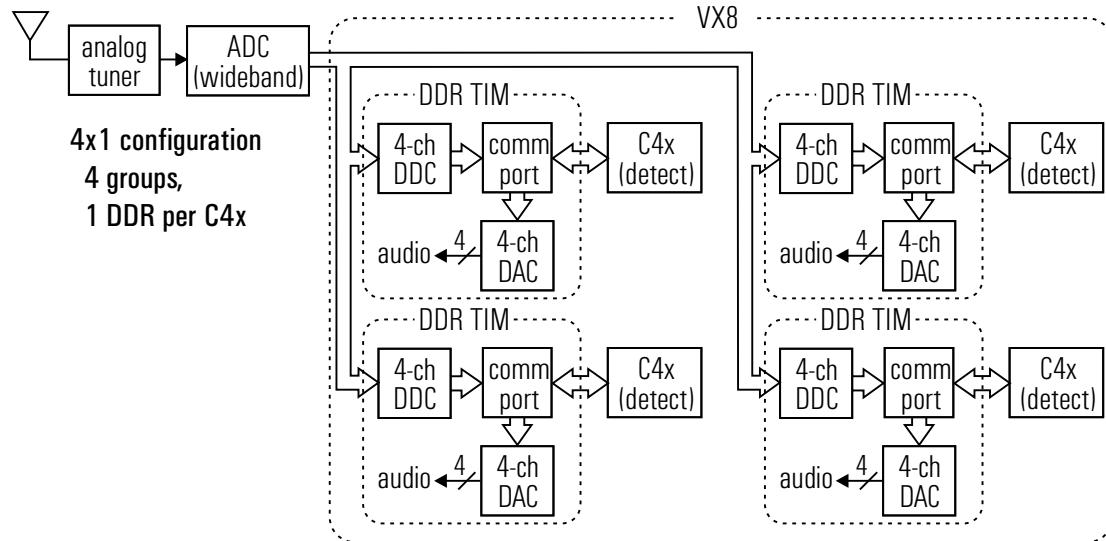

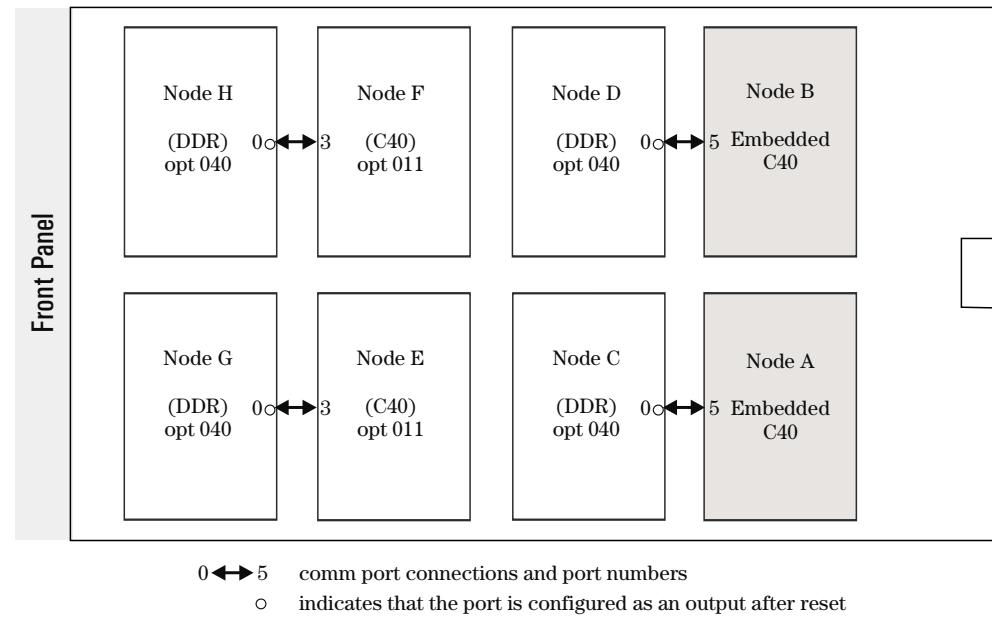

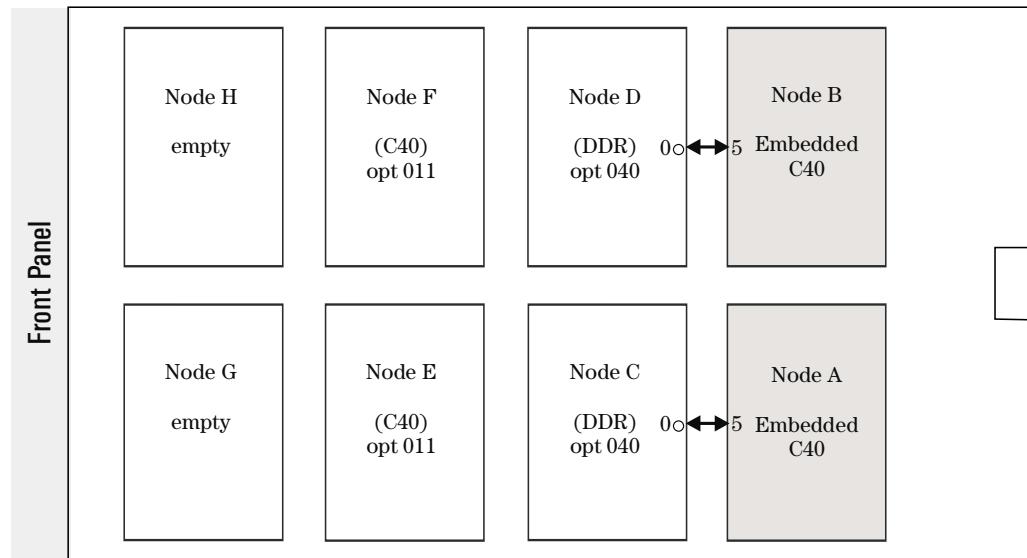

### 16-channel, 4ch/DSP

The configuration shown in the figure below could be created by adding C40 TIM boards at nodes E and F and DDR TIMs at nodes C, D, G, and H. These can be grouped with one DDR per C40 and identified as groups A-C, B-D, E-G, and F-H.

This configuration offers the highest performance (DSP/channel) and most flexibility (4 different bandwidths processed simultaneously). The VX8 board would be loaded as shown in the figure below.

Detailed installation information for this configuration exists on page 68.

---

## System Software Development

---

### Overview

Software development for HP's DDR TIM module involves the following tasks:

- Development of software that runs on the host computer (VXI slot 0 controller) that communicates with and controls the VX8 and other VXI modules. This software is referred to as the *host program*.

- Development of software that runs in the target DSP (VX8 C4x DSP) that controls local resources on the VX8 (e.g. HP DDR TIM) and other resources within the VXI chassis (e.g. ADC). This software is referred to as the *target program*.

- Development of a command, control, data, and synchronization interface between the host and target programs to coordinate overall system operation.

This is an iterative development process whereby coordinated changes in the host and target software must be made. This allows incremental progress in the overall system development while the host and target programs continue to work in concert with one another. Host and target software examples and target source code are supplied to help enable the learning process.

---

### Software Requirements

Software development for a VXI system containing HP's DDR TIM module requires a working knowledge of the following subject areas:

- “C” programming language. “C” is the primary software development language used in both the host and target development environments. Even though it is not required, it is recommended that the target software developer also have a working knowledge of the TMS320C4x assembly language.

- VXI architecture. For more about VXI, please refer to *Feeling Comfortable with VXI*, HP PN: 5965-6497E. For detailed insight, see IEEE Std. 1155-1992 *IEEE Standard for VMEbus Extensions for Instrumentation: VXIbus* or IEEE Std. 1014-1987, *IEEE Standard for a Versatile Backplane Bus: VMEbus*.

- VX8 DSP VXI module architecture. For detailed insight into the VX8, please refer to both the Technical Reference Manual and the Programming Guide supplied with the VX8 from Spectrum Signal Processing.

- TMS320C4x DSP architecture. For detailed insight into the TMS320C4x architecture, please refer to the TMS320C4x User's Guide supplied with the VX8 from Texas Instruments.

- Host and target software development environments. This includes compilers, linkers, debuggers and build tools (e.g. “make”). For host development, one of the following environments is recommended:

- HP-UX Workstations: “ANSI-C Development Bundle”

- PC Workstations: Microsoft Visual C++ (version 5.0 or later)

For target development, you need Texas Instrument's TMS320C4x Code Generation Tools, Revision 4.70. It is recommended that you have the PC Release of these tools. In addition to the basic Texas Instrument's code generation toolset, it is also

recommended that a third-party debugger/development toolset be employed for target development, e.g. GO DSP's Code Composer.

---

## Hardware Requirements

Software development for a VXI system containing HP's DDR TIM module requires the following hardware:

- VXI chassis with slot 0 controller. The slot 0 controller can be either an HP-UX or PC workstation. HP-UX support includes both embedded (E1498A) and external (via E1482B MXI) controllers. PC support includes both embedded (E623xA) and external (via National Instrument's VXI-PCI8000) controllers.

Once the appropriate controller has been chosen, you must install and configure the appropriate I/O layer libraries to communicate with the VXI backplane. Choices of I/O layers include either SICL (Standard Instrument Control Language) or VISA (Virtual Instrument System Architecture). Refer to the documentation for your particular slot 0 controller for more details.

- A VX8 Carrier module with shared DRAM SIMM and one or more HP DDR TIM modules installed. For details on installing the shared DRAM SIMM, please refer to Spectrum's VX8 Carrier Board Installation Guide. For details on installing the HP DDR TIM, please refer Hardware Installation on page 4.

- An external PC with XDS debugger hardware. This external PC is the target software development workstation. This PC should have the TI TMS320C4x code generation tools loaded as well as any third-party development tools (described in Software Requirements section). This PC interfaces with the VX8 via the XDS debugger hardware through the VX8's front panel JTAG connector.

The XDS debugger hardware consists of a plug-in PC card with a ribbon-cabled pod. This ribbon-cabled pod coming from the PC connects to a small JTAG conversion board that provides a connection to the JTAG connector on the VX8 front panel.

The XDS debugger hardware is available from either Texas Instruments (XDS-510) or Spectrum Signal Processing (XDSC40). The JTAG conversion board and VX8 JTAG cable is available as a development option to the VX8.

## HPVX8 Library

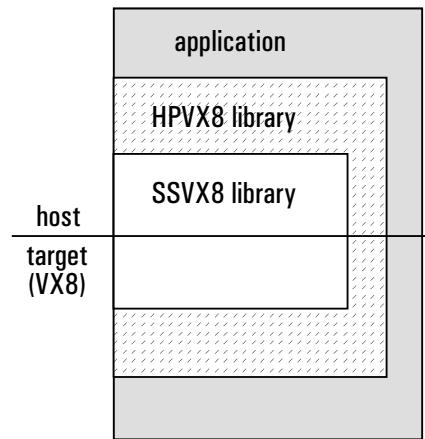

The hpvx8 library provides the means to quickly develop multi-channel, narrowband receiver systems based on the VX8 VXI carrier board, the HP DDR TIM module, and C40/C44 TIM modules. It provides control of the narrowband DDR channelizer modules as well as a method for a host program to communicate with a target program.

The hpvx8 library is built on top of Spectrum Signal Processing's ssvx8 host and DSP (target) libraries. The following figure illustrates how program layers in the host are used to communicate with their counterparts running on the target.

The hpvx8 communication strategy uses a FIFO-based, shared-memory method which also supports communication between DSP units on the VX8 carrier board. This method is one of many possible communication schemes; the source code is provided to allow the developer to explore this approach. The radio demonstration program is an example of how to use the library.

Further information concerning contents of individual files, messaging schemes, and build instructions resides in the `readme.txt` file in the `hpvx8` directory.

---

## Program Development

### Grouping

The hpvx8 library requires a group resource file (.grp) to organize C4x DSPs and DDR TIM boards into groups as well as providing some VX8 board setup information. Examples of the .grp file are in the hpvx8/hpradio directory (hpradio.grp) and the hpvx8/hpradio/resource directory (6 \*.grp files). These .grp files provide support for various hardware configurations and must match their corresponding .sdf files (see same directories).

The hpradio.grp file is used by the hpvx8 library to determine the groupings of C4x DSPs and DDR TIM modules. The concept of a group is used to describe a collection of processing and DDR components. For HP Radio, a group consists of 1 C4x DSP and 1, 2, or 3 DDR TIM modules. In general, systems built with the hpvx8 library define a group to be a C4x master and a number of C4x and DDR TIM slaves (limited by the number of communication ports). The C4x slaves can in turn have a number of C4x and DDR slaves. The HP Radio example restricts a group to one C4x master with only DDR modules as slaves.

The hpradio.grp file also specifies the number of VX8 boards in a system and some parameters specific to VX8s with DDR TIM modules. In general, the hpvx8 library allows any number of VX8 boards to be specified as long as they are all in the same VXIbus chassis. However, HP Radio is programmed to use only one board.

The hpradio.grp file also defines the following DDR parameters:

- the HP local bus mode

- HP local bus DMA wait states and target values

- mapping the IRQ connections.

In general, the .grp files provided in the resource subdirectory should either match or closely approximate the configuration of your VX8 hardware. Comments within the .grp file are provided to help you edit the file according to VX8 configuration.

---

**Note**

If using the HP E1430A digitizer, the DMA wait states parameter should be set to '5'. If using the HP E1437A digitizer, the DMA wait states should be set to '1'.

One digitizer should be selected as the clock ( $F_s$ ) master on the VXI backplane (ECLTRG1). Other digitizers and VX8s receive this clock. The DDR TIM cards should have their clock selection jumper removed to use this clock.

---

### System Definition

The system definition file (.sdf) is required by the ssvx8 library to specify the logical address used by the VX8 and the TIM modules installed. The group resource (.grp) file must match the hardware configuration described in the .sdf file. When the .grp file references an empty site, an error occurs. Note that the .grp file contains the names of the .sdf and .ldf that are used by the program accessing the .grp file. The .ldf (load definition file) is also used by the ssvx8 library to determine which target .out file gets loaded to each DSP. See page 12.

See Spectrum Signal Processing's *VX8 Carrier Board Programming Guide* for more information on the ssvx8 library and the .sdf and .ldf files. See the other readme.txt files distributed with this software for further system information.

The hpvx8 library source files that are involved in extracting information from the .grp and .sdf files are hpvx8res.h, hpvx8res.c, hpvx8sdf.h, and hpvx8sdf.c. The grouping concepts are used throughout the library and are defined and manipulated in hpvx8ifc.h and hpvx8ifc.c. Refer to these source files for more information.

## Host↔Target and Target↔Target Messaging

The hpvx8 library builds a communication system between the host and target groups and between target master nodes and their slaves. Recall that each group has one master C4x DSP. The communication takes place between the host and the master of a group and between a master node and its slaves. Any messages that need to be communicated to a slave node are first passed through the group master.

For host↔target messaging, a command and return-messaging FIFO structure is created in the VX8 shared DRAM. This requires that the VX8 have at least one 4 MB DRAM SIMM installed. The location of the messaging FIFOs are set at startup (see `hpvx8_system_open()` below). The hpvx8 library source files involved with host↔target communication are `hpvx8ifc.h` and `hpvx8ifc.c` on the host side and `hpvx8msg.h` and `hpvx8msg.c` on the DSP (or target) side. Refer to these source files for more information.

For target↔target messaging the same type of messaging FIFO structure is created in each of the slave's near-global SRAM. The hpvx8 library source files that are involved with target↔target communication are `hpvx8msg.h` and `hpvx8msg.c`. Refer to these source files for more information. The HP Radio example does not make use of hpvx8 library target↔target messaging.

## Host↔target Commands

A set of basic commands (and replies) are defined as a starting point for host↔target communication. Normally, an application requires a set of unique commands and replies which can easily be added to the basic set as long as the formats are kept the same. The list of defined commands and replies are as follows:

### HPVX8\_CMD\_AdcSetup

The group master that receives this command is responsible for monitoring and throttling the ADC.

### HPVX8\_CMD\_DdcSetup

The five-bit tag passed with this command is used to identify a DDR module. This information is encoded into each sample point coming out of the DDR module.

### HPVX8\_CMD\_AssignStat

This command assigns a channel statically, meaning it remains assigned until reassigned. The argument specifies a tuned frequency for the channel.

### HPVX8\_CMD\_AssignDyn

This command assigns a channel dynamically, meaning it is assigned until some specified signal-related condition causes it to be released. When the channel is released, the target returns a `_Released` message to the host (see below).

**HPVX8\_CMD\_Start**

This command starts the group, or moves the group from the configuration state to the process state. If a group did not receive an \_AdcSetup command, the HP local bus DMA is set up and waits for data. If a group did receive an \_AdcSetup command, it queries the ADC for block available before enabling the HP local bus DMA.

**HPVX8\_CMD\_Stop**

This command stops the group, or moves the group from the process state back into the configuration state.

**HPVX8\_CMD\_Ifbw**

This command sets the IF bandwidth for all DDR TIM modules in the group.

**HPVX8\_RET\_CmdReply**

This is a reply to any of the above commands. The target must issue a reply to the above commands. This is not a requirement for user-defined commands.

**HPVX8\_RET\_Released**

This reply is used to notify the host that a channel has been released due to a pre-specified condition of the data stream. It would occur only after a channel has been Assigned Dynamically (see above).

**HPVX8\_RET\_Error**

This message is used to notify the host that an error has occurred.

**HPVX8\_RET\_AdcError**

This message notifies the host that an ADC error has occurred. The error code is generated by ANDing the ADC status register contents and the error mask that is provided with the AdcSetup command. Note that this message can be sent only by nodes which have received the AdcSetup command.

See the file hpvx8cmd.h for more details on the format and description of these commands.

## Host Functions

The following functions are included in the hpvx8 host library (see `hpvx8ifc.c`).

**hpvx8\_system\_open(STRING rsrc\_file, HPVX8\_SYS \*sys, FLOAT64 time\_out)**

**Arguments:** `rsrc_file` – name of the group resource file (.grp)

`sys` – pointer to hpvx8 system to be created

`time_out` – time out (in seconds) parameter for all target accesses

**Returns:** Status

**Synopsis:** Opens a VX8 system and loads code to target DSPs.

1. First this function reads and parses the group resource file (.grp) to obtain information about the grouping of DSPs and DDRs

2. Then the group resource information is checked for validity.

3. Next, a call is made to `ssVX8_SystemOpen()` to open the VX8 system, reset it, and load code to the target DSPs. This call reads and parses the .sdf and .ldf files for information about the VX8 hardware. This information is extracted with a call to `parse_sdf()` and the hpvx8 system structure is then created.

4. Finally, the target DSP sites are set up and initialized and group messaging FIFOs are set up between the host and groups via shared memory.

---

**Note**

This function should be called before any calls are made to `hpvx8_group_read()` or `hpvx8_group_write()`.

Since this function handshakes with DSP function **HPVX8\_HOST\_MSG\_SETUP** (page 30), the DSP program *must* call the `msg_setup` function to allow a return. The `system_open` function does not return until `msg_setup` has performed its task

---

**hpvx8\_system\_close(HPVX8\_SYS \*sys)**

**Arguments:** `sys` – hpvx8 system structure pointer

**Returns:** Status

**Synopsis:** Close system, shutdown VX8 hardware.

---

**Note**

This function should be called last, after all processing is finished.

---

**hpvx8\_group\_read(HPVX8\_GRP \*grp, PVOID data, PUINT32 length)**

**Arguments:** `grp` – pointer to hpvx8 group

`data` – pointer to buffer where data will be placed

`length` – pointer to length of data read (to be returned)

**Returns:** Status

**Synopsis:** Read data from group return messaging FIFO.

Each group has a pair of messaging FIFOs: the *command FIFO* is used to write data from the host to the group DSP; the *return FIFO* is used to read data from the group DSP to the host. The return messages have a *message identifier* word which includes a length field defining the number of words in the rest of the message.

This routine first reads the identifier word, then determines the length of the rest of the message, and then reads the rest of the message. The routine must wait for data

to be available. A time-out timer is used to ensure the routine doesn't hang. The time-out interval can be set with the `hpvx8_set_time_out()` routine.

---

**Note**

This routine can be called only after `hpvx8_system_open()` is called.

**`hpvx8_group_write(HPVX8_GRP *grp, PVOID data, UINT32 length)`**

**Arguments:** `grp` – pointer to `hpvx8` group

`data` – pointer to data buffer to be written

`length` – length of data read (to be returned)

**Returns:** Status

**Synopsis:** Write data to group command messaging FIFO.

Each group has a pair of messaging FIFOs: the command FIFO is used to write data from the host to the group DSP and the return FIFO is used to read data from the group DSP to the host. In the `hpvx8` scheme, the first word of the data is a command which includes a command field and a data length field. This is followed by `length` data words. A total of `length + 1` words are written.

This routine first checks the command messaging FIFO for room to place `length` words of data into it. Once room is available, the 'data' is written to the FIFO. Note that time-outs are used to make sure the routine doesn't hang. The time-out interval can be set with the `hpvx8_set_time_out()` routine.

---

**Note**

This routine can be called only after `hpvx8_system_open()` is called.

**`hpvx8_error_query(RESULT error, STRING error_msg)`**

**Arguments:** `error` – error number to be matched with error message

`error_msg` – string pointer to be filled with error message

**Returns:** Status

**Synopsis:** This routine returns a descriptive error message corresponding to the error number passed to it. The error message is obtained by querying the `ssvx8` library, the `hpvx8` library and finally the SICL or VISA library. In the case of an `hpvx8` error, the error message will contain some additional details that are set by the function setting the error. These details are set by calling `set_error_detail()`. Note that the detail is a static variable so error reporting is inherently non-reentrant.

**`hpvx8_set_time_out(FLOAT64 time_out)`**

**Arguments:** `time_out` – time out value in seconds

**Returns:** void

**Synopsis:** This function is used to set the time-out value for VX8 system accesses. The time-out value is global and is used by all `hpvx8` functions that access the system.

## Host Programming Example

The following host .c file demonstrates the use of the most commonly used hpvx8 library function calls. This example simply opens a system as defined by the file hpradio.grp (and thus hpradio.sdf and hpradio.sdf), writes a command and reads the reply to that command for each group defined in the system, and then closes the system.

```

*****

/*

* Example program opens a system, writes the start command to each group, */

/* reads each group's reply, and then closes the system. */

/*

* WindowsNT/95 compile directions */

/* _____ */

/* For WindowsNT/95, be sure to define _WINDOWS and _VISA (via compiler). */

/* The necessary include files can be found in the following directories: */

/*

/* C:\vxipnp\winnt\include */

/* C:\vxipnp\winnt\ssvx8\host\include */

/* C:\vxipnp\winnt\hpvx8\hpvx8\host\include */

/*

/* This program needs to be linked with hpvx8.lib, ssvx8.lib, sdf.lib, */

/* and visa32.lib, all of which can be found in: */

/*

/* C:\vxipnp\winnt\lib\msc */

/*

/* Note: for Windows95, winnt becomes win95 in the above directory paths. */

/*

/* HP-UX compile directions */

/* _____ */

/* For HP-UX, be sure to define _HPUX and _SICL (or _VISA). The necessary */

/* include files can be found in the following directories: */

/*

/* /opt/vxipnp/hpux/include */

/* /opt/vxipnp/hpux/ssvx8/host/include */

/* /opt/vxipnp/hpux/hpvx8/hpvx8/host/include */

/*

/* This program needs to be linked with libhpvx8.a, libssvx8.a, and */

/* libsdf.a, which can be found in: */

/*

/* /opt/vxipnp/hpux/lib */

/*

/* Be sure to use the -lsicl (-lvisa) flag to link in the appropriate */

/* library. */

/*

*****

#include <stdio.h>

#include "hpvx8.h"

void main(void)

{

RESULT status;                      /* function return status */

HPVX8_SYS sys;                     /* hpvx8 system structure */

char error_msg[HPVX8_ERROR_MSG_SIZE]; /* error message buffer */

HPVX8_GRP *gp;                     /* group pointer */

UINT32 msg_buf[2];                 /* message buffer */

UINT32 msg_len;                   /* message length */

```

```

/* open system with no timeout */

status = hpvx8_system_open("hpradio.grp", &sys, HPVX8_INFINITE_TIME);

if (status != SUCCESS)

{

hpvx8_error_query(status, error_msg);

printf("Error during open: %s\n", error_msg);

exit(status);

}

/* send start command to each group defined in system */

for (gp = sys.group; gp != NULL; gp = gp->next)

{

/* send command */

msg_buf[0] = HPVX8_CMD_Start;

status = hpvx8_group_write(gp, msg_buf, 1);

if (status != SUCCESS) break;

/* read reply from group */

status = hpvx8_group_read(gp, msg_buf, &msg_len);

if (status != SUCCESS) break;

/* is reply what we're expecting? */

if ((msg_buf[0] != HPVX8_RET_CmdReply) || (msg_buf[1] != SUCCESS))

{

printf("Error, group '%s' sent bad reply\n", gp->name);

break;

}

}

/* report error before closing */

if (status != SUCCESS)

{

hpvx8_error_query(status, error_msg);

printf("Error while communicating with group '%s': %s\n",

gp->name, error_msg);

}

/* close system */

hpvx8_system_close(&sys);

exit(status);

}

```

## Target Functions

The following functions make up the hpvx8 target library (see `hpvx8msg.c`).

### `hpvx8_host_msg_setup(HPVX8_SITE *site)`

**Arguments:** `site` – pointer to site information, to be copied from host

**Returns:** Pointer to the host↔site message FIFOs

**Synopsis:** This routine synchronizes with the host via handshakes to ensure that:

1. the DSP target code gets started at the right time

2. the site setup information is transferred and read at the right time

The pointers to the host↔site messaging FIFOs are derived from the site setup information and returned.

### `hpvx8_master_msg_setup(UINT32 site_id)`

**Arguments:** `site_id` – site id of the slave

**Returns:** Pointer to the master↔slave messaging FIFO

**Synopsis:** This routine is used to set up messaging between the master (DSP) of a group and one of its slave nodes. Program synchronization between the nodes also occurs.

This routine should be called only by the master node. The slaves should call `hpvx8_slave_msg_setup()` to synchronize with their master. The master must call this routine once for each of its slaves.

The messaging FIFOs are of the same type as the host↔target messaging FIFOs.

### `hpvx8_slave_msg_setup()`

**Arguments:** void

**Returns:** Pointer to the master↔slave messaging FIFO

**Synopsis:** This routine is used to set up messaging between the calling slave (DSP) and its master. Program synchronization between the two also occurs.

This routine should be called only by a slave. A master should call `hpvx8_master_msg_setup()` to synchronize with its slaves.

The messaging FIFOs are the same type as the host↔target messaging FIFOs.

### `hpvx8_msg_cmd_level(HPVX8_MSG *msg)`

**Arguments:** `msg` – address of messaging structure

**Returns:** Number of slots filled with data in the command FIFO

### `hpvx8_msg_ret_level(HPVX8_MSG *msg)`

**Arguments:** `msg` – address of messaging structure

**Returns:** Number of slots filled with data in the return FIFO

**hpvx8\_msg\_cmd\_read(HPVX8\_MSG \*msg, UINT32 cmd[], UINT32 length)**

**Arguments:** **msg** – address of messaging structure

**cmd** – pointer to return data, read from FIFO

**length** – amount of data to be read from FIFO

**Returns:** void

**Synopsis:** Reads data from command messaging FIFO.

You must call hpvx8\_msg\_cmd\_level() prior to this command to determine the number of words to read. That is, the data must exist in the FIFO before this routine reads it.

**hpvx8\_msg\_cmd\_write(HPVX8\_MSG \*msg, UINT32 cmd[], UINT32 length)**

**Arguments:** **msg** – address of messaging structure

**cmd** – pointer to data to be written to FIFO

**length** – amount of data to be written to FIFO

**Returns:** void

**Synopsis:** Writes data to command messaging FIFO.

You must call hpvx8\_msg\_cmd\_level() prior to this command to make sure that there is enough room in the command FIFO to write the data.

**hpvx8\_msg\_ret\_read(HPVX8\_MSG \*msg, UINT32 ret[], UINT32 length)**

**Arguments:** **msg** – address of messaging structure

**ret** – pointer to return data, read from FIFO

**length** – amount of data to be read from FIFO

**Returns:** void

**Synopsis:** Reads data from return messaging FIFO.

You must call hpvx8\_msg\_ret\_level() prior to this command to determine the number of words to read. That is, the data must exist in the FIFO before this routine reads it.

**hpvx8\_msg\_ret\_write(HPVX8\_MSG \*msg, UINT32 ret[], UINT32 length)**

**Arguments:** **msg** – address of messaging structure

**ret** – pointer to data to be written to FIFO

**length** – amount of data to be written to FIFO

**Returns:** void

**Synopsis:** Writes data to return messaging FIFO.

You must call hpvx8\_msg\_ret\_level() prior to this command to make sure that there is enough room in the return FIFO to write the data.

## Target Programming Example

The radio target code provides an example of using the hpvx8 target functions. Refer to source files in \hpvx8\radio\dsp for details.

## DDR Interface Programming

This section describes the sub-directories and files contained in the \vxipnp\winXX\hpvx8\ddrifc directory on WindowNT/95 systems and the /opt/vxipnp/hpux/hpvx8/ddrifc directory on HP-UX systems.

```

dsp/          # DSP (C4x) target code

include/      # C4x include directory

ddr.h       # C4x<->DDR TIM interface header file

src/          # C4x C source directory

ddr.c       # C4x<->DDR TIM interface C source file

```

The purpose of each file will be described in sections that follow.

### DDR TIM hardware overview

A digital drop receiver usually performs three functions:

1. Channelization and down-conversion of broadband digital data

2. Signal detection or demodulation to extract information

3. Converting information to analog audio output

"Channelization" means to extract a narrowband signal at a specific center frequency from a wideband digital data stream.

The DDR TIM provides functions #1 and #3 with four channels of DDCs and four channels of DACs. The DDR TIM is connected to a C4x DSP processor via a communication port. The C4x DSP processor provides the function #2 portion of the digital drop receiver.

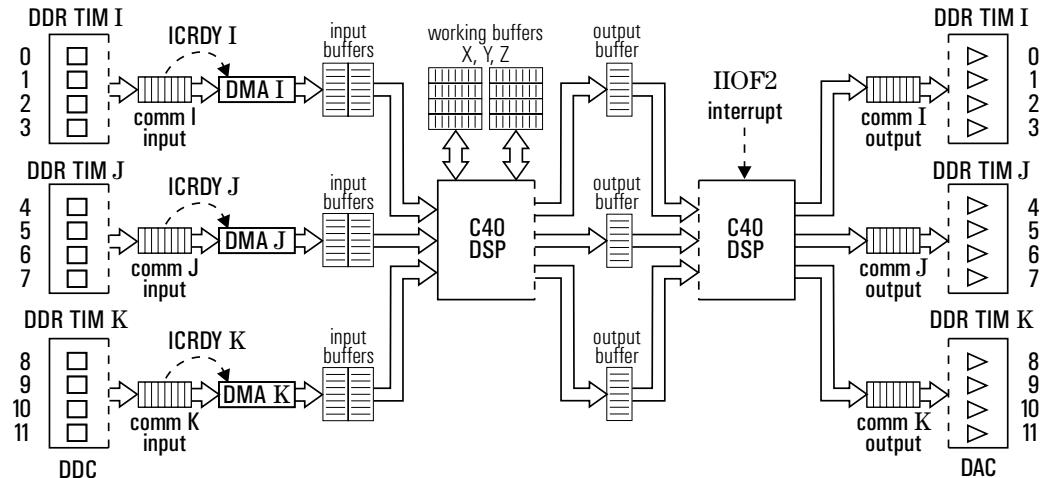

**Data Flow** The source of the broadband digital data is a VXIbus digitizer (ADC) such as the HP E1430A (10 Msamples/sec) or HP E1437A (20 Msamples/sec). The ADC sends real (unmixed), 16-bit data to the VX8 via the HP local bus. The HP local bus receiver on the VX8 moves the data into a 1024-word FIFO. This data is then moved to any (or all) of the six TIM sites and the two onboard C40s via a dedicated DMA controller.

The ADC sends the data as two 16-bit samples packed into a 32-bit word. This word is sent to the DDR TIM module in one of the six TIM sites. The two samples are extracted, optionally interleaved with 0-samples<sup>4</sup>, and then loaded into each of the four DDC chips. The interleaving and subsequent DDC filter operation is effectively an interpolate-by-2 operation. Interpolation is used with the E1430A to provide 20 Msamples/sec data to the DDC chips. This allows the same decimation steps to be used with both the E1430A and the E1437A since the effective sample rate seen at the DDC input will be 20 Msamples/sec for either ADC.

<sup>4</sup> Depends on the ADC installed. Not necessary with the E1437A.

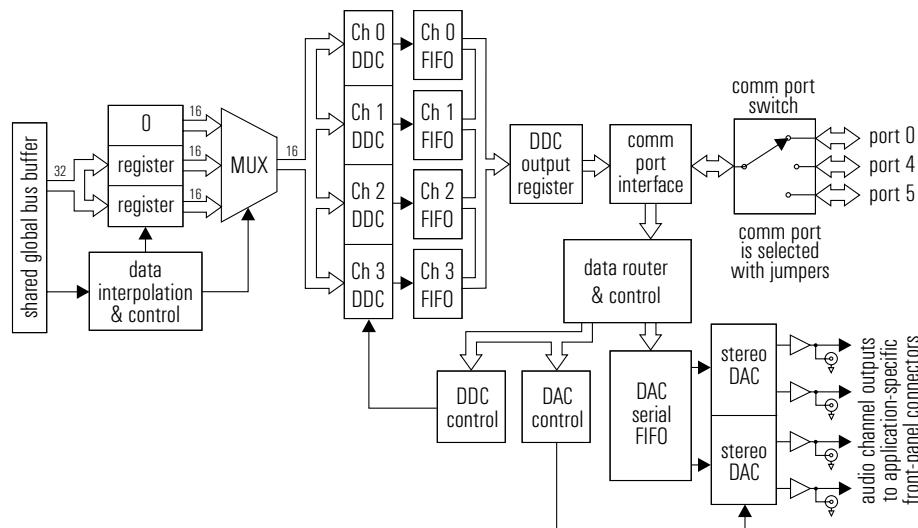

The DDC chip is the Harris Semiconductor HSP50016 digital downconverter. Each of the four DDCs accepts data from the same ADC data stream, mixes it with a unique programmable complex center frequency, and decimates the resulting complex signal to provide a 24-bit complex, channelized, and downconverted output signal. The decimation rate must be the same for each DDC on the module. A gate array on the DDR TIM module collects the output signals from each of the four DDCs, multiplexes them together, and then sends the collective data stream out a communication port to a C4x DSP.

The comm port interface (based on the C4x comm port) provides bi-directional data flow. Data from the DDCs is sent to the C4x while DDC control words are sent from the C4x to the DDR TIM module and then routed to the DDC chips on the module. The DDC control words allow the C4x DSP to set DDC parameters such as center frequency, decimation rate (or IF bandwidth) and gain, among others.

The channelized data from the DDCs are multiplexed and sent to the C4x in the following order:

```

channel 0 real

channel 0 imaginary

channel 1 real

channel 1 imaginary

channel 2 real

channel 2 imaginary

channel 3 real

channel 3 imaginary

```

This process repeats for each sample point. The data is sent in a 32-bit word (as per the C4x comm port specification) and contains a 24-bit real or imaginary sample point along with some identification information. See the **DDR Communication Formats** section (following) for more details. The DDR TIM module can be programmed to output data from either all 4 channels or just the first two channels, channels 0 and 1. The C4x should be ready to accept data from the DDR TIM (via its comm port) without delay since data can be missed if not read in a timely manner. As long as the C4x reads its input comm port FIFO such that the FIFO never becomes full, no data will be lost. Setting up an internal C4x DMA process to transfer data from the comm port to memory is an efficient way to manage this data flow. The 'radio' target example shows one way of doing this.

More information about the Harris Semiconductor HSP50016 DDC chip can be found at Harris' website, [www.semi.harris.com](http://www.semi.harris.com) under the 'Digital Signal Processing' link.

#### Comm Port Operation

The comm port interface is used to pass data and control words between the C4x DSP and the DDR TIMs. The operations allowed are as follows:

- send data from the DDCs to C4x DSP

- send data from the C4x DSP to the output audio DACs

- send control information to the DACs

- program the DAC decimation counter

- send control information to the DDCs

- configure the operation of the DDR TIM module

The data and control word formats are detailed in the **DDR Communication Formats** section (following).

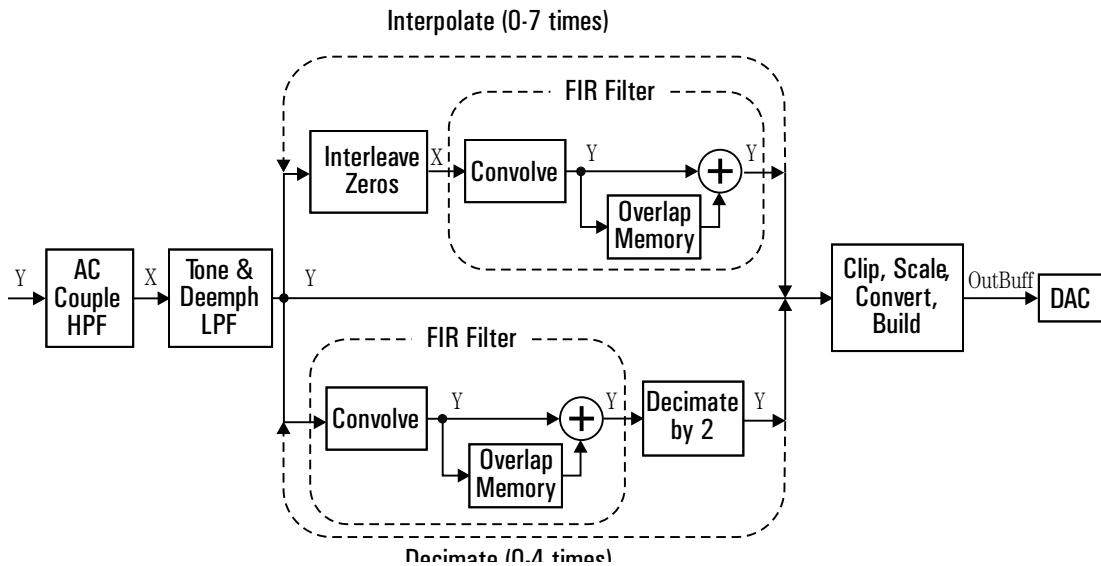

After the C4x DSP receives the channelized data and detects or demodulates it, it can optionally send the audio information contained in the signal back to the DDR TIM module's onboard audio DACs. Each of the four DACs is sent a 16-bit real audio data stream in the format described in the **DDR Communication Formats** section. The data must always be sent in channel pairs (i.e. channels 0 and 1, and then channels 2 and 3). Even if only one audio channel is being utilized, its paired channel must have data sent to it.

The DAC has a decimation counter associated with it to provide control over the output sample rate. The counter divides the ADC sample rate by the number it is programmed to. The ADC clock and the DAC clock must be synchronized to ensure that data flows at the appropriate rate through the system. If these clocks were not derived from the same source, data starvation or overflow could occur. The DAC decimation counter should be programmed with the rate equal to the decimation rate of the DDCs, scaled up (or down) for any interpolation (or decimation) that the C4x DSP program performs in its processing. The audio DACs accept any DAC sample rate within the octave 16.276 kHz to 32.552 kHz.

For the demodulated audio signal data rate to fall within this octave, the C4x program must interpolate or decimate the DDC's output sample rate by the appropriate factor of two. For example, if the system is using an E1437A with a sample rate of 20.48 MHz and the DDCs are programmed to decimate by 2048, the DDCs send a stream of 10 kHz (10 ksa/sec) data to the C4x for detection. Somewhere in the processing flow the C4x program must interpolate this data stream by 2 to get its data rate to fall within the DAC's allowed octave.

The DACs' analog audio output signals are buffered and connected to the VX8's front panel via the application specific connector. The mapping of each TIM site's audio outputs and the front panel connector pins is provided in the table on page 7.

### DDR Communication Formats

The DDR data and control word formats are provided below. Each data word is 32-bits wide, as specified by the C4x comm port.

- DDC data word (from DDR to DSP)

```

bits 31- 8: 24-bit real or imaginary data, 2's-complement

bits 7- 3: copy of tag field in control register, allows DDR id

bits 2- 1: indicates data came from DDC channel number (0-3)

bit      0: indicates data is real (0) or imaginary (1)

```

Bits 7-0 are forced to 0 unless the DDCINFO flag in the control register is set to 1.

- DAC data word format (from DSP to DDR)

```

bits 31-16: 16-bit 2's-complement audio data

bits 15- 8: set these bits to 0

bits 7- 4: command id (0x1)

bits 3- 2: set these bits to 0

bits 1- 0: the DAC ch. to which audio data should be routed (0-3)

```

- DAC control word format (from DSP to DDR)

```

bits 31-24: set these bits to 0

bits 23-16: stereo DAC control word, where:

bit 23: if 0 select channel 0|2, else select channel 1|3

bit 22: if 1 mute output

bits 21-16: attenuation in dB (0-63)

bits 15- 8: set these bits to 0

bits 7- 4: command id (0x2)

bits 3- 1: set these bits to 0

bits      0: if 0 select DAC channels 0 and 1, else channels 2 and 3

```

The combination of bits 0 and 23 are used to select the channel to which the mute and attenuation parameters are sent:

| bit 0 | bit 23 | DAC channel |

|-------|--------|-------------|

| 0     | 0      | 0           |

| 0     | 1      | 1           |

| 1     | 0      | 2           |

| 1     | 1      | 3           |

- DAC decimation counter value (from DSP to DDR)

```

bits 31-25: set these bits to 0

bits 24-16: 9-bit DAC decimation count-1 (clock divider)

bits 15- 8: set these bits to 0

bits  7- 0: command id (0x22)

```

See the `ddr.h` and `ddr.c` files for more information.

- DDC control start command (from DSP to DDR)

```

bits 31- 8: set these bits to 0

bits  7- 0: command id (0x44)

```

This control command is required to start off the DDC control word sequence. To write to a particular DDC, write this word first, then write five consecutive DDC control bytes to make a 40-bit DDC control word value.

- DDC control word format (from DSP to DDR)

```

bits 31-24: set these bits to 0

bits 23-16: control byte, one of 5 in the 40-bit DDC control word

bits 15- 8: set these bits to 0

bits  7- 4: command id (0x4)

bits  3- 2: set these bits to 0

bits  1- 0: select DDC channel (0-3)

```

For more information on the 40-bit DDC control words, see the Harris Semiconductor HSP50016 DDC data sheet.

- DDR control register (from DSP to DDR)

```

bits 31-16: DDR control word, where:

bits 31-29: set these bits to 0

bits 28-24: tag field value gets inserted in bits 7-3 of each

DDC data word sent to C4x if DDCINFO is set to 1

bit    23: set this bit to 0

bit    22: DATAEN enables the data flow from DDC to comm port

(and then to DSP) when set to 1

bit    21: DDCINFO causes the DDC data information to be placed

in the lower bits of each data word when set to 1

bit    20: SYNCEN enables the 'DAC ready for data' interrupt

signal to DSP when set to 1

bit    19: CH2 limits the DDC output to two channels when set

to 1, four channels when cleared to 0

bit    18: INTERP activates the interpolator (L=2) when set to 1

(to be used with E1430A ADC)

bit    17: DACRST* resets the DAC circuitry when cleared to 0

bit    16: SRST* resets the entire DDR TIM when cleared to 0

bits 15- 8: set these bits to 0

bits  7- 0: command id (0x80)

```

Each bit in the control register (bits 31-16) is cleared to 0 on power-up, `iclear vxi`, or hard reset (VX8 reset).

### DDR Data Structures

To simplify the task of programming the DDR TIM module, a DDR library is provided (see `ddr.c`). The state of a DDR TIM module is contained in a structure of type `DDR_STATE` (see `ddr.h`). This structure has the following DDR TIM parameters:

- the C4x communication port the DDR TIM is connected to (`comm_port`)

- the DDC decimation value (`ddc_decimation`)

- the DAC decimation value (`dac_decimation`)

- the state of the DDR TIM control register SRST\* bit (`reset`)

0 =>reset, 1 =>not reset

- the state of the DDR TIM control register DACRST\* bit (`dac_reset`)

0 =>reset, 1 =>not reset

- the state of the DDR TIM control register INTERP bit (`interpolate`)

0 =>no interpolation (for E1437A), 1 =>interpolate (for E1430A)

- the state of the DDR TIM control register CH2 bit (`number_channels`)

0 =>4 channels, 1 =>2 channels

- the state of the DDR TIM control register SYNCEN bit (`sync_enable`)

0 =>disable, 1 =>enable

- the state of the DDR TIM control register DDCINFO bit (`ddc_info`)

(turns on tag, channel, & real/imag information bits in DDC words)

0 =>'00000000', 1 =>'tttttccr', where tttt =>tag, cc =>channel, r =>real(0)/imag(1)

- the state of the DDR TIM control register DATAEN bit (`data_enable`)

0 =>disable, 1 =>enable

- the DDR TIM control register tag field (`data_tag`). A 5-bit, user-defined tag placed in the lower byte of the DDC data (bits 7-3). Active only when the `ddc_info` bit is set.

- a set of four channel-specific parameters (`DDR_CHANNEL`):

- the DDC center frequency (`phase_increment`)

- the DDC spectrum type, up convert or normal (`spectrum_type`)

- the DDC spectrum reversal flag (`spectrum_reverse`)

- the DAC mute state (`mute`)

- the DAC attenuation value (`attenuation`)

The DDR library functions are used to control and communicate with the DDR TIM module and use the `DDR_STATE` to determine which parameters to set. Normally the desired `DDR_STATE` parameter is changed and then the appropriate function is called to make this change to the DDR TIM hardware. A list of DDR library functions follows:

## DDR Functions

Typically, the only functions required to setup and control DDRs are `ddr_new`, `ddr_init`, `ddr_delete`, and `ddr_set_all`. Functions used while running are `ddc_center`, `dac_control`, and `dac_set`. See example code for typical use.

### `ddr_new(long comm_port)`

**Arguments:** `comm_port` – C40 comm port to which the relevant DDR is attached