*LeMans*

**VX8 Carrier Board**

**Programming Guide**

Document Number 500-00330

Revision 2.02

September 1998

*Copyright © 1998 Spectrum Signal Processing Inc.*

*All rights reserved, including those to reproduce this document or parts thereof in any form without permission in writing from Spectrum Signal Processing Inc.*

*All trademarks are registered trademarks of their respective owners.*

*Spectrum Signal Processing reserves the right to change any of the information contained herein without notice.*

---

# Customer Feedback

At Spectrum, we recognize that product documentation that is both accurate and easy to use is important in aiding you in your new product development. We appreciate hearing your comments on how our product's documentation could be improved.

If you wish to comment on any Spectrum documentation then please fax or e-mail a completed copy of this page to us.

Full Name of Document: \_\_\_\_\_

Document Number: \_\_\_\_\_ Version Number: \_\_\_\_\_

If you have found a technical inaccuracy please describe it here:

---

---

---

---

---

If you particularly liked or disliked an aspect of the manual then please describe it here:

---

---

---

---

---

It may be helpful for us to call you to discuss your comments. If this would be acceptable please provide the following details:

Name: \_\_\_\_\_ Telephone #: \_\_\_\_\_

Organization: \_\_\_\_\_

Thank you for your time,

Spectrum Signal Processing Documentation Group

Fax: (604) 421-1764

Email: documentation@spectrumsignal.com

---

# Contacting Spectrum...

Spectrum's team of dedicated Applications Engineers are available to provide technical support to you for this product. Our office hours are Monday to Friday, 8:00 AM to 5:00 PM, Pacific Standard Time.

Telephone      1-800-663-8986 or (604) 421-5422

Fax              (604) 421-1764

Email              support@spectrumsignal.com

Internet        <http://www.spectrumsignal.com>

When you contact us, please have the following information on hand:

- A concise description of the problem

- The name of all Spectrum hardware components

- The name and version number of all Spectrum software components

- The minimum amount of code that demonstrates the problem

- The version number of all software packages, including compilers and operating systems

---

# Preface

Spectrum Signal Processing offers a complete line of DSP hardware, software and I/O products for the DSP Systems market based on the latest DSP microprocessors, bus interface standards, I/O standards and software development environments. By delivering quality products, and DSP expertise tailored to specific application requirements, Spectrum can consistently exceed the expectations of our customers. We pride ourselves in providing unrivaled pre and post sales support from our team of application engineers. Spectrum has excellent relationships with third party vendors which allows us to provide our customers with a more diverse and top quality product offering.

Spectrum achieved ISO 9001 quality certification in 1994.

As Spectrum's hardware products are static sensitive, please take precautions when handling and make sure they are protected against static discharge.

---

# Table of Contents

|                                                |               |

|------------------------------------------------|---------------|

| <b>1 Introduction .....</b>                    | <b>1</b>      |

| 1.1. Purpose of This Manual.....               | 1             |

| 1.2. Reference Documents.....                  | 1             |

| 1.3. Conventions Used in This Manual.....      | 2             |

| <br><b>2 Hardware Overview.....</b>            | <br><b>3</b>  |

| 2.1. Features .....                            | 3             |

| 2.1.1. TMS320C4x Nodes .....                   | 3             |

| 2.1.2. Bus Interfaces.....                     | 3             |

| 2.1.3. Diagnostic Support .....                | 4             |

| 2.2. Board Layout .....                        | 4             |

| 2.3. Front Panel .....                         | 5             |

| 2.3.1. Status LEDs.....                        | 6             |

| 2.3.2. Connectors .....                        | 6             |

| 2.4. C4x Communication Port Architecture ..... | 6             |

| 2.5. Bus Architecture .....                    | 8             |

| 2.6. C4x Interrupt Architecture.....           | 9             |

| 2.6.1. VXLbus Interrupts (IIOF0).....          | 10            |

| 2.6.2. HP Local Bus Interrupts (IIOF1) .....   | 11            |

| 2.6.3. Interrupt Routing Matrix (IIOF2).....   | 11            |

| 2.6.4. IIOF3 Interrupts.....                   | 11            |

| 2.7. JTAG Debugging .....                      | 12            |

| 2.7.1. JTAG Connection .....                   | 13            |

| 2.7.2. JTAG Software Setup .....               | 13            |

| 2.7.3. Debugging tips.....                     | 15            |

| <br><b>3 Software Overview .....</b>           | <br><b>17</b> |

| 3.1. Software Environment .....                | 17            |

| 3.1.1. Host Software Environment.....          | 18            |

| 3.1.2. DSP Software Environment.....           | 19            |

| 3.2. VX8 Support Software.....                 | 19            |

| 3.2.1. SICL/VISA VX8 Instrument Driver .....   | 20            |

| 3.2.2. VX8 C4x Support Software Library.....   | 20            |

| 3.2.3. Example Programs .....                  | 20            |

| 3.3. Data Types .....                          | 22            |

|                                                                      |    |

|----------------------------------------------------------------------|----|

| 3.4. Hardware and Software Requirements .....                        | 25 |

| <hr/>                                                                |    |

| 4 Reset Conditions and Initialization .....                          | 27 |

| 4.1. Reset .....                                                     | 27 |

| 4.1.1. Hard Reset.....                                               | 27 |

| 4.1.2. Soft Reset.....                                               | 27 |

| 4.2. Boot Kernel Initialization .....                                | 28 |

| <hr/>                                                                |    |

| 5 VX8 C4x Software System Description.....                           | 31 |

| 5.1. Introduction.....                                               | 31 |

| 5.2. Fundamentals of C4x Code Development.....                       | 31 |

| 5.2.1. Procedure for Getting a DSP C Program Running .....           | 31 |

| 5.2.2. Compiler Batch Files.....                                     | 33 |

| 5.2.3. Boot (Startup) Files.....                                     | 34 |

| 5.2.4. Linker Command Files.....                                     | 34 |

| 5.2.5. C4x DSP Local and Global Memory Maps .....                    | 35 |

| 5.3. Resources Required by the VX8 C4x Support Software Library..... | 35 |

| 5.3.1. Node A TMS320C40.....                                         | 35 |

| 5.3.2. Node B TMS320C40 and TIM-40 Based DSPs.....                   | 36 |

| <hr/>                                                                |    |

| 6 VX8 C4x Support Software .....                                     | 39 |

| 6.1. A16 Control Module.....                                         | 39 |

| 6.1.1. Description.....                                              | 39 |

| 6.1.2. A16 Control Function.....                                     | 40 |

| 6.2. Global Bus Interface Module .....                               | 40 |

| 6.2.1. Description.....                                              | 40 |

| 6.2.2. Global Bus Functions.....                                     | 41 |

| 6.2.3. Shared Bus Transfers.....                                     | 42 |

| 6.2.4. The Global Shared Bus Lock Stack.....                         | 42 |

| 6.3. VXIbus Interface Module .....                                   | 45 |

| 6.3.1. Description.....                                              | 45 |

| 6.3.2. VXIbus Functions.....                                         | 45 |

| 6.4. HP Local Bus Interface Module .....                             | 46 |

| 6.4.1. Description.....                                              | 46 |

| 6.4.2. HP Local Bus Interface Module Functions & Macros.....         | 47 |

| 6.5. Bus Locking .....                                               | 50 |

| 6.5.1. Why is Bus Locking Required?.....                             | 50 |

| 6.5.2. Automatic Bus Locking .....                                   | 50 |

| 6.5.3. Manual Bus Locking.....                                       | 50 |

| 6.5.4. How to Lock and Unlock the Global Shared Bus.....             | 50 |

| 6.5.5. Debugging Code With Bus Locking.....                          | 51 |

|                                           |    |

|-------------------------------------------|----|

| 6.5.6. Some Tips on Bus Locking.....      | 51 |

| 6.6. DUART Module .....                   | 53 |

| 6.6.1. Description.....                   | 53 |

| 6.6.2. DUART Functions.....               | 53 |

| <hr/>                                     |    |

| 7 VX8 C4x Support Software Functions..... | 55 |

| BOOT_IIOF3Isr .....                       | 56 |

| VX8_DUARTCheckInterrupt.....              | 57 |

| VX8_DUARTDisableInterrupt.....            | 58 |

| VX8_DUARTEnableInterrupt.....             | 59 |

| VX8_DUARTInByte .....                     | 60 |

| VX8_DUARTOutByte.....                     | 61 |

| VX8_DUARTSetBaudRate .....                | 62 |

| VX8_FastTransfer.....                     | 64 |

| VX8_HPCheckInterrupt .....                | 65 |

| VX8_HPClearInterrupt.....                 | 66 |

| VX8_HPDisableInterrupt.....               | 67 |

| VX8_HPEnableInterrupt .....               | 68 |

| VX8_HPGetContBit .....                    | 69 |

| VX8_HPGetDMABuffer.....                   | 70 |

| VX8_HPGetDMAEnable.....                   | 71 |

| VX8_HPGetDMAIncrement.....                | 72 |

| VX8_HPGetFrameBit.....                    | 73 |

| VX8_HPGetMode .....                       | 74 |

| VX8_HPGetPauseBit.....                    | 75 |

| VX8_HPGetRAEBit.....                      | 76 |

| VX8_HPGetRAFBit.....                      | 77 |

| VX8_HPGetReadDone .....                   | 78 |

| VX8_HPGetREBit .....                      | 79 |

| VX8_HPGetRFBit .....                      | 80 |

| VX8_HPGetStripBit.....                    | 81 |

| VX8_HPGetWAEBit.....                      | 82 |

| VX8_HPGetWAFBit .....                     | 83 |

| VX8_HPGetWEBit .....                      | 84 |

| VX8_HPGetWFBit .....                      | 85 |

| VX8_HPGetWriteDoneBit.....                | 86 |

| VX8_HPReadECL .....                       | 87 |

| VX8_HPReadTTL .....                       | 88 |

| VX8_HPReset.....                          | 89 |

| VX8_HPRestart .....                       | 90 |

| VX8_HPSetContBit.....                     | 91 |

| VX8_HPSetDMAEnable .....                  | 92 |

| VX8_HPSetDMAIncrement.....                | 93 |

|                                                       |     |

|-------------------------------------------------------|-----|

| VX8_HPSetDMATarget .....                              | 94  |

| VX8_HPSetFrameBit .....                               | 96  |

| VX8_HPSetMode .....                                   | 97  |

| VX8_HPSetReadDone .....                               | 99  |

| VX8_HPSetStripBit .....                               | 100 |

| VX8_HPSetWriteBlockSize .....                         | 101 |

| VX8_HPSetWriteDoneBit .....                           | 102 |

| VX8_HPSuspendDMA .....                                | 103 |

| VX8_HPWriteECL .....                                  | 104 |

| VX8_HPWriteFIFO .....                                 | 105 |

| VX8_HPWriteTTL .....                                  | 106 |

| VX8_Lock .....                                        | 107 |

| VX8_Read .....                                        | 108 |

| VX8_ReadAsyncReg .....                                | 110 |

| VX8_ReadBit .....                                     | 111 |

| VX8_ReadReg .....                                     | 112 |

| VX8_SCV64AckInterrupt .....                           | 113 |

| VX8_SCV64DisableInterrupt .....                       | 115 |

| VX8_SCV64DMATransfer .....                            | 116 |

| VX8_SCV64EnableInterrupt .....                        | 118 |

| VX8_SCV64GenerateInterrupt .....                      | 119 |

| VX8_SCV64SetSysFail .....                             | 120 |

| VX8_SetUserLED .....                                  | 121 |

| VX8_SCV64SetVXIBusReqRel .....                        | 122 |

| VX8_UnLock .....                                      | 124 |

| VX8_Write .....                                       | 125 |

| VX8_WriteBit .....                                    | 127 |

| VX8_WriteReg .....                                    | 128 |

| <hr/> 8 VX8 Host Software System Description .....    | 129 |

| 8.1. Introduction .....                               | 129 |

| 8.2. Host Software Development .....                  | 129 |

| <hr/> 9 VX8 SICL/VISA Instrument Driver .....         | 131 |

| 9.1. SICL Instrument Driver .....                     | 131 |

| 9.2. VISA Instrument Driver .....                     | 132 |

| 9.3. VXIpnnp Module .....                             | 134 |

| 9.4. System Module .....                              | 137 |

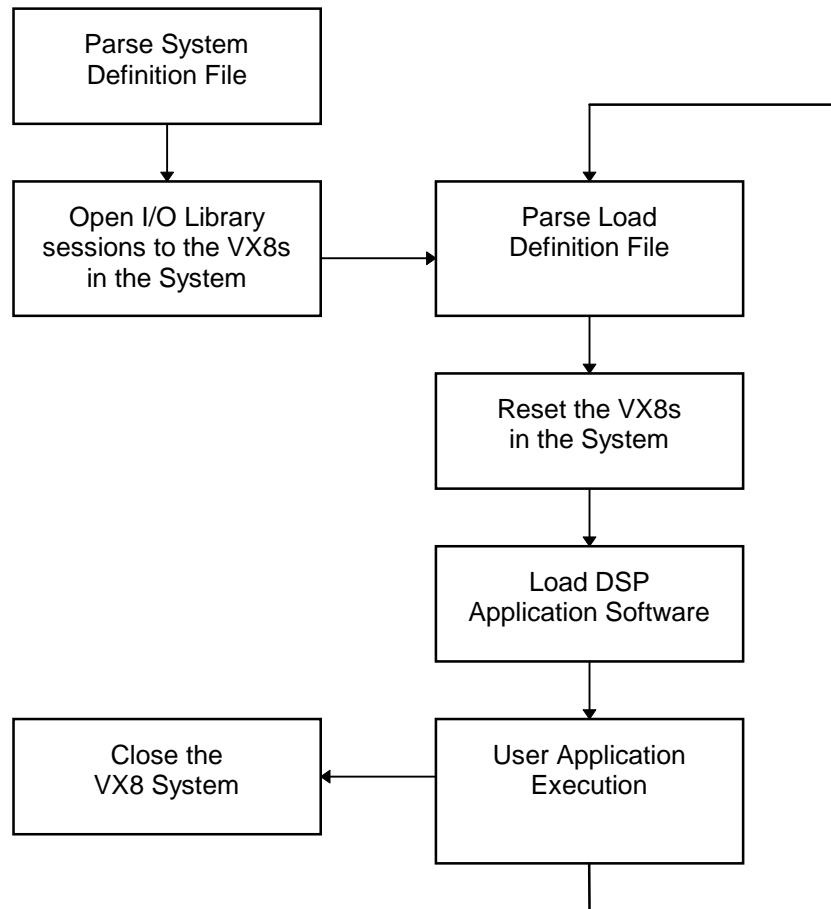

| 9.4.1. Opening a VX8 System .....                     | 139 |

| 9.4.2. System Definition File (SDF) Description ..... | 140 |

| 9.4.3. System Definition File (SDF) Examples .....    | 147 |

| 9.4.4. Load Definition File (LDF) .....               | 156 |

|                                                          |     |

|----------------------------------------------------------|-----|

| 9.4.5. Calling I/O Library Routines Directly.....        | 157 |

| <hr/>                                                    |     |

| 10 VX8 Instrument Driver Functions .....                 | 159 |

| ssVX8_close .....                                        | 160 |

| ssVX8_Deref.....                                         | 161 |

| ssVX8_error_message .....                                | 162 |

| ssVX8_error_query.....                                   | 163 |

| ssVX8_init.....                                          | 164 |

| ssVX8_open .....                                         | 165 |

| ssVX8_reset .....                                        | 166 |

| ssVX8_revision_query.....                                | 167 |

| ssVX8_self_test.....                                     | 168 |

| ssVX8_SystemCheckConfig.....                             | 169 |

| ssVX8_SystemClose .....                                  | 170 |

| ssVX8_SystemErrorMessage.....                            | 171 |

| ssVX8_SystemRevisionQuery.....                           | 172 |

| ssVX8_SystemGetDriverRev.....                            | 173 |

| ssVX8_SystemLoadCode.....                                | 174 |

| ssVX8_SystemOpen.....                                    | 177 |

| ssVX8_SystemRead.....                                    | 180 |

| ssVX8_SystemReset.....                                   | 182 |

| ssVX8_SystemWrite.....                                   | 183 |

| <hr/>                                                    |     |

| 11 Example Software .....                                | 185 |

| 11.1. Floating Point Multiplication Example.....         | 185 |

| 11.2. Node B DUART and C4x ISR Example.....              | 187 |

| 11.3. C4x HP Local Bus Consume Mode and ISR Example..... | 189 |

| 11.4. C4x HP Local Bus Generate Mode Example .....       | 190 |

| 11.5. C4x IIOF2 Interrupt Matrix Example.....            | 192 |

| 11.6. SCV64 Interrupt and Location Monitor Example ..... | 193 |

| 11.7. VXIbus (SCV64) DMA Example .....                   | 195 |

| 11.8. VX8 VXIbus Master Example .....                    | 197 |

---

## List of Figures

|                                                               |     |

|---------------------------------------------------------------|-----|

| Figure 1 VX8 Carrier Board Layout.....                        | 4   |

| Figure 2 VX8 Front Panel.....                                 | 5   |

| Figure 3 Communication Port Routing.....                      | 7   |

| Figure 4 Bus Architecture.....                                | 9   |

| Figure 5 VX8 Interrupt Architecture.....                      | 10  |

| Figure 6 VX8 Software Environment.....                        | 18  |

| Figure 7 Building an Executable File.....                     | 32  |

| Figure 8 HP Local Bus Operation .....                         | 46  |

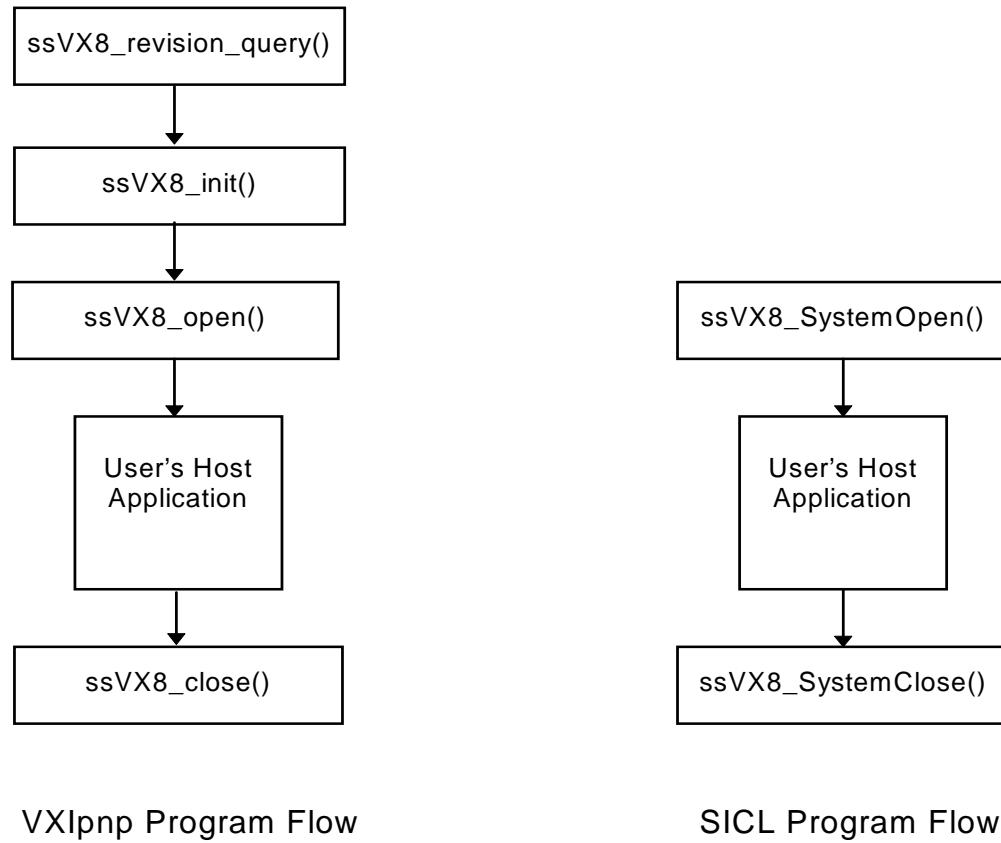

| Figure 9 SICL Instrument Driver Program Flow.....             | 131 |

| Figure 10 VISA Instrument Driver Program Flow.....            | 132 |

| Figure 11 VXIppn Instrument Driver Internal Design Model..... | 134 |

| Figure 12 Program Flow VXIppn vs. SICL.....                   | 136 |

| Figure 13 Instrument Driver Program Flow.....                 | 139 |

---

## List of Tables

|                                                                   |     |

|-------------------------------------------------------------------|-----|

| Table 1 Symbolic Constants Used in the Example Programs.....      | 21  |

| Table 2 Data Types.....                                           | 23  |

| Table 3 Boot Kernel Initialization.....                           | 28  |

| Table 4 Node A Memory Restrictions .....                          | 35  |

| Table 5 Prefixes Used in the VX8 C4x Support Software.....        | 39  |

| Table 6 A16 Control Function .....                                | 40  |

| Table 7 Global Shared and DRAM Shared Bus Functions.....          | 41  |

| Table 8 VXIbus Related Functions.....                             | 45  |

| Table 9 HP Local Bus Initialization/Status Functions.....         | 47  |

| Table 10 HP Local Bus CONSUME Functions .....                     | 48  |

| Table 11 HP Local Bus GENERATE Functions.....                     | 48  |

| Table 12 HP Local Bus Extended Functionality.....                 | 49  |

| Table 13 Accesses to Shared Resources Affect Other Resources..... | 52  |

| Table 14 DUART Functions .....                                    | 53  |

| Table 15 DUART Macros.....                                        | 53  |

| Table 16 BALLISTIC Modes .....                                    | 98  |

| Table 17 VXIppn Module Functions.....                             | 135 |

| Table 18 System Module Functions.....                             | 138 |

| Table 19 Status Codes for DSP functions.....                      | 201 |

| Table 20 Status codes for Host functions .....                    | 203 |

---

# 1 Introduction

## 1.1. Purpose of This Manual

This manual provides the information you need to develop VXIbus system applications using Spectrum's VX8 VXIbus TIM-40 Carrier Board. The manual describes the host and DSP libraries used to program and interface to the VX8s in your system. Helpful programming methods, tips, and software examples are also provided.

A second manual, the *VX8 Carrier Board Technical Reference Manual* (TRM), is the primary hardware reference. You must be familiar with this manual in order to develop system architecture and data flow paths. The TRM is also the primary reference for modifying or extending the functionality of the driver.

---

**Caution:** The hardware interfaces of the VX8 Carrier Board are extremely complex and interrelated. You are strongly urged to make use of the supplied C40 software control libraries to initialize and transfer data to the hardware interfaces.

---

## 1.2. Reference Documents

This guide is meant to be used in conjunction with the following documents:

- *VX8 Carrier Board Technical Reference Manual* available from Spectrum

- *VX8 Carrier Board Installation Guide* available from Spectrum

- *VMEbus Extensions for Instrumentation (VXIbus) VXI-1* Revision 1.4. Authored by the VXIbus Consortium, Inc.

- *TMS320C4x User's Guide* available from Texas Instruments

- *TMS320C4x C Source Debugger User's Guide* available from Texas Instruments

- *TMS320 Floating-Point DSP Assembly Language Tools User's Guide* available from Texas Instruments

- *TMS320 Floating-Point DSP Optimizing C Compiler User's Guide* available from Texas Instruments

- *Getting Started Guide* from Texas Instruments

- *VXIplnp documents* - VXIplug&play Systems Alliance

- *SCV64 User Manual - VMEbus Interface Components Manual* from Tundra Semiconductor Corporation

- *XDSC40 Board MS-DOS User Guide* available from Spectrum

- *BALLISTIC VXIbus Interface Chip Data Sheet* available from Hewlett-Packard

## 1.3. Conventions Used in This Manual

This guide uses the following conventions:

- *Italic* font is used to designate placeholder names, such as command parameter names, cross-references, and references to other documents. For example:

A second manual, the *VX8 Carrier Board Technical Reference Manual* (TRM), is the primary hardware reference.

- **Bold** font is used to emphasize text within paragraphs. For example:

If you edit the **board.cfg** file, you'll have to run **composer.exe** with the file.

- *This* font is used to designate contents of text files (source code, configuration files), filenames, directory names, text that appears on the screen, and commands that you must enter in an interactive display. For example:

These strings should be defined in the [common] section.

- An “h” after a number indicates that this is hexadecimal notation (base 16). For example:

This write-only register is located at address 8B00 0000h on the Shared DRAM Bus.

- “0x” before a number indicates that this is hexadecimal notation (base 16). For example:

The default TIM-40 based DSP linker command file **vx8\_tim.cmd** also defines the space COM\_KERNEL at address 0x8000 0000 with length 0x100 (1 Kbyte).

---

## 2 Hardware Overview

### 2.1. Features

Spectrum's VX8 Carrier Board is a VXIbus based multiple DSP processing engine.

#### 2.1.1. TMS320C4x Nodes

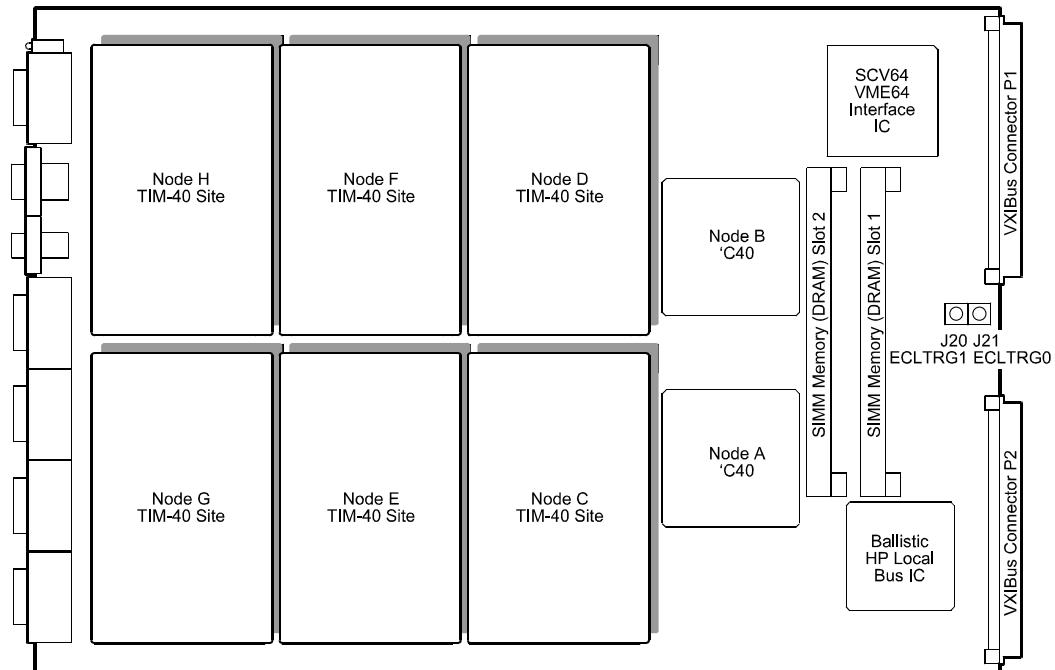

Six TIM-40 sites and two on-board 60 MHz TMS320C40 (C40) processors are incorporated onto the VX8 Carrier Board. The embedded C40s are nodes A and B, and the TIM-40 sites are nodes C to H. Each node has one buffered C4x communication port brought to the front panel.

Each embedded node (A and B) features:

- One bank of 128k x 32 SRAM on both the local and global buses for a total of 1 Mbytes per C40. (Upgradeable to 512 x 32 SRAMs at the factory;)

- One 32kx8 PEROM for booting or TIM-40 IDROM compatibility on the local bus;

- Global bus signals routed to buffers to allow for HP Local Bus DMA controlled data writes to global SRAM;

- The capability to write to the HP Local Bus output FIFO or to access the shared global DRAM through the global bus connector; and

- The capability to access the SCV64 IC to act as a VXIbus master.

Node A has an additional 32k x 8 PEROM used for the board's boot kernel.

Node B has a DUART equipped with RS-232 drivers brought to the front panel Dual RS-232 asynchronous serial ports.

#### 2.1.2. Bus Interfaces

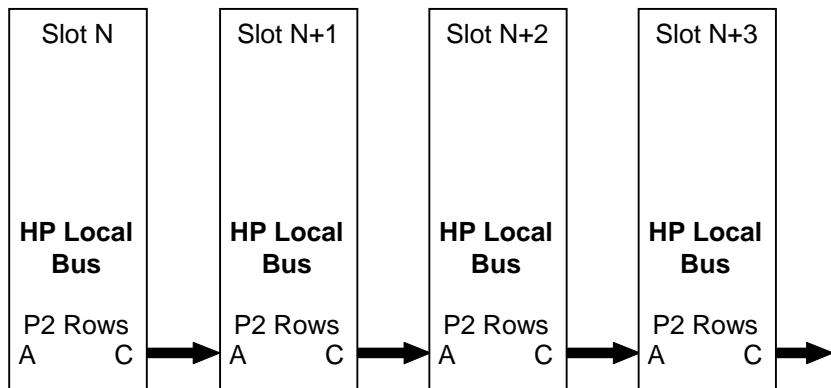

The VX8 has a register based VXIbus interface incorporating an optional Hewlett-Packard (HP) local bus interface. The HP Local Bus interface uses a high speed BALLISTIC interface chip and an intelligent DMA controller.

The VX8 can function as either a Master or as a Slave module on the VXIbus. VXIbus D32, D16, and D08E0 data access is supported in the following address modes:

| Address Mode | Master | Slave                 |

|--------------|--------|-----------------------|

| A32          | Yes    | Yes                   |

| A24          | Yes    | No                    |

| A16          | Yes    | VXIbus registers only |

### 2.1.3. Diagnostic Support

Diagnostic and debugging support for the VX8 is provided through the following features:

- C language source symbolic debugger through front panel JTAG in and out connectors to an XDS510 or a DBC3040

- On board Test Bus Controller for C language source symbolic debugger with WIN95/NT Intel VXIbus slot 0 controllers

## 2.2. Board Layout

Figure 1 VX8 Carrier Board Layout

## 2.3. Front Panel

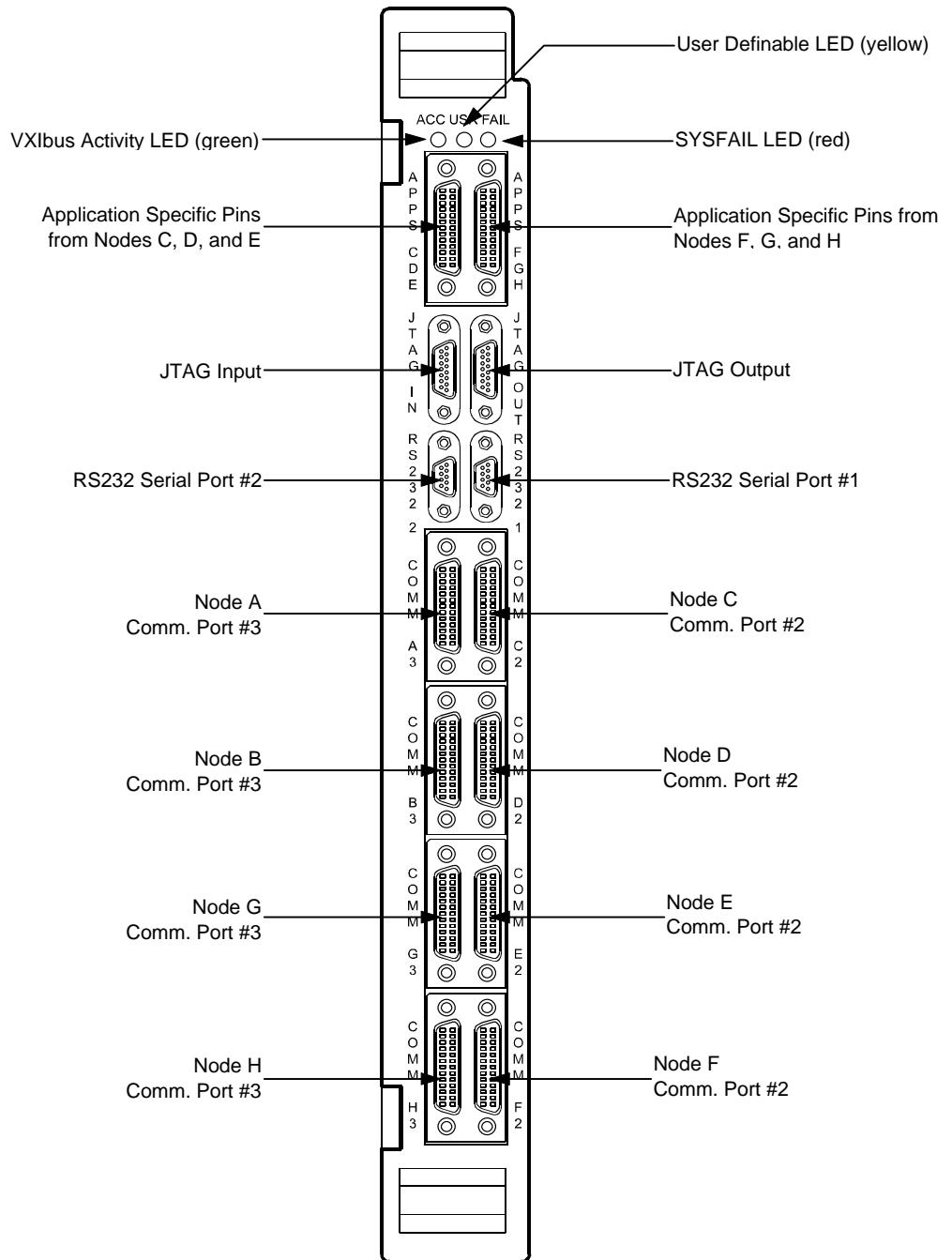

The front panel of the VX8 has a variety of connectors and status LEDs as shown in the following illustration. The pinouts for the connectors and the LEDs are described in the *VX8 Carrier Board Technical Reference Manual*.

**Figure 2 VX8 Front Panel**

### 2.3.1. Status LEDs

| LED  | Color  | Description                                                                                                                                                 |

|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACC  | Green  | VXIbus Activity LED. ON when there is activity between the VXIbus and the VX8 Carrier Board.                                                                |

| USR  | Yellow | User Definable LED. ON when bit 0 (D0) of the LED register is set to "0". This write-only register is located at address 8B00 0000h on the Shared DRAM Bus. |

| FAIL | Red    | VXIbus SYSFAIL LED. The LED is driven when the SCV64 IC drives the VXIbus SYSFAIL line.                                                                     |

### 2.3.2. Connectors

|                            |                                                                                                                         |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------|

| <b>JTAG IN</b>             | Texas Instruments' XDS510 or Spectrum's DBC3040 can be connected to the JTAG IN connector for use with a debug monitor. |

| <b>JTAG OUT</b>            | The JTAG OUT connector allows the VX8 to be part of a multi-module JTAG path.                                           |

| <b>RS232 Serial Ports</b>  | Two RS232 Serial ports are supported by the Node B embedded 'C40 DSP.                                                   |

| <b>Communication Ports</b> | One communication port from each of the Nodes is brought to the front panel via these connectors.                       |

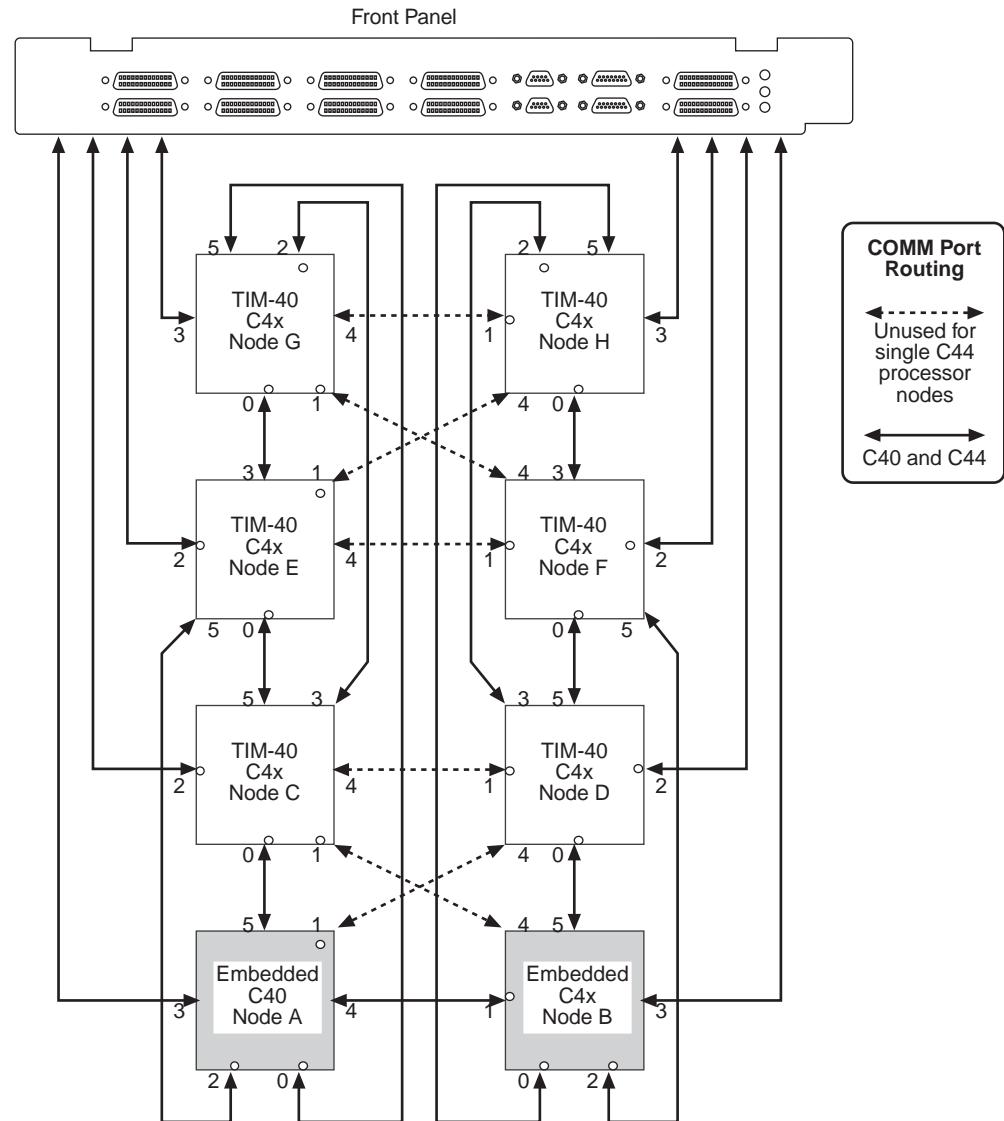

## 2.4. C4x Communication Port Architecture

The C4x Communications ports provide high speed parallel interface communications (~20 Mbytes/sec) to other DSPs and I/O sources. The communication is inherently bi-directional and point to point so there is no latency for access and a single COMM port can be used for half duplex communication between two devices.

The TMS320C40 provides 6 COMM Ports and the TMS320C44 provides 4 COMM Ports. COMM Port routing on the VX8 Carrier Board accounts for fewer COMM Ports on a C44 by ensuring that the front panel connections are valid for Spectrum's C40 and C44 based TIM-40 Modules.

**Figure 3 Communication Port Routing**

Although the C44 does not use COMM ports 0 and 3, Spectrum's C44 based TIM-40 modules route COMM ports 1 and 4 to COMM ports 0 and 3 for compatibility with existing motherboard designs. As a result, COMM Ports 1 and 4 of single C44 based TIM-40 modules are not available. The COMM Port layout shown in *Figure 3* ensures that the front panel COMM ports are valid for all current and planned Spectrum C40 and C44 based TIM-40 Modules.

Refer to the *TMS320C4x User's Guide* for further information on the C4x COMM Ports.

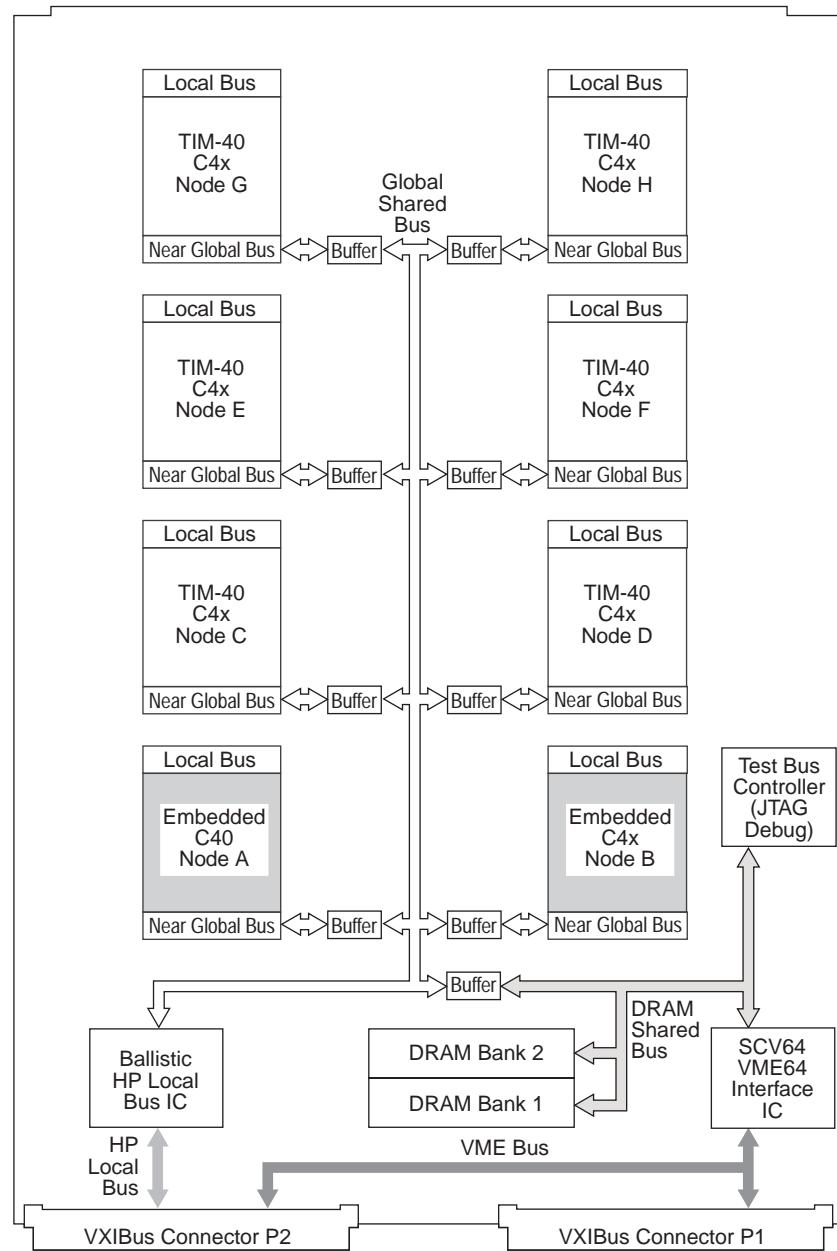

## 2.5. Bus Architecture

Several different communication buses are used on the VX8 Carrier board to connect the C40 processors, TIM-40 sites, memory devices, and interface circuitry. Although the buses are not the only way that devices are interconnected on the VX8, they are the primary means of data transfer between devices.

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Local Bus</b>         | The Local Bus address range is specific to a single C4x DSP, and is therefore not shared with other processors or nodes. It is a private memory bus of a particular C4x.                                                                                                                                                                                                                                                                                                                               |

| <b>Near Global Bus</b>   | The Near Global Bus of the VX8 refers to the Global Bus of each TIM-40 site and the embedded C40 nodes. The SRAM located on these Global Buses is zero wait state from the DSP that owns it, but can be accessed by other DSPs, the HP Local Bus DMA Controller, and the VXIbus Slave Interface via the Global Shared Bus.                                                                                                                                                                             |

| <b>Global Shared Bus</b> | <p>The Global Shared Bus interconnects the:</p> <ul style="list-style-type: none"><li>• Buffered Global Buses of each TIM-40 site via the Global Connectors;</li><li>• Buffered Global Buses of the embedded C40 nodes A and B;</li><li>• DRAM Shared Bus; and</li><li>• HP-Local Bus Interface and registers.</li></ul> <p>32-bit buffers isolate the Global Shared Bus from all these areas except for the HP-Local Bus Interface, which is connected to the bus through a 2 x 1k x 32-bit FIFO.</p> |

| <b>DRAM Shared Bus</b>   | The DRAM Shared Bus enables the VXIbus slave interface to access the DRAM, Test Bus Controller, and the Global Shared Bus. It also allows a C4x DSP to access the DRAM, control / status registers, and the SCV64 as a VXIbus master. Two 72-pin SIMM sites allow expansion of the global shared DRAM using standard PC DRAM memory modules (see Note below).                                                                                                                                          |

---

**Note:** We recommend that DRAM memory be purchased from Spectrum, since this memory has been tested and is guaranteed to be compatible with the VX8 board.

---

**Figure 4 Bus Architecture**

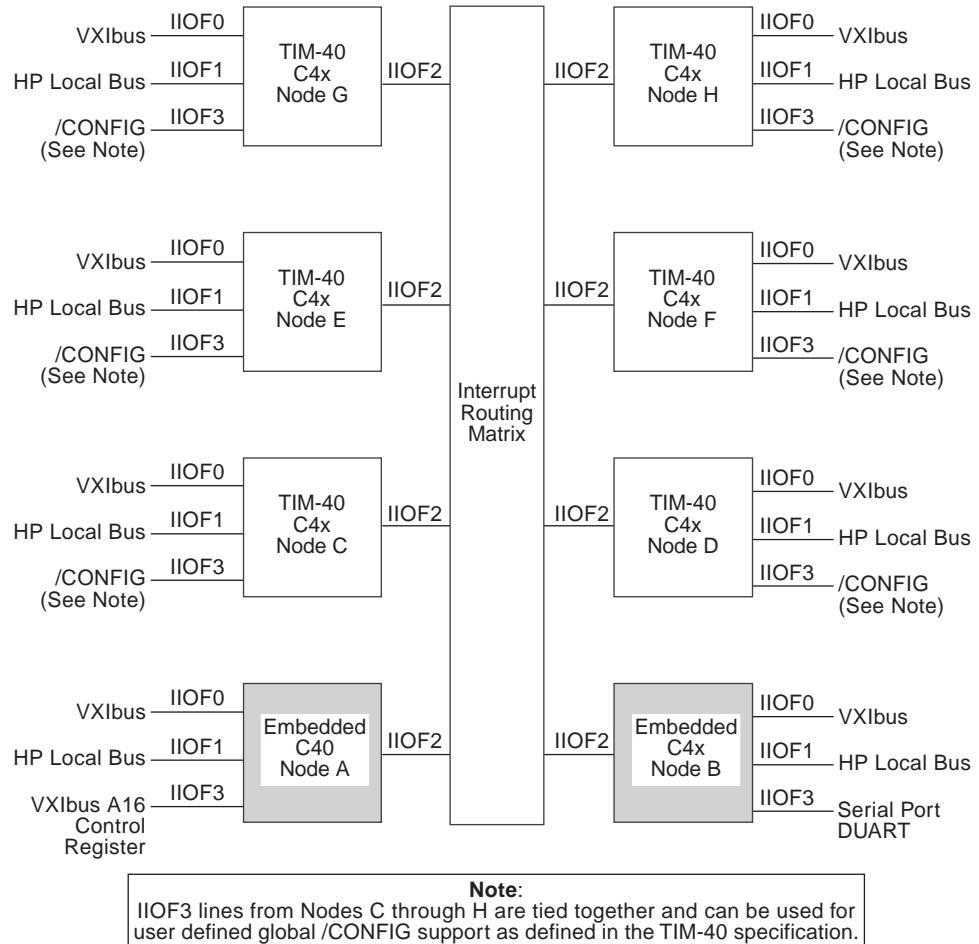

## 2.6. C4x Interrupt Architecture

The four configurable IIOF lines from each 'C4x are used for interrupts

- Between other C4x nodes on the board

- From the SCV64 VXIbus interface chip

- From the HP Local Bus interface

- From the Dual 16550 UART (DUART) (Node B only)

- From the VXIbus A16 Interface (Node A only)

The following figure shows the VX8 interrupt architecture.

**Figure 5 VX8 Interrupt Architecture**

### 2.6.1. VXIbus Interrupts (IIOF0)

Interrupts from the SCV64 VXIbus interface chip are mapped to IIOF0 of all the C4x nodes. This indicates that either a VXIbus interrupt has occurred or that one of the on-board SCV64 interrupt sources has occurred (SCV64 DMA done, for example). Because the interrupt can have several sources, it must be level-triggered so that the source of the interrupt can be identified. VXIbus interrupts can be enabled or disabled based on their interrupt level through registers in the SCV64 VXIbus interface chip. This allows software selectable receipt of interrupts of different priorities. Interrupts must be enabled before they can be generated. The interrupt vector received is latched for reading by the 'C4x' servicing the interrupt through the IACK space in the shared memory map. The 'C4x's interrupt service routine must produce the IACK cycle through the SCV64.

To determine the source and initiate clearing of the interrupt, an interrupt acknowledge (IACK) cycle must be performed. VX8 software functions are available to configure and acknowledge the interrupts for this.

Vectored interrupts can also be generated from any node to the VXIbus using the internal SCV64 register set.

## 2.6.2. HP Local Bus Interrupts (IIOF1)

Three interrupts from the HP Local Bus interface are mapped to IIOF1 of all ‘C4x nodes:

- End of Block (EOB)

- Write FIFO Almost Empty (WAE) sent once per transition of the WAE flag

- Write FIFO Almost Full (WAF)

These interrupts are ORed together onto the IIOF1 line. Use level-triggered interrupts to identify the source of the HP-Bus interrupt. The HINTENABLE, HINTSTAT, and HINTCLR registers on the Global Shared Bus are used to enable, identify, and clear the interrupts. Refer to the *HP Local Bus Interface* section of the *VX8 Carrier Board Technical Reference Manual* for more information on these interrupts.

## 2.6.3. Interrupt Routing Matrix (IIOF2)

The IIOF2 lines from each node can be used as an interrupt or as a general purpose I/O to signal other ‘C4x nodes. This interrupt scheme is under software control, allowing IIOF2 lines to be tied together in any combination through the Interrupt Routing Matrix. The Interrupt Routing Matrix is configured by a register located on node A’s local bus. For further information on the IIOF2 Interrupt Routing Matrix see the *Embedded C40 Node A* section of the *VX8 Carrier Board Technical Reference Manual*.

## 2.6.4. IIOF3 Interrupts

The IIOF3 line is used for three different purposes on the VX8 depending on which node it belongs to.

| Node | Usage                | Description                                                                                                                                                                                                                                       |

|------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A    | VXIbus A16 interrupt | Whenever the host writes to the VXIbus A16 Interface Control Register an interrupt is sent to the IIOF3 line of the Node A C40. For further information on the VXIbus A16 interface see the <i>VX8 Carrier Board Technical Reference Manual</i> . |

| Node   | Usage           | Description                                                                                                                                                                                                                                                                                                                  |

|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B      | DUART interrupt | Node B uses IIOF3 as the interrupt from the serial port DUART. The interrupt lines from Channel 0 and Channel 1 UARTs are ORed together and routed to Node B's IIOF3. For further information on the DUART interrupt see the <i>Embedded C40 Node B</i> section of the <i>VX8 Carrier Board Technical Reference Manual</i> . |

| C to H | TIM-40 /CONFIG  | The IIOF3 lines from the TIM-40 modules (nodes C through H) are not brought off the carrier board. The lines are tied together on the VX8 board, allowing them to be used for the /CONFIG line.                                                                                                                              |

## 2.7. JTAG Debugging

A JTAG IN connector is provided on the front panel of the board for connection to an XDS510 from Texas Instruments or a DBC3040 from Spectrum. This allows use of the Texas Instruments' standard TMS320C4x debug monitor or third party debug monitors such as GO DSP's Code Maestro from an external PC or SUN workstation.

A JTAG OUT connector allows the VX8 to be part of a multi-module JTAG path. The open collector /CONFIG and /GRESET signals are bussed between boards via the JTAG connectors. The JTAG cable allows multi-board resetting (required if the front panel COMM ports are connected between boards) and /CONFIG to be bussed between devices.

---

**Note:** Because of the directional reset state of C4x COMM ports, all VX8s connected together via COMM port MUST be connected by their front panel JTAG connectors. The front panel JTAG connectors will reset JTAG connected VX8s together, thereby damage to COMM ports on reset will be avoided.

---

Each of the C4x processors has a JTAG interface for debugging purposes. The JTAG chain is controlled by the JTAG PAL, which routes the data lines to each available C40 node in turn. If a TIM site is not occupied then the JTAG chain bypasses that node. The full JTAG sequence is JTAG IN, Node A, C, E, G, B, D, F, H, JTAG OUT. For multiple processor TIM-40 modules, refer to the TIM-40 module documentation for information on the order in which the processors are connected in the JTAG scan path. When an external debugger is connected to the JTAG IN connector of a board, the on-board TBC is disabled.

For further details on the JTAG interface, refer to *the VX8 Carrier Board Technical Reference Manual*.

## 2.7.1. JTAG Connection

The JTAG cable from your external debugger should be connected only to the JTAG IN of board 1. For multiple boards, connect the JTAG OUT of board 1 to the JTAG IN of board 2, etc..

---

**Note:** Ensure that your hardware is powered down before connecting the JTAG cable and setting up the JTAG chain.

---

## 2.7.2. JTAG Software Setup

The following describes the software setup required when using Texas Instruments' standard TMS320C4x debug monitor. If you're using a third party debug monitor, refer to that product's documentation for specific software setup instructions.

A configuration file (**board.cfg**) is required to tell the debugger how many C4x processors there are in a JTAG scan chain on your target system and their order in the chain. A sample **board.cfg** has been provided on the *VX8 C4x Support Software* disk and can be found in the *examples\debug* directory. This sample **board.cfg** file includes a setup for three VX8 boards and defines which processors are present in the JTAG scan chain. Sites which are populated are uncommented. In this example, only nodes A and B of board 1 are populated; other processors are commented out.

```

; "CPU_H3"      TI320C4X          ; Module in site H

; "CPU_F3"      TI320C4X          ; Module in site F

; "CPU_D3"      TI320C4X          ; Module in site D

; "CPU_B3"      TI320C4X          ; Module in site B

; "CPU_G3"      TI320C4X          ; Module in site G

; "CPU_E3"      TI320C4X          ; Module in site E

; "CPU_C3"      TI320C4X          ; Module in site C

; "CPU_A3"      TI320C4X          ; Module in site A

; "CPU_H2"      TI320C4X          ; Module in site H

; "CPU_F2"      TI320C4X          ; Module in site F

; "CPU_D2"      TI320C4X          ; Module in site D

; "CPU_B2"      TI320C4X          ; Module in site B

; "CPU_G2"      TI320C4X          ; Module in site G

; "CPU_E2"      TI320C4X          ; Module in site E

; "CPU_C2"      TI320C4X          ; Module in site C

; "CPU_A2"      TI320C4X          ; Module in site A

; "CPU_H1"      TI320C4X          ; Module in site H

; "CPU_F1"      TI320C4X          ; Module in site F

```

|            |          |                    |

|------------|----------|--------------------|

| ; "CPU_D1" | TI320C4X | ; Module in site D |

| "CPU_B1"   | TI320C4X | ; Module in site B |

| ; "CPU_G1" | TI320C4X | ; Module in site G |

| ; "CPU_E1" | TI320C4X | ; Module in site E |

| ; "CPU_C1" | TI320C4X | ; Module in site C |

| "CPU_A1"   | TI320C4X | ; Module in site A |

The JTAG cable from your external debugger should be connected only to the JTAG IN of board 1. For multiple boards, uncomment the appropriate sites and connect the JTAG OUT of board 1 to the JTAG IN of board 2, etc..

---

**Note:** Processors listed in the **board.cfg** file are listed in reverse order than they actually occur in the JTAG chain. The last board listed in the **board.cfg** file should be the first board in the JTAG chain.

---

If you edit the **board.cfg** file, you'll have to run **composer.exe** with the file in order for your changes to take effect.

A memory descriptor file (**emuinit.cmd**) is also required to tell the debugger which areas of memory it can and cannot access. A sample **emuinit.cmd** file has been provided on the *VX8 C4x Support Software* disk and can be found in the *examples\debug* directory. Using a text editor, edit this file to properly reflect the *VX8's* memory mapping (refer to the *VX8 Carrier Board Technical Reference Manual* for details). If you're setting bus control registers in the **emuinit.cmd** file, refer to the *VX8 Carrier Board Technical Reference Manual* and the TIM module documentation for the correct values to calculate.

---

**Note:** If you're loading your application via JTAG, the Global Memory Control Register (GMCR) and Local Memory Control Register (LMCR) have to be set in the **emuinit.cmd** file in order for your program to load, and for the processors to access their memory correctly. You'll need a separate **emuinit.cmd** file for each type of TIM module. Refer to the documentation provided with your TIM modules for the correct GMCR and LMCR values.

---

Refer to the *TMS320C4x C Source Debugger User's Guide* for further details and if you're using Spectrum's DBC3040, also refer to the *XDSC40 Board MS-DOS User Guide*.

---

**Note:** If using Spectrum's DBC3040, do **not** try to integrate C4x programs with MS-DOS applications and do **not** use the debugger to write C4x programs (use the information provided in this manual instead) as described in the *XDSC40 Board MS-DOS User Guide*.

---

### 2.7.3. Debugging tips

When debugging, keep in mind that memory windows to lockable regions (Near Global SRAMs, HP registers, SCV registers, etc.) may not refresh correctly or be visible if other entities (other DSPs, SCV64, or BALLISTIC chip) are using global resources as well.

For information on accessing shared resources while debugging, see *section 6.5.5*.

---

# 3 Software Overview

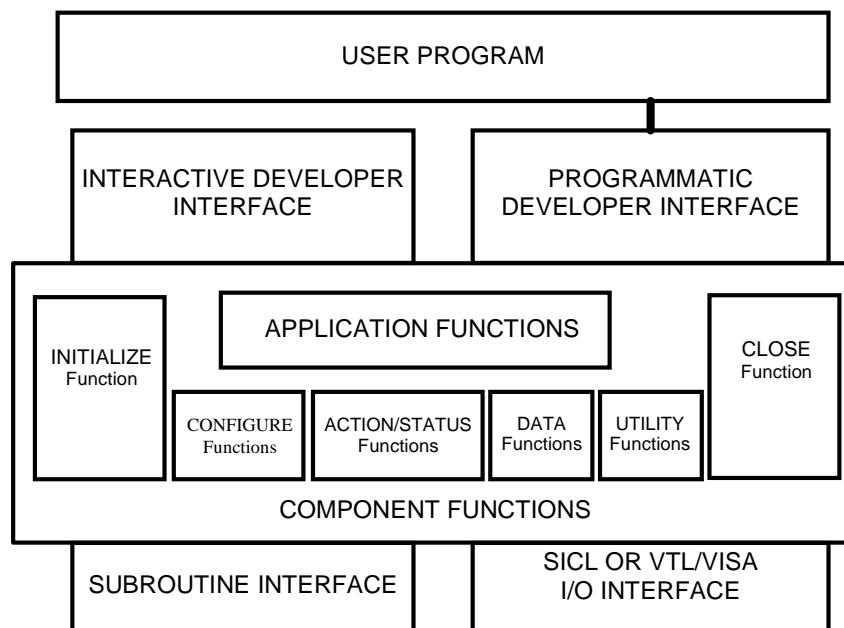

The VX8 Support Software product provides hardware initialization, hardware control, host communications, DSP library functions, and examples. The VX8 Support Software primarily consists of two libraries: the C4x DSP Library (VX8 C4x Support Software Library) and the Host Library (the VX8 Instrument Driver).

**The C4x Support Software Library** contains TMS320C4x functions which perform common tasks (initialization and control) and data transfers required by all C4x processors on the VX8 Carrier Board.

**The VX8 Instrument Driver** provides a host API for performing configuration, control, and communications with a VX8 system. The primary functions of the VX8 Instrument Driver are to initialize and communicate with a VX8 system.

The VX8 board does not ship with resident application software. The VX8 requires C40 and host software development, using the VX8 Support Software, in order to integrate a VX8 DSP subsystem into a total VXIbus solution. The VX8's overall functionality depends on its hardware configuration and the host and C4x application software through which the VX8 will be able to process data and communicate with other devices.

---

**Note:** The VX8 Carrier Board is not a typical VXIbus Instrument due to its configurable nature. The functionality and behavior of a VX8 is completely defined by its application software and its hardware configuration. The VX8 devices must be loaded with a DSP application before they become functional instruments.

---

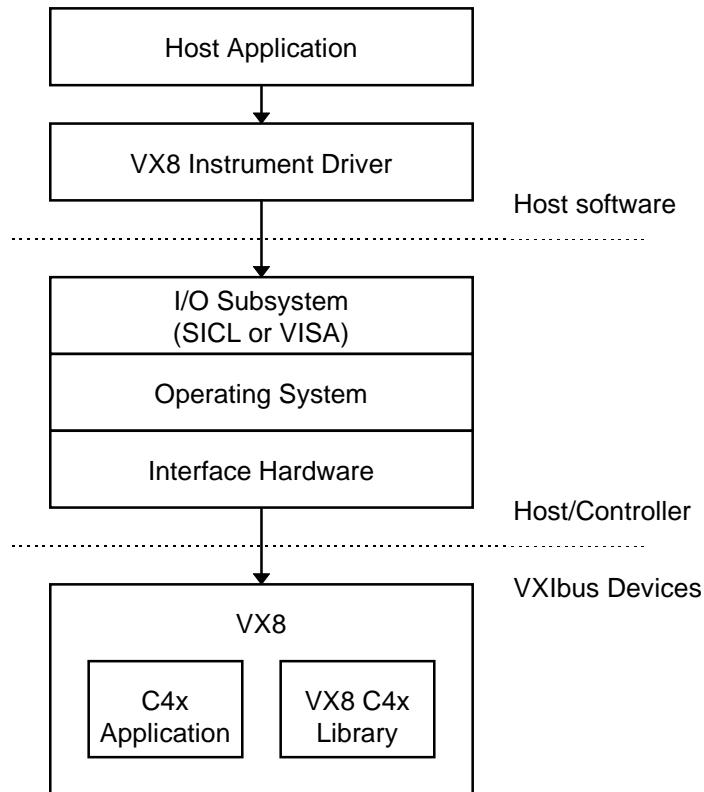

## 3.1. Software Environment

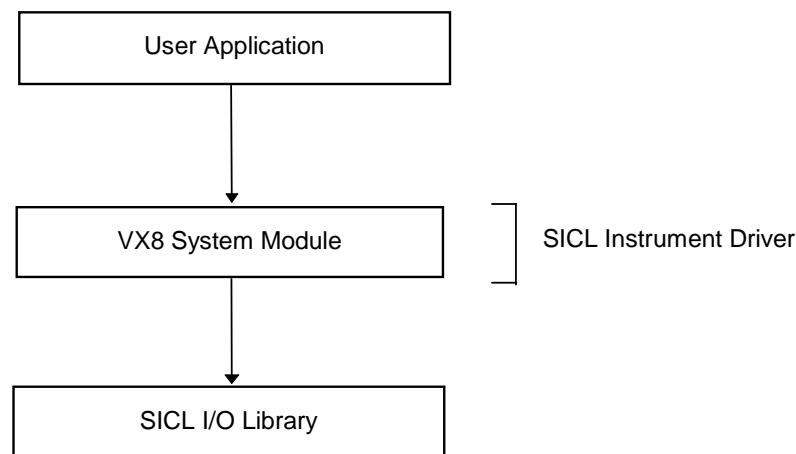

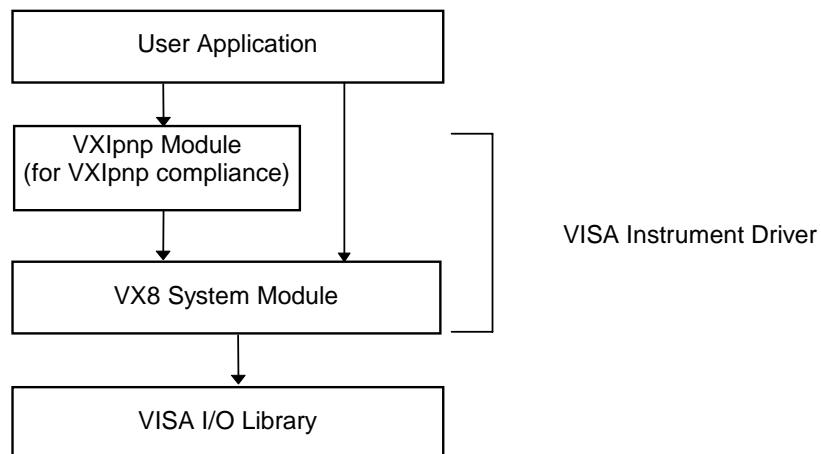

Creating a VX8 application can be broken up into two interrelated tasks: Host software development and DSP software development. The VX8 Support Software product gives you both host and DSP routines to help you develop your application in less time without the need of having detailed knowledge about the inner workings of the VX8. *Figure 6* shows a high level view of the various components in the VX8 Software environment.

**Figure 6 VX8 Software Environment**

### 3.1.1. Host Software Environment

There are many VXIbus host controllers and software configurations available from manufacturers. Fortunately, developing VXIbus host applications on these development platforms is greatly simplified by the standard I/O library present in most VXIbus systems.

The I/O library provides host software with an API (Application Program Interface) to routines for VXIbus communications and control. The I/O library provides numerous functions ranging from low level I/O to higher level interactions like message based communication. The I/O library simplifies host software development by isolating the host software from the underlying host operating system (OS) and interface hardware. Together, the VX8 specific functions contained in the VX8 Instrument Driver and the I/O library provide application developers with a standard, easy to use software interface for developing the host based component of your VX8 application.

The I/O libraries supported by the VX8 Instrument Driver are the VXIpnP Alliance defined **VISA** (Virtual Instrument Software Architecture) and **SICL** (Hewlett-Packard Standard Instrument Control Library).

SICL is available from Hewlett-Packard for many of its VXIbus products. VISA is an open software standard defined by the VXIpnP Systems Alliance. VISA is available on

a variety of VXIbus products from Hewlett-Packard and National Instruments, among others.

The VXIpnnp components of the VX8 Instrument Driver (the VXIpnnp module) **do not** apply to systems using the SICL I/O subsystem.

### 3.1.2. DSP Software Environment

The development environment for the TMS320C4x DSP software is relatively straight forward. You can develop C4x DSP application code for the VX8 on any platform which supports Texas Instruments' TMS320C4x tools.

Currently, you may use DOS, WIN95, WIN NT, or Sun / HP-UX based environments to author and compile DSP software. TI Tools version 5.0 is required under Windows NT.

JTAG based debugging can only be performed on platforms which have C4x JTAG support (DOS, WIN95, WIN NT, SunOS/Solaris). JTAG based debugging is currently **unavailable** for HP-UX based computers.

In addition to the C4x tools available from TI, there are a number of tools available from third party vendors which can help in your application development and debugging.

The VX8 C4x Support Software Library provides VX8 DSP applications with a simple API for initialization, configuration, control, and I/O routines tailored for the VX8 hardware. These routines reduce the amount of in depth information VX8 developers require to generate their applications.

Using the VX8 C4x Support Software Library is a simple chore. To gain access to the calls in the library, simply include the required include files and link in the library as you would with any other static library when you build your DSP software. Specific information about the VX8C4xSS will be detailed in later chapters.

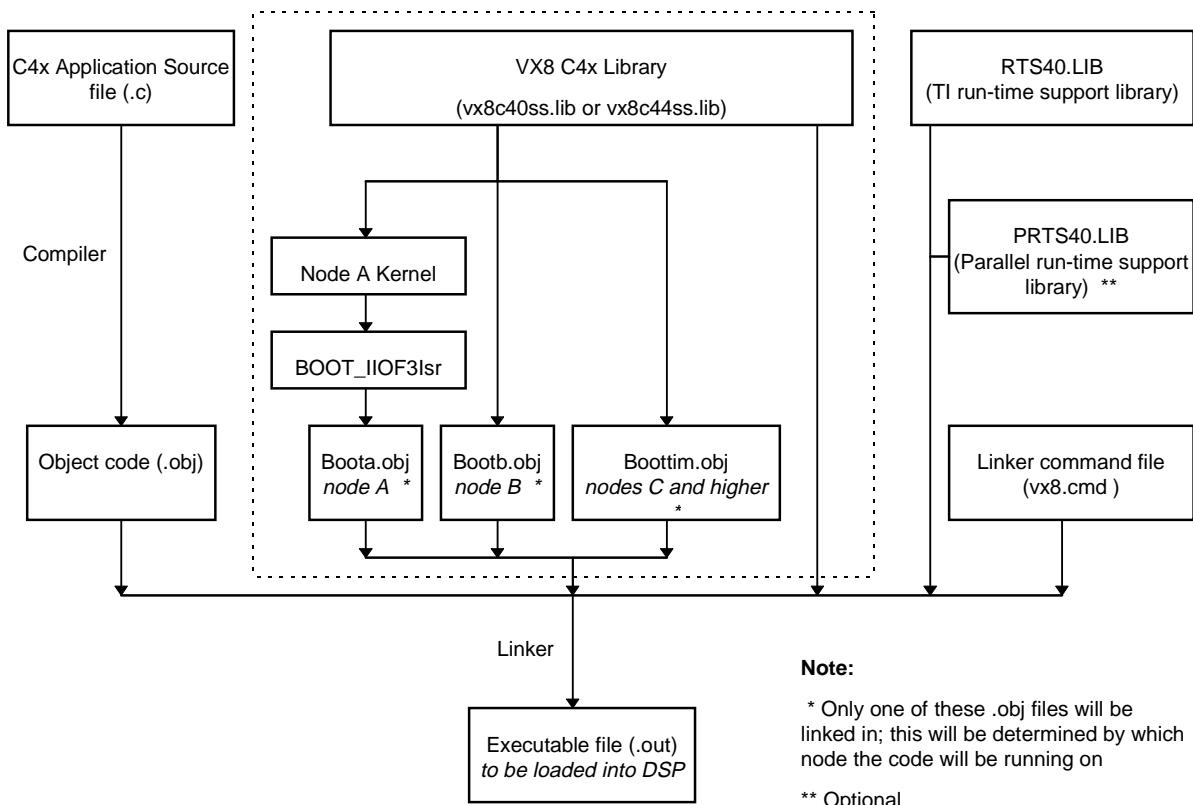

## 3.2. VX8 Support Software

The VX8 Support Software provides host and DSP initialization, communications, and control functions for the VX8 Carrier Board. The VX8 Support Software consists of several major components:

- SICL/VISA Instrument Driver

- VX8 C4x Support Software Library

- Example programs

### 3.2.1. SICL/VISA VX8 Instrument Driver

The VX8 Instrument Driver provides a host API for your application to initialize, control, and communicate with a VX8 system. The device driver consists of ANSI-C host code which will function with either VISA or SICL I/O libraries.

Source code is provided for the VX8 Instrument Driver.

### 3.2.2. VX8 C4x Support Software Library

The VX8 C4x Support Software Library provides your DSP application with routines to configure and communicate with the various VX8 interfaces.

The C4x library can be separated into the following components:

- **Global Bus Interface Module** supporting accesses from a DSP to the global shared or DRAM shared buses

- **VXIbus Interface Module** supporting direct mastering of the VXIbus from a DSP, SCV64 DMA initialization, and VXIbus interrupt support

- **HP Local Bus Interface Module** supporting setup, initialization, and data transfer for the HP Local Bus Interface

- **DUART Module** providing initialization, data transfer and interrupt support for the dual UART on Node B's Local Bus

- **Node A Initialization Kernel Module** supporting VXIbus A16 register access from the host and VX8 initialization after a board reset. The Node A C40 DSP must service any requests made by the host through the A16 configuration registers. Users must link the supplied interrupt service routine for IIOF3 in with their Node A DSP application code and enable this interrupt. This is taken care of by the **boota.asm** boot initialization routine

Source code is provided for the C4x Support Software Library.

### 3.2.3. Example Programs

The VX8 Support Software provides several example programs which demonstrate how to use the various interfaces on the VX8 as well as how to combine host and DSP software to form an application. Some of the examples require additional hardware to run. Please refer to the example program notes in the *Chapter 11* of this manual for system requirements.

The following table lists the symbolic constants used in the example programs.

**Table 1 Symbolic Constants Used in the Example Programs**

| Constant                                                                                  | Example program                   | Description and/or Value                                                                                                                |

|-------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| _FROM_DRAM                                                                                | vx8mult.c,<br>vx8mult.h           | 0                                                                                                                                       |

| ADDR_INC                                                                                  | vx8mult.c,<br>vx8mult.h           | Address increment; is 4 or 1 depending on whether the target is byte or long word addressed. It will be 1 for C4x, 4 for VXIbus devices |

| blockSize                                                                                 | vx8hpgen.c                        | 0x10                                                                                                                                    |

| BOARD2_BASE_ADDR                                                                          | vx8vxi.c                          | 0x28000000                                                                                                                              |

| CH1                                                                                       | vx8duart.c                        | channel number; 1                                                                                                                       |

| CH2                                                                                       | vx8duart.c                        | channel number; 2                                                                                                                       |

| DEST                                                                                      | vx8vxi.c                          | BOARD2_BASE_ADDR + VX8_A32_SLV_DRAM_OFFSET                                                                                              |

| HP_CONSUME_ISR                                                                            | vx8hpcon.c                        | rename the ISR; c_int04                                                                                                                 |

| LENGTH                                                                                    | vx8duart.c                        | ramp length; 10                                                                                                                         |

| LENGTH                                                                                    | vx8vxi.c                          | 0x1000                                                                                                                                  |

| MULT_CTRL_REG,<br>MULT1_REG,<br>MULT2_REG,<br>MULT_RESULT_REG                             | vx8mult.c,<br>vx8mult.h           | mult example registers                                                                                                                  |

| MULT_LDF_FILE                                                                             | mult.c                            | "mult.ldf"                                                                                                                              |

| MULT_REG_OFFSET                                                                           | vx8mult.c,<br>vx8mult.h           | offset into the DRAM space to have registers                                                                                            |

| MULT_SDF_FILE                                                                             | mult.c                            | "mult.sdf"                                                                                                                              |

| SCV_ISR                                                                                   | vx8lm.c,<br>VX8DMA.C,<br>vx8vxi.c | rename the ISR; c_int03                                                                                                                 |

| UART_ISR                                                                                  | Vx8duart.c                        | rename the ISR; c_int06                                                                                                                 |

| VX8_A32_SLV_DRAM_OFFSET                                                                   | vx8vxi.c                          | 0x04000000                                                                                                                              |

| VX8_BOARD240                                                                              | mult.c                            | "vxi,240" or "VXI0::240::INSTR"                                                                                                         |

| VX8_MULT_UNINIT,<br>VX8_MULT_LOADED,<br>VX8_MULT_START,<br>VX8_MULT_DONE,<br>VX8_MULT_END | vx8mult.c,<br>vx8mult.h           | MULT control register defined values                                                                                                    |

### 3.3. Data Types

Data types used in VX8 host and DSP code are defined in these header files:

- ssvx8typ.h defines data types used in VX8 host code

- type\_c3x.h defines data types used in VX8 DSP code

The following base type modifiers are used:

|   |          |

|---|----------|

| U | unsigned |

| R | register |

| P | pointer  |

| V | volatile |

Note that “volatile” generally applies to everything dereferenced from the base type. For example, PVPVUINT16 == PVPUINT16.

**Table 2 Data Types**

| Data type             | Description                                                 |

|-----------------------|-------------------------------------------------------------|

| STATUS                | unsigned long; error code return value for functions        |

| PVOID                 | pointer to void                                             |

| <b>Device handles</b> |                                                             |

| VXIDEV_HANDLE         | typedef ViSession (see VISA documentation)                  |

| PVXIDEV_HANDLE        | typedef ViPSession (see VISA documentation)                 |

| <b>INT8 types</b>     |                                                             |

| INT8                  | char                                                        |

| PINT8                 | pointer to a char                                           |

| VINT8                 | volatile char                                               |

| PVINT8                | pointer to a volatile char                                  |

| VPINT8                | volatile pointer to a (volatile) char                       |

| PVPINT8               | pointer to a volatile pointer to a char                     |

| <b>UINT8 types</b>    |                                                             |

| UINT8                 | unsigned char                                               |

| VUINT8                | volatile unsigned char                                      |

| PUINT8                | pointer to an unsigned char                                 |

| PVUINT8               | pointer to a volatile unsigned char                         |

| VPUINT8               | volatile pointer to a (volatile) unsigned char              |

| PVPUINT8              | pointer to a volatile pointer to a (volatile) unsigned char |

| <b>INT16 types</b>    |                                                             |

| INT16                 | short                                                       |

| VINT16                | volatile short                                              |

| PINT16                | pointer to a short                                          |

| PVINT16               | pointer to a volatile short                                 |

| VPINT16               | volatile pointer to a (volatile) short                      |

| PVPINT16              | pointer to a volatile pointer to a short                    |

| <b>UINT16 types</b>   |                                                             |

| UINT16                | unsigned short                                              |

| VUINT16               | volatile unsigned short                                     |

| PUINT16               | pointer to an unsigned short                                |

| PVUINT16              | pointer to a volatile unsigned short                        |

| VPUINT16              | volatile pointer to a (volatile) unsigned short             |

| PVPUINT16             | pointer to a volatile pointer to (volatile) unsigned short  |

| <b>INT32 types</b>    |                                                             |

| INT32                 | long                                                        |

| VINT32                | volatile long                                               |

| <b>Data type</b>                                                   | <b>Description</b>                                        |

|--------------------------------------------------------------------|-----------------------------------------------------------|

| INT32                                                              | pointer to a long                                         |

| PVINT32                                                            | pointer to a volatile long                                |

| VPINT32                                                            | volatile pointer to a (volatile) long                     |

| PVPINT32                                                           | pointer to a volatile pointer to a long                   |

| <b>UINT32 types</b>                                                |                                                           |

| UINT32                                                             | unsigned long                                             |

| VUINT32                                                            | volatile unsigned long                                    |

| PUINT32                                                            | pointer to an unsigned long                               |

| PVUINT32                                                           | pointer to a volatile unsigned long                       |

| VPUINT32                                                           | volatile pointer to a (volatile) unsigned long            |

| PVPUINT32                                                          | pointer to a volatile pointer to (volatile) unsigned long |

| <b>floating point (32-bit) types</b>                               |                                                           |

| FLOAT32                                                            | float                                                     |

| VFLOAT32                                                           | volatile float                                            |

| PFLOAT32                                                           | pointer to an float                                       |

| PVFLOAT32                                                          | pointer to a volatile float                               |

| VPFLOAT32                                                          | volatile pointer to a (volatile) float                    |

| PVPFLOAT32                                                         | pointer to a volatile pointer to a (volatile) float       |

| <b>floating point (64-bit) types</b> <b>(defined in ssvisa.h )</b> |                                                           |

| FLOAT64                                                            | float                                                     |

| PFLOAT64                                                           | pointer to an float                                       |

| VFLOAT64                                                           | volatile float                                            |

| PVFLOAT64                                                          | pointer to a volatile float                               |

| <b>string types</b>                                                |                                                           |

| STRING                                                             | char                                                      |

| STRING256[MAX_STR_LEN]                                             | string of 256 characters                                  |

| <b>Boolean types</b>                                               |                                                           |

| BOOLEAN                                                            | unsigned long                                             |

### 3.4. Hardware and Software Requirements

VX8 application developers should be familiar with VISA and/or SICL software development. A knowledge of ANSI C software development on VME/VXIbus systems, and TMS320C4x software development in ANSI C/assembly is vital.

VX8 Support Software for HP-UX 9.X/SICL was developed on an HP V743 Embedded controller with HP-UX 9.05 and SICL C.03.09. This version of VX8 Support Software is to be used with the following hardware and software configurations:

| Hardware                                                                                                                                                                                                                                                                                                                                                              | Software                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul style="list-style-type: none"> <li>• VXIbus mainframe chassis with a minimum of 2 slots (for slot 0 controller and a single VX8 card)</li> <li>• VXIbus slot 0 controller (HP V743 VXIbus Embedded Controller for example)</li> <li>• VX8 Carrier Board</li> <li>• DOS/WIN 95 PC and an external JTAG interface for TMS320C4x DSP software development</li> </ul> | <ul style="list-style-type: none"> <li>• ANSI-C compiler</li> <li>• DOS based TI TMS320C4x development tools</li> <li>• SICL C.03.09</li> <li>• HP-UX 9.05</li> </ul> |

The VX8 VISA Windows 95 and Windows NT Instrument driver was developed under Windows NT version 4.0 using Microsoft Visual C compiler version 5.0 with a National Instruments VXI-MXI2 extender. It supports the following hardware and software configurations:

| Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                            | Software                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul style="list-style-type: none"> <li>• VXIbus mainframe chassis with a minimum of 2 slots (for slot 0 controller and a single VX8 card)</li> <li>• VX8 Carrier Board</li> <li>• DOS or Windows 95 PC with an external JTAG interface for TMS320C4x DSP software development. This can be the same PC as the host if running Windows 95. TI Tools version 5.0 and Go DSP Code Composer are required for 'C4x development on Windows NT.</li> </ul> | <ul style="list-style-type: none"> <li>• Microsoft Visual C compiler version 5.0</li> <li>• TI TMS320C4x development tools (version 5.0 required for Windows NT)</li> <li>• VISA (version 1.1 or later)</li> <li>• Windows 95 or Windows NT</li> </ul> |

# 4 Reset Conditions and Initialization

## 4.1. Reset

The VX8 board can be reset from a number of sources, all of which will generate either a hard or soft reset condition.

### 4.1.1. Hard Reset

A hard reset signifies the resetting of the entire system. This includes the Slot 0 controller, other VXIbus devices, and all VX8 boards. This condition resets all devices on the VX8 board, and the VXIbus Resource Manager configures the VX8 board via the A16 space. These writes to A16 cause the Node A IIOF3 ISR to be triggered. Sources of hard resets include:

- **Power On Reset (PORST)** - Entire VXIbus chassis is initialized after power is applied.

- **SYSRST** - The SYSRST\* line on the VXIbus backplane is pulled low by another VXIbus device. SYSRST\* is functionally equivalent to a PORST without the disruption of power from the backplane.

### 4.1.2. Soft Reset

A soft reset signifies the resetting of only VX8s in a system. This can be a single VX8 board or a number of VX8 boards connected by their front panel JTAG connectors. Since the state of the Slot 0 controller is not affected by this action, the Resource Manager will not re-configure nor re-initialize the devices via their A16 configuration registers. Therefore the previous A16 configuration information is still valid (offset value and A32 enable state). To retain this previous state across soft resets, the relevant A16 registers are not reset by a soft reset condition, however the READY and PASSED bits in the A16 Status Register are cleared. Sources of soft reset include:

- **VXIbus A16 Control Register Reset** - If the RESET bit in the A16 VXIbus control register is asserted, the VX8 board will generate a local reset to the entire board with the exception of the A16 Register Set. It will also cause the /GRESET line on the front panel JTAG connector to be asserted to ensure that other C4x DSPs in the system are not driving their COMM Ports in the wrong direction after a DSP is reset.

- **Front Panel JTAG** - If the /GRESET line on the front panel JTAG connector is asserted, the VX8 board will generate a local reset to the board.

---

**Note:** The SYSFAIL LED will light if a board is reset by its A16 control register. Boards reset via front panel JTAG will not light their SYSFAIL LEDs.

## 4.2. Boot Kernel Initialization

The Node A Embedded C40 Boot Kernel is responsible for initializing the VX8 on power-up and interacts with several instrument driver functions. The initialization must be performed by Node A since it is the only DSP on the VX8 with access to the VXIbus defined A16 registers.

The A16 Interrupt Service Routine (ISR) portion of the Node A boot kernel must remain resident on Node A to perform actions triggered by writes to the A16 VXIbus registers by the host. This is accomplished by linking in the ISR for IIOF3 on Node A with your DSP application code for Node A.

The following table illustrates the sequence of events that takes place after a reset:

**Table 3 Boot Kernel Initialization**

| Host                                                                                                                                                                                                                 | Node A DSP                                                                                                                                                                                                                                         | Other DSPs                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Asserts, then releases /RESET                                                                                                                                                                                        | Boots kernel code from the Boot Kernel PEROM and runs board self test                                                                                                                                                                              | Configured to boot from COMM Port, so they are waiting for instruction                                                                                                |

| Writes to A16 Configuration Registers to setup A32 offset and sets A32 Enable bit                                                                                                                                    | Receives an interrupt on IIOF3, reads the A16 Configuration Registers, initializes SCV64, and enables A32 slave image                                                                                                                              | Still waiting                                                                                                                                                         |

| Optional: Sets the bottom two 32-bit words in Node A Near Global to "uninitialized" values. Writes to A16 Control Register requesting Firmware Revision and Self Test Status                                         | Receives an interrupt on IIOF3, reads the A16 Configuration Registers, writes self test results to address 0x8000 0001, writes firmware revision to address 0x8000 0000, writes firmware revision and self test status bits to A16 Status Register | Still waiting                                                                                                                                                         |

| Optional: Polls on Firmware and Self Test locations in Node A Near Global for the values to change from the "uninitialized" value then clears the Firmware Rev and Self Test Query bits in the A16 Control Register. | No Action                                                                                                                                                                                                                                          | Still waiting                                                                                                                                                         |

| Host starts code download by loading the intermediate boot kernel to all DSPs through Node A.                                                                                                                        | Node A receives command and downloads intermediate boot kernel to other nodes via COMM Port.                                                                                                                                                       | Receives Intermediate Boot Kernel from Node A via COMM Port. Not all DSPs are physically connected to Node A via COMM port, so this download may take several 'hops'. |