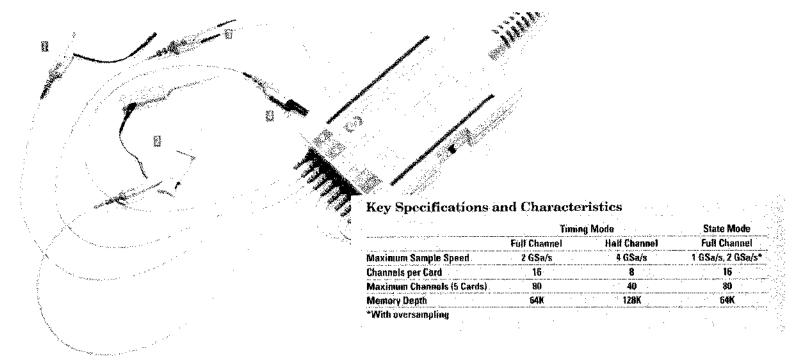

# 4-GSa/s Timing and 1-GSa/s Synchronous State for the HP 16500A/B Logic Analysis System

The HP 16517/18A — Ultra High Speed Timing and State Analysis at an Affordable Price Trace more channels with higher accuracy than ever before in a logic analyzer. Solve your toughest problems with the fastest, most flexible state analysis available.

# **Timing Analysis**

# • 4-GSa/s Conventional Timing Analysis

Verify the timing of critical edges with 250 ps resolution, across up to 40 channels, or 500 ps resolution, across up to 80 channels.

# **Synchronous State Analysis**

# • 1-GSa/s Synchronous State Analysis

View high speed data streams at full speed on up to 80 channels.

# • 200-ps Variable Sample Point

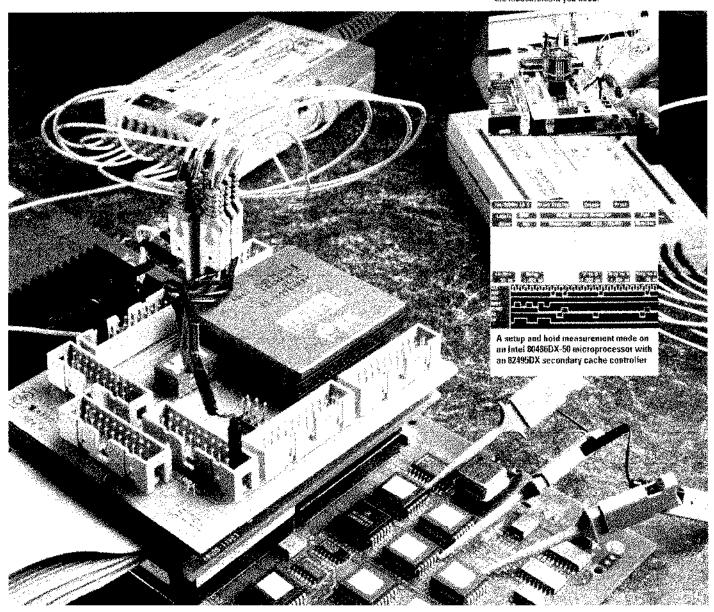

Vary the sample point with respect to the external clock edge in 200-ps increments over a ±5 ns range. *Precisely* characterize setup or hold times, across up to 80 channels.

# Oversampled External Clock

Take state traces with the resolution of a timing trace. The oversampled mode allows more than one sample per clock edge, up to a sample rate of 2 GSa/s. This mode provides the functional equivalent of Dual-Analysis-Per-Pin (DAPP).

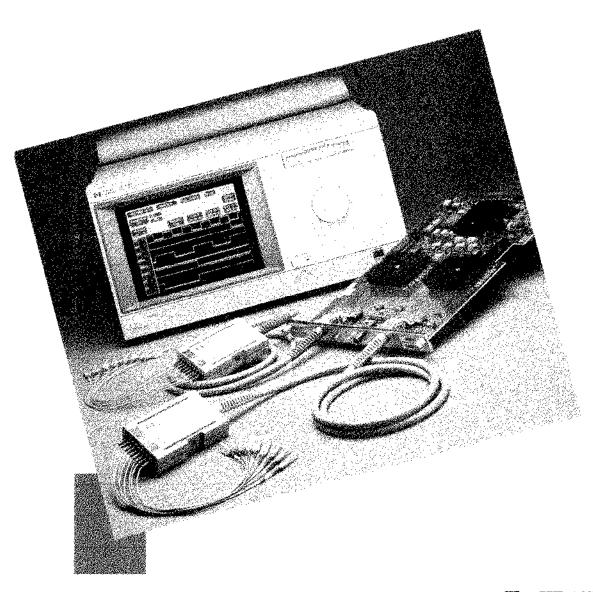

Flexible probe options allow you to get the measurement you need.

# **Memory Depth**

#### • 64K Samples in Full Channel Mode

Full channel mode is available in timing and synchronous state mode.

#### 128K Samples in Half Channel Mode

Half-channel mode is available in the timing mode only. With this memory depth, traces taken at 4 GSa/s are 32.8 µs long.

### Advanced Triggering Features

- Trigger Macro Library

Both basic and complex macros

are available. Macros can be

combined to create custom

trigger conditions

- Easy Trigger Setup

A menu with graphics of the measurement and sentence-like structure make triggering easy.

- True, 500-MHz, 4-level

Trigger Sequencer

Trigger on complex events with durations as short as 2 ns.

- 4 Pattern Terms

Trigger on events occurring across groups of channels up to the full width of the analyzer. The trigger terms and their logical combinations let you identify when to branch and when to trigger.

### • 2 Edge Terms

In timing mode, use the edge terms to trigger on an asynchronous rising edge, falling edge, or either edge.

Timer/ Occurance Counter

For each sequence level, trigger

when events occur too soon, or

when a time-out occurs in a

data stream.

## Time-Correlated Measurements Add to the Power of the HP 16517/18A

- Creating a 160-Channel

System Using the HP 16501A

Use the intermodule bus to

combine two 80 channel

HP 16517/18A systems with

2 ns accuracy. Double probe a

data line to achieve greater

accuracy between the two

systems. Display traces from

both systems on one screen

- Establishing Context Using the HP 16550A

Use 102 or 204 channels at 4-ns resolution to establish the context of the measurement. Then trigger up to 40 channels at 250-ps resolution on the HP 16517/18A.

# Display Options Help You Identify Interesting System Activity Quickly

In addition to the traditional state listing and timing waveform display modes, the HP 16517/18A provides the following:

State Waveforms

View large portions of the state acquisition at a glance.

- State Compare

Find differences between acquisitions automatically.

- Timing Listing

Observe bus values or other

timing activity in listing format

with time tags.

# The Ultimate in Timing Resolution and Accuracy

The 250-ps resolution of this analyzer is only part of the story. An innovative approach, using phase-locked loops, keeps the skew between channels to ±250ps. This accuracy is maintained across all pods and expansion boards, for a total of up to 80 channels.

## Characterize Your High-Speed ASIC or Target System

Now, you can speed up the process of making setup and hold time measurements by taking advantage of the high channel count of a logic analyzer. This can be done in one of two ways. First, use the sample point offset of the synchronous state mode to take advantage of the precision of 50-ps increments (using the fine adjustment). Or, second, use the 250-ps resolution of the timing mode.

#### **Probe Accessories:**

- Probe pin with right angle ground

- 2 0.05 pitch grabbers

- SMT tack on signal and ground wire

- 4 Ground extender

# Primary Specifications and Characteristics

Timing Analysis

| Sample Period Accuracy                                     | ±0.005% of sample period                                                                                    |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Channel-to-Channel Skew                                    | 250 ps, typical                                                                                             |

| Time-Interval Accuracy                                     | ± (sample period<br>+ channel-to-<br>channel skew<br>+ 0.01% of time<br>interval reading)                   |

| Synchronous State Ana                                      | ys:s                                                                                                        |

| Maximum External Clock<br>Frequency                        | 1 GHz                                                                                                       |

| Setup/Hold Time<br>(Internal)                              | 350/350 ps (with<br>deskew) adjustable<br>with sample<br>placement                                          |

| Sample Placement with<br>Respect to External<br>Clock Edge | ±5 ns in 200 ps<br>increments (course<br>adjustment)<br>±250 ps in 50 ps<br>increments (fine<br>adjustment) |

| Number of Samples per<br>External Clock                    | Adjustable in increments of 1, 2, 4, 8, 16, 32                                                              |

| Maximum Sample Rate, with Oversampling                     | 2 GSa/s                                                                                                     |

| Triggering                                                 |                                                                                                             |

| Sequencer Speed                                            | 500 MHz, maximum                                                                                            |

| Timing/State Sequence<br>Levels                            | 4                                                                                                           |

|                                                            |                                                                                                             |

| Pattern Recognizers                          | 4                                                                                         |

|----------------------------------------------|-------------------------------------------------------------------------------------------|

| Maximum Channel Width<br>For Patterns        | 16 – one card<br>32 – two cards<br>48 – three cards<br>64 – four cards<br>80 – five cards |

| Edge Recognizers<br>(Timing only)            | 2                                                                                         |

| Maximum Channel Width<br>For Edges           | 16 – one card<br>32 – two cards<br>48 – three cards<br>64 – four cards<br>80 – five cards |

| Maximum Number of<br>Recognizers at One Time | 4                                                                                         |

| Timers / Counters                            | 1 per sequence level                                                                      |

| Probes                                       |                                                                                           |

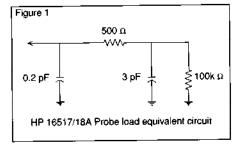

| Input de Resistance                          | 100k Ω, ± 2%                                                                              |

| Input Impedance                              | 500Ω typical,<br>at 100 MHz through<br>1 GHz                                              |

| Input Capacitance                            | 0.2 pF and then, through 500 $\Omega$ , 3 pF (see figure 1)                               |

| Minimum Voltage<br>Swing                     | 500 mV<br>peak-to-peak                                                                    |

| Threshold Range                              | ±5.0 V, adjustable in 10 mV increments                                                    |

|                                              |                                                                                           |

# Demonstrating Commitment to Meeting Your Evolving Digital Design Needs

#### Modularity

HP's modular 16500A/B family lets you configure your mainframe with the modules you need today, while providing you the flexibility to grow with your evolving digital design needs.

#### Intuitive User Interface

If you are already familiar with one HP Logic analyzer interface, you'll be able to start making measurements right away. An optional keyboard, mouse, or trackball provide you with the most flexible user interface available on any logic analyzer.

# **Quick-Start Training Kit**

Get a quick start making measurements with your logic analyzer. The Quick-Start Training Kit includes an active-circuit target system, a training guide, and software. Several easy-to-understand exercises are designed to improve the productivity of new or intermediate users.

# PACKARD

For more information, call your local HP sales office listed in your telephone directory or an HP regional office listed below for the location of your nearest sales office.

#### **United States:**

Hewlett-Packard Company 4 Choke Cherry Road Rockville, MD 20850 (301) 670-4300

Hewlett-Packard Company 5201 Tollview Drive Rolling Meadows, IL 60008 (708) 255-9800

Hewlett-Packard Company 1421 S. Manhattan Ave Pullerton, CA 92631 (714) 999-6700

Hewlett-Packard Company 2000 South Park Place Atlanta, GA 30339 (404) 980-7351

#### Canada:

Hewlett-Packard Ltd. 6877 Goreway Drive Mississauga, Ontario LAV 1M8 (416) 678-9430

#### Europe:

Hewlett-Packard

European Marketing Centre

P.O. Box 999

1180 AZ Amstelveen

The Netherlands

# Japan:

Yokogawa-Hewlett-Packard Ltd. 3-29-21 Takaido bigashi Suginami-ku, Tokyo 168, Japan (813) 3335-8192

# Latin America:

Hewlett-Packard Latin American Region Headquarters Monte Pelvoux No. 111 Lomas de Chapultepec 11000 Mexico, D.F. (525) 202 0155

# Australia/New Zealand:

Hewlett-Packard Australia Ltd. 31-41 Joseph Street Blackburn, Victoria 3130 Australia (A.C.N. 004 394 763) (03) 895-2895

# Far East:

Hewlett-Packard Asia Ltd. 22/F EIE Tower, Bond Centre 89 Queensway, Central Hong Kong (852) 848-7070

Technical information and prices in this document are subject to change without notice.

Printed in U.S.A. 5091-8096 E 6/93

### **Ordering Information**

#### HP 16517A

4-GHz Timing / 1-GHz Synchronous State Logic Analyzer Master Module

### HP 16518A

4-GHz Timing / 1-GHz Synchronous State Logic Analyzer Expansion Module (Requires HP 16517A)

# **Option AV8**

Extra operating and Programming Manuals

# Option 110

1-Mbyte or 2.5-Mbyte to 4-Mbyte CPU Upgrade for the HP 16500A mainframe

(Requires 16500A frame)

#### HP 16500B

Logic Analysis System Mainframe **HP 16500L**

Local area network card for 16500B

#### HP 16500U

Upgrades HP 16500A to an HP 16500B (Requires 16500A frame)