# 8-Port, 4x InfiniBand Switch (HDMP-2840)

# **Product Overview**

### **Applications**

- · Storage Area Networks (SAN)s

- · Servers and workstations

- Clustering

- I/O adapters

- · Data networks

- · High speed backplanes

#### **Features**

#### Hardware:

- 8 Independent InfiniBand data ports supports the 4x or 1x InfiniBand links

- Aggregate switch bandwidth of 160 Gbps and aggregate switch data rate of 128 Gbps

- Each 4x port supports bit rates up to 10 Gbps in each direction allowing a 16 Gbps full duplex data rate per port

- Integrated SerDes for reduced system cost, power consumption, and latency

- Unloaded fall-through switch latency of 110 ns including integrated SerDes

- Fully non-blocking internal switch architecture and support for cutthrough, and store and forward switching algorithms

- Support for both Unicast and Multicast packets

- Unicast forwarding table size of 16k entries

- Multicast forwarding table of 512 entries

- Error handling and packet checking for all data, link and management packets in hardware including ICRC check and generation for management packets

- Internal SRAM for packet buffering and queuing

- Programmable Virtual Lanes (VLs)

- Programmable partition key checking: check inbound packets only, outbound packets only, both inbound and outbound packets, or disable checks

- · Support for 16 partition keys per port

- Integrated CPU interface to support optional external processor for advanced management functionality

- I<sup>2</sup>C support for system configuration via external NVRAM, system bringup and system diagnostics

- IEEE 1149.1 TAP compliance

- Implemented in 0.18 micron 1.8 V, 6 metal layer process technology

- 400-pin 22 mm ceramic BGA FlipChip package

#### Software:

- Feature-rich management capabilities including on-board SMA, PMA and BMA

- Supports extended management functionality such as SNMP tunneling and subnet management, via the CPU interface to an optional external processor

- SMA support for SMP traffic and pass-thru SMP traffic as well as trap and notice queue management

- Support for all required InfiniBand performance and diagnostic counters

- Supports vendor-specific configuration and programming

#### InfiniBand:

- Compliant with InfiniBand architecture specification 1.0a requirements

- Exceeds or conforms to IBTA profiles A and B

## **Description**

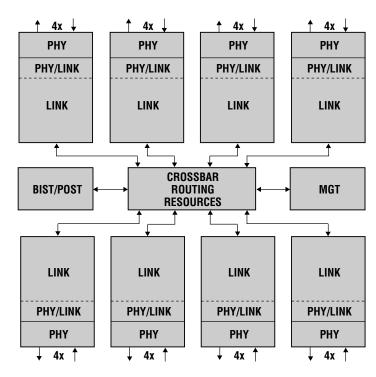

The HDMP-2840 is a highly integrated, cost effective 8-port 4x-channel switching solution.

Each port can run at 4x or 1x operating mode, which is defined as four pairs of full-duplex differential signals, or one pair of full-duplex differential signals, respectively.

The HDMP-2840 combines SerDes (SERializer-DESerializer) technology with additional logic to support a 2.0 Gbps InfiniBand data rate (2.5 GHz signaling).

Each port contains an independent Physical layer (Phy) and Link. The SerDes Phy block includes the analog transceiver through "8B/10B" encoding/decoding logic and elastic buffers for rate matching and lane de-

skew. The Phy transmitter block accepts 8-bit wide parallel data and serializes this data into a high-speed serial data stream. The high-speed outputs are capable of interfacing directly to connectors and copper cables for electrical transmission or to fiber-optic modules for optical transmission.

The Phy/Link block completes the required Phy functionality and provides an interface to the Data Link layer. This block contains the sync and idle character insertion, Phy training controller, and character recognition logic.

The InfiniBand specified Link block supports programmable Virtual Lanes (VLs) and other functions such as link state and status, error detecting and recording, flow control generation, and output buffering.

The input Virtual Lanes (VLs) within the Link are configurable to a programmable number of VLs and Maximum Transfer Units (MTUs) to support either one or two VLs at 4096 MTUs, or four VLs at 2048 MTUs, or eight virtual lanes at 1024 MTUs.

The HDMP-2840 Crossbar is designed with input buffers that can be drained faster than they can be filled. Each of the HDMP-2840's eight ports is treated in identical fashion in the crossbar. The Crossbar includes two additional internal ports for InfiniBand Management and internal BIST/POST.

The Management block includes agents for various programming, quality of service, performance monitoring, and error detecting services. These agents include PMA, the Performance Management Agent SMA, and BMA, the Baseboard Management Agent.

The HDMP-2840 can be configured to use an external processor for management-related functions that may be implemented in firmware. The CPU interface sends and receives both general service management and subnet management traffic in addition to other capabilities such as on chip initialization and diagnostics.

The HDMP-2840 requires an external differential clock generator at 62.5 MHz as reference clock. All internal clocks, including the transmit Phy clocks, are synthesized from this reference clock per the InfiniBand specification.

Figure 1. HDMP-2840 Functional Block Diagram.

For product information and a complete list of Agilent contacts and distributors, please go to our web site.

#### www.agilent.com/semiconductors

E-mail: SemiconductorSupport@agilent.com Data subject to change. Copyright © 2003 Agilent Technologies, Inc. June 11, 2003 5988-7782EN