# Applications of the OP AMP

**By:** John Getty

Laboratory Director

Engineering Dept.

University of Denver

Denver, CO

# Purpose:

Examine an OP AMP circuit design cycle and gain experience in OP AMP circuit analysis.

# **Equipment Required:**

- 1 HP 34401A Digital Multimeter

- 1 HP E3631A power supply

- 1 Protoboard

- 8 10-kΩ Resistors

- 1 470-Ω Resistor

- 4 1.2-kΩ Resistors

- 1 11-kΩ Resistor

- 3 1-kΩ Resistors

- 1 741 OP AMP

- 1 LM339 Quad Comparator

- 4 LEDs

#### Prelab:

Your supervisor at your new job as an instrumentation engineer is part of a design team working on a remote sensing project. Her part of the project is to design a signal transmission system and display for one of the remote sensors. The sensor is a digital device that outputs one octal number (base 8) represented by TTL (transistor-transistor logic) signals on each of three outputs (3 bits). For example, the sensor represents an octal 1 with an output of 5 V on the LSB (least significant bit). An output of  $5_8$  is represented by a TTL high (5 V) on the first and third bits (MSB, most significant bit) and the output of bit 2 is 0 V, representing a binary zero.

The design of the display is left to her discretion. If she had direct access to the three data lines, this design would not be difficult; one solution would be to connect each of the three binary signal conductors to it's own LED (light emitting diode). Each LED would then indicate a single binary digit. But in this case, she has been allocated only one signal conductor and a reference ground in a multi-conductor data cable. Two other conductors in the cable have been designated to supply  $\pm V_{\rm CC}$ , which she may use for power. Thus, the most serious constraint is that the signal must pass through a single conductor from the digital source to the LED display.

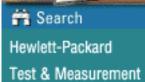

She has decided that the most efficient way to transmit the data is via an analog signal. This means the design must include a D/A (digital to analog) converter on the remote end, and a way to decode the data back into a format that can be read from a display by the system operator. To reduce the design time, she has divided her assignment into two parts. She will design the circuit to decode the analog signal and generate an appropriate display. She has assigned the D/A problem to you. Her specifications are that each increment in the binary number is to be represented by a 1 V increase in the signal on the conductor, e.g., a remote  $001_2$  produces 1 V, and a  $101_2$  produces 5 V. Your supervisor has told you the polarity of the signal doesn't matter. Luckily, she provided a terrific hint on a possible solution by recalling a circuit she built in college, an R-2R ladder circuit. On the back of an envelope, your supervisor drew a schematic similar to that of Fig. 1.

# Educator's Corner

#### 1. R-2R ladder circuit

In your lab journal, provide a detailed circuit analysis that shows that the Thévenin equivalent of the circuit of Fig. 1, defined at  $v_0$  to ground, is:

$$v_{TH} = \left(\frac{v_1}{2} + \frac{v_2}{4} + \frac{v_3}{8}\right)$$

$R_{TH} = R$

(Hint: Perhaps the easiest way to analyze this circuit is to use superposition and the unit output method; see Sect 3-1 of the text\* for details. For this circuit, assume all resistor values are exactly nominal.)

Figure 1

# 2. Interface circuit design

Let the resistance R, in Fig. 1, equal  $5.0~k\Omega$ . Design an OP AMP interface circuit for the R-2R ladder that will properly scale the signal to the specified voltage levels.

In your lab journal, make a table like the one below, and fill in the " $v_0$  calculated" column.

Table 1

| $\mathbf{v}_1$ | $\mathbf{v}_2$ | $v_3$ | ${ m v}_0^{}{ m calculated}$ | v <sub>0</sub> actual |

|----------------|----------------|-------|------------------------------|-----------------------|

| 0              | 0              | 0     |                              |                       |

| 0              | 0              | 5     |                              |                       |

| 0              | 5              | 0     |                              |                       |

| 0              | 5              | 5     |                              |                       |

| 5              | 0              | 0     |                              |                       |

| 5              | 0              | 5     |                              |                       |

| 5              | 5              | 0     |                              |                       |

| 5              | 5              | 5     |                              |                       |

## **Procedure**

### 1. Build the D/A Converter

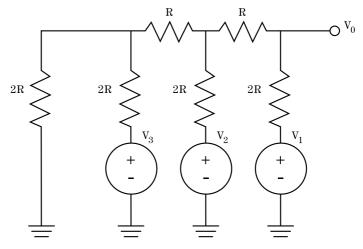

a. With the power off, connect the circuit of Fig. 1. The goal is to measure  $v_o$  for every possibility in Table 1. Simulation of the two TTL signal levels (0 and 1) for  $v_1$ ,  $v_2$ , and  $v_3$  is accomplished by applying either 0 V or 5 V to the appropriate places in the circuit. Figure 2a shows an example of how this may be accomplished for  $v_3 = 5$  V,  $v_2 = 0$  V and  $v_1 = 5$  V. Simply by connecting to "A", 0 V is applied. To obtain 5 V, the resistor is connected to "B" as shown in Fig. 2b.

- b. Connect the three inputs  $v_1$ ,  $v_2$  and  $v_3$ , so that when power is applied all three will be at 5 V. Check the circuit one more time, then turn on the power and check the output voltage at pin 6 of the OP AMP. Is the output what is expect for this octal input? If not, troubleshoot the circuit. It may be necessary to "tweak" the value of R<sub>f</sub> to obtain the desired  $7 \, V_{DC}$  output. If you are not sure about a connection, ask for help.

- c. When your circuit is working, verify circuit performance by recording data for all of the other combinations. This information will be used by your supervisor to ensure her decoding circuit is receiving the proper voltage levels.

Figure 2

### 2. Build the A/D converter

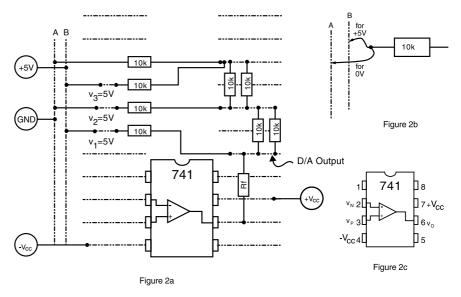

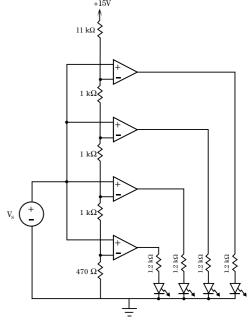

Your supervisor has decided to use seven LEDs in the display. An octal 0 is indicated when all of the LEDs are off. Each increment in the octal number will light an additional LED. Her technique for decoding the analog signal is to use an A/D (analog to digital) converter called a flash converter. Her design uses two LM339s, (quad comparators), with the pin-out shown in Fig. 3. The circuit she gave you for the display requires that the output of your D/A be positive. If your D/A outputs negative voltages, you will need to modify her design. She wants you to verify her design by constructing the first half of her circuit as shown in Fig. 4. Conduct a system test by connecting your design to her prototype to ensure the entire system is in compliance with the design specs.

- a. Breadboard your supervisor's design and verify the system performance.  $\pm V_{\rm CC}$  for the LM339 will be  $\pm 15~V_{\rm DC}$

- b. When you get the system operational, have your supervisor (or perhaps your lab instructor) sign off in your lab journal, verifying system compliance with design specifications.

Figure 4

#### Conclusion:

1. Compute error

Compute the percent error for each of the data points recorded for your D/A converter. Is the error consistent, i.e. does the error for each of the inputs have the same sign and magnitude? If not, why? Suggest ways to improve the precision of the analog voltage output of your circuit.

- 2. Analyze your supervisor's design

- a. Identify what reference voltage she used at each of the four comparators. What could be her motivation for selecting these particular voltages?

- b. When "forward biased", that is, when an LED is on, LEDs usually have a voltage drop of 1.7 V. Most are operated at about 10 mA. As shown in Fig. 4, your supervisor specified  $1.2~\mathrm{k}\Omega$  "current limit" resistors in each LED branch of her circuit. Did she select the correct resistors?

<sup>\*</sup> Roland E. Thomas and Albert J. Rosa, <u>The Analysis and Design of Linear Circuits</u>, Prentice Hall, (New Jersey, 1994)