# Agilent 81250 ParBERT 81250

## パラレル・ビット・エラー・レート・テスタ

Product Overview

バージョン4.2.3(ParBERT 81250ソフトウェア改訂

4.2xに対応)

**675MHz、1.65Gbps、2.7Gbps、

3.35Gbps、10.8Gbpsおよび

43.2Gbpsに対応する

パラレル・ビット・エラー・

レート・ソリューション**

### ご注意

2002年6月13日より、製品のオプション構成が変更されています。

カタログの記載と異なりますので、ご発注の

前にご確認をお願いします。

Agilent Technologies

# Agilent ParBERT 81250

Agilent ParBERT 81250は、最高43.2Gbpsで動作するモジュラ型のパラレル・ビット・エラー・レート・テスト・ソリューションです。ParBERT 81250には、43.2Gbps、10.8Gbps、2.7Gbps、および675MHzで動作するモジュールが用意されています。本システムを使えば、疑似ランダム・ワード・シーケンス(PRWS)、標準の疑似ランダム・ビット・シーケンス(PRBS)、ユーザ定義のパターンをパラレル・ライン上に生成できます。ユーザ定義パターン、PRBS/PRWS、混合データ(ユーザ定義パターンとPRBSとの組み合わせ)を使って、ビット・エラー・レートの解析を実行できます。

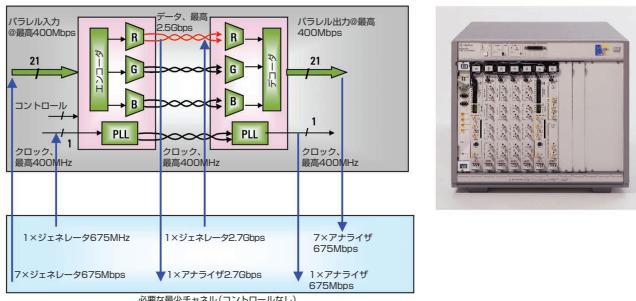

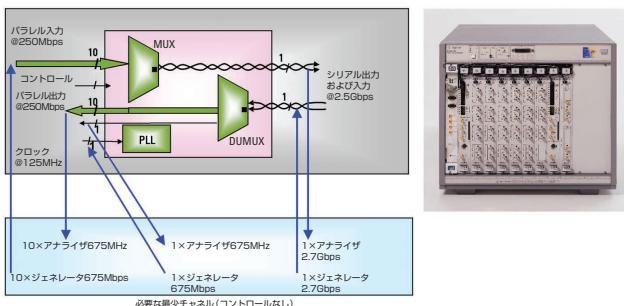

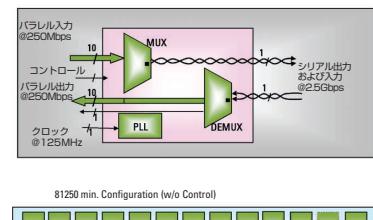

ParBERT 81250が特に威力を發揮するのは、テレコムおよびシステム・エリア・ネットワーク(SAN)向けICに用いられるマルチプレクサ/デマルチプレクサ(mux/demux)またはSERDES(シリアルライザ/デシリアルライザ)のテスト、製造環境での複数のトランスマッタ/レシーバ・テスト、フォワード・エラー訂正(FEC)デバイスのテストなどです。ParBERT 81250は、必要な場合はDUTにデータや制御信号も供給できます。

ParBERTメジャメント・ソフトウェアは、以下に示す3つの異なるレベルの測定解析機能を備えたパッケージです。

1. 製造試験に最適な高速アイ・マスク合否判定

2. セットアップ/ホールド時間およびアイ開口仕様の結果がすぐに得られるため、値の計算が不要

3. 詳細な根本原因解析の結果を図でわかりやすく表示。傾向をすばやく明確に表示(例: カラー区分表示)

Agilent ParBERT 81250は、特に以下の用途に適しています。

## - マルチプレクサ/デマルチプレクサ・テスト

1. OC-768デバイスのテスト: ParBERT 81250の43.2Gbpsと、2.7Gbpsまたは10.8Gbpsモジュールを使って、16:1および4:1 40ギガビット・デバイスをテストできます。

2. OC-192デバイスのテスト: ParBERT 81250の10.8Gbpsモジュールを使って、MUX/DEMUXの高速シリアル・サイドをテストできます

す。667MHzまたは2.7Gbpsモジュールと組み合わせると、マルチプレクサ/デマルチプレクサのパラレル/シリアル両方をテストできます。

3. OC-48デバイスのテスト: ParBERT 81250を使えば、ゴールデン・デバイスなしでOC-48までのテストが可能です。

## - SAN ICの特性試験

- 複数のトランスマッタ/レシーバの製造試験

- FECデバイス・テスト

これらのアプリケーションの詳細については、Brochure(カタログ番号5968-9250J)を参照してください。Agilent ParBERT 81250 43.Gの詳細については、カタログ番号5988-3020ENを参照してください。ここでは、10.8GbpsまでのParBERTソリューションについて説明します。

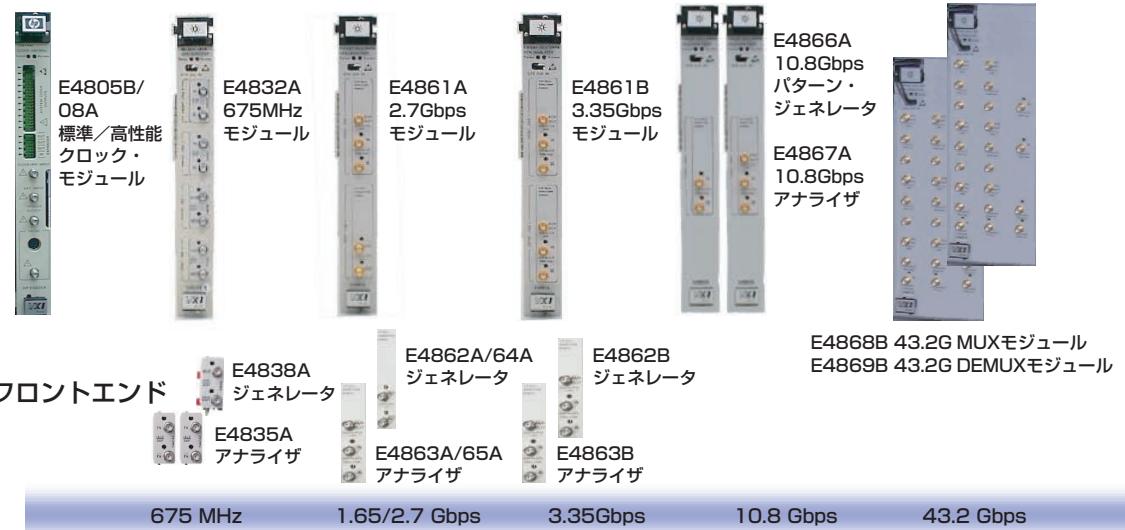

## モジュール

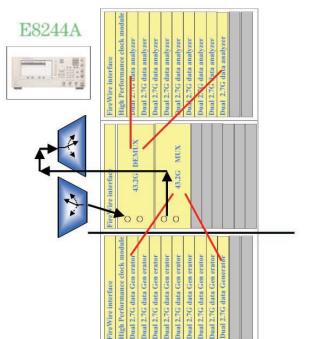

図1. ParBERT製品ファミリ

# ParBERT 81250の主な機能と特長

| 機能                                                                                                                                                                       | 特長                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 新機能：3.35Gモジュール                                                                                                                                                           | <ul style="list-style-type: none"> <li>XAUのパラレル・ラインをテスト</li> <li>OC-768 (1×43.2Gおよび16×3.35GHz) のパラレル・ライン (SFI5) とシリアル・ラインをテスト</li> <li>製造段階で複数のE/OおよびO/Eデバイスを同時にテスト可能</li> <li>ジッタのエミュレーションによりジッタ許容値をテスト</li> </ul> |

| <ul style="list-style-type: none"> <li>疑似ランダム・ワード・シーケンス (PRWS) および最大<math>2^{31}-1</math>の標準PRBSの生成</li> <li>パラレル・ポートからのユーザ定義データ、PRBS、混合データを使ったビット・エラー・レートの解析</li> </ul> | <ul style="list-style-type: none"> <li>パラレルBER測定を実行可能 — マルチプレクサ/デマルチプレクサ (シリアルライザ/デシリアルライザ) 回路に最適</li> </ul>                                                                                                        |

| <ul style="list-style-type: none"> <li>675MHzで最大128チャネル</li> <li>2.7Gbpsおよび3.35Gbpsで最大64チャネル</li> <li>10.8Gbpsで最大30チャネル</li> </ul>                                       | <ul style="list-style-type: none"> <li>1台のシステムでアプリケーション・ニーズに適合</li> <li>チャネルを使ってDUTとの間で制御信号をやりとり</li> </ul>                                                                                                         |

| 最高43.2Gbpsの速度                                                                                                                                                            | 広帯域幅テクノロジーに対応                                                                                                                                                                                                       |

| <ul style="list-style-type: none"> <li>チャネル (ジェネレータ/アナライザ) と異なる速度のフロントエンドを混合可能</li> <li>モジュラ型の拡張可能なアーキテクチャ</li> </ul>                                                    | <ul style="list-style-type: none"> <li>多数のチャネルと多数の周波数を持つ複雑なデバイス、例えばマルチプレクサ/デマルチプレクサ (SERDE) やFEC回路などをテスト可能</li> </ul>                                                                                               |

| <ul style="list-style-type: none"> <li>シングルエンド、低電圧信号および差動信号 (真の差動信号も可) を生成、解析可能</li> </ul>                                                                               | <ul style="list-style-type: none"> <li>LVDS、ECL、PECL、SSTL-2などのロジック回路のテスト</li> <li>マージン・テスト、周波数/レベル変化のエミュレーション、デバイスの徹底したストレス・テストに必要な信号を生成</li> </ul>                                                                 |

| <ul style="list-style-type: none"> <li>シーケンスとループを使ったデータの生成と解析</li> </ul>                                                                                                 | <ul style="list-style-type: none"> <li>メモリ・ベース (最大32Mビット) またはPRBS/PRWSのデータを含む複雑なシーケンスを生成</li> <li>ヘッダとペイロードのついたデータ・パケットを生成</li> <li>DUTからの制御信号に反応</li> </ul>                                                        |

| <ul style="list-style-type: none"> <li>自動位相/自動遅延アライメント</li> </ul>                                                                                                        | <ul style="list-style-type: none"> <li>予測データと入力データの自動アライメント</li> <li>正しいサンプル・ポイントを手動で見つける必要がないので、時間の節約が可能。通常100msしかからないので、製造に最適</li> </ul>                                                                          |

| <ul style="list-style-type: none"> <li>わかりやすいWindows-NT®ベースのユーザ・ソフトウェア</li> </ul>                                                                                        | <ul style="list-style-type: none"> <li>「標準」ビューと「詳細」ビューにより、測定に必要なパラメータだけを表示</li> </ul>                                                                                                                               |

| 3つの異なる測定機能：                                                                                                                                                              | <ul style="list-style-type: none"> <li>これらの拡張測定機能によってDUTの動作をさらに詳しく解析可能</li> </ul>                                                                                                                                   |

| <ul style="list-style-type: none"> <li>高速アイ・マスク合否判定</li> </ul>                                                                                                           | <ul style="list-style-type: none"> <li>自動しきい値調整</li> <li>生産部門に最適。テスト時間が最大で10分の1に短縮。1秒以内に2.7Gbpsで2チャネルをテスト可能</li> </ul>                                                                                              |

| <ul style="list-style-type: none"> <li>DUTの出力タイミング測定 (スキュー、セットアップ/ホールド時間など)</li> </ul>                                                                                   | <ul style="list-style-type: none"> <li>必要な仕様を表示可能、例：クロック出力からデータ出力までの時間 (セットアップ/ホールド時間)、値の計算が不要</li> <li>ジッタ・ヒストグラムを表示</li> </ul>                                                                                    |

| <ul style="list-style-type: none"> <li>アイ開口測定</li> </ul>                                                                                                                 | <ul style="list-style-type: none"> <li>傾向をすばやく明確に表示 (例：カラー区分表示)</li> </ul>                                                                                                                                          |

| <ul style="list-style-type: none"> <li>総合的なBER測定</li> </ul>                                                                                                              | <ul style="list-style-type: none"> <li>現時点と積算のBER、および転送された1、0、総ビットのエラーを一度に表示</li> <li>合否測定</li> <li>後処理用のファイルを生成</li> <li>端子のBERが再同期BERしきい値を超えた場合、測定で自動的に再同期を実行</li> </ul>                                          |

| <ul style="list-style-type: none"> <li>内蔵ジェネレータ/アナライザと異なる速度の外部クロックにシステムを同期可能</li> </ul>                                                                                  | <ul style="list-style-type: none"> <li>マルチ周波数デバイス、例えばマルチプレクサ/デマルチプレクサ (SERDE) やFEC回路のテスト</li> </ul>                                                                                                                 |

| <ul style="list-style-type: none"> <li>ジェネレータ/アナライザの各チャネルの電圧レベルとタイミング遅延を独立にプログラム制御可能</li> </ul>                                                                          | <ul style="list-style-type: none"> <li>さまざまなテクノロジーを採用したデバイスの特性試験が可能</li> </ul>                                                                                                                                      |

| <ul style="list-style-type: none"> <li>プラグ・アンド・プレイ・ドライバ</li> </ul>                                                                                                       | <ul style="list-style-type: none"> <li>リモート・プログラムの開発が簡単</li> </ul>                                                                                                                                                  |

| <ul style="list-style-type: none"> <li>アナライザ遅延/ジェネレータ遅延 (3.35Gジェネレータのみ) を中断なしに変更可能</li> </ul>                                                                            | <ul style="list-style-type: none"> <li>アナライザ遅延が必要な測定も連続した信号で実行可能</li> </ul>                                                                                                                                         |

## 主な特長(続き)

### 最高3.35Gbpsの パラレルBER測定

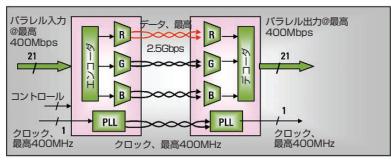

ParBERT 81250を使えば、マルチプレクサ／デマルチプレクサ(シリアルライザ／デシリアルライザ)デバイスのテストが簡単になります。疑似ランダム・ワード・シーケンス(PRWS)をパラレル・ラインで生成し、ユーザ定義パターン、最大 $2^{31}-1$ のPRBS、およびそれらの組み合わせによってビット・エラー・レートを解析できるのは、ParBERT 81250だけです。

### PRBS/PRWSおよびメモリ機能

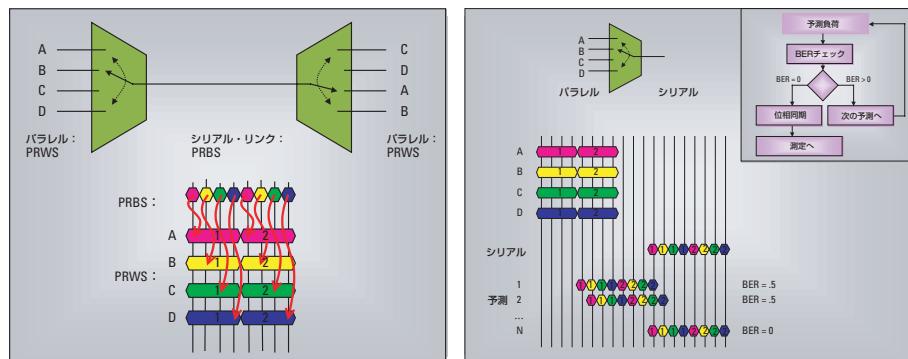

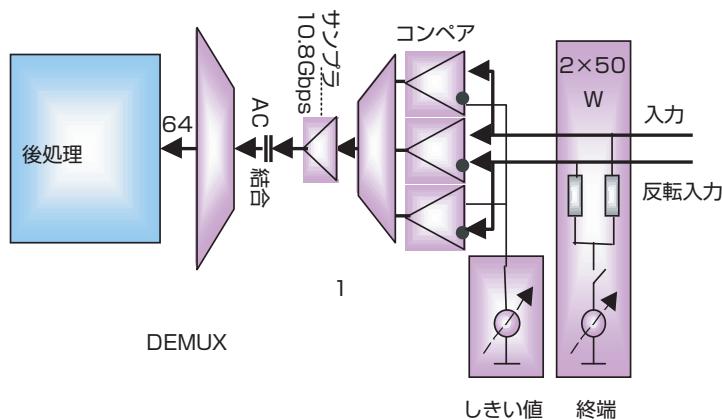

PRWSは、 $2^n-1$ 次多項式、PRBSアルゴリズム、パラレル・バス幅によって定義されます。PRWSの各ビットがパラレル・ラインに割り当てられ、多重化されてPRBSになります(図3を参照)。

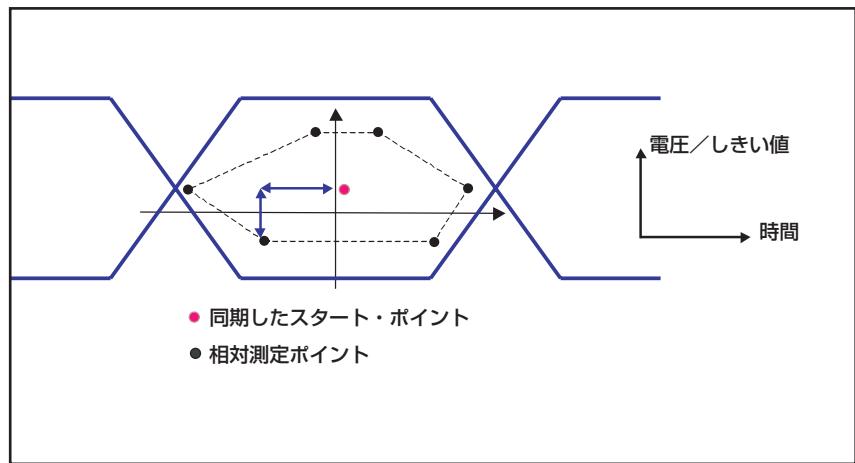

### 自動位相／自動遅延アライメント

入力一出力間のレイテンシは正確にわからないことが多く、決定できない場合もあるため、入力データと出力データの同期を行う必要があります。ParBERT 81250には入力データを自動的に同期／整列するための3つの機能があります(図4および5を参照)。

- 1) PRBS使用時の、ビットごとのデータ・シフト

- 2) ユーザ定義パターン使用時の、ワード検出

- 3) 測定を中断せずに、アナライザのサンプリング・ポイント遅延を最大10ns移動可能

- サンプリング・ポイント遅延の移動とデータ・パターンのアライメント(1と2)とを併用することにより、同期を微調整することもできます。

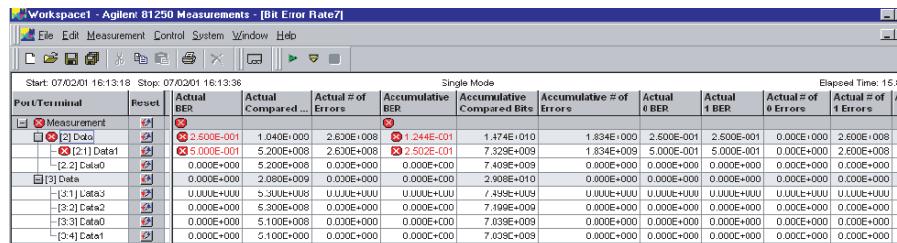

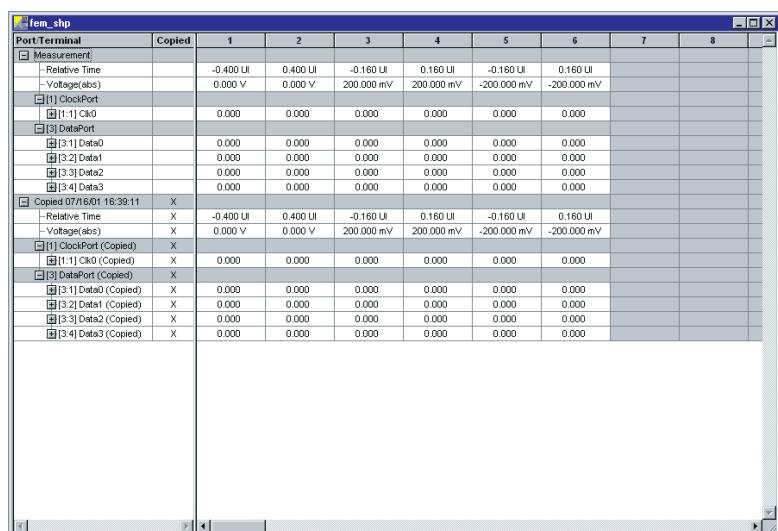

図2：BER結果画面

図3：マルチプレクサ／デマルチプレクサ・

アプリケーション：PRBSとPRWSとの関係

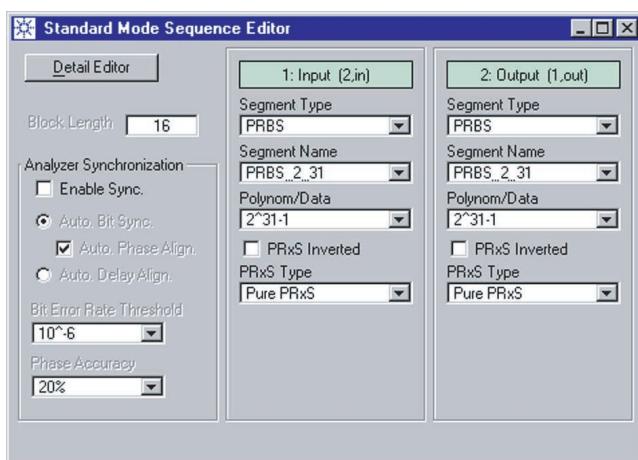

図5：PRBS/PRWSパターンおよびデータ同期モード選択時の標準ダイアログ・ボックス

### アナライザ遅延を中断なしで変更可能

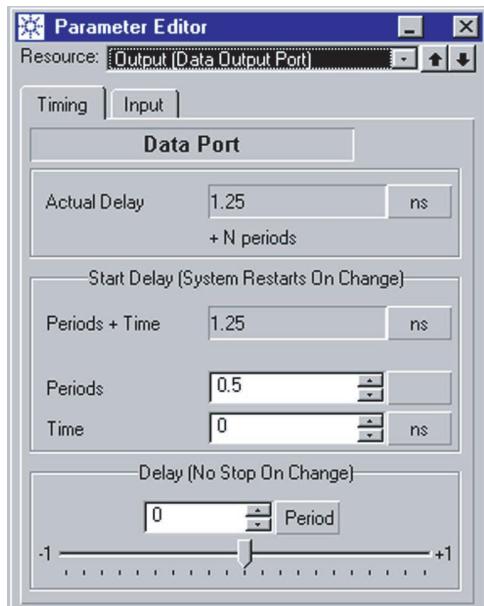

測定実行中に機器を停止せずにアナライザ遅延を±1周期の範囲で変更できます(図6を参照)。3.35Gモジュールでも同様にアナライザおよびジェネレータにおいて行うことができます。

図6：タイミング解析のためのパラメータ・エディタ

### マルチ周波数

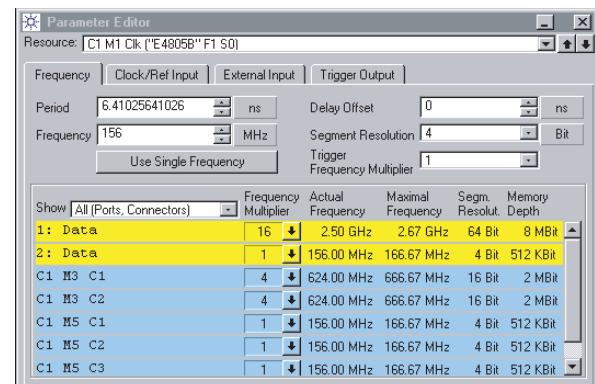

ParBERTはモジュラ構造をとっているため、チャネルごとにスピードを変えることができます。

したがって、1つのParBERTシステムで異なるスピードを持つチャネルを組み合わせることができます。ParBERTシステムに1つ以上のクロック・グループを設定できます。各クロック・グループはそれぞれ、1個のクロック・モジュールによって制御されます。1つのクロック・グループ(あるクロック・モジュールが制御しているチャネルのグループ)内では、 $2^n$ 、 $n=1, 2, \dots, 10$ の周波数比が可能です(図7を参照)。

図7：マルチ周波数設定のためのパラメータ・エディタ

2個のクロック・グループを使用する場合、 $m/n$   $m, n=1, 2, \dots, 256$ の周波数比が可能です。「アプリケーションの例」に、2クロック・システム構成をいくつか示します。

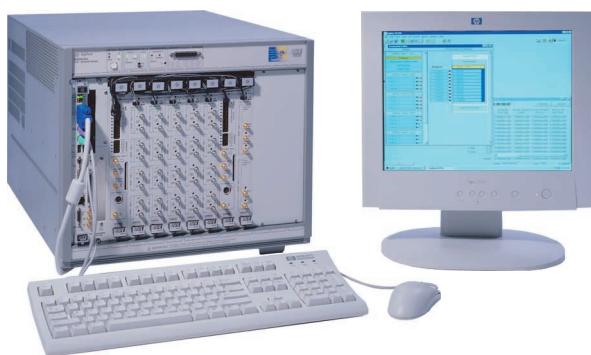

# 基本プラットフォームの解説

ParBERT 81250は、測定に最適な機能が得られるように考慮されています。ParBERTはモジュール方式によって、複数のモジュールとフロントエンドを提供します。10.8Gbpsでは、ジェネレータとアナライザ用の専用モジュールがあります。2.7Gbpsと675MHz/Mbpsでは、モジュールは2ないし4個のフロントエンドを収容できます。

フロントエンドで、測定器の入出力コネクタの種類が決まります。すなわち、測定器の速度と入出力機能はフロントエンドによって決まります。複数モジュールではフロントエンドの混用が可能です。

選択したフロントエンドを、**データ・モジュール**に組み込みます。このモジュールは、PRBS/PRWSなどのデータ・パターンのシーケンス設定、生成、解析を担当します。データ・モジュールと最低1台のクロック・モジュール(測定器の共通システム周波数を生成)をメインフレームに組み込みます。

VXIフレームには、13個のスロットが用意されています。Firewireインターフェースを使用し1個のクロック・モジュールを組み込むこめば、メインフレームに収容できる最大チャネル数は、10.8Gbpsで11チャネル、2.7Gbpsで22チャネル、675MHzで44チャネルです。チャネル数が足りない場合、拡張フレーム(最大2台)を追加することにより、1つのクロック・グループの中で最大チャネル数まで拡張できます。

表6には、スピード別の主要特性の概要が示されます。

|                           | 675MHz             | 2.7Gbps/3.35Gbps                                      | 10.8Gbps                  |

|---------------------------|--------------------|-------------------------------------------------------|---------------------------|

| データ・レート・レンジ               | 333.3kHz~675MHz    | 333.4Mbps~2.7Gbps<br>20.8Mbps~3.35Gbps                | 9.5~10.8Gbps              |

| 1フレーム/+2拡張フレーム<br>内のチャネル数 |                    |                                                       |                           |

| 外部PCを使用時                  | 44/132             | 22/66<br>20/62                                        | 11/33<br>10/31            |

| 2スロット付きPCを使用時             | 40/124             |                                                       |                           |

| 入力/出力                     | 差動&シングルエンド         | 差動&シングルエンド                                            | 差動&シングルエンド                |

| データ機能                     | PRBS/PRWS/2Mメモリ    | PRBS/PRWS/8/16Mメモリ                                    | PRBS/PRWS/32Mメモリ***       |

| ジェネレータ・フォーマット             | DNRZ, RZ, R1       | 2.7G: DNRZ,<br>50%クロック                                | DNRZ、個別の<br>クロック出力**      |

| 対応ロジック信号                  | TTL, (P) ECL, LVDS | 3.35G: DNRZ, R1, RZ<br>CML, (P) ECL*,<br>LVDS, SSTL-2 | CML, ECL, LVDS,<br>SSTL-2 |

注記： \*PECLの場合、アナライザ入力にはバイアス・ティーが必要

\*\*個別のクロック出力はシングルエンドのみ

\*\*\*平衡バターンのみ

表6：PARBERTチャネルの主要特性

異なる複数のクロック速度で動作させる場合、それらの速度が2、4、8、16(E4832A使用時)および2と4(E4861A使用時)で割り切れるか倍数になっていない場合は、複数のクロック・モジュールが必要になります。例えば、1:7または1:10のマルチプレクサ/デマルチプレクサ・デバイスをテストする場合には、2台のクロック・モジュールが必要です。次章でアプリケーション例を参照してください。

ParBERT 81250のユーザ・ソフトウェアは、2スロットのVXI PCまたは、IEEE 1394 PC-VXIリンクで接続された外部PCで動作します。オペレーティング・システムはMS Windows NT 4.0またはWindows 2000です。

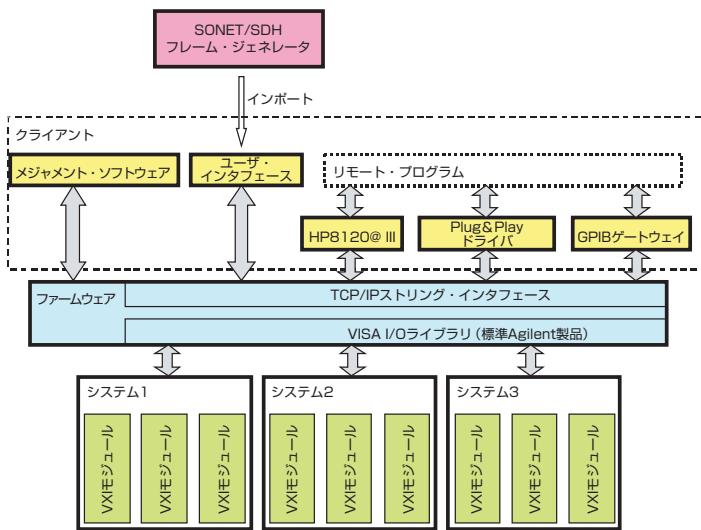

ParBERT 81250ユーザ・ソフトウェアには以下のものが含まれます。

- グラフィカル・ユーザ・インターフェース

- メジャメント・ソフトウェア

- SONET/SDHフレーム・ジェネレータ

- ファームウェア・サーバ

- VXI Plug & Play ドライバ

実行時、ソフトウェアは複数のプロセスが起動しています。新しい図をご覧ください。ファームウェア・サーバはハードウェアを制御し、グラフィカル・ユーザ・インターフェースおよびハードウェア・モジュール間をリンクします。また、メジャメント・ソフトウェアまたは任意のカスタム・リモート・プログラムにより、ファームウェア・サーバとの対話が可能です。リモート・アクセスはAgilent VEEまたはC/C++/Visual BasicプログラムからのPlug&Play ドライバ、あるいはSCPI言語により可能です。これにより標準VXIモジュールを含むVXIシステムのカスタマイズが可能になります。

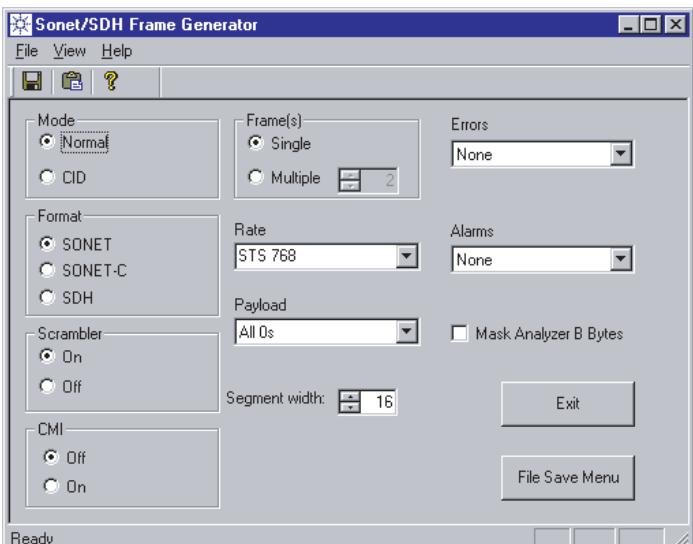

SONET/SDHのフレーム・ジェネレータでは、フレーム・ベース・データを設定できます。選択可能なエディタを以下に示します。

- SONET/SONET-C/SDH

- スクランブル・オン/オフ

- データ・レート (STS3~STS768)

- エラー&アラームの挿入

- ペイロードのタイプ(定義済み、PRBS、手動エディタまたはカスタム・インポート)

- ポート幅

一般的なフレームは表示および編集が可能です。フレーム・データをASCIIフォーマットに変換し、81250のハードウェアが使用するセグメントヘインポートすることができます。そのため、81250ジェネレータは、1ストリームのフレームを供給でき、81520アナライザはそのフレームを予測データとして使用することができます。

図7b：ソフトウェア・アーキテクチャ

図7c：SONET/SDHエディタ

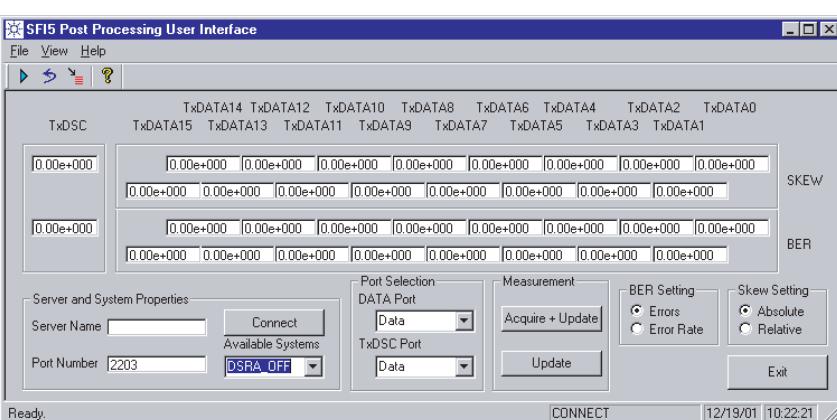

図7d：SFI5の後処理

### SFI-5：パラレル・データ&DSCビットの解析

16個のデータ・チャネルが有効であることを確認してください。(有効なPRBS 2<sup>7</sup>-1または2<sup>11</sup>-1ストリーム)

16個のデータ・チャネルがスキュー仕様内であることを確認してください。DSCビットが有効であることを確認してください。

- 補正ヘッダ

- 16個のデータ・チャネルに一致

# メジャメント・ソフトウェア

ParBERTメジャメント・ソフトウェアには、以下の測定が含まれます。

- 1.BER測定

- 2.高速アイ・マスク測定

- 3.DUT出力タイミング測定

- 4.アイ開口測定

ParBERT 81250メジャメント・ソフトウェアは、すぐに使用できる測定ユーザ・インターフェースです。ParBERT 81250を使えば、高速デジタル・コンポーネントおよびモジュールの検証と特性評価を簡単に行うことができます。

メジャメント・ソフトウェアには、以下に示す3つの異なるレベルの測定解析機能があります。

## 1. 製造試験に最適な高速アイ・マスク合否判定

製造試験の場合、ビット・エラー・レート(BER)に所定のしきい値を設定するなど、ある限界値に対するテストが実行できます。高速アイ・マスク合否判定によって、デバイスのテスト時間を以前のテスト手法と比べ、最大10分の1に短縮できます。テストの所要時間は1秒(代表値)です。

## 2. クロック出力からデータ出力までの時間(セットアップ/ホールド時間)、スキューワンおよびアイ開口仕様の結果がすぐに得られるため、値の計算が不要

## 3. 根本原因解析の結果を図で表示。傾向をすばやく明確に表示(例:擬似カラー区分表示)

研究開発の場合、被測定デバイス(DUT)の特性評価に使用できます(DUTの限界値と仕様を見つけ、結果を図を使ってわかりやすく表示できます)。

使いやすいWindows® NT 4.0ベースGUIおよび図による結果表示により、テストの開発が容易になり、テストを簡単に実行できます。データをエクスポートしたり、図や数値から成る結果を印刷することができます。

表1:概要

|               |                                                                                          |

|---------------|------------------------------------------------------------------------------------------|

| セーブ/リコード      | ワークスペース<br>単発測定                                                                          |

| コピー/ペースト      | 測定値同士を比較するための測定データ                                                                       |

| プリント          |                                                                                          |

| エクスポート        | 測定データ(ASCII)                                                                             |

| オンライン・ヘルプ     |                                                                                          |

| リモート・インターフェース | Plug&Play ドライバ<br>アクティブXコンポーネントを使い、VEE、Visual C++、VB、Labview、Mathlab、Excelで測定を簡単に統合できます。 |

Agilent VEE、National InstrumentsのLabVIEW®、Excel、Agilent TestExec、C/C++、Microsoft® VisualBasicを使い、テスト監視プログラムを作成できます。

メジャメント・ソフトウェアは、各ParBERT 81250システムに付属の標準ソフトウェア・パッケージに含まれています。

## BER測定

ビット・エラー・レート測定では、送信されたビットの総数とエラーとなったビット(判定しきい値に適合しないビット)の数を測定します。0と1の現時点のBER、0と1の現時点のエラー、0と1の積算BER、1と0の積算エラーをすぐに表示することができます(図2を参照)。

ビット・エラー・レート測定は、単発で、あるいは繰り返し実行できます。複数の実行およびエラー・カウント・オプション、停止基準を定義できます。繰り返しモードの場合、再同期が自動的に行なわれます。繰り返しモードはデバイスの特性評価に適しており、研究開発で例えば温度の変化がBERに与える影響を測定する場合などに便利です。単発モードは、指定したエラー数あるいは秒数に達したときに測定を中止できるので、製造に便利です。

以下の測定結果が得られます。

- エラーとなった1と0を同時に表示した画面

- ログ・ファイル

- 再同期

- 合否結果

表2:BER測定

|         |                                                                               |

|---------|-------------------------------------------------------------------------------|

| 測定パラメータ | BER<br>比較ビット<br>予測0からのエラー<br>予測1からのエラー<br>合計エラー<br>前回の測定周期からのパラメータ<br>積算パラメータ |

| 測定モード   | 単発または繰り返し<br>繰り返し速度は秒単位でプログラム可能<br>(このモードでは再同期をイネーブルにできます)                    |

| 合否      | 現時点のパラメータと積算パラメータに対する合否                                                       |

| ログ・ファイル | すべての測定対象パラメータを記録                                                              |

## 高速アイ・マスク測定

高速アイ・マスク測定は、通常所要時間が(同期も含めて)1秒しかかからないため、製造試験での使用に最適です。この測定では、アイ全体ではなく、あらかじめ定義したポイント数(1~32)のBERを測定します。ポイント数は、しきい値と測定の開始点を基準としたタイミング値によって定義されます。測定の合否基準とBERのしきい値を入力し、シーケンスによってアイの中間点を見つけた後、BERを実行します。例えば、しきい値を定義すると、ParBERTが最適なサンプル・ポイントおよびハイ・レベルとロー・レベル(20%と80%など)を見つけます。

以下の測定結果が得られます。

- 定義済みサンプリング・ポイントにおけるBER

- 合否結果

図8：高速アイ・マスク測定の動作のしくみ

図9：高速アイ・マスクのセットアップおよび結果ウィンドウ

| 周波数      | チャネル数 | 測定ポイント数 | 比較されるビット | 測定時間 |

|----------|-------|---------|----------|------|

| 2.67Gbps | 2     | 6       | $10^6$   | <1 s |

| 2.67Gbps | 2     | 32      | $10^6$   | ~1 s |

| 675 MHz  | 16    | 6       | $10^6$   | ~6 s |

| 675 MHz  | 16    | 32      | $10^6$   | ~6 s |

表3：高速アイ・マスク測定の時間例

(IEEE 1394 PCリンクを介してシステム上で実行)

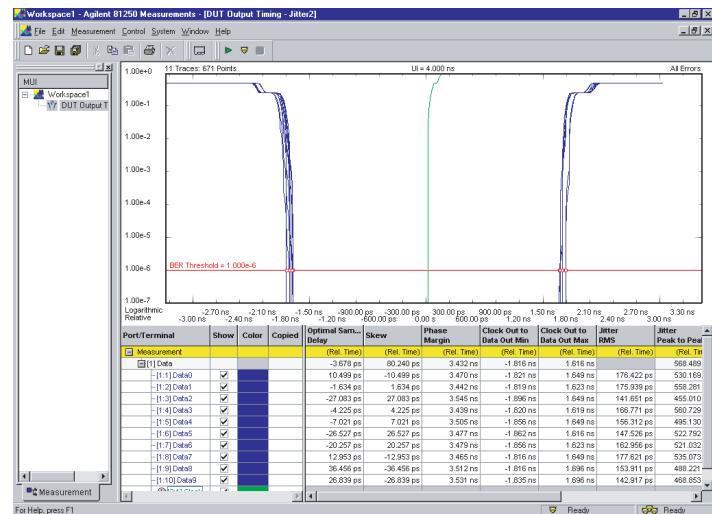

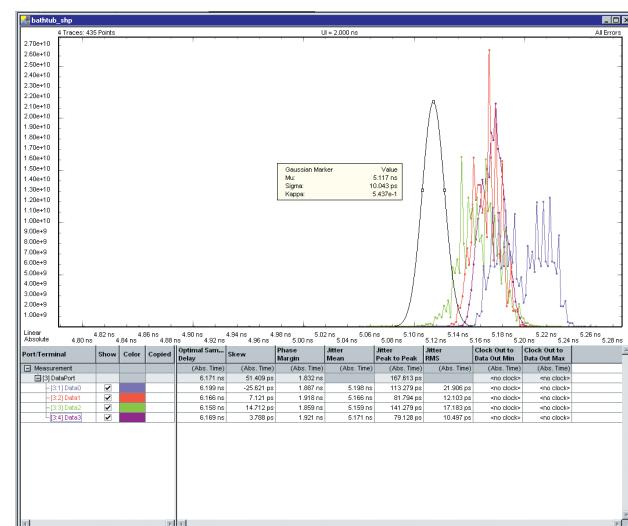

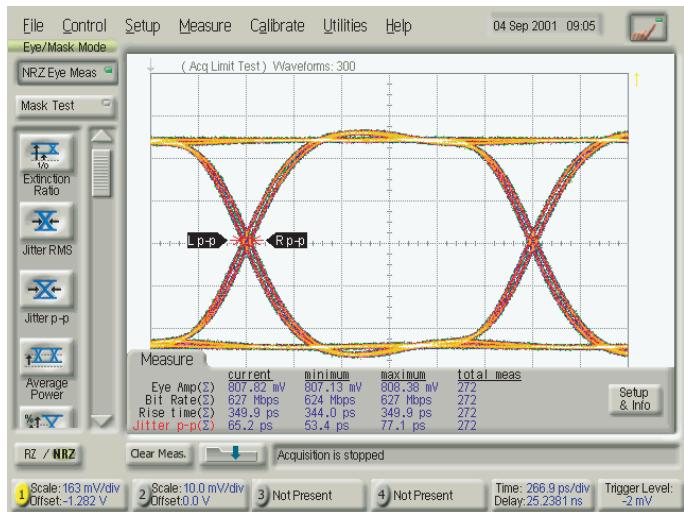

# DUT出力タイミング測定

この測定では、DUT出力のBER対サンプリング・ポイントの遅延を測定します。測定結果は、バスタブ・カーブとして図示されます。遅延の中心は、常にポート(端子)の最適サンプリング遅延ポイントに来ます。クロックを定義した場合、クロックとデータのアライメントが測定されます。絶対遅延を測定できる場合、絶対遅延も表示されます。エッジ同士を比較する相対タイミングも可能です。

以下の測定結果が得られます。

- クロック出力からデータ出力までのタイミング関係(セットアップ/ホールド時間)

- 出力間のスキュー

- 最適サンプリング・ポイントにおける遅延

- 位相マージン

- 合否結果

選択したBERしきい値に対する戻り値のみを示す、数値表示もあります。

図10：DUT出力の測定結果をバスタブ・カーブとして表示

図11：ジッタは、バスタブ・カーブから直接、式で示すことができます。ジッタをヒストグラムとして表示します。

表4：DUT出力のタイミング測定

|             |                                                                                   |

|-------------|-----------------------------------------------------------------------------------|

| タイミング・パラメータ | 最適サンプリング・ポイントの遅延<br>位相マージン<br>クロックからデータ出力までの最小値<br>クロックからデータ出力までの最大値<br>チャネル間スキュー |

| ジッタ・パラメータ   | rmsジッタ<br>平均値<br>特定BERのピーク・ピーク・ジッタ                                                |

| 合否          | 全タイミング・パラメータとジッタ・パラメータが対象<br>各パラメータを個別にイネーブル可能                                    |

| グラフ         | BER対サンプリング遅延の表示<br>2個のマーカ：遅延、BER                                                  |

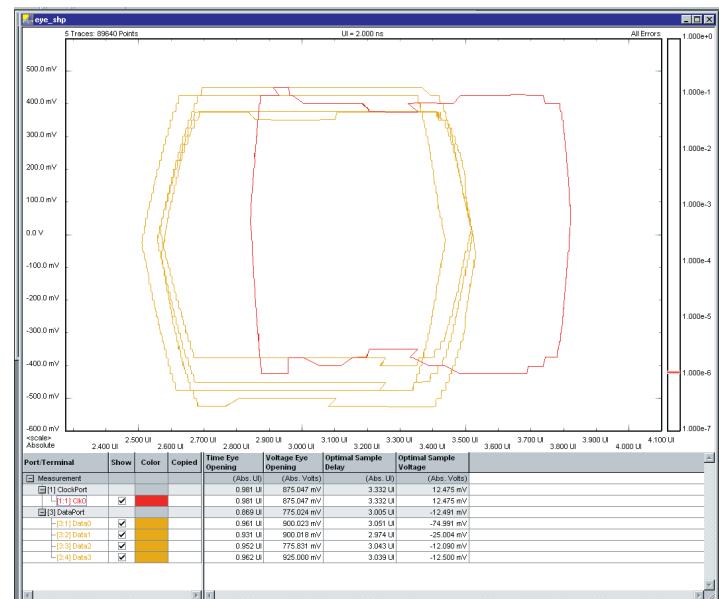

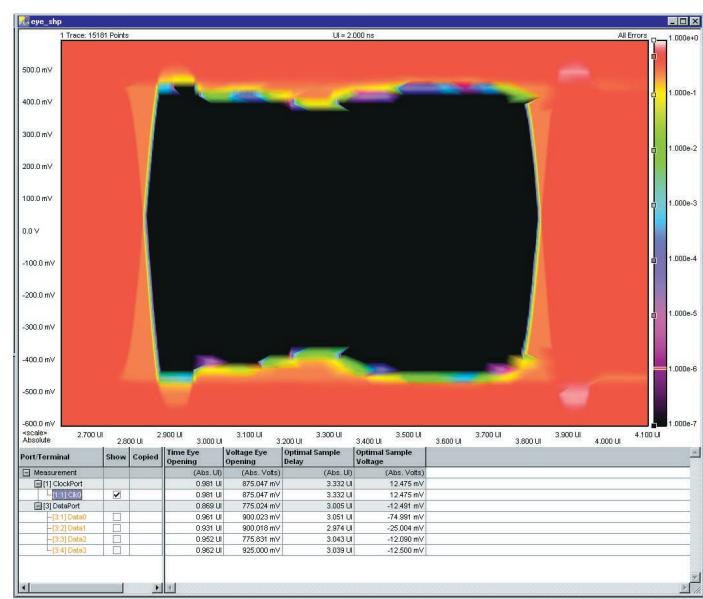

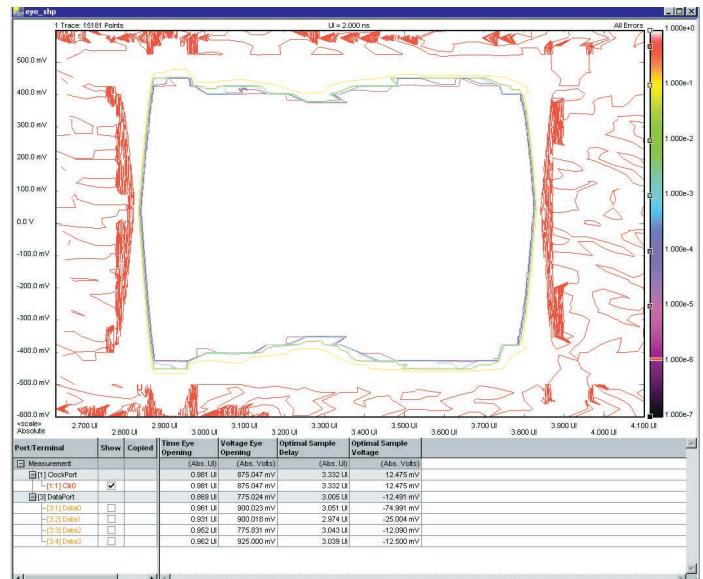

# アイ開口測定

アイ開口測定では、受信するチャネルのサンプリング遅延と電圧しきい値が掃引されます。

以下の測定結果が得られます。

- アイ開口特性(電圧およびタイミング)

- 最適なサンプリング・ポイント

表5：アイ開口測定

| 測定パラメータ | 最適サンプリング・ポイントの遅延<br>最適しきい値<br>アイ開口特性(電圧)<br>位相マージン |

|---------|----------------------------------------------------|

| 合否      | 全パラメータが対象<br>各パラメータは個別に<br>イネーブル可能                 |

| グラフ     | 2個のマーカ：電圧、<br>遅延、BER                               |

図12a/b/c：1つの端子のBERを色分けプロット、または区切り線プロット、またはBERしきい値における等価BERとして表示

## アプリケーション例

### ビデオ (DVI)、1:7 MUX/DEMUX

図13: ビデオ (DVI) の例

### ギガビット・イーサネット、1:10 MUX/DEMUX

図14: ギガビット・イーサネットの例

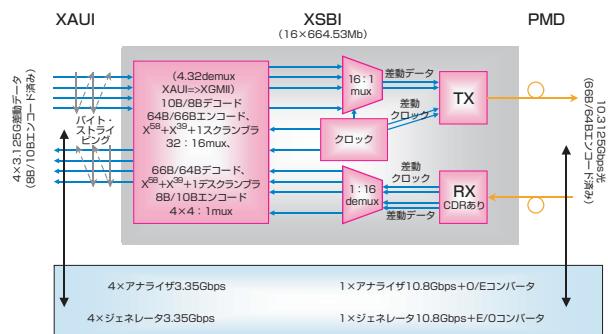

### 10GbE

図14a: 10GbE

### OC 192、1:16 MUX/DEMUX

図15: OC 192の例

### デジタル・ビデオ

CPUとディスプレイ間のデータ転送のために、デジタル・ビデオ・インターフェースが作成されました。ここに示す図は、シリアル相互接続(最大8)を使った単純な例です。これらのビデオ・インターフェースでは、MUX/DEMUX比1:7が一般的です。DUTは、TXとRXの2個のチップから成り、3個のシリアル・ラインとクロック・ラインがあります。

このデバイスで必要なチャネル数は、3つのMUX/DEMUXパスの1つをステイミュレートし、解析するために必要なチャネル数となります。この場合は合計で、675MHzジェネレータおよびアナライザが8個(クロック用に1個、データ用に7個)、およびシリアル・ラインに2.7Gbpsジェネレータおよびアナライザが1個必要です。

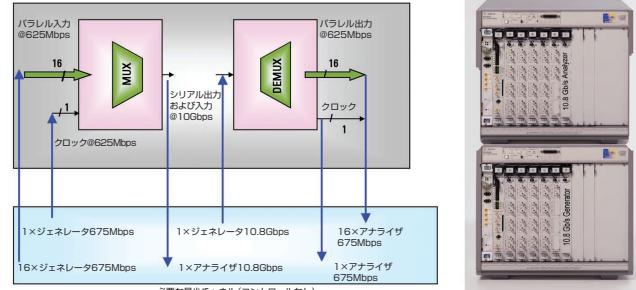

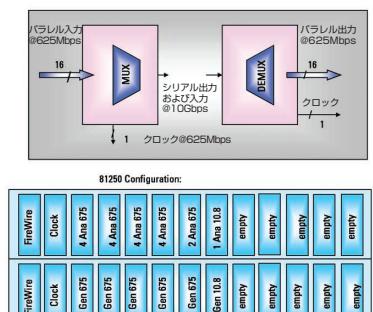

### ギガビット・イーサネット

ギガビット・イーサネット・トランシーバは、PCとローカル・ネットワーク間の物理トランシーバ・データを処理します。インプリメンテーションは、1つのTXと1つのRXを含む1個のチップから成ります。シリアル・ラインにクロックはありません(10ギガビット・イーサネットの場合、3.125Gbpsで動作する信号があります)。コントロール入力なしでこのデバイスをテストする場合、パラレル・ライン用に675Mbpsジェネレータおよび675MHzアナライザ・チャネルが11個(クロック用に1個、データ用に10個)必要です。シリアル・ライン用には、2.7Gbpsのジェネレータおよびアナライザが1個必要です。

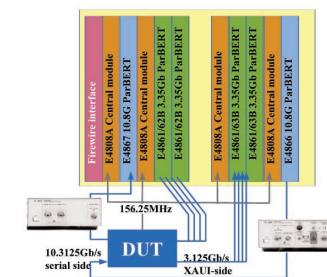

### 10GbE

10GbEは、メトロの領域で使用されます。DUTは、各モジュールに4つの3.125Gbps電気入力および出力、1つの10.3125Gbps光入力および出力を持つモジュールです。DUTにより、156.25MHzのクロックがシステムに供給されます。光信号は電気信号に変換されます。

### OC 192

OC 192はテレコム・アプリケーションで使用されます。ここでは、DUTは2個のチップ(1個のTXと1個のRX)から成ります。シリアル・ラインにクロックはありません。テストするには、パラレル・ライン用に16の675Mbpsジェネレータおよびアナライザが必要となります。シリアル・ライン用には、1個の10.8Gbpsジェネレータおよびアナライザが必要です。

## OC 768、1:4 MUX/DEMUX

図16: OC 768の例

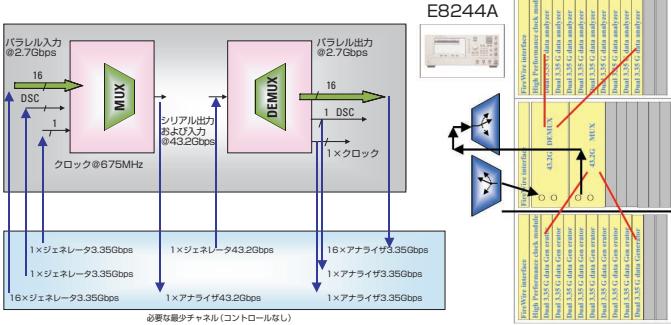

## OC 768、SF15 (1:17) MUX/DEMUX

ParBERT 3.35Gモジュール@パラレル付き

図16a: OC 768 SF15 Mux/DeMux

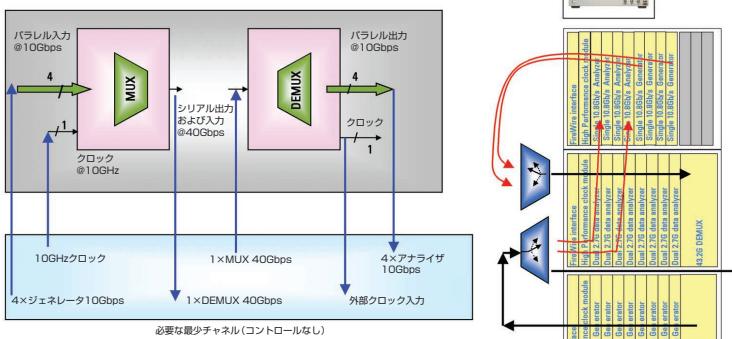

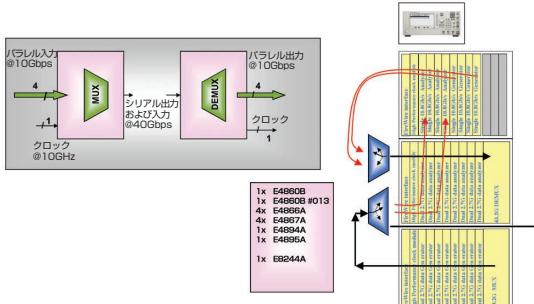

## OC 768、1:4 MUX/DEMUX比

DUTは、2個のチップ(1個のTXと1個のRX)からなります。シリアル・ラインにクロックはありません。テストには、パラレル・ライン用に4台の10.8Gbpsジェネレータおよびアライザ・チャネル、1台の43.2Gbpsジェネレータおよびエラー検出器バンドルE4894AとE4895Aが必要となります。

## OC 768、SF15(1:17) MUX/DEMUX

DUTは2つのパートからなり立ちます。TXおよびRXのパートです。SF15用の特性は17番目のビットでDSC信号と呼ばれます。この信号は指定されたタイミングでアライメント・データを搬送します。モジュール型ParBERT 81250のアーキテクチャは、17番目のジェネレータおよびアライザ・チャネルを容易に追加するだけでDSC信号にも対応できます。

## 信号の波形

以下の波形は、さまざまな速度のParBERTファミリから取得しています。

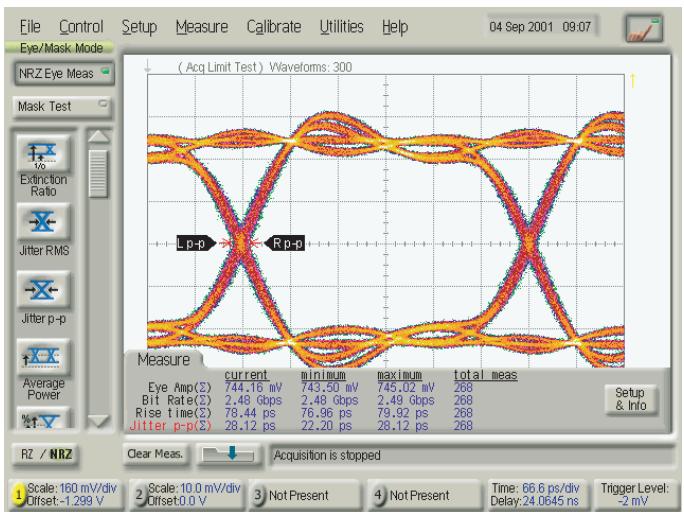

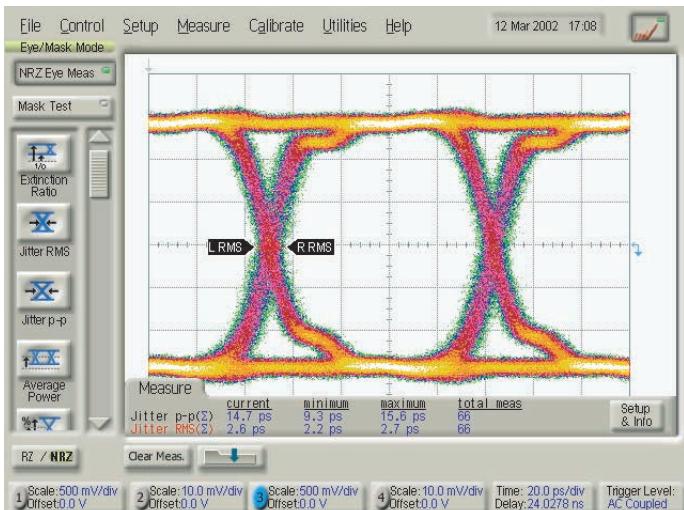

ここに示した図は、まずオシロスコープのジェネレータ出力、次にアライザ入力を理想信号源に接続し、アイ開口測定(9ページを参照)を使ってアライザの性能を記録したもので

### ParBERTの設定:

ジェネレータとアライザをシングル・エンド・モードに設定し、通常の入出力を使用

### 周波数:

以下には625Mbpsを使用:

E4808A+E4832A+E4838A+E4835A

以下には2.5Gbpsを使用:

E4808A+E4861A+E4862A+E4863A

以下には10.0Gbpsを使用:

E4808A+E4866A+E4867A

**データ: PRBS 2<sup>23</sup>-1 (ステイミュラスおよび予測) データ**

### ジェネレータ・レベル:

ロー・レベル-0.4V、ハイ・レベル+0.4V

### アライザ/アイの開口:

シングル・エンド、GRDに終端

比較ビット10<sup>6</sup>

BERしきい値 10<sup>-3</sup>

**トリガ出力: クロック・モード (625MHz)、レベル0/1V**

### オシロスコープの設定:

Agilent 81600 DCA、83484A 50GHzモジュール装備

- 1m SMAケーブルで接続

- 81250トリガ出力による外部トリガ

- 自動スケールによる信号調整

- 300イベントの全測定

### 理想信号源:

675、2.7G、3.35Gを使用の場合

遷移時間 30ps

ジッタ <10ps pp、レベル-0.5V/0V

### 10.8Gを使用の場合:

遷移時間10ps

ジッタ <8ps pp、レベル±0.4V

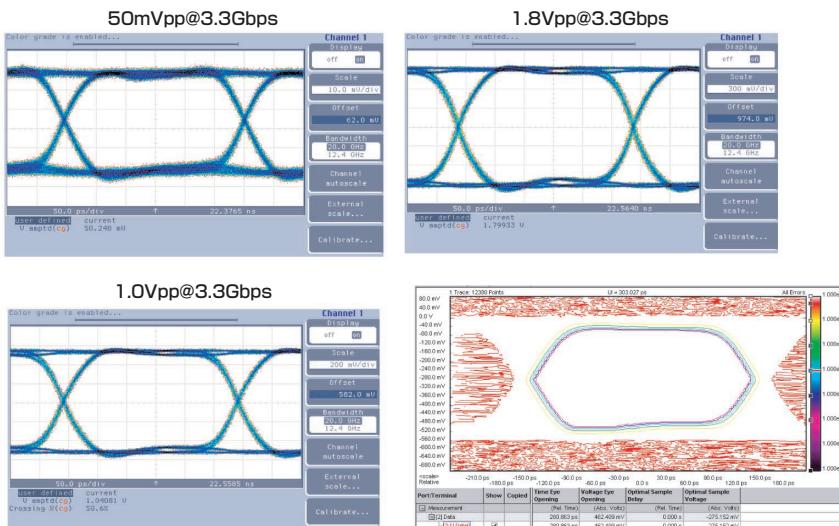

## アイ・ダイアグラム(3.3Gbpsモジュール：E4861B/E4862B/E4863B)

3.35ジェネレータ出力は、クリーンで高速な信号を出力できるように設計されています。電圧ウインドウ上に50mV～1.8Vの振幅が表示され、LVDS、CML、(P) ECLおよびSSTL-2のテストに適しています。

E4863Bアナライザでのアイ開口測定にはE4862Bジェネレータが必要です。

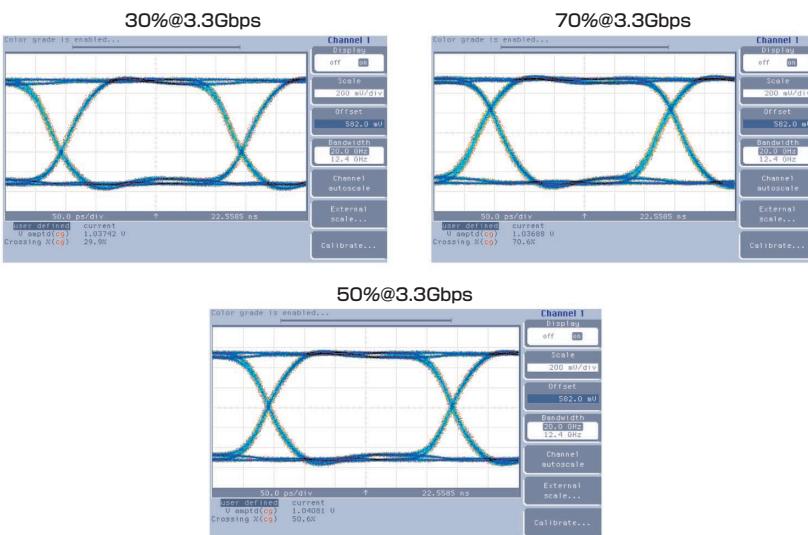

## クロス・ポイント可変(3.3Gbpsモジュール：E4861B/E4862B/E4863B)

3.35ジェネレータにより、差動信号のクロスオーバーを変更できます。クロスオーバーは、ユーザ・インターフェースまたはリモート・プログラムにより30～70%の範囲でプログラム可能です。

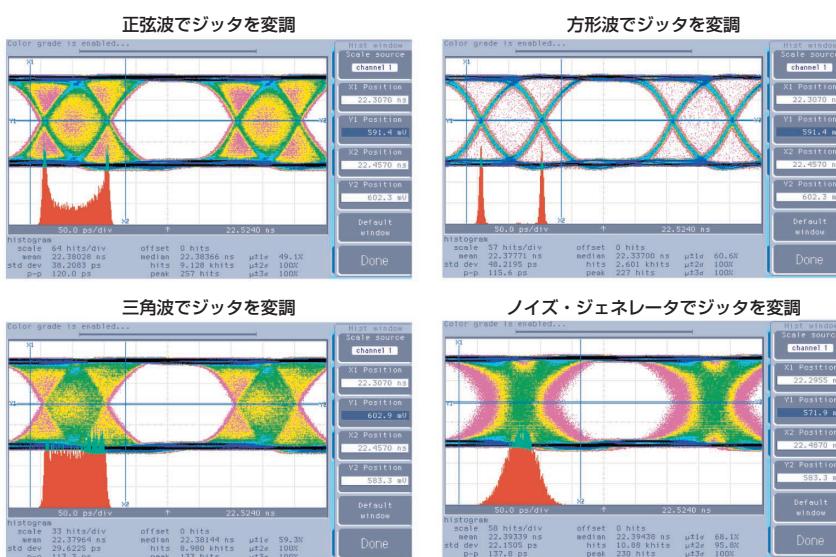

## ジッタ変調(3.3Gbpsモジュール：E4861B/E4862B/E4863B)

3.35Gジェネレータには、外部信号により遅延を変調するための制御入力が用意されています。

この変調によりジッタのエミュレーションが可能です。左の図にはタイプが異なる電圧制御における変調が示されています。この変調を利用してDUTをテストすれば、ジッタの許容値を求めるることができます。

図17a) b) : 675MHzモジュールの信号波形(E4838A/E4835A/E4832A)

図18a) b) : 1.65Gbpsモジュールの信号波形(E4862A/E4863A/E4861A)

図19a) b) : 10.8Gbpsモジュール(N4869A併用)の信号波形(E4866A/E4867A)

# 仕様

ここに示す仕様は、機器の保証される性能を表します。保証されない値は、代表値として示します。すべての仕様は、特に記載がない限り、周囲温度10°C~40°C、30分間のウォームアップ後、ECLレベルで出力と入力をグランドに対して50Ωで終端した状態で有効です。

## 3.35Gbps E4861B (E4862B/E4863B)

表6:E4861Bデータ・ジェネレータのタイミング仕様(50%振幅、GNDに対して50Ω)

|                   |                                                         |

|-------------------|---------------------------------------------------------|

| 周波数レンジ            | 20.834MHz~3.350GHz                                      |

| 遅延=開始遅延+ファイン遅延    | 立上がりエッジの遅延として各チャネルでビットの分数で指定可能                          |

| 開始遅延レンジ           | 0~200ns (周期による制限なし)                                     |

| ファイン遅延レンジ         | ±1周期 (停止なしで変更可能)                                        |

| 遅延分解能             | 1ps                                                     |

| 確度(データ・モード)       | ±25ps±50ppm、0遅延位置を基準、自動校正後±10°Cの温度変化                    |

| 確度(クロック・モード)      | ±50ps±50ppm、0遅延位置を基準                                    |

| 同種モジュール間のスキュー     | 50ps(代表値)、カスタマ・レベルでのスキュー補正後、(データ・モード) システム周波数の変化なし      |

| データ・モードおよびパルス・モード | データ・モードおよびパルス・モードで遅延時間を変更できます。クロック・モードでのタイミングは固定されています。 |

表7:E4861Bアナライザのタイミング機能

タイミング・パラメータはすべてECLレベルで測定、GNDに対して50Ωで終端

|            |                    |

|------------|--------------------|

| サンプリング・レート | ジェネレータと同じ          |

| サンプル遅延     | サンプル遅延=開始遅延+ファイン遅延 |

| 開始遅延レンジ    | ジェネレータと同じ          |

| ファイン遅延レンジ  | ジェネレータと同じ          |

| 分解能        | ジェネレータと同じ          |

| 確度         | ジェネレータと同じ          |

| スキュー       | ジェネレータと同じ          |

表8:E4861Bパターン機能およびシーケンス機能

### パターン:

|              |                                                                |

|--------------|----------------------------------------------------------------|

| メモリ・ベース      | 最大16Mビット(表9を参照)                                                |

| PRBS/PRWS    |                                                                |

| マーク密度        | 2 <sup>n</sup> -1, n=7, 9, 10, 11, 15, 23, 31                  |

| エラーPRBS/PRWS | 2 <sup>n</sup> -1, n=7, 9, 10, 11, 15で、1/8, 1/4, 1/2, 3/4, 7/8 |

| 拡張1または0      | 2 <sup>n</sup> -1, n=7, 9, 10, 11, 15                          |

| クロック・パターン    | 2 <sup>n</sup> -1, n=7, 9, 10, 11, 15                          |

| ユーザ          | 1, 2, 4により除算または乗算                                              |

### アナライザの自動同期

|                    |                                                                                                                      |

|--------------------|----------------------------------------------------------------------------------------------------------------------|

| PRBSまたはメモリ・ベース・データ | PRBSまたはメモリ・ベース・データに対して手動または自動:                                                                                       |

|                    | ビット同期*、自動位相アライメントありまたはなし<br>スタート・サンプル遅延付近での自動遅延アライメント<br>(レンジ: ±50ns)<br>BERしきい値: 10 <sup>-4</sup> ~10 <sup>-9</sup> |

PRBSデータにより、アナライザはPRBSデータ・ビットに自動的に同期できます。メモリ・ベース・データを使用する際には、このデータ中に、セグメントの先頭の48ビットのユニークな検出ワードが含まれていなければなりません。またジェネレータは個別のシステム・クロック上に配置される必要があります。検出ワード内では、任意のビットが可能です。複数の入力を同期する場合、端子間の遅延差は±5セグメント長以下であることが必要です。

表8a

|         |                            |

|---------|----------------------------|

| セグメント数  | 120ループ数                    |

| ループ・レベル | 2                          |

| ループ長    | (2~2 <sup>20</sup> ) *MUX値 |

## 一般情報

ParBERT3.35Gモジュールは、ジェネレータ2個、アナライザ2個、あるいはそれぞれが1個ずつの合計2個のフロントエンドを収納できます。

ParBERT 3.35Gモジュールは、クロック・モジュールE4808Aと組み合わせることにより動作します。クロック・モジュールE4805Bとは組み合わせないでください。次に、ParBERT 3.35Gの主な仕様を示します。

- 21MHz~3.350GHzクロック/データ・レート

- チャネル当たり16Mビットのメモリ長

- 最大2<sup>31</sup>-1のHWベースのPRBSの生成

- 48ビットの検出ワード(メモリ・ベースのデータ)に対してアナライザは同期可能

- 検出ワードなしで、純粋なPRBSパターンに対してアナライザは同期可能

## タイミング仕様

モジュールの周波数レンジは、21MHz~3.350GHzです。ParBERT 3.35Gフロントエンドは周波数倍PLLを使用して、システムのマスター・クロックを4倍または8倍のクロック周波数にします。クロック・モジュールでは、外部クロック・ソースを使用できます。外部クロックは、連続して動作する必要があります。クロック信号に割り込みがかかる場合、周波数倍PLLは、クロックを再度ロック・オンするために通常100msかかります。

## シーケンス機能

シーケンサはクロック・モジュールから命令を受け取ります。チャネル・シーケンサは最大120セグメントで構成されるシーケンスを発生できます。シーケンサには2つのループ・レベルがあり、ネスト・ループにも対応しています。アナライザ・チャネルは、すべてのパラレル・チャネルが共通に反応するためにクロック・モジュール内で組み合わせられるフィードバック信号を発生することができます。受信チャネルが1つの場合は、チャネル・シーケンサ自体がフィードバック信号を処理します。

表9：データ・レート・レンジ、セグメント長分解能、同期およびファイン遅延動作で利用可能なメモリ

| データ・レート・レンジ、Mbps | セグメント長分解能 | 最大メモリ長、ビット |

|------------------|-----------|------------|

| 20.834~41.666    | 1ビット      | 131,072    |

| 20.834~82.333    | 2ビット      | 262,144    |

| 20.834~166.666   | 4ビット      | 524,288    |

| 20.834~333.333   | 8ビット      | 1,048,576  |

| 20.834~666.666   | 16ビット     | 2,097,152  |

| 20.834~1,333.333 | 32ビット     | 4,194,304  |

| 20.834~2,700.000 | 64ビット     | 8,388,608  |

| 20.834~3,350.000 | 128ビット    | 16,777,216 |

表10：PRWSの生成とポート幅の依存関係

以下の組み合わせを除いて、ほとんどの組み合わせが可能

| PRWS       | ポート幅       |

|------------|------------|

| $2^7-1$    | 制限なし       |

| $2^9-1$    | 7          |

| $2^{10}-1$ | 3、11、31、33 |

| $2^{11}-1$ | 23         |

| $2^{15}-1$ | 7、31       |

| $2^{23}-1$ | 47         |

| $2^{31}-1$ | 制限なし       |

表11：ジェネレータ・フロントエンドE4862B 3.350Gbpsのパラメータ

|                              |                             |

|------------------------------|-----------------------------|

| 出力                           | 1、差動またはシングルエンド              |

| インピーダンス                      | 50Ω (代表値)                   |

| データ・フォーマット                   | データ：NRZ、DNRZ、RZ、R1          |

| パルス・モード                      |                             |

| レンジ                          | 150ps~(1UI-150ps)           |

| 分解能                          | 1ps                         |

| 幅確度                          | 40ps (代表値)                  |

| 出力電圧ウィンドウ                    | -2.00~+3.00V                |

| 絶対最大外部電圧                     | -2.2V~+3.2V                 |

| 外部終端電圧                       | -2V~+3V                     |

| 対応ロジック信号                     | LVD、SCM、PECL、ECL<br>低電圧CMOS |

| 振幅/分解能                       | 0.05Vpp~1.8Vpp/10mV         |

| 確度ハイレベル/振幅                   | ±2%±10mV                    |

| ショート回路電流                     | 72mA (最大値)                  |

| 遷移時間(20%~80%)                | <75ps、60ps (代表値)            |

| オーバーシュート/リンギング               | 5%+10mV (代表値)               |

| ジッタ、NRZデータ・モード               | <30ps ピークツーピーク              |

| クロック・モード                     | <2ps rms                    |

| パルス、RZ、R1モード                 | 30ps ピークツーピーク (代表値)         |

| クロスポイント調整<br>(デューティ・サイクルの歪み) | 30%~70% (NRZモード)            |

(1) E4808A クロック・モジュールで測定

## パターン・ジェネレーション機能

データ・ストリームはセグメントで構成されています。セグメントは、メモリ・ベースのパターン、メモリ・ベースのPRBS、または、ハードウェアPRBSです。メモリ・ベースのパターンとメモリ・ベースのPRBSを発生するために、合計で16Mビット(128ビットのセグメント長分解能で)を使用できます。

メモリ・ベースのPRBSは、 $2^{15}-1$ 以下に制限されます。メモリ・ベースのPRBSは、ゼロ代用(拡張ゼロ・ラン)のような特別なPRBSモードと可変マーク比が可能です。ゼロ代用パターンは、ユーザが選択可能な追加のゼロの数により、最長ゼロ列を拡張します。ゼロ列に続く次のビットは必ず1になります。マーク比は、PRBS列での1の列と0の列の比です。通常のPRBS列では、マーク比は1/2です。マーク比は、1/8、1/4、1/2、3/4、7/8にすることができます。メモリ分解能のために、PRBSはRAMに数回、128の倍数の因子で、書き込まれる必要があります。また、繰り返し回数も128回です。つまり、 $2^{15}-1$  PRBSでは最大4Mビットのメモリを使用します。

ハードウェア・ベースのPRBSでは、任意の多項式で最大 $2^{31}-1$ になります。メモリを使用しないため、メモリ・ベースのパターン・ジェネレーション用のメモリはフリーとなります。エラー挿入機能により、1つまたは複数のエラーをデータ列に挿入できます。エラーでは、ビットについて反転を行います。つまり、「0」であれば「1」に、「1」であれば「0」に置き換えます。単一エラーは、Pにより、またはセントラル・シーケンサからの命令を使って挿入します。セントラル・モジュールのクロリファイア・ポッドに提供される信号を使ってエラーにトリガをかけることができます。固定レートと固定分布のエラー挿入機能がサポートされています。ユーザ・ソフトウェアでは、エラー・セグメントとエラーフリー・セグメントを選択できます。

## ジェネレータ・フロント・エンド(E4862B)：

增幅器は差動出力信号を発生します。各出力は個別にオンとオフに切り換えることができます。ECL、LVPECL、LVDSのようなインターフェースを持つ一般的な高速デバイスをドライブできる十分な出力レベルがあります。公称出力インピーダンスは50Ωです。遅延制御入力は、50Ωインピーダンスのシングル・エンド入力です。入力電圧はジェネレータの差動出力内の遅延素子を変調します。遅延制御入力の機能はオンまたはオフに選択できます。さらに、2つの遅延レンジを選択できます。

**表12：遅延制御入力**

|           |                      |

|-----------|----------------------|

| 入力電圧ウィンドウ | −500mV～+500mV (DC結合) |

| 遅延レンジ1    | −250ps～+250ps        |

| 遅延レンジ2    | −25ps～+25ps          |

| 変調帯域幅     | DC～200MHz            |

| 入力インピーダンス | 50Ω (代表値)            |

**表13：アナライザ・フロントエンドE4863B 3.350Gサンプル/秒のパラメータ**

|                    |                                         |

|--------------------|-----------------------------------------|

| チャネル数              | 1、差動またはシングルエンド                          |

| インピーダンス            | 50Ω (代表値)<br>(終端電圧をオフにした場合は100Ω差動)      |

| 内部終端電圧(オフ可能)       | −2.0～+3.0V                              |

| しきい値電圧範囲           | −2.0～+3.0V                              |

| しきい値分解能            | 1mV                                     |

| しきい値確度             | ±20mV±1%                                |

| 入力感度(シングルエンドおよび差動) | <50mV                                   |

| 最小検出可能パルス幅         | <150ps                                  |

| 最小入力電圧レンジ          | 3レンジ選択可能<br>−2V～+1V<br>−1V～+2V<br>0V～3V |

| 最大差動電圧             | 1.8V                                    |

| 位相マージン、理想入力信号使用時   | >1UI−30ps (1)                           |

| 位相マージン、E4862B      | >1UI−50ps (1)                           |

| ジェネレータ使用時          |                                         |

| 補助出力               | Vout: 350mVpp (代表値)、AC結合 (2)            |

(1) E4808Aセントラル・モジュールで計測

(2) 使用しない場合、GNDに対して50Ωで終端

**アナライザ・フロントエンド

(E4863B) :**

次に、アナライザの機能を示します。

- スタートからのデータ収集

- エラー周辺のデータの比較と収集

- 間違った1と0の比較とカウントによるBERの計算。収集データ用の受信メモリは、セグメント長分解能に依存しますが、最大で16Mビット長です。チャネルのステイミュラス部は、期待値データとマスク・データを発生します。マスク・データは、最大メモリ分解能で使用可能です。

アナライザは、ユーザ定義の検出ワードを使用して受信したデータ列に同期することができます。検出ワードは、期待値セグメント内の最初の数ビットで定義され、長さは48ビットあり、0、1、X(ドント・ケア)で構成されます。検出ワードは、データ列内で一意であることが必要です。純粋なPRBSデータ列に対しては、内部のPRBSジェネレータに入力されるビット数を単にロードすることにより、検出ワードを使わずに同期をとります。このためには、受信するPRBSの多項式を予め知っておく必要があります。

入力コンパレータは、50Ωインピーダンスの差動入力です。50mVの最大入力感度とコンパレータのコモン・モード・レンジにより、あらゆる一般的な差動高速デバイスを試験することができます。ユーザは、終端電圧をオンまたはオフに切り換えて差動入力またはシングル・エンド入力(終端電圧をオン)を選択します。差動入力モードではしきい値電圧は必要ありませんが、シングル・エンドではしきい値電圧は必要です。また、差動入力モードでは、2入力の内1つを選択して、その信号をしきい値電圧と比較することができます。

**保護**

絶対最大電圧ウィンドウを超えると、入力および出力リレーはオフに自動的に切り替ります。

## 10.8Gbps (E4866A/N4868Aブースタ/E4867A)

### E4866Aジェネレータ・モジュール

表14: E4866Aのタイミング仕様(50%振幅、GNDに対して50Ω)

|               |                                          |

|---------------|------------------------------------------|

| データ・レンジ       | 9.5Gbps~10.8Gbps                         |

| クロック・レンジ      | 9.5GHz~10.8GHz                           |

| 遅延レンジ         | 0~300ns                                  |

| 遅延分解能         | 1ps                                      |

| 確度            | ±20ps±50ppm、0遅延位置を基準                     |

| 同種モジュール間のスキュー | 50ps(代表値)、カスタマ・レベルでのスキュー補正後、システム周波数の変化なし |

表15: E4866Aのパターン機能とシーケンス機能

|              |                                                                       |

|--------------|-----------------------------------------------------------------------|

| セグメント長分解能    | 256ビット                                                                |

| パターン:        |                                                                       |

| メモリ・ベース      | 最大33,554,432ビット                                                       |

| PRBS/PRWS    | $2^n - 1$ , n=7, 9, 10, 11, 15, 23, 31                                |

| マーカ密度        | $2^n - 1$ , n=7, 9, 10, 11, 15で $1/8$ , $1/4$ , $1/2$ , $3/4$ , $7/8$ |

| エラーPRBS/PRWS | $2^n - 1$ , n=7, 9, 10, 11, 15                                        |

| 拡張1または0      | $2^n - 1$ , n=7, 9, 10, 11, 15                                        |

| クロック・パターン    | 1, 2, 4による除算または乗算                                                     |

表16: クロック出力E4866A 10.8GHzのパラメータ

|               |                             |

|---------------|-----------------------------|

| 出力            | 1、シングル・エンド、AC結合、50Ωに終端させて使用 |

| デューティ・サイクル    | 50% (代表値)                   |

| 最大外部電圧        | -2.2V~+3.3V                 |

| 振幅/分解能        | 0.5Vpp固定(代表値)               |

| 遷移時間(20%~80%) | 正弦波                         |

| クロック・ジッタ      | <2ps RMS                    |

| 表17: データ出力E4866A 10.8Gbpsのパラメータ |                | N4868Aブースタ使用時    |

|---------------------------------|----------------|------------------|

| 出力                              | 1、差動、50Ω (代表値) | 1、差動または2、シングルエンド |

| データ・フォーマット                      | NRZ            | NRZ              |

| 振幅/分解能                          | 0.3V~1.8V/10mV | 0.5~2V           |

| 確度ハイレベル/振幅                      | ±2%±10mV       | tbd              |

| 外部端子電圧                          | -2V~+1.5V      |                  |

| 出力電圧ウィンドウ                       | -2.0~+2.7V     | AC結合             |

| 最大外部電圧                          | -2.2V~+3.3V    |                  |

| イネーブル/ディスエーブル                   | リレー            | —                |

| 遷移時間(20%~80%)                   | <60ps          | <20ps*           |

| オーバシュート/リンギング                   | 10%+20mV (代表値) | tbd              |

| ジッタ                             | <25ps ピークツーピーク | 同                |

\* ブースタ入力はE4866Aジェネレータから1.8Vの振幅でドライブ

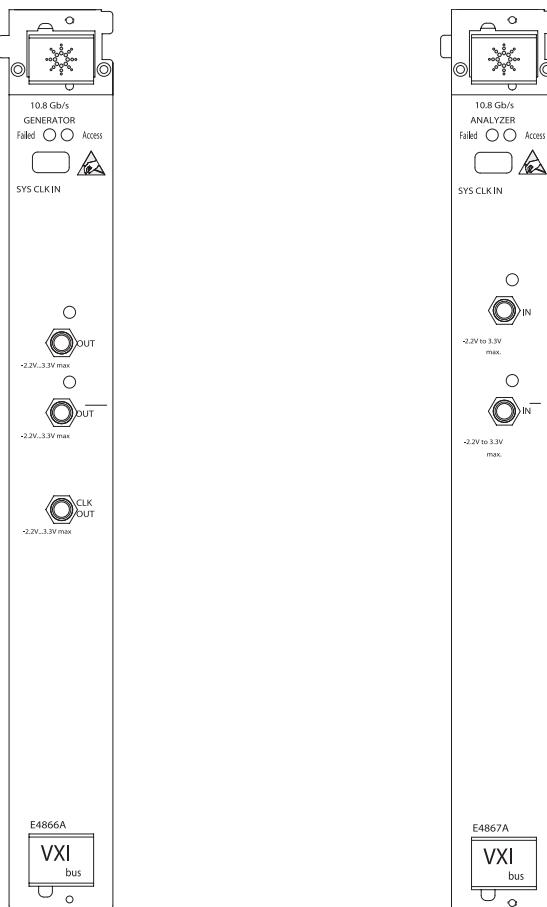

### E4866A/E4867A

10.8Gbpsモジュールには、ジェネレータ・モジュールとしてE4866A、アナライザ・モジュールとしてE4867Aがあります。N4868AはE4866Aジェネレータ用のブースタ・モジュールです。

### クロック・タイミング

ジェネレータは、相補データおよびシングル・エンド・クロック出力を提供します(詳細については、表7/8を参照してください)。クロック出力とデータ出力の両方を遅延できますが、両方の遅延は同じです。アナライザには、サンプリング遅延調整もあります。これは、2つの異なる遅延調整から成り、1つは、1周期以上の調整レンジを持つ開始遅延と、もう1つは±1周期以内のファイン遅延調整です。

### データ機能

PRBS/PRWSとメモリ・ベースのデータは、セグメントによって定義されます。セグメントは、ジェネレータ・モジュールではパターン生成のために用いられ、アナライザ・モジュールでは予測パターンを定義するために用いられます。予測パターンは、マスク・ビットを使って定義できます。セグメント長分解能は、パターン・セグメントの長さを設定する際の分解能です。全体で32Mメモリの場合、セグメント長分解能は256ビットです。

### サンプル回路でのAC結合

AC結合は、入力データが平衡、または以下に示す制限事項を超えない限り、アナライザの性能に影響することはありません。

- 無限の時間周期でのマーク密度の許容値は9/10~10/9

- すべて0またはすべて1のパターンは、20000ビットまたは $2\mu\text{s}$ 以下

- データが不均衡パターンから均衡パターンへ回復する場合、セッティング時間は $200\mu\text{s}$ (最大値)で有効(続)

## E4867Aアナライザ・モジュール

表18:E4867Aのタイミング仕様(50%振幅、GNDに対して50Ω)

|              |                                                            |

|--------------|------------------------------------------------------------|

| データ・レンジ      | 9.5Gbps~10.8Gbps                                           |

| 遅延(チャネル間)    | 立上がりエッジの遅延(開始遅延)として、各チャネルでビットの分数で指定可能。測定器を停止せずにファイン遅延を変更可能 |

| 開始遅延レンジ      | 0~300ns(周期による制限なし)                                         |

| ファイン遅延レンジ    | ±1周期(停止なし)                                                 |

| 分解能          | 1ps                                                        |

| 確度           | ±20ps±50ppm、0遅延位置を基準                                       |

| 同種モジュール間のスキー | 50ps(代表値)、カスタマ・レベルでのスキー補正後、システム周波数の変化なし                    |

図19c:E4867Aアナライザの内部AC結合

表19:E4867Aのパターン機能とシーケンス機能

|                    |                                                                                                                            |

|--------------------|----------------------------------------------------------------------------------------------------------------------------|

| セグメント長分解能          | 256ビット                                                                                                                     |

| パターン:              |                                                                                                                            |

| メモリ・ベース            | 最大33,554,432                                                                                                               |

| PRBS/PRWS          | $2^n-1$ , $n=7, 9, 10, 11, 15, 23, 31$                                                                                     |

| マーカ密度              | $2^n-1$ , $n=7, 9, 10, 11, 15$ で $1/8, 1/4, 1/2, 3/4, 7/8$                                                                 |

| エラーPRBS/PRWS       | $2^n-1$ , $n=7, 9, 10, 11, 15$                                                                                             |

| 拡張1または0            | $2^n-1$ , $n=7, 9, 10, 11, 15$                                                                                             |

| ユーザ                | データ・エディタ、ファイル・インポート                                                                                                        |

| アナライザ予測データ         |                                                                                                                            |

| マーク密度              | 9/10~10/9                                                                                                                  |

| 連續0または1の最大値        | 20000または $2\mu s$                                                                                                          |

| 不均衡パターンからのデータ・リカバリ | $200\mu s$                                                                                                                 |

| アナライザの自動同期         | PRBSまたはメモリ・ベース・データに対して手動または自動:<br>ビット同期*、自動位相アライメントありまたはなし<br>スタート・サンプル遅延付近での自動遅延アライメント<br>BERしきい値: $10^{-4} \sim 10^{-9}$ |

\* データ上のビット同期は、セグメントの先頭で48ビットのユニーク・ワードを検出することを行われます(検出ワード内では、任意のビットが可能です)。本モードでは、同一システム内でのメモリ・ベース・データの送信は不可です。複数の入力と、端子間の遅延差を同期させる場合は、±5セグメント長分解能以下であることが必要です。

一般的にはシーケンスの開始時には常にAC結合を考慮する必要があります。

結果を無効にせずAC結合を実行するには2つの方法があります。

1. 仕様に適合する均衡パターンに付随される同期機能(ビット同期、または自動遅延アライメント)を可能な限り使用してください。この場合、シーケンスの開始後にリカバリ時間は必要ありません。

2. 同期が実行できない場合、プリアンブルを使用してください。データ・セグメント長は指定したセッティング時間に対応させます。プリアンブルのパターンは、以下に示すデータ・セグメントと同様に、許容範囲の不均衡の最大値(9/10~10/9)を超えてはいけません。

### 同期

同期は、入力ビット・ストリーム上でデータを比較するためにビット位相を自動的に調整する手法です。

同期は、PRBS/PRWSでもメモリ・ベース・データでも実行できます(ただし、PRxSとメモリ・ベース・データが混在する場合は実行できません)。以下2種類の同期があります。

- ビット同期

- 自動遅延アライメント

ビット同期の場合、サイクル数が不明でもビット・アライメントをカバーできます。メモリ・ベースのデータを使用すると、予測データ・セグメント内の最初の48ビットは、入力データと比較する検出ワードとして機能します。入力データがこの検出ワードと一致すると、さらなる解析がスタートします。

自動遅延アライメントは、アナライザのサンプリング遅延を使って実行します。このためレンジが制限され、レンジが10nsである可能性があります。自動遅延アライメントを使用すると、グループのアナライザ・チャネル間で絶対タイミング関係を持つ同期が得られます。したがって、スキー測定が可能です。

## 入出力

対応ロジック信号：

CML、SSTL-2、ECL(0V/-2Vに終端)、

LVPECL (1.3Vに終端)

### ジェネレータ出力

ジェネレータ出力はシングル・エンドまたは差動で使用できます。リレーのイネーブル/ディスエーブルによってオン/オフを切り替えます。スイッチ・オフの場合、内部で終端されます。未使用出力はオフにするか、外部で終端することをお勧めします。

ジェネレータ出力は50Ωセンタ・タップ終端または100Ω差動終端で動作できます。

適切な終端をエディタで選択し、適切なレベルに適合させることができます。

### アナライザ入力

アナライザ入力では、90%以上のアイ開口測定に理想的な入力信号を提供できます。(遷移時間10ps) 特性試験で優れた性能を発揮します。

アナライザ・チャネルは以下のモードで動作します。

- シングル・エンド・ノーマル

- シングル・エンド・コンプリメント

- 差動

終端のため、常に50Ωが接続されています。差動モードでは、さらに100Ω差動終端も選択可能です。終端の選択とは別に、入力信号の解析を入力で実施するか、補助入力で実施するか、真に差動的に実施するかを選択できます。

### ブースタN4868A

N4868Aには、1つの差動チャネルまたは2つのシングルエンド・チャネルが用意されています。N4868A-001には、2つの差動チャネルまたは4つのシングルエンド・チャネルが用意されています。差動動作では、N4869Aケーブルキットと差動バス用の位相調整機能との併用を推奨します。N4868A-001では、両方の差動チャネルを使用する場合、2つのケーブル・キットが必要です。N4868A-001では、1つの差動および2つのシングルエンド・チャネルを使用して、差動データとは別にE4866Aのクロック出力をブーストすることも可能です。

表20：アナライザ・モジュールE4867A 10.8Gbpsのパラメータ

|                          |                                    |

|--------------------------|------------------------------------|

| 入力                       | 1、差動またはシングルエンド                     |

| インピーダンス                  | 50Ω (代表値)<br>(終端電圧をオフにした場合は100Ω差動) |

| 入力感度                     | 100mV (代表値)、シングルエンドおよび差動           |

| 内部終端電圧                   | -2.0～+2.0V (オフ可能)                  |

| しきい値電圧範囲                 | -2.0～+2.0V                         |

| しきい値分解能                  | 1mV                                |

| しきい値確度                   | ±2% ±20mV                          |

| 最大入力電圧レンジ                | 3レンジ選択可能： -2V～+0V、 -1V～+1V、 0V～2V  |

| 最大差動電圧                   | 1.2V                               |

| イネーブル/ディスエーブル            | リレー                                |

| 帯域幅、遷移時間に同等<br>(20%～80%) | 35ps (代表値)                         |

| 最小検出可能                   | データ：80ps (代表値)                     |

| パルス幅                     | 連続クロック：40ps (代表値)                  |

| 位相マージン、理想入力信号使用時         | >1UI-15ps                          |

| E4866Aジェネレータ使用時          | >1UI-33ps                          |

図20：E4866A/E4867Aモジュール

# 1.65Gbps/2.7Gbps

## E4861Aジェネレータ／アナライザ・モジュール

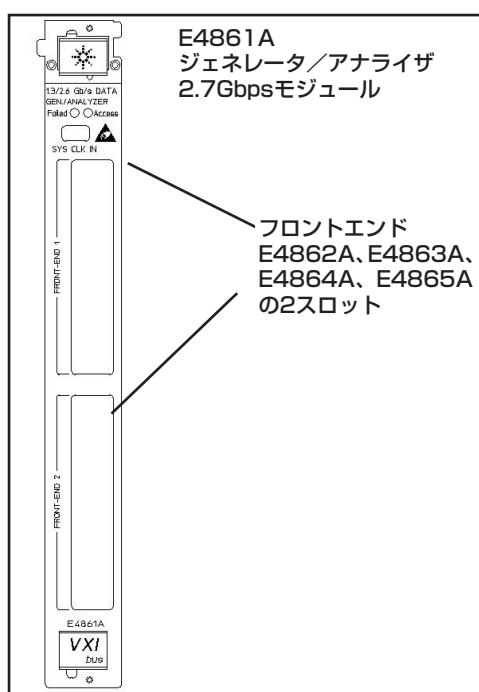

このモジュールには、アナライザ・フロントエンド(E4863A、E4865A)とジェネレータ・フロントエンド(E4862A、E4864A)を最大2台収容できます。

フロントエンドE4864AおよびE4865Aを使用する場合、最大速度は1.65GHz/Gbpsに制限されます。2.70GHz/Gbpsの最大速度は、フロントエンドE4862AおよびE4863Aを使用すると実現されます。

## クロック・モジュール／データ・モード

ジェネレータは、クロック・モードまたはデータ・モードで動作できます。クロック・モードにするには、ジェネレータをパルス・ポートとして割り当てます。データ・モードにするには、ジェネレータをデータ・ポートとして使用します。クロック・モードでは、デューティ・サイクルが50%に固定されます。データ・モードでは、可変遅延を持つNRZフォーマットとなります。アナライザは、常に可変サンプリング遅延を持つデータ・ポートとして機能します。サンプリング遅延は、2つの要素、開始遅延とファイン遅延からなります。ファイン遅延は、測定を停止せずに±1周期内で変更できます。

## データ機能

PRBS/PRWSとメモリ・ベースのデータは、セグメントによって定義されます。セグメントは、ジェネレータ・モジュールではパターン生成のために用いられ、アナライザ・モジュールでは予測パターンを定義するために用いられます。予測パターンは、マスク・ビットを使って定義できます。

セグメント長分解能は、パターン・セグメントの長さまたはマスクを設定する際の分解能です。E4861Aのチャネルあたりの最大メモリは、64ビット・ステップで8192Kビットまで設定できます。64ビットのセグメント長分解能が粗過ぎる場合、メモリ長と周波数を表17に示すようにトレードオフできます。

表21：E4861Aデータ・ジェネレータのタイミング仕様

(50%振幅、GNDに対して50Ω)

|               |                                                                                              |

|---------------|----------------------------------------------------------------------------------------------|

| 周波数レンジ*       | クロック／データ・モード333.334MHz/Mbps～2.70GHz<br>(1.65Gbps、E4864A/E4865A)                              |

| 遅延(チャネル間)     | 立上がりエッジの遅延として、各チャネルでビットの<br>分數で指定可能                                                          |

| レンジ           | 0～300ns(周期による制限なし)                                                                           |

| 分解能           | 1ps                                                                                          |

| 確度            | ±50ps±50ppm、0遅延位置を基準<br>(20°C～35°C、自動校正なし)<br>±30ps±50ppm(代表値)、0遅延位置を基準、<br>自動校正後±5°C以内の温度変化 |

| 同種モジュール間のスキュー | 50ps(代表値)、カスタマ・レベルでのスキュー補正後、<br>システム周波数の変化なし                                                 |

| パルス幅          | クロック・モードで周期の50%(代表値)                                                                         |

\* フロントエンドのディレーティングについては表を参照してください。

表22：E4861Aアナライザのタイミング。すべてのタイミング・パラメータはECLおよびレベルで測定。GNDに対して50Ω終端

|                       |           |

|-----------------------|-----------|

| サンプリング遅延：=開始遅延+ファイン遅延 |           |

| 測定器を停止せずにファイン遅延を変更可能  |           |

| サンプリング・レート*           | ジェネレータと同じ |

| ファイン遅延レンジ             | ±1周期      |

| サンプリング遅延レンジ           | ジェネレータと同じ |

| 確度                    | ジェネレータと同じ |

| 分解能                   | ジェネレータと同じ |

| スキュー                  | ジェネレータと同じ |

\* フロントエンドのディレーティングについては表を参照してください。

図21：E4861Aモジュール

表23：E4861Aのパターン機能とシーケンス機能

|            |                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| パターン：      |                                                                                                                                                   |

| メモリ・ベース    | 最大8Mビット、表18を参照                                                                                                                                    |

| PRBS/PRWS  | $2^n-1$ 、 $n=7, 9, 10, 11, 15, 23, 31$                                                                                                            |

| マーカ密度      | PRBS/PRWS ( $2^n-1$ 、 $n=7, 9, 10, 11, 15$ ) で $1/8, 1/4, 1/2, 3/4, 7/8$                                                                          |

| エラー        | $2^n-1$ 、 $n=7, 9, 10, 11, 15$                                                                                                                    |

| 拡張1または0    | $2^n-1$ 、 $n=7, 9, 10, 11, 15$                                                                                                                    |

| クロック・パターン  | 2、4、8、16による除算または乗算                                                                                                                                |

| ユーナ        | データ・エディタ、ファイル・インポート                                                                                                                               |

| アナライザの自動同期 | PRBSまたはメモリ・ベース・データに対して手動または自動：<br>ビット同期*、自動位相アライメントありまたはなし<br>スタート・サンプル遅延付近での自動遅延アライメント<br>(レンジ： $\pm 10\text{ns}$ )<br>BERしきい値： $10^4 \sim 10^9$ |

\* データ上のビット同期は、セグメントの先頭で48ビットのユニーク・ワードを検出することで行われます。検出ワード内では、任意のビットが可能です。本モードでは、同一システム内でのメモリ・ベース・データの送信は不可です。複数の入力と、端子間の遅延差を同期させる場合は、 $\pm 5$ セグメント長分解能以下であることが必要です。

表24：データ・レート・レンジ、セグメント長分解能、同期およびファイン遅延動作で利用可能なメモリ

| データ・レート・レンジ、<br>Mbps | セグメント長分解能 | 最大メモリ長、ビット |

|----------------------|-----------|------------|

| 333.334～666.666      | 16ビット     | 2,097,152  |

| 666.667～1,333.333    | 32ビット     | 4,194,304  |

| 1,333.334～2,666.667  | 64ビット     | 8,388,608  |

通常、セグメント長分解能を上記の表に記載された値以上に設定することも可能です。また、低い周波数を設定することもできます。

表25：PRWS生成能力とポート幅との依存関係。

以下の組み合わせを除いて、ほぼすべての組み合わせが可能。

| PRWS       | ポート幅       |

|------------|------------|

| $2^7-1$    | 無制限        |

| $2^9-1$    | 7          |

| $2^{10}-1$ | 3、11、31、33 |

| $2^{11}-1$ | 23         |

| $2^{15}-1$ | 7、31       |

| $2^{23}-1$ | 47         |

| $2^{31}-1$ | 無制限        |

#### サブ周波数：

システム・クロックを分周した周波数が必要なアプリケーションでは、レートに対して1、2、4による除算または乗算が可能です。これにより、セグメント長分解能と最大メモリ長との間のトレード・オフが変化します(表24を参照)。

#### 同期

同期は、入力ビット・ストリーム上でデータを比較するためにビット位相を自動的に調整する手法です。同期は、PRBS/PRWSでもメモリ・ベース・データでも実行できますが、PRxSとメモリ・ベース・データが混在する場合は実行できません。

以下の2種類の同期があります。

- ビット同期

- 自動遅延アライメント

ビット同期の場合、サイクル数が不明でもビット・アライメントをカバーできます。メモリ・ベースのデータを使用すると、予測データ・セグメント内の最初の48ビットは、入力データと比較する検出ワードとして機能します。入力データがこの検出ワードと一致すると、さらなる解析がスタートします。

自動遅延アライメントは、アナライザのサンプリング遅延を使って実行します。このためレンジが制限され、レンジが10nsである可能性があります。

自動遅延アライメントを使用すると、グループのアナライザ・チャネル間で絶対タイミング関係を持つ同期が得られ、スキューティングが可能になります。

表26：アナライザ・フロントエンドE4863A、2.7Gサンプル／秒

(E4865A、1.65Gサンプル／秒)のパラメータ

|                        |                                          |

|------------------------|------------------------------------------|

| チャネル数                  | 1、差動またはシングルエンド                           |

| インピーダンス                | 50Ω (代表値)<br>(終端電圧をオフにした場合は100Ω差動)       |

| 内部終端電圧(オフ可能)           | -2.0～+3.0V                               |

| しきい値電圧範囲               | -2.0～+3.0V                               |

| しきい値分解能                | 2mV                                      |

| しきい値確度                 | ±1% ±20mV                                |

| 入力感度<br>(シングルエンドおよび差動) | 50mV (代表値)                               |

| 最小検出可能パルス幅             | 180ps (代表値、ECLレベル)                       |

| 最大入力電圧レンジ              | 3レンジ選択可能：<br>-2V～+1V<br>-1V～+2V<br>0V～3V |

| 最大差動電圧                 | 1.8V動作時<br>最大3V                          |

| 位相マージン、理想入力信号使用時       | >1UI-50ps                                |

| ジェネレータE4862A使用時        | >1UI-75ps                                |

| 補助出力                   | 振幅：400mVpp (代表値、AC結合)                    |

表27：ジェネレータ・フロントエンドE4862A 2.7Gbps

(E4864A 1.65Gbps)のパラメータ

|                |                                                 |

|----------------|-------------------------------------------------|

| 出力             | 1、差動またはシングルエンド                                  |

| インピーダンス        | 50Ω (代表値)                                       |

| フォーマット         | クロック：デューティ・サイクル50%±10%<br>(代表値)<br>データ：NRZ、DNRZ |

| 出力電圧ウィンドウ      | -2.00～+3.00V<br>3.00V～4.5V (+3Vにのみ終端)           |

| 最大外部電圧         | -2.2～+4.7V                                      |

| 外部端子電圧         | -2V～+3V                                         |

| 振幅／分解能         | 低電圧CMOS 0.05～1.8Vpp*/10mV                       |

| 確度ハイレベル／振幅     | ±2% ±10mV                                       |

| ショート回路電流       | 72mA最大値                                         |

| 遷移時間(20%-80%)  | 90ps (代表値) ECL、LVDSの場合<br>110ps (代表値) Vpp最大値の場合 |

| オーバーシュート／リンギング | 20%+20mV (代表値)                                  |

| ジッタ、データ・モード    | <50ps ピークツーピーク                                  |

| クロック・モード       | <5ps、rms                                        |

\* オープンの場合は2倍。ただし、出力がオフになる可能性があります。

## 入出力

### 対応ロジック信号

LVDS、ECL (0V/-2V～50Ωで終端)、

PECL (+3Vに終端)

### アナライザ入力

アナライザ・チャネルは、以下のモードで動作します。

- シングル・エンド・ノーマル

- シングル・エンド・コンプリメント

- 差動

終端のため、常に50Ωに接続されています。差動モードでは、さらに100Ω差動終端も選択可能です。終端の選択とは別に、入力信号の解析を入力で実施するか、真に差動的に実施するかを選択できます。PECLに接続する場合、BiasTを使用することを推奨します。2.7Gbpsアナライザは、補助出力を提供します。補助出力では、差動入力信号がシングルエンド信号として入手可能です。補助出力の帯域幅は2GHzに制限されます。

### ジェネレータ出力

ジェネレータ出力はシングル・エンドまたは差動で使用できます。リレーのイネーブル／ディスエーブルによってオン／オフを切り替えます。スイッチ・オフの場合、内部で終端されます。未使用出力はオフにするか、外部で終端することをお勧めします。

ジェネレータ出力は50Ωセンタ・タップ終端または100Ω差動終端で動作できます。適切な終端をエディタで選択し、適切なレベルに適合させることができます。

### 保護

入力リレーと出力リレーは、最大電圧を超えると自動的にオフになります。

# 675MHz

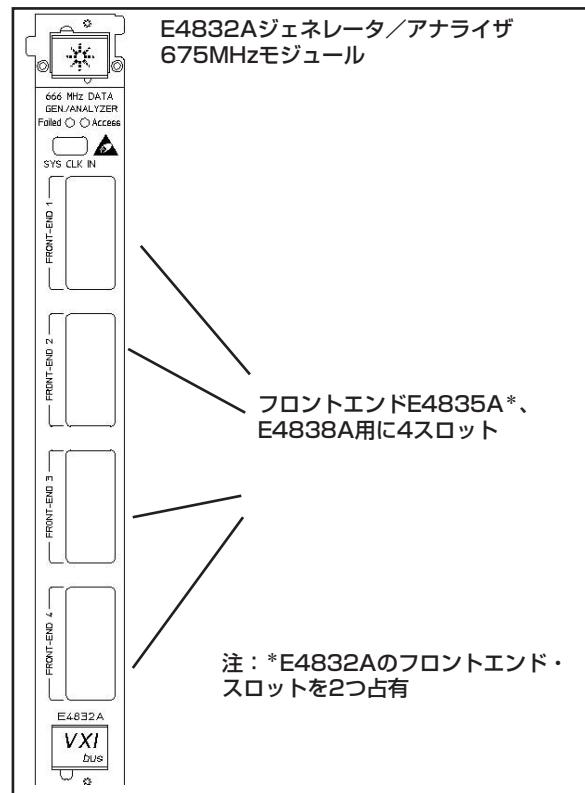

## E4832A 675MHzジェネレータ／アナライザ・モジュール

このモジュールには、最大2台のアナライザ・フロントエンド (E4835A) と最大4台のジェネレータ・フロントエンド (E4838A) を収容できます。

### クロック・モジュール／データ・モード

ジェネレータは、クロック・モードまたはデータ・モードで動作できます。クロック・モードにするには、ジェネレータをパルス・ポートとして割り当てます。データ・モードにするには、ジェネレータをデータ・ポートとして使用します。クロック・モードでは、デューティ・サイクルが50%に固定されます。データ・モードでは、可変遅延を持つNRZフォーマットとなります。アナライザは、常に可変サンプリング遅延を持つデータ・ポートとして機能します。サンプリング遅延は、2つの要素、開始遅延とファイン遅延からなります。ファイン遅延は、測定を停止せずに±1周期内で変更できます。

### データ機能

PRBS/PRWSとメモリ・ベースのデータは、セグメントによって定義されます。セグメントは、ジェネレータ・モジュールではパターン生成のために用いられ、アナライザ・モジュールでは予測パターンを定義するために用いられます。予測パターンは、マスク・ビットを使って定義できます。

セグメント長分解能は、パターン・セグメントの長さを設定する際の分解能です。E4832Aのチャネルあたりの最大メモリは、16ビット・ステップで2048Kビットまで設定できます。16ビット・セグメント長分解能が粗過ぎる場合、メモリ長と周波数を表28に示すようにトレードオフできます。

### サブ周波数：

システム・クロックを分周した周波数が必要なアプリケーションでは、レートに対して2、4、8、16による除算または乗算が可能です。これにより、セグメント長分解能と最大メモリ長との間のトレード・オフが変化します(表28を参照)。

図22 : E4832Aモジュール

表28 : E4832Aデータ・ジェネレータのタイミング仕様

(50%振幅、GNDに対して50Ω、最速遷移時間)

|            |                             |

|------------|-----------------------------|

| 周波数レンジ     | 33.334kHz～675MHz            |

| 遅延レンジ      | 0～3.0μs (周期による制限なし)         |

| 分解能        | 2ps                         |

| 確度         | ±50ps±50ppm、0遅延位置を基準*       |

| スキュー       | 50ps(代表値)、カスタマ・レベルでのスキュー補正後 |

| パルス幅       | 幅またはデューティ・サイクルの%で指定         |

| レンジ        | 750ps～[周期-750ps]            |

| 分解能        | 2ps                         |

| 確度         | ±200ps±0.1%                 |

| デューティ・サイクル | 1%～99%、パルス幅により制限            |

\* 室温15～35°Cで有効。

表29 : E4832Aアナライザのタイミング。すべてのタイミング・パラメータはECLレベルでGNDに対して50Ωの終端で測定

|                      |              |

|----------------------|--------------|

| サンプリング遅延             | =開始遅延+ファイン遅延 |

| 測定器を停止せずにファイン遅延を変更可能 | **           |

| サンプリング・レート*          | ジェネレータと同じ    |

| ファイン遅延レンジ            | ±1周期         |

| サンプリング遅延レンジ          | ジェネレータと同じ    |

| 確度                   | ジェネレータと同じ    |

| 分解能                  | ジェネレータと同じ    |

| スキュー                 | ジェネレータと同じ    |

\* フロントエンドのディレーティングについては表を参照してください。

\*\* 条件 : 周波数>20.8MHz、および最高セグメント長分解能の場合。

表30: E4832Aのパターン機能とシーケンス機能

|               |                                                                                                                                                        |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| パターン:         |                                                                                                                                                        |

| メモリ・ベース       | 最大2Mビット (表24を参照)                                                                                                                                       |

| PRBS/PRWS     | $2^n-1$ 、 $n=7, 9, 10, 11, 15, 23, 31$                                                                                                                 |

| マーカ密度         | PRBS/PRWS ( $2^n-1$ 、 $n=7, 9, 10, 11, 15$ ) で1/8、1/4、1/2、3/4、7/8                                                                                      |

| エラー           | $2^n-1$ 、 $n=7, 9, 10, 11, 15$                                                                                                                         |

| 拡張1または0       | $2^n-1$ 、 $n=7, 9, 10, 11, 15$                                                                                                                         |

| クロック・パターン     | 2、4、8、16で除算または乗算                                                                                                                                       |

| ユーザ           | データ・エディタ、ファイル・インポート                                                                                                                                    |

| アナライザ自動同期: ** | PRBSまたはメモリ・ベース・データに対して<br>手動または自動:<br>ビット同期*、自動位相アライメントありまたはなし<br>スタート・サンプル遅延付近での自動遅延<br>アライメント (レンジ: $\pm 50\text{ns}$ )<br>BERしきい値: $10^4 \sim 10^9$ |

\* データ上のビット同期は、セグメントの先頭で48ビットのユニーク・ワードを検出することで行われます。検出ワード内では、任意のビットが可能です。本モードでは、同一システム内でのメモリ・ベース・データの送信は不可です。複数の入力と、端子間の遅延差を同期させる場合は、 $\pm 5$ セグメント長分解能以下であることが必要です。

\*\* 条件: 周波数 $>20.8\text{MHz}$ 、および最高セグメント長分解能の場合。

表31: データ・レート・レンジ、セグメント長分解能、同期およびファイン遅延動作で利用可能なメモリ

| データ・レート・レンジ、Mbps | セグメント長分解能 | 最大メモリ長、ビット |

|------------------|-----------|------------|

| 20.834~41.666    | 1ビット      | 131,008    |

| 41.667~83.333    | 2ビット      | 262,016    |

| 83.334~166.666   | 4ビット      | 524,032    |

| 166.667~333.333  | 8ビット      | 1,048,064  |

| 333.334~666.667  | 16ビット     | 2,097,152  |

通常、セグメント長分解能を上記の表に記載された値以上に設定することも可能です。また、低い周波数を設定することもできます。ただし、その場合は、ファイン遅延機能および自動同期機能は使用不可です。

表32: PRWS生成能力とポート幅との依存関係。

以下の組み合わせを除いて、ほぼすべての組み合わせが可能。

| PRWS       | ポート幅       |

|------------|------------|

| $2^7-1$    | 無制限        |

| $2^9-1$    | 7          |

| $2^{10}-1$ | 3、11、31、33 |

| $2^{11}-1$ | 23         |

| $2^{15}-1$ | 7、31       |

| $2^{23}-1$ | 47         |

| $2^{31}-1$ | 無制限        |

## 同期

同期は、入力ビット・ストリーム上でデータを比較するためにビット位相を自動的に調整する手法です。同期は、PRBS/PRWSでもメモリ・ベース・データでも実行できますが、PRxSとメモリ・ベース・データが混在する場合は実行できません。

以下の2種類の同期があります。

- ビット同期

- 自動遅延アライメント

ビット同期の場合、サイクル数が不明でもビット・アライメントをカバーできます。メモリ・ベースのデータを使用すると、予測データ・セグメント内の最初の48ビットは、入力データと比較する検出ワードとして機能します。入力データがこの検出ワードと一致すると、さらなる解析がスタートします。

自動遅延アライメントは、アナライザのサンプリング遅延を使って実行します。このためレンジが制限され、レンジが $50\text{ns}$ である可能性があります。

自動遅延アライメントを使用すると、グループのアナライザ・チャネル間で絶対タイミング関係を持つ同期が得られ、スキー測定が可能になります。

| 表33：差動ジェネレータ・フロントエンドE4838A 675MHzのレベル・パラメータ |                                 |

|---------------------------------------------|---------------------------------|

| チャネル数                                       | 1、差動出力                          |

| インピーダンス                                     | 50Ω (代表値)                       |

| データ・フォーマット                                  | RZ、R1、NRZ、DNRZ                  |

| 出力電圧ウィンドウ                                   | -2.2~+4.4V (開放端子に対しては2倍、最大5Vpp) |

| 振幅/分解能                                      | <0.1~3.50Vpp/10mV               |

| レベル確度                                       | ±3%±25mV (セトリング時間5ns後)          |

| @LVDS/(P) ECL                               | ±1%±25mV (セトリング時間5ns後)          |

| 可変遷移時間範囲<br>(振幅の10~90%)                     | 0.5~4.5ns                       |

| 確度                                          | ±5%±100ps                       |

| @LVDS/(P) ECL (振幅の20~80%)                   | 0.35ns (代表値)                    |

| オーバーシュート/リンギング                              | <7%/<5% (代表値)                   |

| ジッタ データ・モード                                 | <100psピークツーピーク (80ps代表値)        |

| クロック・モード                                    | 8ps rms (代表値)                   |

| チャネル加算                                      | XORおよびアナログ                      |

表34：2差動アナライザ・フロントエンドE4835A<sup>1</sup>、675Mサンプル/秒

|                  |                                    |

|------------------|------------------------------------|

| チャネル数            | 2、差動またはシングルエンド(切り替え可能)             |

| インピーダンス          | 50Ω (代表値)<br>(終端電圧をオフにした場合は100Ω差動) |

| 終端電圧(オフ可能)       | -2.0~+3.0V                         |

| しきい値電圧範囲/しきい値確度  | -2.00~+4.50V/±1%±20mV              |

| しきい値分解能          | 2mV                                |

| 入力感度             | 差動50mV (代表値)<br>シングルエンド100mV (代表値) |

| 最小検出可能パルス幅       | 400ps (代表値)、ECLレベル                 |

| 入力電圧範囲           | 2レンジ選択可能: 0~5Vおよび-2V~+3V           |

| 位相マージン、理想入力信号使用時 | >1UI-100ps                         |

| ジェネレータE4838A使用時  | >1UI-180ps                         |

<sup>1</sup> E4832Aのフロントエンド・スロット2個を占有。E4835Aには、2台のフロントエンド(E4835AZ)と共通データ・バックエンドが含まれています。ここでは、1台のフロントエンドをE4835Aと呼んでいます。

## 入出力

### 対応ロジック信号

LVDS、(P) ECL、TTL、3.3V CMOS

### アナライザ入力

アナライザ・チャネルは、以下のモードで動作します。

- シングル・エンド・ノーマル

- シングル・エンド・コンプリメント

- 差動

終端のため、常に50Ωに接続されています。差動モードでは、さらに100Ω差動終端も選択可能です。終端の選択とは別に、入力信号の解析を入力で実施するか、真に差動的に実施するかを選択できます。

### ジェネレータ出力

ジェネレータ出力はシングル・エンドまたは差動で使用できます。リレーのイネーブル/ディスエーブルによってオン/オフを切り替えます。スイッチ・オフの場合、内部で終端されます。未使用出力はオフにするか、外部で終端することをお勧めします。

ジェネレータ出力は50Ωセンタ・タップ終端または100Ω差動終端で動作できます。適切な終端をエディタで選択し、適切なレベルに適合させることができます。

# クロック・モジュール

システムは、1台以上のジェネレータまたはアナライザ、および最低1台のクロック・モジュールから構成されます。

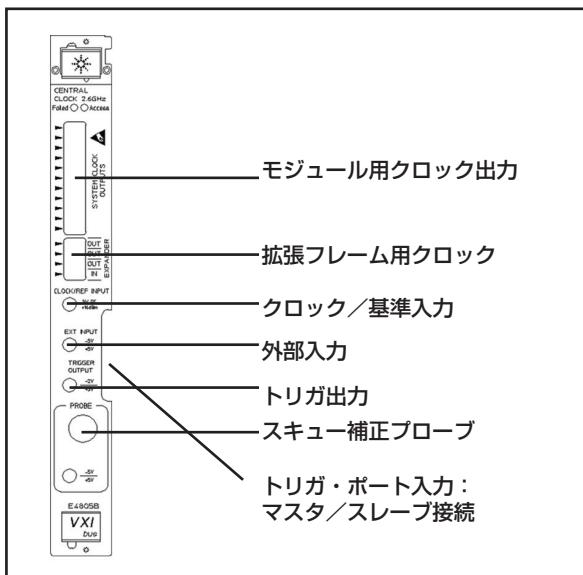

## E4805BおよびE4808A セントラル・クロック・モジュール

セントラル・クロック・モジュールには、システム・クロックを供給するPLL(フェーズロック・ループ)周波数発生器が内蔵されています。選択した周波数に応じて、データ・モジュールにシステム・クロックより1、2、4、8、16、32、64、256倍高いが分周されたクロックを供給できます。

**外部スタート/ストップ:** データ・ランは、外部入力に外部信号を供給することにより開始できます。モジュールE4832Aを使用すると、ストップ・モードとゲート・モードも使用できます。

**外部クロック/外部基準:** この入力は、ParBERT 81250を外部クロックと同期させる役割を果たします。内部発振器よりも正確な基準が必要な場合などに使用します。連続クロックを使用する必要があります。外部クロックとしてバースト・クロックを使用することはできません。最大外部クロックはE4805Bの場合は2.7GHz、E4808Aの場合は10.8Gbpsです(注: ジッタ仕様は改善されません)。

**ガイド付きスキー補正:** チャネルごとの半自動スキー補正。スキー補正プローブ15447Aを使うと、DUT(被試験デバイス)フィクスチャでのスキー補正が可能です。

表35 : E4805B/E4808Aクロック・モジュール仕様

|                                  | E4805B                                                                                          | E4808A                                                                                                                                                            |

|----------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>周波数レンジ*</b> (周期または周波数として入力可能) | 1kHz~675MHz<br>E4805Bが動作するクロック・モジュールの周波数レンジ<br>- E4861Aは334MHz~2.7GHz<br>- E4832Aは334kHz~675MHz | 170kHz~675MHz<br>E4808Aが動作するクロック・モジュールの周波数レンジ<br>- E4866A/E4867Aは9.5GHz~10.8GHz<br>- E4861Bは20.834MHz~3.35GHz<br>- E4861Aは334MHz~2.7GHz<br>- E4832Aは334kHz~675MHz |

| <b>分解能</b>                       | 1Hz                                                                                             | 1Hz                                                                                                                                                               |

| <b>確度</b>                        | ±50ppm (内部PLL基準使用)                                                                              | ±50ppm (内部PLL基準使用)                                                                                                                                                |

\* モジュールまたはフロントエンドにより制限または拡大される場合があります。

表36 : 外部入力および外部クロック/外部基準入力

|                                     | E4805B                                                                           | E4808A                                                  |

|-------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------|

| <b>Zin/終端電圧</b>                     | 50Ω/-2.10V~3.30V                                                                 | 50Ω/-2.10V~3.30V                                        |

| <b>感度/最大レベル</b>                     | 400mVpp/-3V~+6V                                                                  | 200mVpp/-3V~+6V<br>(<9.5Gbpsの場合)<br>300mVpp/-3V~+6V<br> |

| <b>カップリング</b><br><b>外部入力:</b>       | DC、<br>しきい値レンジ: -1.40V~<br>+3.70V                                                | DC、<br>-1.40V~+3.70V                                    |

| <b>外部クロック/</b><br><b>外部基準:</b>      | AC                                                                               | AC                                                      |

| <b>入力遷移/スロープ</b>                    | <20ns、外部入力のアクティブ・エッジは選択可能                                                        | <20ns、外部入力のアクティブ・エッジは選択可能                               |

| <b>クロック入力</b><br><b>乗数(m)/除数(d)</b> | m=1~256、n=1~256<br>m*n<=1024m/n *入力周波数は、データ・レンジの<br>入力周波数/n>=1.3MHzに適合する必要があります。 |                                                         |

| <b>PLLロック・タイム</b>                   | 100ms                                                                            | 100ms                                                   |

| <b>入力周波数/周期:</b>                    |                                                                                  |                                                         |

| <b>外部クロック</b>                       | 170kHz~2.7GHz                                                                    | 170kHz~10.8GHz                                          |

| <b>外部基準</b>                         | 1*、2*、5、10MHz                                                                    | 1*、2*、5、10MHz                                           |

| <b>必要デューティ・サイクル</b>                 | 50±10%                                                                           | 50±10%                                                  |

| <b>レイテンシ(代表値):</b><br><b>外部入力</b>   | トリガ出力まで 16ns±1クロック                                                               | チャネル出力まで 46ns±1クロック<br>16ns±1クロック 46ns±1クロック**          |

| <b>外部クロック</b>                       | 15ns<br>拡張フレーム使用時は3nsを加算                                                         | 45ns<br>拡張フレーム使用時は3nsを加算                                |

\* ジッタ性能が低下することがあります。 \*\* 周波数=667MHzの場合

図23 : クロック・モジュール

**表37：トリガ出力特性E4805BおよびE4808A**

|                  |                                                               |

|------------------|---------------------------------------------------------------|

| トリガ出力信号          | - クロック・モード(最高675MHzまで)<br>- シーケンス・モード                         |

| 出力インピーダンス        | 50Ω(代表値)                                                      |

| 出力レベル            | TTL(周波数<180MHz)、GNDに対して50Ω、ECL GND/-2Vに対して50Ω、PECL +3Vに対して50Ω |

| トリガ進行速度          | 代表値30ns、トリガ出力とデータ出力/サンプリング・ポイントとの間(どちらの場合も遅延は0に設定)            |

| 最大外部電圧           | -2V～+3.3V                                                     |

| ジッタ(内部基準／内部クロック) | <10ps rms(代表値は5ps)                                            |

**表38：E4805BおよびE4808Aシーケンス機能**

|             |                                                                      |

|-------------|----------------------------------------------------------------------|

| セグメント数      | 1～30(全セグメントを1回ループ)<br>1～60(ループするセグメントなし)                             |

| ループ・レベル     | 最大4レベルのネスト・ループと、オプションの1無限ループ<br>ループの反復回数は独立に1～2 <sup>20</sup> 回に設定可能 |

| スタート/ストップ   | 外部入力、手動、プログラム<br>(ストップはE4832Aの場合のみ)                                  |

| イベント・ハンドリング | 内部/外部イベント発生時に動作。<br>詳細については表32を参照。                                   |

**表39：イベント・ハンドリングE4805BおよびE4808A****イベント・トリガ・ソース**

イベントは、以下のソースの任意の組み合わせとして定義可能。最大10イベントまで定義可能。

- 8ライン・トリガ入力ポッド、TTL信号用

- VXIトリガ・ラインT0およびT1

- アナライザ・チャネルの1つで検出した捕捉エラー/非エラー

- ソフトウェア・コマンド・コントロール：ローカル/リモートで発行されるイベント・トリガ・コマンド

**イベント発生時の動作は**、データ・セグメントごとに、即時実行または一定時間後の実行を設定可能。以下の任意の組み合わせが可能。

- データ・セグメント・ジャンプ

- クロック・モジュールのトリガ出力へトリガ・パルスを印加

- VXIトリガ・ラインT0およびT1を、01、10、11に設定

**表40：E4808AおよびE4805Bトリガ・ポッド特性**

|                |                   |           |

|----------------|-------------------|-----------|

| 入力ライン          | 8、シングル・エンド        |           |

| 入力レベル          | TTL互換             |           |

| 入力しきい値         | 1.5V              |           |

| 入力端子           | 5kΩで+5Vにプルアップ     |           |

| 入力電圧の絶対最大定格    | -1.2V～+7.0V       |           |

| ケーブル遅延         | 11ns(代表値)         |           |

| サンプリング・クロック周波数 | システム周波数/セグメント長分解能 |           |

| セットアップ時間*      | トリガ出力             | クロック/基準入力 |

| ホールド時間*        | 2.5ns             | -12.5ns   |

|                | 5ns               | 20ns      |

\* ケーブル遅延が含まれます。

**トリガ出力**

以下のモードで使用できます。

- クロック・モード

- シーケンス・モード

シーケンス・モードでは、任意セグメントのスタートをマークするためパルスを設定します。

トリガ出力は、最高675MHzまで実行可能です。さらに高速性能を持つクロックが必要な場合：

- 2.7GHzのクロックは、パルス・ポートとして動作する2.7Gbpsのチャネルから使用可能です。

- 10.8GHzのクロックは、クロック出力として動作する10.8Gbps生成モジュールから使用可能です。

**シーケンス機能**

シーケンス機能は以下のデータ・フローの指定に使用されます。

- シングル

- ループ

- 無限

- イベント・ハンドリング(分岐)

- 同期

**イベント・ハンドリング**

イベント・ハンドリングを使用する場合、データ生成のフローと解析は実行時、外部信号によって制御できます。

**イベントの利用：**

- データの停止と続行

- 一致ループ

- 他の機器との統合(ATE)

- エラーでのトリガ

イベント・トリガのリソースと動作については、表39を参照してください。

**マスター/スレーブ、マルチメインフレーム、異なるクロック・グループ**

マスター/スレーブ・ケーブルを接続することにより、最高3個のクロック・モジュールを組み合わせ、1つのクロック・グループとして動作させることができます。これは、1つのフレームに納まらないチャネルを1つのクロック・グループに結合する際に使用します。最初のマスター/スレーブ接続を省略すると、チャネルが個別のクロック・グループとして動作します。システムは異なるクロック・グループを使用して動作します。そのため、複数のチャネルが、1つのクロック・モジュールと組み合わされます。使用された周波数は、全体的に非同期またはm/n比(クロック入力の乗数/乗数を参照)にすることができます。クロック・グループを分ける場合には、マスター/スレーブ接続は行いません。1つのシステム内でモジュールのタイプは常に同じである必要があります。

# 一般仕様

メインフレーム：表34を参照

セーブ／リコール：パターン・セグメント、設定、全設定+セグメントのセーブ／リコールが可能。記憶可能な設定の数は内部ディスク容量でのみ制限。

ベクタのインポート／エクスポート：パターン・ファイルのインポート／エクスポートは、3.5インチ・フロッピー・ディスク、LANまたはGPIB (IEEE 488.2) で可能。ファイル・フォーマットはASCIIで、STILのサブセットを使用。

プログラミング・インターフェース：GPIB (IEEE 488.2) およびLAN。アプリケーションのインターフェースとしてC、Visual Basic、VEEなどのインストールが必要。Agilent 81200プラグ・アンド・プレイ・ドライバによる容易なプログラミングが可能。

プログラミング言語：SCPI 1992.0

プログラミング時間：メモリとハードウェアとの間のベクタ転送時間はデータ量に依存。表34も参照。

オンライン・ヘルプ：コンテキスト依存

プリント・オン・デマンド：入門ガイドとプログラミング・ガイドは、ParBERT 81250ソフトウェア付属の.pdfファイルからプリント可能。

セルフテスト：モジュールとシステムのセルフテストを実行可能

## モジュール

モジュール・サイズ：VXI Cサイズ、1スロット

モジュール・タイプ：レジスタ・ベース。メインフレームに付属のParBERT 81250ユーザ・ソフトウェア E4875Aが必要。

質量：(フロントエンド含む)

正味：2kg

輸送時：2.5kg

保証：3年間引き取り修理、サポート・オプションによって異なる

再校正期間：3年間推奨

## Agilent Technologies 品質標準

ParBERT 81250はISO 9001国際品質システム標準に基づいて製造されています。これは、品質管理の改善によってお客様の満足を追求するというAgilent Technologiesの方針の一環です。

表41：プログラミング時間

| プログラミング時間                  |                                                                                            |

|----------------------------|--------------------------------------------------------------------------------------------|

| レベル変化                      | 6ms (代表値)                                                                                  |

| 遅延変化                       | 16ms (代表値) ラン・モードには適用不可                                                                    |

| 周期変化                       | 60ms (代表値) E4805B 1台とE4832A 1台の場合。<br>ラン・モードには適用不可。モジュール数に応じて<br>増加するが、モジュール数を掛けたものよりは小さい。 |

| ストップ+スタート                  | 32ms (代表値)                                                                                 |

| 同期*                        | 50ms (代表値、位相アライメントなし)<br>110ms (代表値、660MHzで20%の位相確度)<br>650ms (代表値、660MHzで1%の位相確度)         |

| 値のダウンロード：                  |                                                                                            |

| 4チャネル・システム、<br>各100,000ビット | <1.5s (代表値)                                                                                |

| 120チャネル・システム、<br>各1Mビット    | <30s (代表値)                                                                                 |

| 40チャネル・システム、<br>各1Mビット     | <10s (代表値)                                                                                 |

\* 1つのモジュール内の同期アナライザごとに仕様値を追加。

表42：モジュールおよびフロントエンドの電源要件

|                                                                                                        | DC電圧     | +24V    | +12V   | +5V    | -2V   | -5.2V | -12V  |

|--------------------------------------------------------------------------------------------------------|----------|---------|--------|--------|-------|-------|-------|

| <b>モジュール(本仕様は、フロントエンドが装着されたモジュールに対して有効)</b>                                                            |          |         |        |        |       |       |       |

| E4805Bセントラル・クロック・モジュール                                                                                 | DC電流     | 0.15A   | 0.2A   | 1.8A   | 1.4A  | 3.8A  | 0.2A  |

|                                                                                                        | ダイナミック電流 | 0.0015A | 0.02A  | 0.18A  | 0.14A | 0.38A | 0.02A |

| E4808A                                                                                                 | DC電流     | 0.35A   | 0.2A   | 3.0A   | 1.2A  | 3.6A  | 0.2A  |

|                                                                                                        | ダイナミック電流 | 0.04 A  | 0.02A  | 0.30 A | 0.12A | 0.36A | 0.02A |

| E4867A                                                                                                 | DC電流     | 0.2A    | 1.0A   | 7.0A   | 1.5A  | 3.0A  | 0.8A  |

|                                                                                                        | ダイナミック電流 | 0.02A   | 0.1A   | 0.7A   | 0.15A | 0.3A  | 0.08A |

| E4866A                                                                                                 | DC電流     | 0.2A    | 1.0A   | 5.0A   | 1.2A  | 2.6A  | 0.5A  |

|                                                                                                        | ダイナミック電流 | 0.02A   | 0.1A   | 0.5A   | 0.12A | 0.26A | 0.05A |

| E4861A 2.67Gbps ジェネレータ/アナライザ・モジュール                                                                     | DC電流     | 0.10A   | 0.50A  | 5.20A  | 1.80A | 4.00A | 0.90A |

|                                                                                                        | ダイナミック電流 | 0.01A   | 0.05A  | 0.52A  | 0.18A | 0.40A | 0.09A |

| 注記：E4861Aの電源条件には、2つのフロント・エンドの電源条件が含まれています。                                                             |          |         |        |        |       |       |       |

| E4861B                                                                                                 | DC電流     | 0.02A   | 0.02A  | 1.8A   | 0.33A | 0.04A | 0.A   |

|                                                                                                        | ダイナミック電流 | 0.01A   | 0.01A  | 0.2A   | 0.03A | 0.05A | 0.A   |

| E4832A 667MHz ジェネレータ/アナライザ・モジュール                                                                       | DC電流     | 0.10A   | 0.10A  | 2.60A  | 0.60A | 3.60A | 0.10A |

|                                                                                                        | ダイナミック電流 | 0.01A   | 0.001A | 0.26A  | 0.06A | 0.36A | 0.01A |

| 注記：モジュールE4832Aの場合、選択したフロントエンド(E4835A、E4838A、E4843A)の電源仕様の値を、E4832Aモジュールの電源仕様の値に追加することで、全体の電源仕様の値となります。 |          |         |        |        |       |       |       |

### フロントエンド

|                                         |          |        |        |        |        |        |

|-----------------------------------------|----------|--------|--------|--------|--------|--------|

| E4835A 2差動アナライザ、667Mサンブル/秒<br>(E4835AZ) | DC電流     | 0.2A   | 1.2A   | 0.2A   | 0.3A   | 0.3A   |

|                                         | ダイナミック電流 | 0.02A  | 0.12A  | 0.02A  | 0.03A  | 0.03A  |

| E4838A 差動ジェネレータ、667MHz、可変スロープ           | DC電流     | 0.45A  | 0.18A  | 0.07A  | 0.38A  | 0.41A  |

|                                         | ダイナミック電流 | 0.045A | 0.006A | 0.007A | 0.038A | 0.041A |

| E4862Bジェネレータ                            | DC電流     | 0.2A   | 0.2A   | 0.7A   | 0.2A   | 0.5A   |

|                                         | ダイナミック電流 | 0.02A  | 0.02A  | 0.07A  | 0.02A  | 0.05A  |

| E4863Bアナライザ                             | DC電流     | 0.2A   | 0.2A   | 1.8A   | 0.2A   | 0.5A   |

|                                         | ダイナミック電流 | 0.02A  | 0.02A  | 0.2A   | 0.02A  | 0.05A  |

|                                         |          |        |        |        |        | 0.02A  |

表43：フロントエンド装着時のモジュールE4805BおよびE4861Aの冷却要件

| モジュール  | △Pmm H <sub>2</sub> O、<br>10°C上昇毎 | エア流量、<br>リッタ/秒 |

|--------|-----------------------------------|----------------|

| E4805B | 0.25                              | 3.6            |

| E4861A | 0.4                               | 5.2            |

| E4866A | tbd                               | tbd            |

| E4867A | tbd                               | tbd            |

表44：フロントエンド装着時のモジュールE4832Aの冷却要件

| モジュール  | △Pmm H <sub>2</sub> O、<br>15°C上昇毎 | エア流量、<br>リッタ/秒 |

|--------|-----------------------------------|----------------|

| E4832A | 0.3                               | 4.7            |

表38：メインフレームの一般特性

| E4860/91/92/93Aメインフレーム |                                                                                                                                                                                                                                               |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 工場インストール済み品目           | E8403A 13スロットVXI Cサイズ・フレーム、E4805Bセントラル・クロック・モジュール<br>コントローラ・オプションのどれか1つ：<br>● #012 VXI 2スロットPC E9850A+64MB追加メモリ(合計128MB)+<br>Windows NT 4.0、E4875A ParBERT 81250ユーザ・ソフトウェアはインストール済み<br>● #013 IEEE 1394 PC-VXIリンク(E8491B)+E4875AのインストールCD-ROM |