1

# MINIATURIZED UNIVERSAL TRUNK FRAME DESCRIPTION AND THEORY

## 2-WIRE NO. 1 AND NO. 1A "ESS\*" SWITCHES

| CONTENTS PAGE CONTENTS                                                       | PAGE     |

|------------------------------------------------------------------------------|----------|

| 1. GENERAL 2 J. SD First Stage Triac Circuit .                               | 10       |

| 2. PHYSICAL DESCRIPTION 2 K. SD Second Stage Triac Circuit                   | 10       |

| 3. OVERALL FUNCTIONAL DESCRIPTION 2 L. SD Controller Logic and Timing        | 10       |

| A. General 2 POWER AND MISCELLANEOUS CIRCU                                   | IT . 13  |

| B. Bus Circuit 2 5. MAINTENANCE AND DUPLICATION                              | 13       |

| C. Signal Distributors Controller 6 6. POWER AND MISCELLANEOUS CIRCU         | ITS . 16 |

| D. Scanner Controller 7 FRAME LINE TELEPHONE JACKS .                         | 16       |

| 4. DETAILED FUNCTIONAL DESCRIPTION 7 SPARE JACK                              | 16       |

| PERIPHERAL BUS CIRCUIT                                                       | 16       |

| A. Peripheral Unit Address Bus 7 FILTERS, FUSES, AND FUSE ALARM CI           |          |

| B. Scanner Answer Bus                                                        |          |

| 7. TAKING EQUIPMENT OUT OF SERVIC<br>SCANNER CONTROLLER 8                    |          |

| 8. ABBREVIATIONS AND ACRONYMS<br>C. Scanner Register and Access Circuit . 8  | 17       |

| D. Scanner Power Circuit 8<br>Figures                                        |          |

| E. Ferrod Matrix Circuit 8<br>1. Miniaturized Universal Trunk Frame          | e3       |

| F. Scanner Detector Circuit 8<br>2. Circuit Board Mounted Universal Tr       | runk . 4 |

| SIGNAL DISTRIBUTOR CONTROLLER 8<br>3. Relationship of Trunk Circuits to Tru  | unk . 4  |

| G. SD Buffer and Maintenance Circuit . 8<br>4. Outgoing and Incoming Trunk A | Arrange- |

| H. SD Timing, Pulse, and Miscellaneous ment                                  | _        |

| Circuit 9<br>5. Normal (Split) Mode Configuration<br>nal Distributors        | -        |

| I. Intertace Circuit 10                                                      | 9        |

#### NOTICE

Not for use or disclosure outside the Bell System except under written agreement

Printed in U.S.A.

|     | CONTENTS P                                                                                             | AGE |

|-----|--------------------------------------------------------------------------------------------------------|-----|

| 7.  | Basic Signal Distributor Controller Block Dia-<br>gram                                                 | 12  |

| 8.  | Maintenance Logic                                                                                      | 14  |

| 9.  | 1024-Point Signal Distributor with Selection<br>and Pulse Path Required for Combined<br>Mode Operation | 15  |

| 10. | Home and Mate Frame Bay Control Panels                                                                 | 17  |

| 11. | MUT Functions Block Diagram (SD-1A338-<br>02)                                                          | 19  |

## 1. GENERAL

1.01 This section describes the miniaturized universal trunk (MUT) frame used in the No. 1 and No. 1A "ESS\*" switches. The schematic diagram of the MUT is SD-1A338-02.

1.02 This section is reissued to add ♦information for the improved minitrunk signal distributor diagnostic (IMD) feature (option P) and to make other changes minor in nature. Change arrows are used to indicate these changes.

**1.03** Abbreviations used in this section are listed in Part 8.

#### 2. PHYSICAL DESCRIPTION

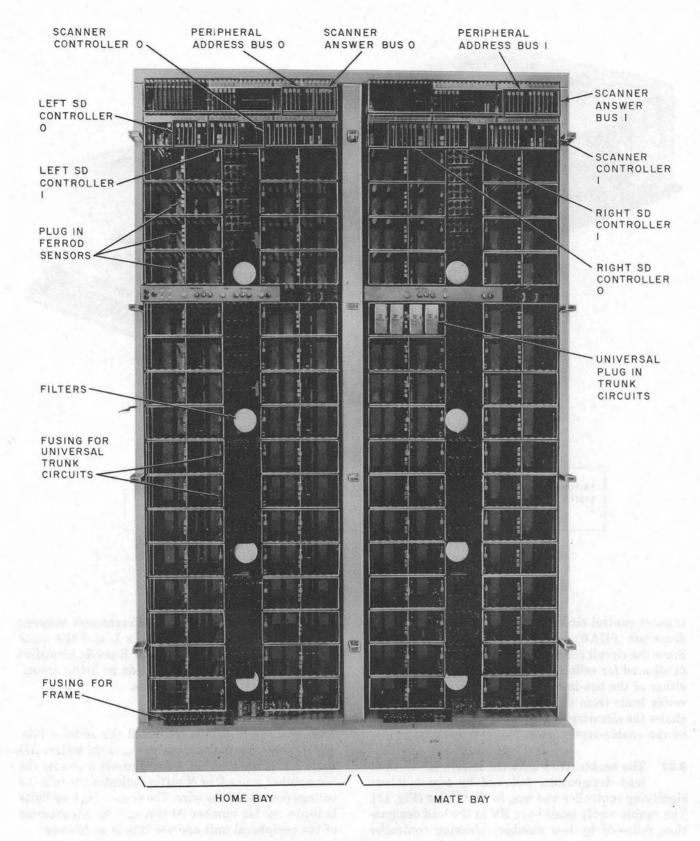

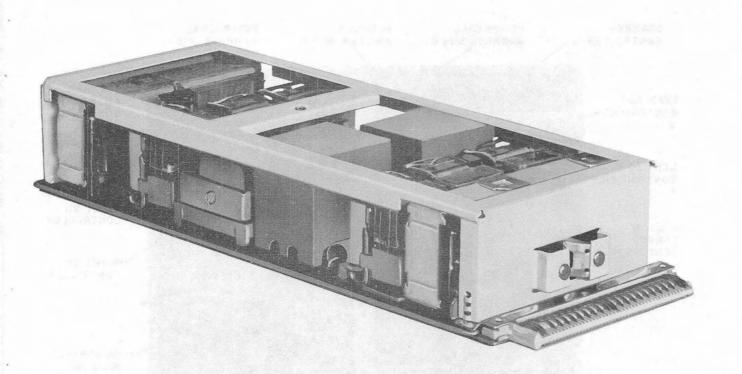

2.01 The MUT frame consists of a pair of 2-foot 2-inch bays that contain two 1024-point triac signal distributors (SDs), a 1024-point scanner, and peripheral bus units (see Fig. 1). The bays are arranged in a home-mate configuration that provides plug-in housing for 256 circuit board mounted universal trunk units (Fig. 2). The trunk unit can contain one or two trunks. The MUT frame also provides power, filters, and fusing for the trunk units.

## 3. OVERALL FUNCTIONAL DESCRIPTION

#### A. General

**3.01** The MUT establishes telephone connections between trunk circuits or to customer lines

through the switching network. The main function of the MUT is for transmission and supervision. All other functions of the trunk circuits, such as pulsing, charging, timing, etc, are delegated either directly to program control or to the service circuits which, in turn, are under program control.

**3.02** The MUT circuits have little, if any, autonomy. With few exceptions, relays within these circuits operate only under the direction of central control (CC) via the central pulse distributor (CPD) and the SD. The CC detects via a scanner any change in the trunk or loop conditions that results from relay operation or from actions by a customer or a distant office.

The MUT is used to complete and supervise 3.03 paths established through the switching network. Relays within the trunk circuits operate under the direction of CC via the CPD and SD. The SDs give CC access to relays in the trunk circuits. They are the buffers between the high-speed CC and the low-speed relays. The scanner in the MUT supervises only trunks and service circuits mounted in the MUT frame. The frames are arranged for mate operation in the scanner section. The home frame has the 0 controller for the 1024-point scanner and the mate frame has the 1 controller for the 1024-point scanner. The associated matrix is split in half with 512 points on the home frame and 512 points on the mate frame. The scanner detects and sends to CC any change in trunk or loop conditions that results from relay operations or from actions by a customer or a distant office.

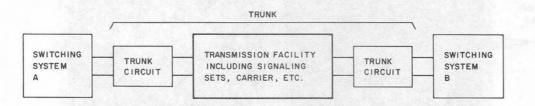

3.04 The MUT is part of the communication chan-

nel between two switching systems. The communication channel starts at the outgoing terminals of the originating office and ends at the incoming terminals of the switching network of the terminating office. As shown in Fig. 3, a trunk includes the transmission facility terminated in two trunk circuits, one at each end.

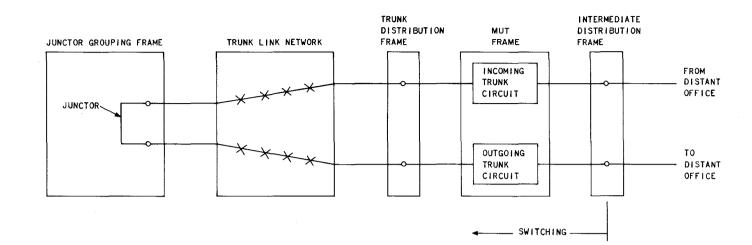

**3.05** The simplified illustration of Fig. 4 shows the relationship of outgoing and incoming trunks to the switching network. Leads from the MUT are cabled to the trunk distribution frame and the intermediate distribution frame.

#### B. Bus Circuit

**3.06** The bus circuit provides the necessary interface circuitry between the SD controllers or

Fig. 1—Miniaturized Universal Trunk Frame

Fig. 2—Circuit Board Mounted Universal Trunk

scanner control circuits and the peripheral unit address bus (PUAB) and scanner answer bus (SCAB). Since the circuit controllers, as well as the buses, are duplicated for reliability, the system needs to select either of the bus-to-controller paths via the enableverify leads from the CPD. The bus circuit also includes the circuitry to generate enable-verify signals on the enable-verify leads.

3.07 The enable pairs have the letters EN in their lead designation, followed by two numbers signifying controller and bus, in that order (Fig. 11). The enable-verify leads have EV in the lead designation, followed by two numbers showing controller

and bus. The L and R prefix differentiates between the two SDs. The home frame is L and the mate frame is R. The absence of an L or R prefix identifies the enable and enable-verify leads as being associated with the scanner controllers.

3.08 The PU bus bits are called the address bits. The incoming address bits have the letters AD in their lead designation. A 0 or 1 prefix indicates the bus number, and a P or N suffix indicates the relative voltage polarity of the wire. The remaining two digits indicate the bit number 00 through 36. An example of the peripheral unit address bits is as follows:

<u>\_\_\_\_</u>

î,

Fig. 4—Outgoing and Incoming Trunk Arrangement

## Page 5

This is No. of bit a PU address

#### C. Signal Distributors Controller

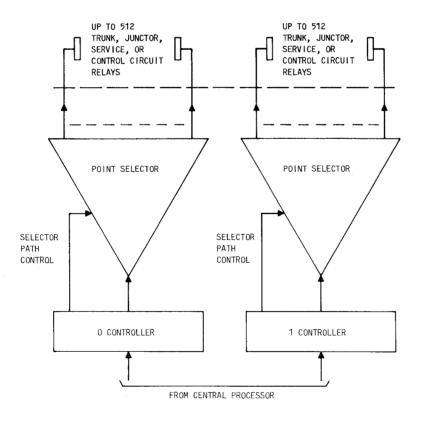

3.09 There are two pairs of SD controllers in the MUT frame. The two controllers of a pair are designated by 0 and 1. The SD controller pair for the home frame (left) is designated by the letter L. The SD controller pair for the mate frame (right) is designated by the letter R.

3.10 The SD controller used in No. 1 and No. 1A ESS switches is provided to give the central processor the ability to select magnetic latching relays in trunk circuits, junctor circuits, and certain control circuits. The SD controller acts as a buffer between the central processor (electronic speeds) and the peripheral relays (relay speeds).

3.11 The basic SD is composed of a controller and a 1-out-of-512 point selector. The SD controller, when directed by information sent in the form of a 28-bit address from the central processor, sets up a signal path to one of the 512 magnetic latching relays. The address also directs the controller to send a release or an operate signal to the relay. The controller detects the movement of the relay armature that initiates the reset of the controller enable and address register. Until this reset function has been accomplished, no new addresses can be registered or acted upon.

**3.12** The basic SD is divided into a controller and a selector. Two of these units make up a 1024-point SD. Normally, they operate independently of

each other as separate identities in what is known as *split mode* operation. In No. 1 and No. 1A ESS switches, they are always provided in pairs, as shown in Fig. 5.

Fig. 5—Normal (Split) Mode Configuration of Signal Distributors

#### D. Scanner Controller

**3.13** The scanner controller circuit provides supervision of interoffice calls and can monitor a

maximum of 512 calls (1024 parties) simultaneously. The scanner consists of a ferrod sensor matrix and a controller that is duplicated for reliability. The ferrod sensors are assigned to trunk circuits and are not duplicated. Groups of 16 ferrod sensors are scanned (interrogated) simultaneously.

#### **Ferrod Sensor**

**3.14** The ferrod sensor is the basic unit of the scan-

ner. The ferrod sensor can be considered a 2winding transformer whose coupling (the ability to induce a signal from the primary winding to the secondary winding) is controlled by the current in its control winding. The primary and secondary windings of the transformer are associated with the access and readout equipment and are referred to as the interrogate and readout windings, respectively. The control windings are associated with either the network side or the trunk side of a plug-in type trunk circuit. When a transmission path is established (talking battery current present in control windings), coupling is destroyed and the interrogate signal is not able to induce a signal into the readout windings. When no transmission path exists (no current in control windings), the interrogate signal will induce a signal in the readout winding. If the scanner seems to have functioned properly, an all-seems-well scanner signal (ASWS) is sent with the 16 interrogation replies. Each trunk circuit is scanned at an average rate of once every 0.1 second.

#### **Enabling and Addressing a Scanner**

3.15 Scanners are considered peripheral units (PUs). All PUs are addressed simultaneously from the central processor over the PU address bus. The particular PU that is to reply is selected by an enabling signal from the CPD.

3.16 All signaling to the scanner, except the control of the ferrod sensors, is done with a 0.5 µsec pulse on duplicated peripheral address buses. Each controller of the scanner must be able to operate from either PUAB with the selection being made by the enabling pulse via the CPD. The addressed controller replies simultaneously on both SCAB buses.

**3.17** Associated with each controller are two enabling pairs that determine from which bus to

accept addresses. The answer bus contains 16 pairs for ferrod outputs and a seventeenth pair for the ASWS signal.

3.18 An address bus to the scanner is divided into

two groups: the least significant (LS) group and the most significant (MS) group. Both groups contain eight pairs of wires. The scanner uses an additional pair of wires of the address bus for maintenance test (MT) orders.

## 4. DETAILED FUNCTIONAL DESCRIPTION

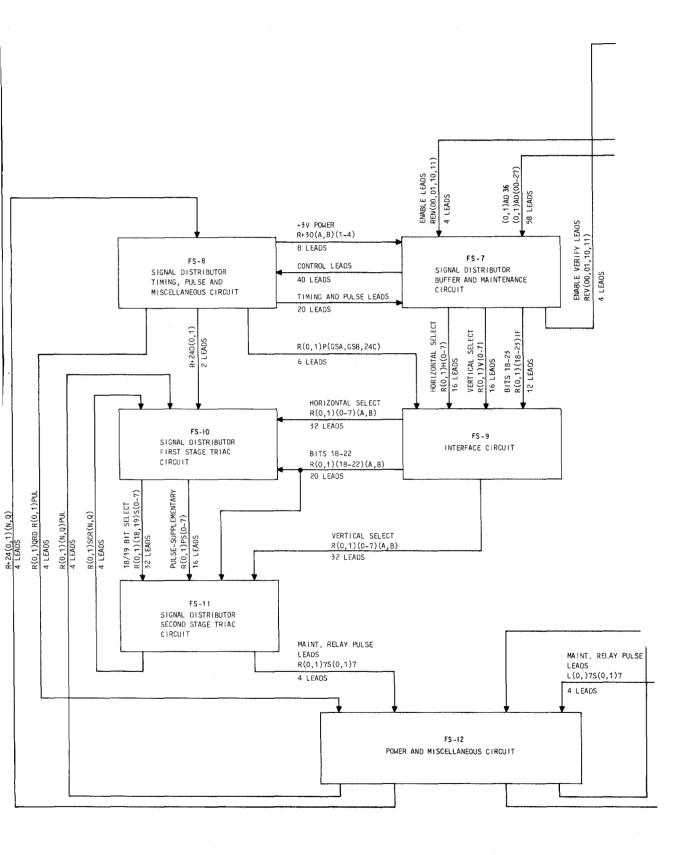

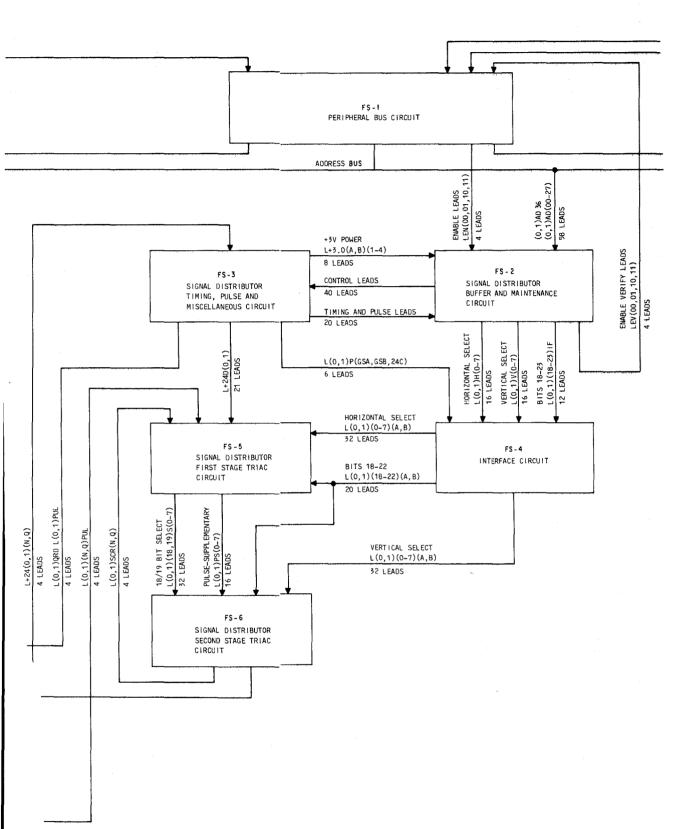

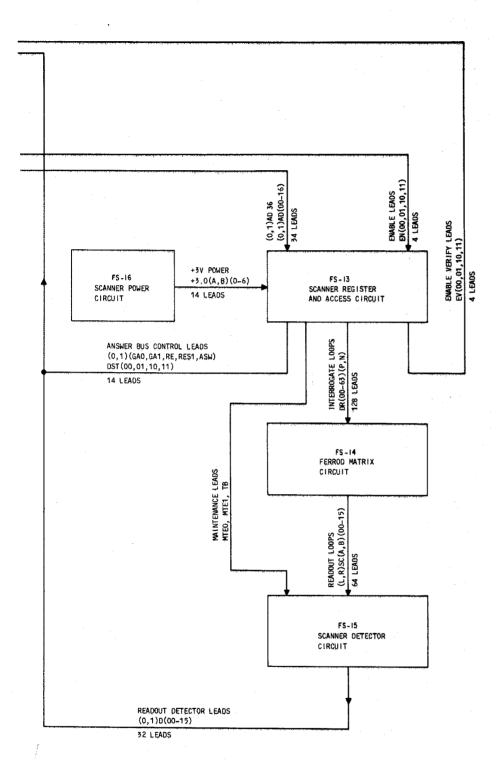

**4.01** Figure 11 is a functional block diagram of the MUT. This figure shows the left and right SD controllers, the scanner controller, and the interconnecting leads.

#### PERIPHERAL BUS CIRCUIT

## A. Peripheral Unit Address Bus

**4.02** The PUAB circuits 0 and 1 are physically and electrically separate; however, their functions are identical. The following description applies to both bus 0 and bus 1, unless otherwise stated.

**4.03** There are five FC 12 cable receiver circuit packs, four of which are capable of receiving a total of 29 address or control bits. The fifth cable receiver pack is provided to terminate six enable cable pairs.

**4.04** The cable receivers convert an input current pulse of 35 milliamperes (minimum) to a voltage swing on the output of the receiver, using a saturating transistor. The receiver output terminal is normally high (no pulse). An output on the receiver is a low going voltage pulse 0.5 microseconds wide.

**4.05** The input pick-off transformer is located on the receiver circuit pack. A bypass resistor maintains the continuity of the bus when the receiver circuit pack is pulled out and the transformer is removed.

## B. Scanner Answer Bus

**4.06** There are three FC 13 cable driver circuit packs, two of which are capable of terminating only 16 of the 17 required answer bus pairs. The seventeenth pair is terminated by one of the eight cable drivers on the third cable driver circuit pack. Six of

the remaining circuit outputs are connected to the inputs of the enable cable receiver circuit pack. These six cable drivers generate enable-verify signals on the same cable pair over which an enable signal was previously received. These enable pairs are terminated in 100 ohms.

4.07 The cable drivers convert the low voltage digi-

tal inputs into current pulses that are returned on the SCAB. The same results are sent back on both circuits (0 and 1).

**4.08** The FA 776 SCAB register circuit pack stores the results of the scanner-detector circuit pack (FC 135 on FS 15), stores the ASW information, and provides the low voltage digital inputs to the cable drivers. The SCAB register circuits are always active and perform the same functions regardless of which scanner controller is active.

#### SCANNER CONTROLLER

4.09 To operate a scanner controller, an enabling pulse is sent from the CPD. This opens a gate, permitting the address to be received for 2.2  $\mu$ sec or for 0.4  $\mu$ sec after an address is received. At 2  $\mu$ sec after the start of the enabling pulse, the previously enabled pair is pulsed for 1  $\mu$ sec by the controller. This permits the CPD to verify that the enable pulses reach the correct equipment. A valid address results in a pulse on only one pair of wires in the LS and MS group of inputs (maintenance-test pair not pulsed). The PU bus circuit receives the address pulses and stores them in the address register and the access circuitry. The register and access circuitry translates LS and MS address inputs so that one of 64 rows of 16 ferrods is selected and interrogated. The outputs of the 16 ferrods are detected by the detector circuit and stored in the scanner-answer register. If there is less than the nonoperate current in the control windings of the ferrod, the output circuitry produces a pulse (1). If there is sufficient current in the control windings of the ferrod, the output circuitry will produce no pulse (0) when interrogated. The result of the interrogation (16 outputs) is transmitted simultaneously on both SCABs.

**4.10** The maximum operate time of the scanner is 2.2  $\mu$ sec. A scanner may be addressed at a minimum interval of 7  $\mu$ sec.

## C. Scanner Register and Access Circuit

**4.11** The function of the scanner register and access circuit is to provide a bipolar interrogate

pulse to the correct ferrod row. There are 64 rows of 16 ferrods that a scanner controller interrogates.

4.12 This circuit registers and translates the ad-

dress inormation, provides the all-seems-well (ASW) logic, and contains the logic for the enable and enable-verify circuitry. The timing for the scanner controller is also provided by this circuit.

**4.13** The ASW pulse is used to indicate that the scanner controller has interrogated only one ferrod row. If more than one row is pulsed due to faulty circuitry or because an invalid code is received, the ASW pulse is inhibited.

#### D. Scanner Power Circuit

**4.14** The scanner power circuit converts the +24 DC frame voltage to the +3 DC volts used for logic and timing functions.

#### E. Ferrod Matrix Circuit

4.15 The ferrod sensors, two per trunk, are arranged in two 16 by 32 matrices for a 1024-point scanner. The scanner matrix consists of miniaturized plug-in ferrods mounted on printed circuit packs (Fig. 6). These packs are distributed in the same housing as the trunks (Fig. 1). There is a particular scanner address associated with each row of 16 ferrods. All 16 ferrods in the row are interrogated simultaneously when an address is received from the central processor. The answers of the scanner busy/idle information for eight trunk circuits are returned to the central processor via the scanner detector circuit.

#### F. Scanner Detector Circuit

**4.16** A scanner detector board contains 16 circuits that detect the readout current of an unsaturated ferrod. An unsaturated ferrod, upon interrogation, causes current to flow in the readout loop.

4.17 Scanner detector boards also contain a transformer which is activated during a mainte-

nance test. The test verifies that the readout loop has continuity and that the detector works correctly.

## SIGNAL DISTRIBUTOR CONTROLLER

#### G. SD Buffer and Maintenance Circuit

**4.18** The SD buffer and maintenance circuit buffers the address signals from the bus circuit to

Fig. 6—Plug-In Ferrod Circuit Pack

the rest of the SD controller. This circuit is also used to control the state of the duplicated SD controllers (0 and 1).

4.19 Each SD cycle begins when the CC instructs the CPD to send an enable pulse to the SD controller. The enable pulse is received by the buffer circuit from either peripheral bus circuit 0 or 1. This enable sets an enable register. A pulse is sent over the control leads to the SD timing, pulse, and miscellaneous circuit which returns a pulse over the timing and pulse leads. This pulse is used as a timing window for the address registers to accept address information from the bus circuit. An enable-verify signal is sent back to the peripheral bus circuit.

4.20 System reset pulses are also sent via the pe-

ripheral bus circuit. If one of the enable registers is set, a pulse is sent to the SD timing, pulse, and miscellaneous circuit which returns pulses to reset the appropriate enable and address registers. Normally, these register reset pulses are sent at the end of the SD cycle and are caused by the armaturemovement register and the end-of-timing pulse being set.

**4.21** The address bits are divided into subgroups. Several subgroups are used to set registers which generate the horizontal and vertical select pulses sent to the interface circuit. The vertical selectors determine the location of the vertical column or trunk position of the relay to be controlled. The horizontal selection determines the horizontal mounting plate location of the relay to be controlled. One of the subgroups is used to determine whether a magneticlatching relay is going to receive an operate or release pulse. Another subgroup is used to determine which half of the SD (0 or 1) is to be activated. A third subgroup determines whether the controller is in the normal or maintenance mode. The operate/release pulses and the controller status information is transmitted to the SD timing, pulse, and miscellaneous circuit.

#### H. SD Timing, Pulse, and Miscellaneous Circuit

**4.22** The SD timing, pulse, and miscellaneous circuit is used to send pulses for creating timing windows, for operating relays, and for resetting registers. This circuit also includes some scan point driving circuits.

4.23 This circuit provides timing for the enable signals, relay pulser, triac selectors, and detection circuits. A pulse is sent to the SD buffer and maintenance circuit for use as a timing window to accept address information from the bus circuit.

4.24 The SD timing, pulse, and miscellaneous circuit supplies the -48 volt operate pulses needed to operate magnetic-latching relays. It sends +24 volt pulses over the same leads to release the relays. If the triac selection circuits have two or more relay paths selected, the operate or release pulses are

removed from the selected paths before the relays have time to operate or release.

4.25 This circuit also detects relay armature movement which is required before the enable and bit register resets are generated. The armature movement detector generates a pulse which is gated with the output of a double release detector. This can set a register which results in a controller failure for the cycle. Resets are not sent to the enable and address bit registers in the case of controller failure. A system reset pulse from the SD buffer and maintenance circuit is necessary to clear the controller for the next cycle.

**4.26** When the controller is put in the quarantine mode of operation, the SD timing, pulse, and miscellaneous circuit generates a pulse to operate the quarantine relay.

**4.27** Another function of this circuit is to reset all the registers when power is applied to the SD circuit. The SD controller always comes up in the quarantine mode when power is restored. Register reset pulses are also sent when a controller is placed in or out of the maintenance mode.

**4.28** Each controller has three dedicated scan points. The scan point driving circuits are located on the miscellaneous circuit. Inputs to the driving circuits come from the SD buffer and maintenance circuit. The miscellaneous circuit also contains the driving circuits for five common diagnostic master scanner points associated with all SD controllers. These five scan points become active only when the controller is in the test access mode.

## I. Interface Circuit

**4.29** The interface circuit provides for conversion between digital logic and the +24 volt selection circuits. This circuit also provides node isolation between normal and quarantine selection.

#### J. SD First Stage Triac Circuit

**4.30** The triac select circuit provides the triac gate current for the first and second stage supplementary triacs. It also contains the circuitry for selecting the triac gate current path in the first stage for the universal triac points. When the proper combination of inputs to the first stage triac circuit is made, a gate selection path is established for the first triac stage.

**4.31** The first stage triac circuit provides the first

of two stages of triac switches that make up the SD matrix. When gating occurs, a current is established through the triac and subsequently through a magnetic relay to ground.

**4.32** When the SD is equipped with option P, the

first stage triac circuit is replaced by first stage relays. These are small mercury relays mounted on circuit packs. The relays provide better isolation between selection circuitry and the SD matrix than triacs.

#### K. SD Second Stage Triac Circuit

**4.33** The second stage triac circuit consists of two types of circuits: the second stage triac selec-

tion and triac circuit and the second stage triac circuit. The second stage triac selection and triac circuit provides 24-second stage triacs and their associated selection circuitry. Sixteen of these triacs are used as supplementary points and eight triacs are used as universal points. The second stage triac circuit contains 40 triacs and the associated gating circuitry for 40 universal SD points.

#### L. SD Controller Logic and Timing

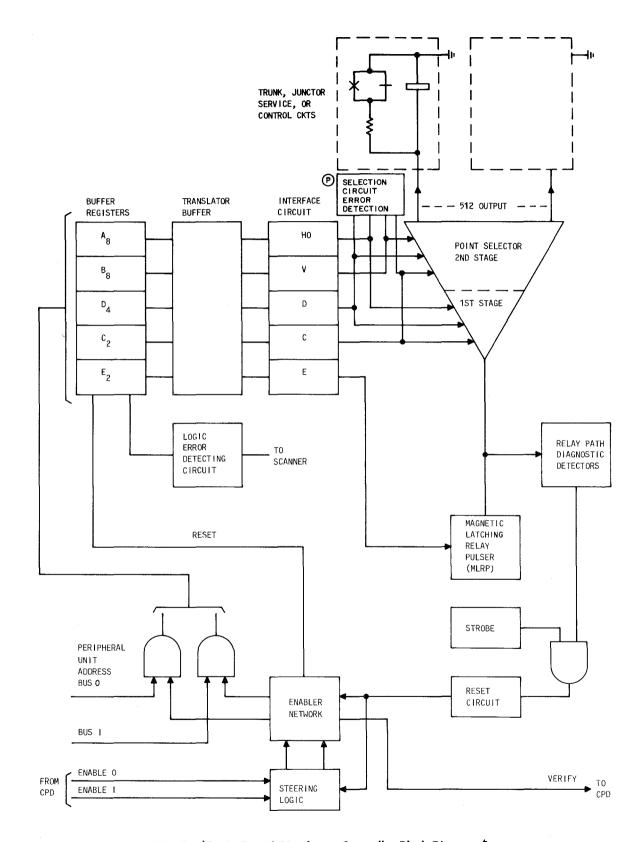

**4.34** The SD cycle begins when an enable signal is sent under direction of the central processor.

via the CPD, to a specified SD controller (Fig. 7). This enables the signal gates on the buffer registers via the enable network. The buffer registers store the address information for the duration of the operation cycle. Information stored in the buffer register is used to establish a path through the triac selector to a specified magnetic latching relay and to select the operate or release signal (E) from the magnetic latching relay pulser (MLRP). When the relay operation or release is sensed by the relay action detector, the enable registers in the enabler circuit and the buffer registers are reset. The controller is now prepared to receive a new order from the central processor.

- **4.35** The functions of the SD controller are as follows:

- (1) Receive address information from the central processor

- (2) Temporarily store address information

- (3) Check address and pulse path for errors ♦(with option P, also check first-stage selection circuit for errors)

- (4) Inhibit continued operation of the cycle when errors are found and report errors to the central processor

- (5) Establish a path through the triac selector

- (6) Verify that relays worked as intended.

If all circuit conditions are satisfied, the controller resets and awaits the next order.

- **4.36** As shown in Fig. 7, the controller contains the following circuits:

- (1) Steering logic circuit

- (2) Enabler

- (3) Buffer registers

- (4) Selector interface and translation buffer

- (5) Logic error detecting circuit

- (6) Path detector circuit (point selector)

- (7) Magnetic latching relay pulser

- (8) Relay path diagnostic detectors

- (9) Strobe circuits

- (10) Reset circuit.

**4.37** The steering circuit is used to direct the SD buffer register circuits to the proper bus for reception of address signals.

**4.38** The enabler circuit generates the time window during which address information can be received. The start of the window occurs when an enable pulse is received. The enable circuit also generates on termination of the address window an enable-verify signal that is sent to the central processor indicating that an enable signal had been properly received.

4.39 The buffer register is a 28-bit buffer used to store an address. The buffer register is broken down into seven subregisters, five of which are shown in Fig. 7. The registers are given an alpha designation with the numeric subscript indicating the number of bits in the register. The designations are A8, B8, D4,

C2, E2, H2, and T2. For a proper address to exist, each of these registers must have one and only one bit set. The A, B, C, and D registers designate the path through the selector, E designates the operation or release of the magnetic latching relay, H designates which of the two selectors in an SD is to be used (this will become more significant when combined mode operation is explained), and T specifies normal or maintenance operation during the cycle. With option P, both bits set in the T register is a valid address and specifies a special order used during diagnostics.

**4.40** The selector interface and translation buffer circuits convert the logic outputs from the buffer register into signals which are compatible with the gating of the selector circuit.

**4.41** The logic error detecting circuit determines if one and only one bit has been set in the buffer register. If an error has occurred, progress through the SD cycle is interrupted and the fault is reported to the CC.

4.42 One function of the relay path diagnostic detectors is to determine if one, and only one, path has been established through the selector. It also determines if two or more relays have been connected to a given selector output. With option P, it also determines if no relays have been connected. If a single path with a single relay is not indicated, the SD cycle is interrupted and the fault condition is reported to the CC.

4.43 The magnetic latching relay pulser generates

signals of the proper amplitude and duration for operating and releasing a magnetic latching relay. The relay path diagnostic detector has two functions in addition to the one described. One is to sense when the magnetic latching relay has worked as intended. This part of the circuit is called the armature movement detector. The detection of armature movement is used to indicate a successful cycle and to initiate the reset of the buffer registers. On the other hand, failure of armature movement indicates a faulty operation and is reported to the CC on the next cycle. The second function is used to sense when a release signal is being sent to an already released relay. This circuit is called a double release detector. Double release detection is important since second release under some circumstances can place a magnetic latching relay in an operated state. Then the CC would consider the relay released when it is actually

operated, and an intolerable situation would exist; hence, double releases must be detected and interrupted before operation of the relay can occur. The detection of double release is used to terminate the SD cycle. Since detection occurs early in the cycle, an operated relay will be avoided.

**4.44** The strobe circuit shown in Fig. 7 is used to mask out rapid voltage changes that occur on the selector path while the path is being established. These rapid voltage changes may cause false operation of the armature movement detector. The strobe gates the detector output only after sufficient time has elapsed to ensure that the chatter has disappeared.

4.45 The reset circuit is actuated if armature movement has been detected and the selection signal has been applied for a specified length of time. The reset circuit drives the enable and buffer register into a reset state.

## POWER AND MISCELLANEOUS CIRCUIT

4.46 The power and miscellaneous circuit provides +24, +48, and -48 volt filters and fuses for circuits on the frame. This circuit also provides ground, high resistance ground, -48 volts, and +24 volts to test-pin jacks for frame testing.

#### 5. MAINTENANCE AND DUPLICATION

5.01 Maintenance registers are provided for placing either of the two controllers in modes of operation other than normal. These modes are used under trouble conditions and/or to perform maintenance tests.

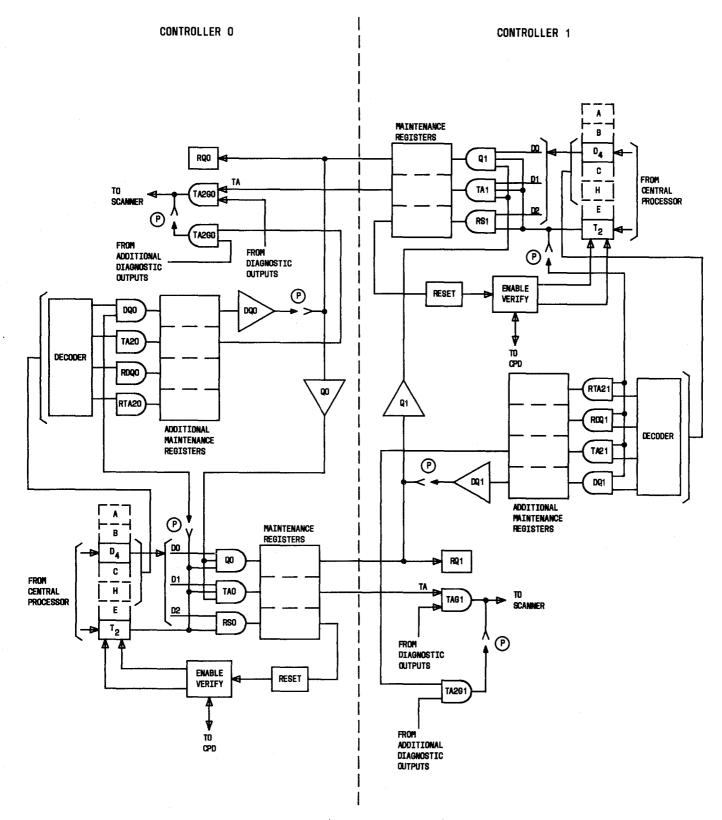

5.02 Maintenance addresses are indicated when the ♦D1 bit of the D24 register is set, as shown in Fig. 8. When the ♦D14 bit is set, the D4 register is used to indicate what maintenance function is to be performed. The D0 bit indicates a quarantine or an out-of-service mode is to be established, the D1 bit indicates a test access mode is to be established, and the D2 bit indicates the maintenance registers are to be reset.

5.03 Note that maintenance functions to be performed on the left-half controller are addressed to the right-half buffer register, and vice versa. The maintenance mode, once established, is maintained by the maintenance registers (Fig. 8) until the registers are released by direction of the CC which simultaneously sends a D14 and D2 bit.

5.04 When a controller is placed in the test access mode, its ability to operate and release magnetic latching relays is not affected. In the test access mode, scanner 00 is connected to check circuits within the SD. The check circuits of each controller are connected to the scanner via multiples that are common to all SD controllers and are referred to as the SD diagnostic bus.

5.05 While a controller is in the test access mode,

the addresses from the CC that are used for testing purposes may be incomplete; in which case, no path is closed through the selector. Each of these addresses is directed to the basic SD in which the test access mode has been established. The CC then inspects the test points via the master scanner. After each test, the CC resets all circuits in the controller by signaling over an appropriate path provided in the PUAB.

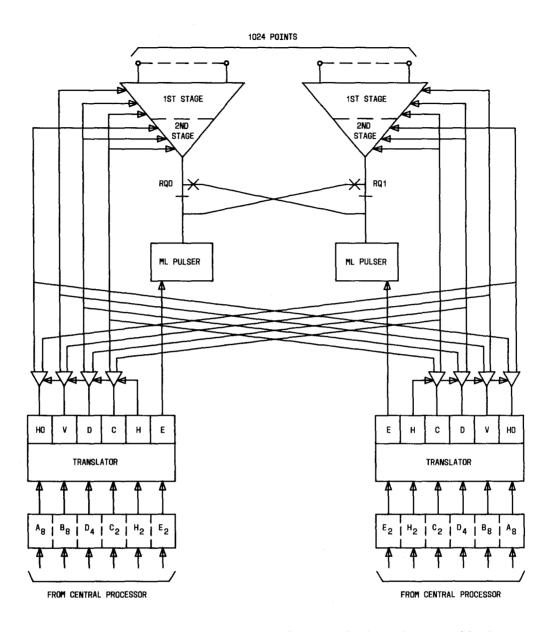

When a controller is placed in guarantine, it 5.06 is removed from service. The other controller is given full access to both selectors. (This is called the combined mode of operation.) The in-service controller has the capability of making a 1-out-of-1024point selection and controlling any of the magnetic latching relays connected to the two selectors. Assume the left controller is guarantined; the right controller can complete a path to any one of the 1024 output terminals (Fig. 9). The H section of the buffer register controls the half of the selector in which a pulse path is established. In all modes of operation, the address from the CC contains selections of the H section of the buffer register. However, only one controller can control all of the outputs if the other controller is in guarantine. Control connections between opposite halves are established only when one of the quarantine relays, \$RQ0 or RQ1. is operated (Fig. 8) and 9).

5.07 Provisions have been made so that a controller can be manually quarantined. Manual quarantine is established automatically when power is removed from one of the controllers. A mechanical lock-out feature is provided to eliminate the possibility of manually removing power from both controllers at the same time.

**5.08** To return an SD from a combined mode of operation to split mode, the CC addresses the

Fig. 8—\$Maintenance Logic\$

Fig. 9—1024-Point Signal Distributor with Selection and Pulse Path Required for Combined Mode Operation

buffer register such that the D2 and T1 bits are set. This results in the maintenance registers being cleared.

5.09 The controlling circuitry of the SD distributor is duplicated, but not in the sense that one controller operates the whole SD while the other stands by ready to take over. Normally, one controller offers access to one-half of the output terminals, while the other controller offers access to the other half.

5.10 In each controller, the buffer registers are equipped to accept an address from either of the duplicated PU buses. Each controller has two enable inputs through which the CC determines the bus from which address information is to be registered and to which SD, of the many possible SDs in an office, the address is to be sent.

5.11 When the SD is equipped with options P, Q, and S, there are significant additions to the maintenance functions of the SD. Options P, Q, and S provide SD controller packs, wiring, and second-stage triac circuit packs for the improved minitrunk signal distributor diagnostic (IMD) feature. This feature provides improved fault detection and isolation, as well as some maintenance improvements. In addition to maintenance functions described in the above paragraphs, IMD also provides functions as described in the following paragraphs.

5.12 Besides maintenance states of normal, quarantine, and test access mode, IMD provides double quarantine and a second test access mode called TPA2. The original test access mode is renamed TPA1. There are also two additional reset orders. One is Release Double Quarantine, which takes the controller which is in double quarantine and puts it into quarantine mode. The second reset is Release TPA2, which takes a controller out of TPA2 and puts it into TPA1.

5.13 Unlike quarantine and TPA1, maintenance functions of double quarantine and TPA2 are addressed to the controller which is under test. For example, the order to put the left-half controller into double quarantine is sent to the left-hand controller. These maintenance modes are maintained by maintenance registers until an appropriate reset order is sent.

5.14 It should be noted that in order to put a controller into double quarantine, it must first be in quarantine mode. Similar conditions are used for TPA2. A controller must be in TPA1 before it is put into TPA2.

5.15 Double quarantine mode allows both controllers full access to all 1024 SD points. It is used

during SD diagnostics so that one controller can operate and release all 1024 trunk and service circuit relays while the other controller is being thoroughly checked by the diagnostic program. The controller in double quarantine is considered out of service to the call processing program. When either controller is in double quarantine, both out-of-service lamps will be illuminated and both quarantine relays will be operated.

5.16 The TPA2 mode provides more test points which can be monitored. The TPA2 uses the same SD diagnostic bus as TPA1.€

#### 6. POWER AND MISCELLANEOUS CIRCUITS

6.01 These circuits provide filters, fuses, and a means to remove power from the MUT frame. Abnormal conditions within the frame are reported to the system via scan points, and visual and audible alarms are also initiated. These circuits also provide test-pin voltage jacks and a means of communicating between frames.

#### FRAME LINE TELEPHONE JACKS

6.02 This circuit provides means of communicating between the MUT frame and other frames in the ESS switch. The telephone jacks are located on the extreme left-hand side of the left bay control panel (Fig. 1). The local frame line is located in the line and trunk test bay of the master control center. The telephone head set, when plugged into the telephone jacks, completes the talking path. The local frame line has no means of signaling.

#### SPARE JACK

**6.03** This circuit provides a 3-wire belt line around the office for miscellaneous use. The jack is located on the left bay control panel next to the telephone jack (Fig. 1).

## **TEST-PIN JACKS**

6.04 These circuits provide ground, high resistance ground, and -48 and +24 volts for testing in

the frame. These jacks are located on the left bay control panel and provide access from both front and back of the frame.

#### FILTERS, FUSES, AND FUSE ALARM CIRCUITS

6.05 These circuits provide +24, +48 and -48 volt filters and fuses for circuits on the MUT frame. The +24TBS and -48TBS non-alarm fuses provide voltage for the test-pin jacks on the frame. The +24LP non-alarm fuses provide voltage through the +24LP leads, to the fuse alarm scan point SC00, to the PWR OFFL and PWR OFFR lamps, and to other lamps on the frame.

- 6.06 The failure of any alarmed fuse on the frame will operate the FA relay and

- (1) Light the PWR OFFL and PWR OFFR lamps

- (2) Signal the major alarm to the office alarm circuit through leads ABG and MJ

- (3) Indicate a failure via scan point SC00.

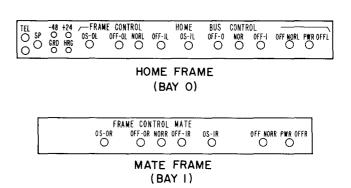

#### 7. TAKING EQUIPMENT OUT OF SERVICE

7.01 Only one of the two controllers of an SD or scanner can be taken out of service at any time. This is accomplished by the system when it has been requested to do so via the teletypewriter. Once a controller has been removed from service, power to it can be removed by operating the appropriate FRAME CONTROL OUT-OF-SERVICE key. The system should always be requested to remove both the left SD and scanner controllers before the HOME FRAME CONTROL OUT-OF-SERVICE key is operated because the HOME FRAME CONTROL OUT-OF-SERVICE key controls both the left SD and both scanner controllers. The appropriate out-of-service lamp will light when the system quarantines (removes from service) the controller. The out-of-service keys override any frame condition previously established. The system is able to determine the state of the controllers by the state of the S, F, and T scan points assigned to it. The home and mate bay control panels are shown in Fig. 10.

7.02 Whenever a request has been made to take a controller out of service, it remains out of service until a request has been made to the system via the teletypewriter to restore it to service.

#### Fig. 10—Home and Mate Frame Bay Control Panels

## ABBREVIATIONS AND ACRONYMS

SD

8.01 Abbreviations and acronyms used in this section are listed below.

| ASW  | All-Seems-Well                                        |

|------|-------------------------------------------------------|

| ASWS | All-Seems-Well Scanner                                |

| CC   | Central Control                                       |

| CPD  | Central Pulse Distributor                             |

| IMD  | Improved Minitrunk Signal Dis-<br>tributor Diagnostic |

| LS   | Least Significant                                     |

| MLRP | Magnetic Latching Relay Pulser                        |

| MS   | Most Significant                                      |

| МТ   | Maintenance Test                                      |

| MUT  | Miniaturized Universal Trunk                          |

| PU   | Peripheral Unit                                       |

| PUAB | Peripheral Unit Address Bus                           |

| SCAB | Scanner Answer Bus                                    |

|      |                                                       |

Signal Distributor.

Fig. 11-MUT Functions Block Diagram (SD-1A338-02)

Page 19 19 Pages