# PERIPHERAL UNIT CONTROLLER DIGITAL CARRIER TRUNK AND DATA LINK DESCRIPTION AND MAINTENANCE CONSIDERATIONS NO. 1 AND NO. 1A ELECTRONIC SWITCHING SYSTEMS

|    | CONTENTS                          | PAGE | CONTENTS                                                | AGE |

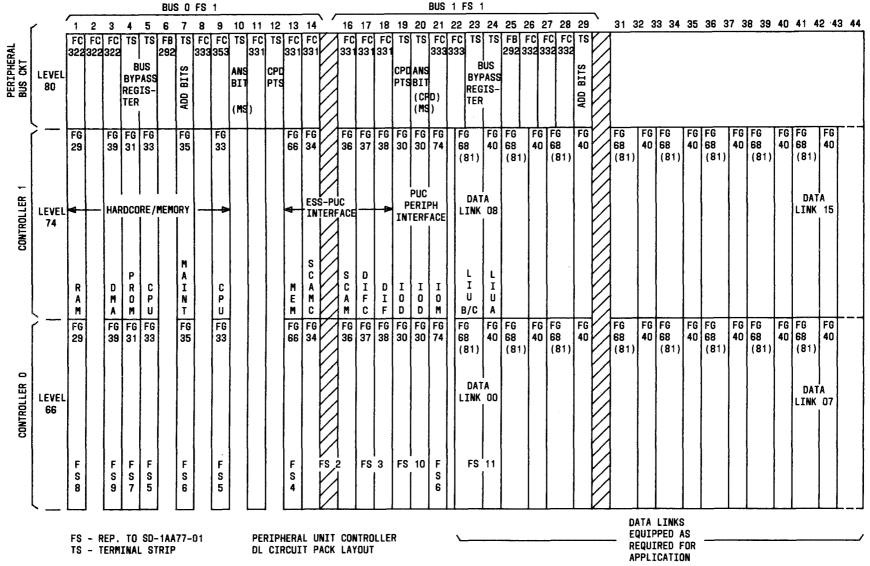

|----|-----------------------------------|------|---------------------------------------------------------|-----|

| 1. | GENERAL                           | . 3  | E. Order Hopper                                         | 17  |

| 2. | PERIPHERAL UNIT CONTROLLER        | . 3  | F. Link Table                                           | 17  |

|    | MICROPROCESSOR CONTROLLER         | . 3  | G. Firmware Counts                                      | 17  |

|    | A. Interface                      | . 3  | H. Parameters                                           | 17  |

|    | B. Hardcore                       | . 7  | I. Digroup Buffers in Service                           | 18  |

|    | C. Controller Memory              | . 7  | J. Address Block                                        | 18  |

|    | D. Internal Buses                 | . 8  | K. Conversion Tables for Trunk and Chan-<br>nel Numbers | 18  |

|    | E. Peripheral Interface           | . 8  | L. Conversion Tables for State Designa-                 |     |

|    | POWER BUS AND CONTROL             | . 8  | tions                                                   | 18  |

| 3. | OPERATION                         | . 8  | M. Miscellaneous Data Tables                            | 18  |

| 4. | MAINTENANCE CAPABILITIES          | . 8  | INPUT FORMAT                                            | 18  |

|    | PERIPHERAL UNIT PARITY            | . 9  | OUTPUT FORMAT                                           | 18  |

|    | FIRMWARE UPDATING                 | . 12 | DIGROUP ORDERS AND MESSAGES                             | 18  |

| 5. | DIGITAL CARRIER TRUNK APPLICATION | . 13 | 6. DATA LINK APPLICATION                                | 18  |

|    | DATA STRUCTURES                   | . 17 |                                                         | 22  |

|    | A. Digroup Register               | . 17 | A. Timing                                               | 22  |

|    | B. Trunk Register                 | . 17 | B. Input                                                | 22  |

|    | C. Pulsing State Register         | . 17 | C. Audits                                               | 26  |

|    | D. Timing Structures              | . 17 | PROTOCOL BLOCK ROUTINES                                 | 27  |

# NOTICE

Not for use or disclosure outside the Bell System except under written agreement

Printed in U.S.A.

|              |            | CONTENTS                                                          | PAGE     |  |

|--------------|------------|-------------------------------------------------------------------|----------|--|

|              | Α.         | Communicate                                                       | 27       |  |

|              | B.         | Handshake                                                         | 27       |  |

|              | C.         | Switch Links                                                      | 27       |  |

|              | D.         | Line Interface Units Diagnostics                                  | 27       |  |

|              | PROC       | GRAM TIME SEQUENCE                                                | 27       |  |

|              | INPU       | IT FORMAT                                                         | 29       |  |

|              | <b>A</b> . | Data Messages                                                     | 29       |  |

|              | В.         | Maintenance Messages                                              | 30       |  |

|              | OUT        | PUT FORMAT                                                        | 30       |  |

|              | Α.         | Incoming Data from Data Links                                     | 31       |  |

|              | B.         | Maintenance Messages                                              | 31       |  |

|              | С.         | Special Indicators                                                | 31       |  |

|              | PAR/       | AMETERS                                                           | , . 31   |  |

|              | Α.         | General Parameters                                                | 32       |  |

|              | B.         | Destination Paraameters                                           | 35       |  |

|              | С.         | Data Link Basic Parameters                                        | 35       |  |

|              | D.         | Data Link Protocol Parameters .                                   | 35       |  |

|              | E.         | Parameter Table                                                   | 36       |  |

| 7.           | REFE       | RENCES                                                            | 36       |  |

| 8.           | ABB        | REVIATIONS                                                        | 36       |  |

| Figur        | 'es        |                                                                   |          |  |

| 1.           |            | ripheral Unit Controller/ Data Link<br>gital Carrier Trunk Frames | and<br>4 |  |

| <b>, 2</b> . | In         | terface Bus Circuit                                               | 5        |  |

| 3.           | Pe         | ripheral Unit Controller Block Diagra                             | ım       |  |

|              |            |                                                                   | 6        |  |

| 4.           | Ро         | wer Distribution                                                  | 9        |  |

| 5.          | Power and Alarm Control Unit                                                      | 10 |

|-------------|-----------------------------------------------------------------------------------|----|

| 6.          | Peripheral Unit Controller/Digital Carrier<br>Trunk Block Diagram                 | 14 |

| 7.          | Peripheral Unit Controller—Digital Carrier<br>Trunk Circuit Pack Layout           | 15 |

| 8.          | Peripheral Unit Controller Program Cycle for<br>Digital Carrier Trunk             | 16 |

| 9.          | Digital Carrier Trunk Input Operational<br>Orders, General Form                   | 19 |

| 10.         | Digital Carrier Trunk Input Maintenance<br>Order, General Form                    | 20 |

| 11.         | Digital Carrier Trunk Output Operational<br>Messages, General Form                | 20 |

| 12.         | Single Word Digital Carrier Trunk Output<br>Maintenance Message, General Form .   | 21 |

| 13.         | Multiple Word Digital Carrier Trunk Output<br>Maintenance Message, General Form . | 21 |

| 14.         | Digital Carrier Trunk Digroup Order and<br>Message, General Form                  | 22 |

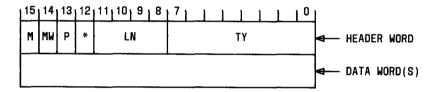

| 15.         | Peripheral Unit Controller—DL Circuit Pack<br>Layout                              | 23 |

| 16.         | Peripheral Unit Controller/Data Link Block<br>Diagram                             | 24 |

| 17.         | Peripheral Unit Controller/Data Link Firm-<br>ware Structure Simplified           | 25 |

| 18.         | Peripheral Unit Controller/Data Links Destination Buffer Structure                | 26 |

| 19.         | Peripheal Unit Controller/Data Link Main<br>Program Cycle                         | 28 |

| 20.         | Peripheral Unit Controller/Data Link Input<br>Format                              | 30 |

| <b>21</b> . | Input Heading Control Field                                                       | 31 |

| 22.         | Input Data Message                                                                | 32 |

CONTENTS

PAGE

|        | CONTENTS PAGE                                                              |

|--------|----------------------------------------------------------------------------|

| 23.    | Scan Memory Layout                                                         |

| 24.    | Structure of Peripheral Unit Controller/Data<br>Link Application Parameter |

| Tables |                                                                            |

| ۸      | Valid Pasinharal Unit Controllar Occural                                   |

# 1. GENERAL

States

1.01 This section describes the peripheral unit controller (PUC) when used with the No. 1 or the No. 1A Electronic Switching Systems (ESS). The PUC (J1A098B-1) is a universal microprocessor controller which provides control of certain frames of equipment. For example, the PUC controls the digital carrier trunk (DCT) frame and data link information for the Remote Switching System (RSS), electronic tandem switching (ETS), and common channel interoffice signaling (CCIS).

**1.02** This section is reissued for the reasons listed below. Revision arrows are used to emphasize the more significant changes. Equipment Test Lists are not affected.

- (1) Add information related to the scanner answer memory

- (2) Add information for internal buses

- (3) Add information related to the power bus and control

- (4) Add information related to the peripheral unit parity feature

- (5) Add information related to the digroup buffer circuit.

- **1.03** Abbreviations used in this section are listed in Part 8.

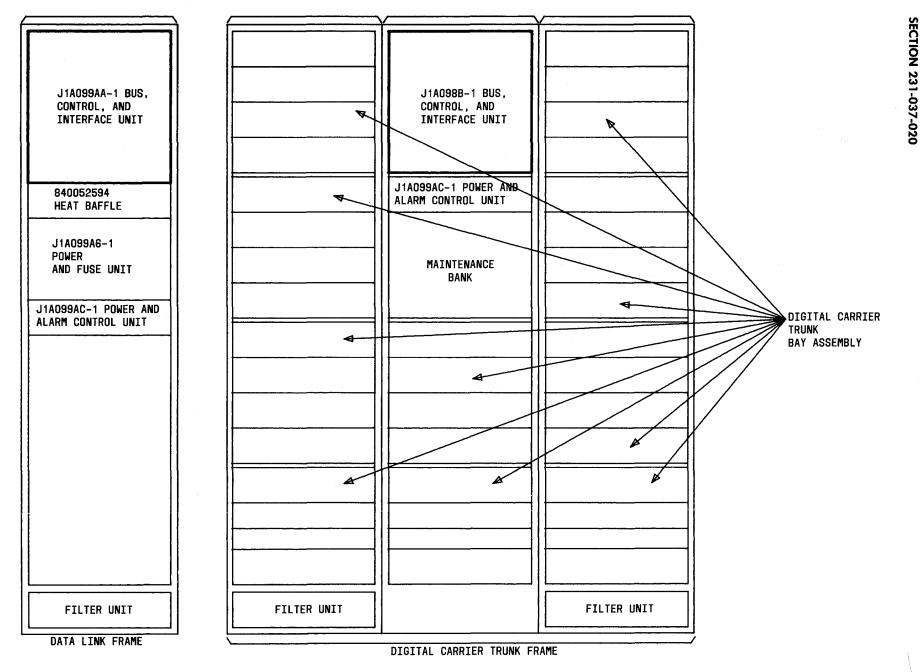

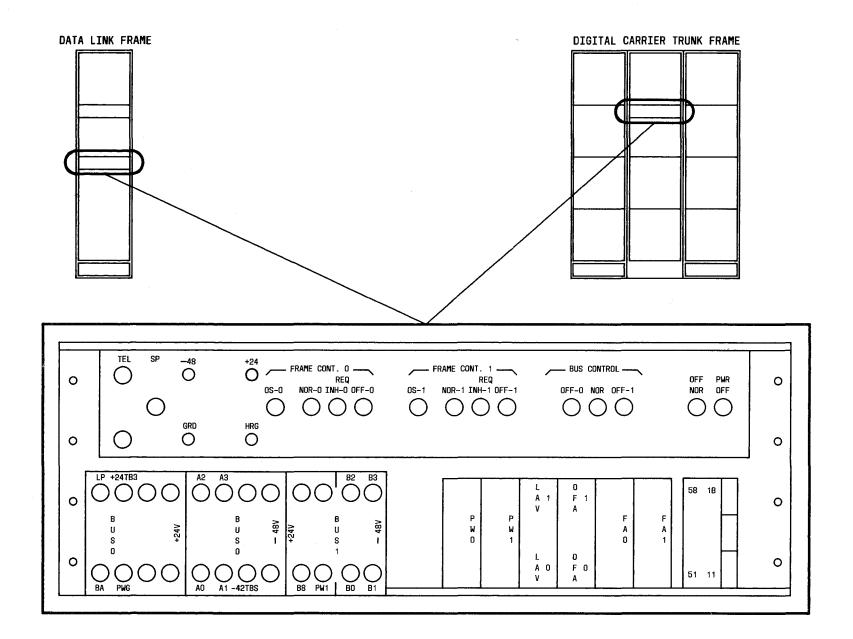

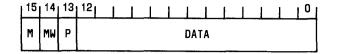

1.04 The PUC mounts in a standard universal trunk frame and is 24 inches high. It is a selfcontained, pluggable unit, equipped with its own power supplies, control panel, and fusing. The PUC is used in a one bay frame for the data link (DL) application and a three-bay frame for the DCT application (Fig. 1).

# 2. PERIPHERAL UNIT CONTROLLER

11

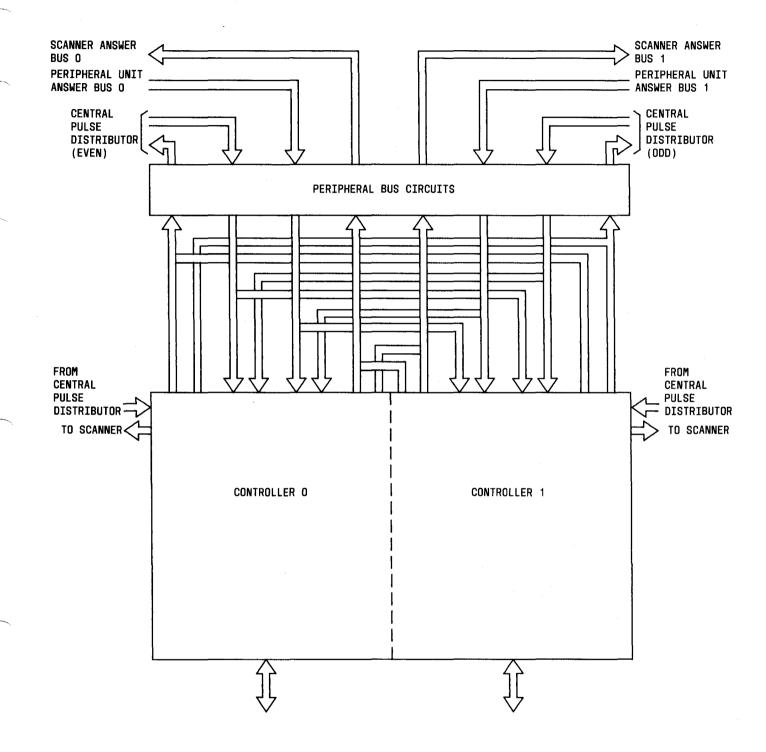

2.01 Orders and signaling information are sent to the PUC via the peripheral unit address bus (PUAB) and central pulse distributor (CPD) (Fig. 2). The communication loop is completed with the re-

sponse messages returned to the ESS on the scanner answer bus (SCAB). The peripheral bus circuit contains the bus receivers and drivers. Operational orders and maintenance orders are sent to the PUC, and either by command or timing are acted upon with a reply message returned via the SCAB. The reply messages contain operations completed, maintenance data, error alarms, and audit reports.

2.02 ♦Each PUC frame in an ESS office requires 44 unipolar and 12 bipolar CPD points plus 24 scan points of which 20 are direct and 4 superviosry.

#### MICROPROCESSOR CONTROLLER

A PUC frame consists of two identical micro-2.03 processor based controllers. In normal operation both controllers run in a matched mode (DUPLEX) executing identical instruction streams. Controllers are synchronized by means of a shared clock. Each controller receives orders from the ESS and executes the commands. The processing is performed and outputs are matched, but only the controller designated as active outputs to the system. In case of a failure the other controller would be configured to be the output device. The controller hardware is mounted on plug-in circuit packs which insert into two shelves with the power bus and converters as a part of the PUC. The bus interface units are mounted in a third shelf at the top of the PUC.

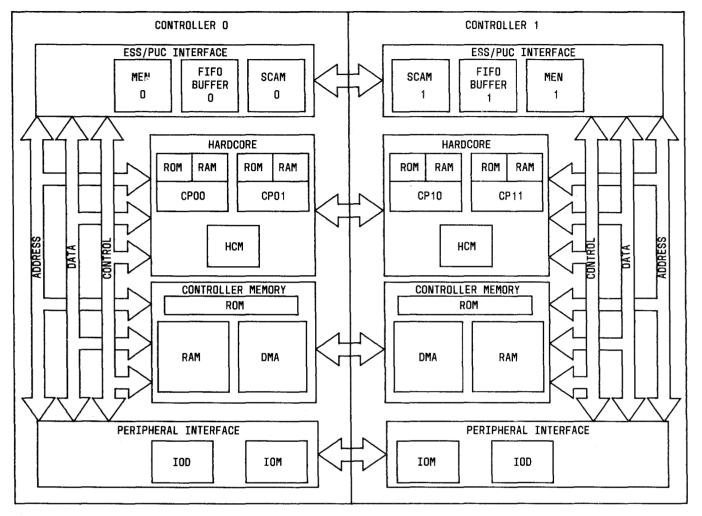

2.04 Each PUC controller (Fig. 3) consists of four functional areas—the ESS/PUC interface, hardcore, memory, and the PUC/peripheral interface.

# A. Interface

2.05 The ESS/PUC interface consists of a mode and enable (MEN) circuit, a first in-first out (FIFO) buffer, and a scanner answer memory (SCAM).

Fig. 1—Peripheral Unit Controller/ Data Link and Digital Carrier Trunk Frames

Page 4

Fig. 2—Interface Bus Circuit

LEGEND:

- **CP CENTRAL PROCESSOR** DMA - DIRECT MEMORY ACCESS FIFO - FIRST IN FIRST OUT

- HCM HARDCORE MATCHER

- IOD INPUT OUTPUT DECODER

- IOM INPUT OUTPUT MATCHER

- MEN MODE AND ENABLE

SCAM - SCANNER ANSWER MEMORY

- RAM RANDOM ACCESS MEMORY

- ROM READ ONLY MEMORY

- Fig. 3—Peripheral Unit Controller Block Diagram

2.06 ♦The MEN circuit allows the ESS to monitor and control the maintenance states of the controller, enable the FIFO buffer, and monitor the controller for failures. It also controls the out-of-service lamps on the power and alarm control unit.

2.07 The MEN circuit contains a set of mode flipflops which allows the ESS to control and monitor the maintenance states of the associated PUC controller. These flip-flops are called master, lockout, scanner answer bus access, and divorce. Master flip-flops are duplicated and matched for reliability. When both master flip-flops are set, the associated controller has access to the peripheral units. In addition to ESS control, the PUC hardcore may also change the state of the master flip-flops. When the lockout flip-flop is set, the hardcore is prevented from changing the master flip-flops. When the scanner answer bus access flip-flop is set, the PUC controller has access to the scanner answer bus thus allowing the associated SCAM to return data to the ESS. When the divorce flip-flop is set, the enable inputs to the FIFO buffer are inhibited and no ESS orders are input to the FIFO buffer.

2.08 The FIFO buffer enable circuit receives enables from the ESS and produces the necessary signals to load the FIFO buffer from the PUAB.

2.09 The MEN circuit contains four failure flipflops controlled by the hardcore plus scanner drivers which allow the ESS to monitor the state of the failure flip-flops. These flip-flops may be reset by the ESS or PUC. Internal fault flip-flops are set when any fault in the controller processor is detected by hardware. There is one internal fault flip-flop for each of the two controller processors contained in the hardware. The SCAM failure flip-flop is set when the hardware detects any fault in the SCAM. The hardcore failure flip-flop is set when a mismatch between hardcores is detected.

2.10 The FIFO buffer, also called the data input FIFO buffer (DIF), consists of a memory with the control circuitry required to make it a first infirst out queue. ESS orders are input to the FIFO buffer from the PUAB. The FIFO buffer is controlled by the ESS via the MEN circuit. The ESS orders are unloaded periodically by the hardcore. The hardcore controls the FIFO buffer using the DIF controller (DIFC) circuit. The ESS sends a 24-bit word to be loaded but the PUC hardcore unloads them in 8-bit words. 2.11 Sixteen-bit reply and maintenance messages are sent from the hardcore to the SCAM. The SCAM consists of random access memory (RAM) which temporarily stores data. The ESS sends enable signals and addresses to return data via the SCAB. The SCAM controller (SCAMC) controls the loading and unloading of the SCAM.

2.12 The SCAM circuitry returns a 16-bit data word, an all seems well (ASW) bit, a parity bit, and a check bit back to the ESS over the SCAB. The ASW bit is used to indicate that the scanner circuit has functioned properly and that the information being sent to the ESS CC is correct. The parity and the check bit are returned for the PUP feature (paragraph 4.06).◀

#### B. Hardcore

2.13 The controller hardcore consists of two central processors (CPs) and associated memory.A hardcore matcher is also included.

2.14 The central processor is a BELLMAC\*-8 microprocessor. This microprocessor runs on a program contained in its read only memory (ROM).

2.15 The hardcore memory consists of RAM and ROM for each individual central processor. The RAM stores transient data for the processor. The ROM is in the form of erasable programmable read only memory (EPROM). This memory stores the program for the processor and can only be read. The EPROM is used so that the circuit pack can be reused if a program change is made (see paragraph 4.09).

2.16 The hardcore matcher (HCM) compares the two central processor outputs for fault detection.

### C. Controller Memory

2.17 The controller memory consists of RAM, a direct memory access (DMA), and ROM. The RAM is used to store transient data associated with the controller. The DMA is used to update the RAM of a controller which is being brought back in service. The DMA copies the RAM contents of the active controller into the RAM of the controller being initialized. The ROM is in the form of EPROM and is programmed with application firmware.

\*Trademark

# D. Internal Buses

2.18 The internal PUC bus system consists of an address bus, data bus, and control bus. The address bus is used to communicate the address of memory locations for read and write operations. The data bus consists of eight data bits and one even parity bit. The bus is bidirectional and the direction of data transfer is determined by the system's read and write control signals. The control bus communicates control signals and fault indications. ♦

# E. Peripheral Interface

2.19 The PUC/peripheral interface consists of an input-output decoder (IOD) and an input-output matcher (IOM).

2.20 The IOD decodes commands from the PUC to be used by the peripheral circuits. It also sends enables to the line interface units used for DL applications. The IOM compares certain outputs of the controllers before being sent out to the peripheral units.

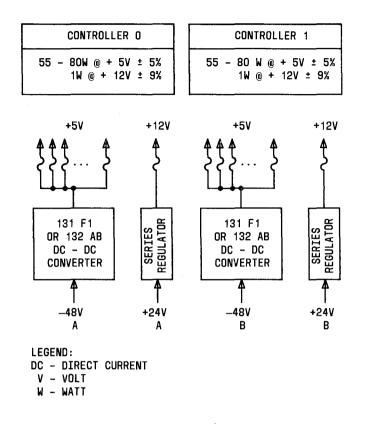

# POWER BUS AND CONTROL

2.21 The power is provided to converter packs located on the right side of the shelf for DCT and below the PUC for the DL application. Distribution of +5 and +12 volts to the circuit packs is handled by the converters and regulators (Fig. 4). Power indicators and manual switches are provided on the control panel (Fig. 5). Test jacks are provided to measure power levels at the panel. The PUC controllers (called controller 0 and 1) are supplied by a separate power bus for reliability. This arrangement allows one controller to be removed for maintenance with no interruption of power to the other controller.

2.22 ♦Only one of the two PUC controllers or data buses can be taken out of service at any time. This is accomplished by the system and can be requested manually by maintenance personnel or automatically requested due to faults detected by the system. The manual request is made via the teletype or by operating the REQ INH key on the PUC power alarm control unit (Fig. 5). The out-of-service lamp will light when the system takes the controller out of service for any reason. The actual removal of power can only be done manually at the PUC power and alarm control unit by operating the appropriate OFF key for either the controller or data bus circuit. The power removal and restoral procedure is contained in Section 231-105-302.

# 3. OPERATION

**3.01** The PUC is a general purpose, microprocessor

based controller. The operation of the PUC is different for the different applications depending on the application firmware. However, there are some operations which remain the same for different applications such as the maintenance operations for the microprocessors. For all applications, the PUC operates autonomously using its own timing clock. The PUC receives information from the ESS but acts on the information at the appropriate time in the PUC's program cycle. Returning data from the PUC is accomplished by normal scan orders.

#### 4. MAINTENANCE CAPABILITIES

- **4.01** The maintenance functions of the PUC may be classified as follows:

- Fault detection and location

- Reconfiguration and recovery.

**4.02** Fault detection and location is achieved through hardware fault detection circuits (matching circuits, parity checks, etc), and by frequent self-diagnostic tests.

The PUC has two controllers -one active and 4.03 one standby-that normally run in a duplex mode fully synchronized and continuously matched to each other. Each controller contains two microprocessors. Each controller is self-checking, using its own internal diagnostic routines, and the microprocessor's outputs are simultaneously matched to detect faults in the instruction sequence. Faults not detected internally by the microprocessors will be recognized (within microseconds) by the mismatch. This mismatch triggers a diagnostic. Matching is performed on two levels: between the two PUC controller outputs and internally in the hardcore modules. There are also automatically run background diagnostics built into the firmware. Most of the maintenance firmware resides in the HC ROM. Some maintenance firmware is in the controller ROM.

# **4.04** Reconfiguration of controllers is automatically done if the active controller is deter-

mined faulty. The reconfigured operation would put

#### ISS 3, SECTION 231-037-020

#### Fig. 4—Power Distribution

the other controller in the active state. If both controllers are diagnosed to have faults, the active controller will continue to output data and signaling for system operation while the out-of-service controller runs diagnostics. The ESS monitors the PUC diagnostics and may request certain diagnostics. The ESS also has ultimate CPD control and can reconfigure the PUC contrary to the PUC controllers. Teletypewriter (TTY) messages indicating PUC faults are output at the time of occurrence via PUC error messages. These faults may be transient in nature causing no reconfiguration or may be hard faults which cause the PUC to reconfigure as part of a recovery action. Controller states are automatically changed by the system to the preferred state; however, they may be changed by maintenance personnel using TTY input messages (IM1A001 or IM6A001). See Table A for the valid PUC states.

4.05 The PUC diagnostic is a special purpose program designed to test the PUC and aid maintenance personnel in locating any hardware faults that might be present. The maintenance procedures for the PUC/DCT are contained in task oriented

practice (TOP) 231-050-015. The maintenance procedures for the PUC/DL are contained in TOP 231-050-027. PK-1A473 is a tutorial and reference manual on how to use the PUC diagnostics in a No. 1 ESS.

#### PERIPHERAL UNIT PARITY

Peripheral unit parity (PUP) is a maintenance 4.06 feature which provides parity checking on the SCAB associated with the PUC. The PUP feature requires two additional bits on the duplicated SCAB. One bit is a parity bit which is pulsed whenever the parity over the 16 data bits is even. The other bit is a parity check request bit which is pulsed whenever the PUC identifies itself as a circuit. Pulsing the parity check request bit causes the central control (CC) and signal processor (SP) to check the parity of the 16 data bits and the parity check bit. If the parity check indicates an error, a maintenance interrupt will occur to call in the recovery programs to resolve the problem. Also, an associated interrupt printout message informs the maintenance personnel of the trouble condition that occurred. The CCs and SPs compute the parity of the SCAB without the parity

Fig. 5—Power and Alarm Control Unit

Page 10

# TABLE A

# VALID PERIPHERAL UNIT CONTROLLER OVERALL STATES

| STATE NAME (NOTE)   | DESCRIPTION OF STATE                                                                                                                                                                                                                                                                                                                                   |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACTIVE:STBY-SUPPORT | The PUC is running matched between controllers. Both controllers receive all orders from ESS but only the defined ACTIVE controller sends orders to shared periphery.                                                                                                                                                                                  |

| ACTIVE:OS-OFF-LINE  | The controller designated ACTIVE performs the operational function<br>of the PUC while the OS-OFF-LINE controller is being used by<br>maintenance programs for testing (diagnostics). The OS-OFF-LINE<br>controller will be automatically returned to service if a fault occurs on<br>the active controller.                                           |

| ACTIVE:OS-MANUAL    | The controller designated ACTIVE performs the operational functions<br>of the PUC while the OS-MANUAL controller is available for mainte-<br>nance and test programs. The OS-MANUAL controller will be<br>returned to service if a fault occurs (ERR-ANALYSIS) in the ACTIVE<br>controller.                                                            |

| ACTIVE:OS-FAULT     | The controller designated ACTIVE performs the operational functions<br>of the PUC while the OS-FAULT controller has been diagnosed to<br>have a fault. The OS-FAULT controller will be returned to service<br>(ACT-MR) if the ACTIVE controller fails.                                                                                                 |

| ACTIVE:OS-RMVD      | The ACTIVE controller performs the operational functions of the<br>PUC while the OS-RMVD controller, having a possible fault, is being<br>diagnosed. Upon completion of diagnostics the OS-RMVD controller<br>moves to the appropriate permanent state.                                                                                                |

| ACTIVE:UNAV-FORCED  | While the ACTIVE controller is operational, the UNAV-FORCED<br>controller has, by maintenance personnel action, been removed from<br>automatic system use. The UNAV-FORCED controller is left in a<br>maintenance access mode.                                                                                                                         |

| ACT-MR:OS-FAULT     | Both controllers are known to be faulty. The ACT-MR is used for<br>operation with all fault detection turned off. The OS-FAULT<br>controller, also known to have a fault, is locked out.                                                                                                                                                               |

| ACT-MR:OS-RMVD      | Both controllers have failed. The ACT-MR controller is known to<br>be faulty, but is used for operation with all fault detection turned<br>off. The OS-RMVD controller, also having failed, is awaiting execution<br>and completion of the diagnostic to move to a permanent state.                                                                    |

| ACT-MR:UNAV-FORCED  | The ACTIVE controller has failed while the support controller<br>(UNAV-FORCED) is unavailable to the system. All maintenance is<br>removed from the active controller (ACT-MR). The UNAV-FORCED<br>controller was removed from system use by maintenance personnel<br>action and will remain so until future maintenance personnel action<br>is taken. |

| ACTIVE:OS-PWR-OFF   | The ACTIVE controller performs the operational functions of the PUC. The OS-PWR-OFF controller has power removed.                                                                                                                                                                                                                                      |

| PWR-OFF:PWR-OFF     | Both controllers have power removed.                                                                                                                                                                                                                                                                                                                   |

# TABLE A (Contd)

| STATE NAME (NOTE)  | DESCRIPTION OF STATE                                                                                                                                                                                                 |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACT-MR: OS-PWR-OFF | The designated ACT-MR has a fault but attempts to perform the operatinal function of the PUC. The second controller has power off.                                                                                   |

| ACTIVE: OS-PWR-OFF | (Last state return). The OS-PWR-OFF controller has power off. After<br>power is restored, it will return to the OS state it was in prior to<br>power removal.                                                        |

| ACT-MR: OS-PWR-OFF | (Last state return). The ACT-MR controller attempts to perform the operational function for the PUC. The second controller has power off but will return to the OS state in which it resided prior to power removal. |

#### VALID PERIPHERAL UNIT CONTROLLER OVERALL STATES

*Note:* The first state name is defining one controller and the second state name (after the colon) is defining the second controller.

check bit and match the results. This parity match provides more immediate detection of certain classes of PUC troubles before they result in C-level interrupts. In addition to the 16 data bits and the 2 PUP bits there is an all seems well (ASW) bit on the SCAB.

4.07 ♦The hardware modifications required to install the PUP feature in a No. 1 ESS office consists of a central control circuit SD-1A105 and a communication bus circuit SD-1A119. The central control circuit equips the CC for communications with the peripheral units. The communication bus circuit provides for maintenance of the peripheral unit bus and improves maintenance of the peripheral addressing system. Additional hardware changes required when the PUP feature is used in an SP office consists of a signal processor to serve as a buffer between the CC and the input/output equipment.

4.08 When the PUP feature is used with the No. 1A ESS, wiring changes are required on the SD-5A010-01/02 central control circuit and the SD-5A014-01 peripheral processor interface circuit. In addition to these modified processor units, the communication bus circuit SD-1A119 must also be modified to provide maintenance of the peripheral unit bus and to improve maintenance of the peripheral addressing system. €

### FIRMWARE UPDATING

**4.09** Firmware used in the PUC consists of software programmed into erasable programmable read only memory (EPROM). The EPROM consists of integrated circuits mounted on circuit packs installed in the PUC frame. It has the capability of being erased and reprogrammed when a program change occurs:

**4.10** The prompt remotely operated memory update system (PROMUS\*) is used to reprogram the PUC firmware. The PROMUS unit has the capability to erase, reprogram, and verify EPROM.

**4.11** A basic PROMUS unit is capable of simultaneously programming two circuit packs and erasing one. The basic unit can be expanded by adding programming and erase modules to program a total of eight and to erase a total of six circuit packs.

**4.12** The PROMUS units are located at centralized programming sites where the circuits are reprogrammed and shipped to the telephone company.

**4.13** The update process begins with an information-only broadcast warning message (BWM)

\*Trademark

sent over the software change administration and notification system (SCANS). The appropriate circuit packs are then reprogrammed and shipped.

# 5. DIGITAL CARRIER TRUNK APPLICATION

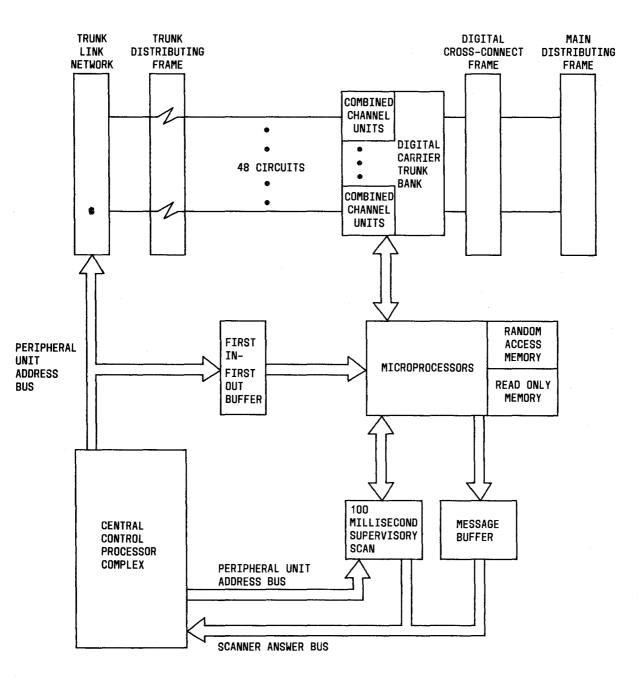

5.01 The PUC/DCT application (Fig. 6) provides call processing and channel multiplexing for up to 480 T1-channels (24 channels in each of 20 digroups) per DCT frame. The PUC is mounted in the center bay of a three-bay DCT frame. Shelf locations and circuit pack FG numbers are indicated in Fig. 7. Voltage regulators and power distribution units are mounted on the right-hand side of the shelves. The power and alarm control unit is located directly under controller 0 on a separate panel. Levels 66 and 74 slots 20 through 29 are special application circuit packs for DCT. One FG67 circuit pack is required for each digroup appearing in the DCT frame. The DCT application firmware resides in the CPU hardcore.

5.02 The DCT application firmware resides in the controller memory in the form of ROM. There are several PUC functions associated with the DCT application firmware. These functions include interfacing the No. 1/1A ESS CC with digroups and combined channel units (CCU), directing changes in signaling states, and summarizing and reporting changes in supervisory states. The PUC generates and receives dial pulse digits and revertive pulse digits.

5.03 The active PUC controller receives and translates relatively high-level CC orders into primitive control signals necessary to interface with the wired-logic digroup controllers. Call processing orders for the PUC/DCT are loaded in standard ESS peripheral order buffers (POBs). The orders are sent from the ESS to the PUC/DCT frame over the PUAB. The orders are in the form of 23-bit words. The orders are stored in a first in-first out buffer until the PUC's microprocessors are ready to execute them. This first in-first out buffer is called a data input first in-first out buffer (DIF). A DIF controller (DIFC) is used to control the loading and unloading of the buffer.

**5.04** ♦The SCAM has a 64-row and 16-column scanner configuration. The DCT application uses two scanners.

5.05 The PUC circuit unique to the DCT application is called a digroup buffer circuit (Fig. 7).This circuit consists of two 32-word FIFO buffers.

The words consist of eight data bits and one even parity indicator. One FIFO buffer for input and the other is used for output. The input FIFO buffer stores orders and data destined for the digroup controller in the channel bank. The output FIFO buffer stores data concerning trunk and digroup controller states. One digroup buffer is required for each digroup equipped.

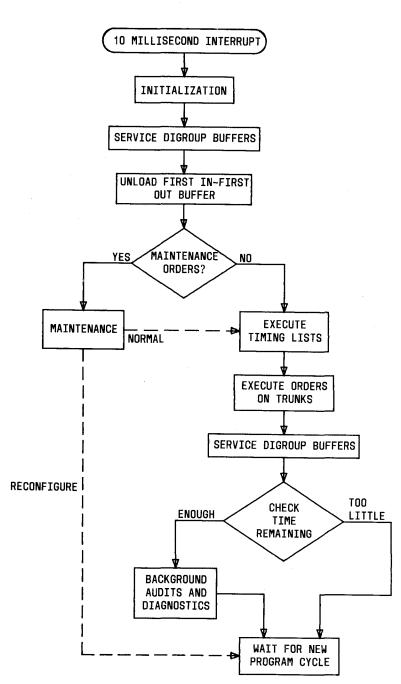

5.06 The DCT program cycle (Fig. 8) operates on a 10 millisecond interrupt from a clock. After initialization, the change reports from the digroup buffers are processed. The program then unloads an order from the FIFO buffer to load it into a hopper in the RAM. The BELLMAC-8 microprocessor decodes the order type, stores the order in the proper hopper for execution and sets an execution flag. The program terminates unloading of the FIFO buffer if the hoppers fill or if a high priority PUC maintenance order is found.

5.07 If there is a maintenance order which requires reconfiguration, the program will stop execution until the next program cycle. If there are no maintenance orders or they are low priority, the program continues. Timing list execution involves processing the information in each pulsing state register (PSR) on the list.

5.08 Executing orders on trunks involves processing state changes from ESS POB orders, checking the consistency of the states, and changing the state of the CCU. Orders to assign or release a link between a PSR and an ESS call register may also be executed. The program may also process digit output orders for outgoing calls on dial pulse or revertive pulse trunks. The program now services digroup buffers again until a necessary real time break for timing or output occurs. If there is enough time remaining, some background work may be done. This includes circuit diagnostics, data structure audits, translation updates from the ESS, and carrier facility monitoring (error rate counts). The program will start over when the 10 millisecond interrupt occurs.

5.09 The DCT firmware programs provide the ca-

pability of receiving, interpreting, and executing trunk state control and signaling orders from the ESS central control. In addition, it will process supervision and signaling (dial pulse, revertive pulse, and multifrequency) based on information from the digroup controllers. The programs also contain audits to keep all the data structure sane and intact.

Fig. 6—Peripheral Unit Controller/Digital Carrier Trunk Block Diagram

|          |          |             |           |                   |          |                   | BU        | s o        | FS                | 1 |                                 |           |                   |          |                   |      |                     |             |               |                         |              | E                        | BUS      | 1 F       | S 1      |                  |                    |           |           |           |          | - |           |           |      |               |             |    | FS | 12        |    |      |              |      |     |   |

|----------|----------|-------------|-----------|-------------------|----------|-------------------|-----------|------------|-------------------|---|---------------------------------|-----------|-------------------|----------|-------------------|------|---------------------|-------------|---------------|-------------------------|--------------|--------------------------|----------|-----------|----------|------------------|--------------------|-----------|-----------|-----------|----------|---|-----------|-----------|------|---------------|-------------|----|----|-----------|----|------|--------------|------|-----|---|

| ٢        |          | 1           | 2         | 3                 | 4        | 5                 | 6         | 7          | 8                 | 9 | 10                              | 11        | 12                | 13       | 14                | ` '  | 16                  | 17          |               |                         |              |                          |          |           |          |                  |                    |           |           |           | 29       |   | 31        |           |      |               | 35          | 36 | 37 | 38        | 39 | 40   | 41           | 42   | 43  | 4 |

| LE\<br>8 | VEL      | FC<br>322   | FC<br>322 | 322               | B<br>Byf | US<br>PASS<br>IS- | 292       | ADD BITS 5 | FC<br>333         |   | TS<br>ANS<br>BIT<br>(CFI<br>(MS | 331<br>D) | FC<br>332         |          |                   |      |                     |             | F<br>3:       | °C<br>313               | 132<br>1     | TS<br>ANS<br>BIT<br>(CPI | 333      | 333       |          | US<br>ASS<br>IS- | FB<br>292          | FC<br>333 | F0<br>333 | FC<br>33: |          |   |           | FB<br>668 |      | FB<br>668     |             |    |    |           |    |      |              |      |     |   |

| } -      |          | FG<br>32    |           |                   |          | FG<br>33          |           |            | FG<br>33          |   | FG<br>31                        |           | FG<br>68          | FG<br>34 | FG<br>36          |      | FG<br>37            | F0<br>38    | G F<br>3 3    | G F                     | =G<br>74     | FG<br>67                 | FG<br>67 | FG<br>67  | FG<br>67 | FG<br>67         | FG<br>67           | FG<br>67  | FG<br>67  | FG<br>67  | FG<br>67 |   | 131<br>F1 |           |      | -5V  <br>Cont |             |    |    | 131<br>F1 |    |      | 5V F<br>800- |      |     | - |

| LEV<br>7 | VEL      |             | H         | ARD               | COR      | <br>E/ME<br>      | <br>Emor  | <br>1Y<br> | -                 |   |                                 |           | 4                 |          |                   | S-PI | 1<br>uc<br>fac<br>1 | E-I         | ► P<br>I      | UC<br>ERI<br>NTE<br>ACE | R-           |                          |          |           |          | 10-<br>          |                    | i         | ł         | -         | Ð        |   |           |           |      |               |             |    |    |           |    |      |              |      |     |   |

|          |          |             | 2         |                   | Р        |                   | M         |            |                   |   | Р                               |           |                   | S<br>C   | S                 |      |                     |             |               |                         |              |                          | 11       | 12        | 13       | 14               | 15                 | 16        | 17        | 18        | 19       |   | 1         | 5V (      | POWE | 1             | LAN         |    |    |           | +5 | 5V F | SE E<br>Or ( | DB 1 | 6-1 |   |

| <br> -   | _        | R<br>A<br>M |           | D<br>M<br>A<br>FG |          |                   |           |            | C<br>P<br>U<br>FG |   | R<br>O<br>M<br>FG               |           | M<br>E<br>M<br>FG |          | C<br>A<br>M<br>FG |      |                     | D<br>I<br>F | (<br>[<br>] [ |                         | O<br>M<br>Fg | D<br>G<br>B<br>FG        | FG       | FG        | FG       | FG               | FG                 | FG        | FG        | FG        | FG       |   | 131       | +5V       |      |               | BLO(<br>NT  |    |    | 131       | +5 |      | SE B<br>Or ( |      |     |   |

|          |          | 32          |           | 39                | 31       | 33                | 35        |            | 33                |   | 31                              |           | 66                | 34       | 36                |      | 37                  | 38          | 3 3           |                         |              | 67                       |          |           |          |                  | 67<br>JFF          |           |           | 67        | 67       |   | F1        |           |      | 5V I<br>Cont  |             |    |    | F1        |    |      | 5V F<br>300- |      |     |   |

|          | VEL<br>6 |             |           |                   |          |                   |           |            |                   |   |                                 |           |                   |          |                   |      |                     |             |               |                         |              |                          |          |           |          | 10-0<br>         | 9                  | ł         | I         | 08        | 09       |   |           |           |      | BLO           |             |    |    |           |    | FU   | SE E         | BLO  | СК  |   |

|          |          | F           |           | F                 | F        | F                 | F         |            | F                 |   | F                               |           | F                 | FS       | 2                 |      | F                   | 5 3         |               |                         |              | FS                       | 11       |           |          | c                |                    |           |           |           |          |   |           | (         | CONT | 0             | LAN:        |    |    |           | +5 | 5V F | OR (         | DB2  | 0-2 |   |

|          | [        | S<br>8      |           | S<br>9            | S<br>7   | S<br>5            | S<br>6    |            | S<br>5            |   | S<br>7                          |           | S<br>4            |          |                   | V    | 1                   |             | 1             |                         | S<br>6       |                          |          |           |          |                  |                    |           |           |           |          |   |           |           |      |               | BLC<br>NT ( |    |    |           |    |      | SE B<br>V FC |      |     |   |

|          |          |             |           |                   |          | 7-0*<br>L S1      | 1<br>IRIP | ı          |                   |   |                                 |           |                   |          |                   |      |                     | F           |               |                         |              |                          | NIT      | EQU<br>CO |          | ED<br>DLLE       | P BI<br>As F<br>Er | -         |           | Đ         |          | , |           |           |      |               |             |    |    |           |    |      |              |      |     |   |

Fig. 7—Peripheral Unit Controller—Digital Carrier Trunk Circuit Pack Layout

# ISS 3, SECTION 231-037-020

}

Page 15

Fig. 8—Peripheral Unit Controller Program Cycle for Digital Carrier Trunk

The firmware consists of a main program, modules called directly by the main, and subroutine modules. The main program initializes the program cycle when it is entered.

# DATA STRUCTURES

5.10 Data structures are blocks of memory used by the DCT firmware programs to store and retrieve data for various operations. Some of the data structures are in RAM where data may be stored. Other data structures are in ROM where data can only be read.

# A. Digroup Register

5.11 Each DCT digroup has one digroup register (DR) assigned to it. This register occupies 16 eight-bit bytes of the SCAM in a fixed location. The data in this register is used to keep track of the digroup error history and maintain a communication link with the combined channel units (CCUs) plugged into the digroup. The DR contains the message being processed from the digroup buffer circuit, status and alarm bits, and error counts.

#### B. Trunk Register

5.12 There is one trunk register (TR) for each CCU. Each TR occupies 4 eight-bit bytes of SCAM.

The first byte of the TR contains the trunk status.

The second byte contains ordered trunk state changes which have not been completed and process markers which indicate that a trunk state change was detected and is being procesed. The third byte contains translation data for the trunk which gets pumped up periodically by the ESS. The fourth byte contains either a link to a PSR or a progress marker when the trunk is active on a call. When the BELLMAC-8 microprocessor receives an order from a POB, the TR is checked to see if it is a valid order.

#### C. Pulsing State Register

5.13 The PSRs are used for storing and processing data on trunks which are in the transient state. The PSR is attached to the TR during digit pulsing. These registers are used for timing and counting dial pulses and revertive pulses. They are also used for wink detection on operator trunks. The PSR contains the digits received from or to be transmitted to the connected office, the link index to the ESS call register, and address pointers to timing lists. The PSR also contains the trunk state ordered by the ESS and the state of current PSR activity. Each PSR uses 22 eight-bit bytes of memory.

# D. Timing Structures

5.14 Each timing list has a four-byte headcell which forms the pointers to the first and last registers on that particular list. There are three types of timing lists which are relatively short, medium, or long in time.

#### E. Order Hopper

5.15 The order hopper receives the orders read out by the FIFO buffer. All of the orders in the FIFO buffer are unloaded during each 10 millisecond program cycle. The order hopper provides for four POB orders and eleven non-POB orders. Only four POB orders can come in during one cycle, so there is no possibility of overflow. If more than eleven non-POB orders are received, the firmware program will begin executing the orders starting with the POB orders first.

# F. Link Table

5.16 The link table serves as a translator to convert

the link number used by the ESS call processing programs to a PSR number. The PSR number is an index into the memory blocks of PSRs.

#### G. Firmware Counts

5.17 Firmware counts are maintained on various events which indicate the status of the PUC. For example, counts are kept on the number of times a TR audit completed and the number of times that the PUC failed to seize a PSR at a time that one was required. These counts are kept in a 32-byte dedicated memory block. The ESS CC can request that the counts be reported through the message buffer upon demand. The CC is responsible for getting the counts out of the PUC and for resetting them.

#### H. Parameters

5.18 The PUC application program for DCT requires parameters to do certain types of timing. These parameters are pumped up from the CC periodically. They are stored in a dedicated memory block named PARAM. This memory block is 16 bytes long.

# I. Digroup Buffers in Service

5.19 The PUC maintenance programs require an indication of which digroup buffer circuits are in service. This block of memory consists of three bytes with each bit (0-19) assigned to one digroup buffer circuit. If the circuit is in service, the bit is set to a one. Four bits are not used and must be zero.

# J. Address Block

5.20 This block of memory contains the parameters used most frequently during a given call. The first two bytes of the address block hold the flag bits which indicate parameters in the block are present. The block includes such parameters as the trunk circuit number, internal trunk number, and pulsing state register number. The digroup, trunk, and PSR pointers are also included.

# K. Conversion Tables for Trunk and Channel Numbers

5.21 The ESS refers to trunks numbered from 0-119, 128-247, 256-375, and 384-503. In each quadrant, the trunks are numbered in the order of their physical position in the channel banks. The internal representation of the channel numbers in the DCT uses the numbering scheme employed by the digroup controller unit. The first channel is 4, the last channel is 27, the increment from one channel to the next is 4, and the sequence wraps around when the next value would exceed 27. In order to provide a quick way to convert between the two numbering schemes, these tables, stored in ROM, are provided.

#### L. Conversion Tables for State Designations

**5.22** These tables are provided to convert between

the state designations used in orders from the central control and the designations employed by the channel bank hardware.

# M. Miscellaneous Data Tables

**5.23** These are tables of constants required for miscellaneous functions in the DCT operational programs.

# **INPUT FORMAT**

**5.24** Peripheral order buffer orders from the ESS CC are sent over the PUAB and written into the FIFO buffer. The orders are in two general forms:

DCT application operational orders and DCT application maintenance orders.

5.25 The DCT input application operational orders

all follow the general form shown in Fig. 9. These orders are distinguished from the maintenance orders by the maintenance order indicator in bit 17. This bit is always set to zero for DCT applicaton operational orders.

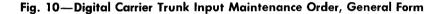

**5.26** The general form of the DCT application maintenance order is shown in Fig. 10. A one in bit position 17 indicates that the order is a maintenance order and not an operational order.

# **OUTPUT FORMAT**

**5.27** Messages from the PUC/DCT are unloaded from the SCAM and transmitted over the scanner answer bus to the ESS. These messages consist of 16-bit words called DCT application operational messages and DCT application maintenance messages.

5.28 The DCT output application operational orders follow the general form shown in Fig. 11. These messages are distinguished from maintenance messages by the maintenance indicator (bit position 15). This bit is zero for all operational messages.

5.29 The DCT application maintenance messages are in two forms, a single word message and a multiple word message. They are both 16-bit words with the maintenance indiator in bit position 15 set to a one. Figure 12 shows the general form of a single word maintenance message. Figure 13 gives the general form of the multiple word maintenance message.

#### **DIGROUP ORDERS AND MESSAGES**

**5.30** Communication with the digroup controller unit (DCU) takes place over a serial channel

implemented on the digroup buffer circuit pack. The serial channel is asynchronous at approximately 20,000 bits per second. The general format of the 8-bit data values exchanged between the PUC program and the digroup buffer/digroup controller is shown in Fig. 14.

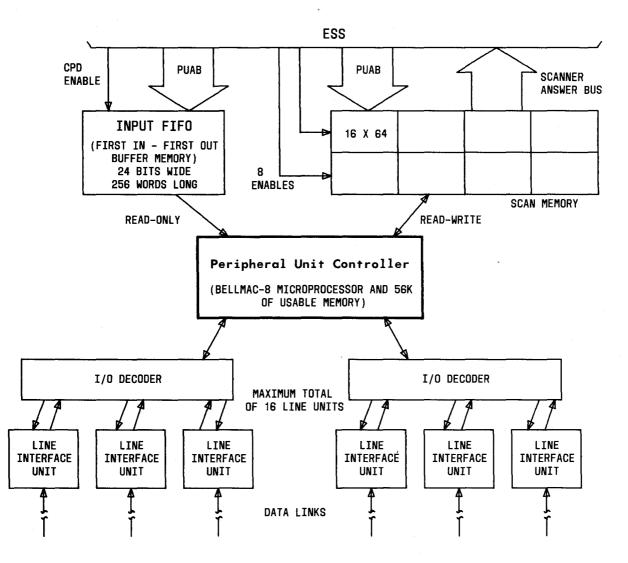

# 6. DATA LINK APPLICATION

6.01 The peripheral unit controller/data link (PUC/DL) is a particular application of the

PUC. It is designed to serve as a general purpose DL controller for several projects requiring a DL from ESS central office. The PUC/DL provides an interface between a No. 1/1A ESS central office and up to 16 bidirectional DLs. The RSS interface is described in Section 231-037-022. The ETS interface is described in Section 231-037-023. The CCIS interface is described in Section 231-037-025.

6.02 The PUC/DL feature is available with the 1E6 and later generic programs for No. 1 ESS and 1AE6 and later generic programs for No. 1A ESS. The PUC/DL feature is addressed in Section 231-090-062.€

6.03 The PUC/DL application program receives and sends data to the CC and selects 1 of 16

possible DLs for transmission. The PUC is mounted in the top section of a single bay frame (Fig. 1). Shelf locations and circuit pack FG numbers are indicated in Fig. 15. The power and fuse unit is mounted below the PUC/DL unit. Directly below the power and fuse unit is the power and alarm control unit. Levels 66 and 74 slots 22 through 44 are special application circuit packs for DLs termed line interface units (LIUs). One LIU is required for each DL equipped. LIUs are different for the various DL applications. Data link application firmware resides in the controller memory in the form of ROM.

6.04 Data exchanged between the No. 1/1A ESS and PUC/DL consists of application informa-

tion and maintenance information. The insertion and deletion of protocol words and any necessary error recovery actions are handled within the PUC/DL.

6.05 Communication from the ESS to the PUC/DL

comes through the input FIFO buffer memory (Fig. 16). Three byte data words are read from the FIFO.

6.06 Data is passed to the ESS from the PUC/DL by writing it into the SCAM. The SCAM is a specified address range of the PUC/DLs' read/write memory. The ESS has read-only access to these locations where they are treated as a sequence of scanner rows. This data is passed over the SCAB. Data links are accessed through the I/O decoder.

#### BIT POSITIONS

| 22 21 20 | 19 | 18 | 17 | 16 | 1_1 |  |       |   | 1 | L | 1 | 1. | 1. | 10 | 1 |

|----------|----|----|----|----|-----|--|-------|---|---|---|---|----|----|----|---|

|          |    | D1 |    |    |     |  | <br>D | 2 |   |   |   |    |    |    |   |

COM - COMMAND CODE. THIS THREE BIT FIELD SPECIFIES THE TYPE OF OPERATION REQUIRED BY THE ORDER. 001 - STATE CHANGE ORDER FOR A TRUNK. 010 - DIGIT OUT ORDER FOR OUTPULSING ON A TRUNK. 011 - LINK ORDER FOR ASSOCIATING A LINK BETWEEN A PSR IN THE PUC AND AN ESS CALL REGISTER. 101 - DETECT STPS (START PULSING SIGNAL) ORDER, USED TO INFORM THE PUC ABOUT START PULSING FOR A TRUNK.

- D1 AND D2 DATA ASSOCIATED WITH THE SPECIFIC ORDER TYPE INDICATED BY THE COMMAND CODE.

- M MAINTENANCE ORDER INDICATOR. THIS BIT IS ALWAYS ZERO FOR DCT OPERATIONAL ORDERS.

- \* THIS BIT IS NOT USED. IT MUST BE ZERO DUE TO INTERACTIONS WITH CERTAIN ESS PROGRAMS.

Fig. 9—Digital Carrier Trunk Input Operational Orders, General Form

# BIT POSITIONS

| 22 | 21 | 20 | 19  | 18 | 17 | 16 | 15 | 1_ | 1 | 1 | 1 | 1 |     |   | 1 | 1 |  |  |

|----|----|----|-----|----|----|----|----|----|---|---|---|---|-----|---|---|---|--|--|

| PF | AP |    | HOP |    | M  | L  |    |    |   |   |   |   | DAT | A |   |   |  |  |

- PR PRIORITY INDICATOR. MUST EQUAL 0 (LOW PRIORITY) FOR APPLICATION MAINTENANCE ORDERS.

- AP APPLICATION ORDER INDICATOR FOR LOW PRIORITY MAINTENANCE ORDERS.

- HOP THE HIGH ORDER 3 BITS OF THE OPERATION CODE OF THE ORDER.

- M MAINTENANCE ORDER INDICATOR. A ONE IN THIS BIT POSITION ALWAYS OCCURS FOR MAINTENANCE ORDERS.

- L THE LOW ORDER BIT OF THE OPERATION CODE OF THE ORDER.

- DATA THE DATA ASSOCIATED WITH THE PARTICULAR ORDER TYPE INDICATED BY THE OPERATION CODE.

BIT POSITIONS

| 15 | 14 13 | 12 | 11 | 1 | ł |   | 1   | I |  | 0 |

|----|-------|----|----|---|---|---|-----|---|--|---|

| M  | MT    |    |    |   |   | I | DAT | A |  |   |

- M MAINTENANCE INDICATOR. THIS BIT IS O FOR ALL APPLICATION OPERATIONAL MESSAGES.

- MT MESSAGE TYPE INDICATOR.

- 001 DIGIT RECEIVED MESSAGE.

- 010 TERMINATING REVERTIVE PULSE REPORT MESSAGE.

- 011 SXS FAST RESEIZURE MESSAGE.

- 100 SXS PREPULSE MESSAGE.

- 110 WINK DETECTED MESSAGE FOR INBAND OPERATOR TRUNK SIGNALING.

- 111 GENERAL REPLY MESSAGE.

DATA - DATA DEPENDING ON THE MESSAGE TYPE.

Fig. 11—Digital Carrier Trunk Output Operational Messages, General Form

#### BIT POSITIONS

- M MAINTENANCE INDICATOR. THIS BIT IS ONE FOR ALL MAINTENANCE MESSAGES.

- MX MULTI-WORD MESSAGE INDICATOR. THIS BIT IS ZERO FOR SINGLE WORD MESSAGES.

- P PUC MESSAGE INDICATOR. THIS BIT IS ZERO FOR APPLICATION MAINTENANCE MESSAGES.

- DATA THE CONTENTS OF THIS 13 BIT FIELD ARE THE DATA FOR THE MESSAGE.

# Fig. 12—Single Word Digital Carrier Trunk Output Maintenance Message, General Form

#### BIT POSITIONS

M - MAINTENANCE MESSAGE INDICATOR. THIS BIT WILL BE ONE FOR ALL MESSAGES IN THIS CLASS.

- MW MULTI-WORD MESSAGE INDICATOR. THIS BIT WILL BE ONE FOR ALL MESSAGES IN THIS CLASS.

- P PUC MESSAGE INDICATOR. THIS BIT WILL BE ZERO FOR ALL MESSAGES IN THIS CLASS, SINCE THEY ARE ALL APPLICATION MAINTENANCE MESSAGES.

- LN THE LENGTH INDICATOR. THE VALUE OF LN WILL BE TWO LESS THAN THE TOTAL MESSAGE LENGTH INCLUDING THE HEADER.

- TY TYPE. THIS EIGHT BIT FIELD SPECIFIES THE TYPE OF MESSAGE.

- \* THIS BIT IS NOT ASSIGNED.

- Fig. 13—Multiple Word Digital Carrier Trunk Output Maintenance Message, General Form

BIT POSITIONS

| 7 | 6       | 2 1 0 |

|---|---------|-------|

| x | ADDRESS | YZ    |

- X A CONTROL BIT USED TO SPECIFY ONE OF TWO CLASSES OF ORDERS OR MESSAGES.

- ADDRESS THIS FIVE BIT FIELD NORMALLY CONTAINS A CHANNEL ADDRESS, WHICH IS A VALUE IN THE RANGE 00100 THROUGH 11011. IF THE VALUE IS NOT IN THAT RANGE, A SPECIAL FUNCTION SPECIFIED BY THE OUT-OF-RANGE (OOR) CODE IS PERFORMED.

- YZ THIS FIELD CONTAINS EITHER DATA CORRESPONDING TO A PARTICULAR CHANNEL, A CODE SPECIFYING WHAT DATA IS BEING REFERENCED BY THE ORDER OR MESSAGE, OR DATA CORRESPONDING TO THE ENTIRE DIGROUP.

#### Fig. 14—Digital Carrier Trunk Digroup Order and Message, General Form

6.07 The PUC/DL firmware consists of common routines and protocol blocks (Fig. 17). Common routines can be used with different types of DLs. They are involved in functions such as the input of data, timing, and audits. The link dependent operations are taken care of within the protocol blocks. A protocol block is a group of subroutines designed to take data from a buffer in memory and dispatch it on a link following the rules of a specific DL protocol. The maintenance functions for the link interface hardware are also included in the protocol blocks.

# **COMMON ROUTINES**

#### A. Timing

**6.08** A 20-millisecond software clock is maintained for timing. The clock has a 16-bit output and a single client delayed entry is provided.

#### B. Input

6.09 All incoming data from the ESS is read from the input FIFO buffer and sorted in three categories—data, parameters, and maintenance orders. The data is destined to be sent on a DL. Data is not addressed to a specific link number; it is marked with a destination number specifying a buffer in the PUC/DL read-write memory. One destination buffer exists for each remote terminal. The association of a destination buffer and a single data link is specified in a parameter. Switching between redundant links can be requested through a maintenance order. The switching can occur during communication without loss of data.

6.10 Incoming data is placed in the destination buffer requested in the data heading (first) word. This buffer is managed as a linked list. See Fig. 18. Each new message is added to the end of the list. The buffer is circular, thus the physical end of the address space is of no concern. When the buffer is full, as indicated when the end of the list meets the beginning, the present data message is discarded and an error reported. This action is necessary to prevent one link out of service from jamming all data flow through a PUC/DL. Such a problem would otherwise occur since there is no way to look ahead in the input FIFO buffer other than to read the bottom message and either store or discard it. Cumulative counts are kept of all words unloaded from the FIFO buffer and from the destination buffers. These counts are recorded in the SCAM where they are read and used by the ESS to control the input rates and prevent overflow in normal operation.

FRONT VIEW

Fig. 15—Peripheral Unit Controller—DL Circuit Pack Layout

Fig. 16—Peripheral Unit Controller/Data Link Block Diagram

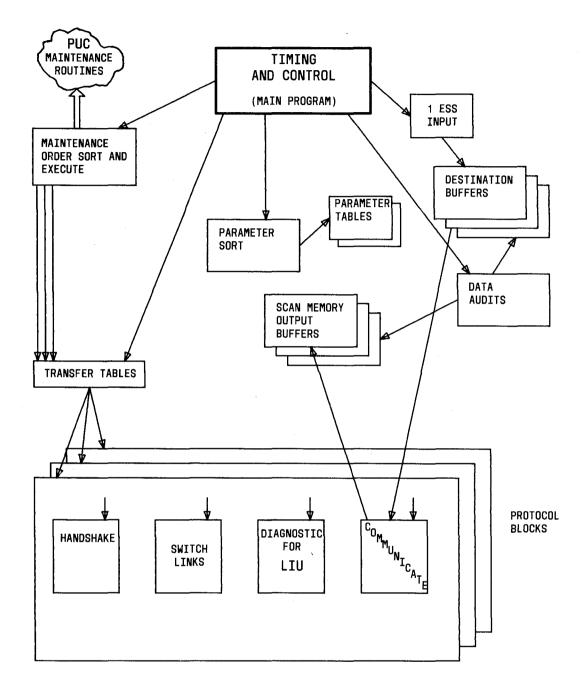

# Fig. 17—Peripheral Unit Controller/Data Link Firmware Structure Simplified

Fig. 18—Peripheral Unit Controller/Data Links Destination Buffer Structure

6.11 The PUC/DL operation is defined by parameter input messages. Most parameters are sent when the unit is brought on-line. Receipt of a parameter causes a table entry to be initialized or changed and an audit request generated. The audit routine will be run at the next opportunity. It alters the internal data structures to agree with the new parameter. Parameters specify things such as the number and length of destination buffers, the number, length, and location of data output buffers in the SCAM, or the destination and protocol type of each DL.

6.12 The PUC maintenance orders are split off immediately. These are processed by the controller maintenance programs and are of no concern to the application firmware. Application maintenance orders are what remain. They initiate functions such as bringing a DL on-line, clearing an error count, or switching between redundant DLs to the same destination.

#### C. Audits

6.13 The main purpose of audits is to build and ini-

tialize data structures in the read/write memory. The input for all audits comes from the parameter table. The output is pointers which delimit data buffers. The audit routines are a run-time memory allocation facility. They provide space for destination buffers and scratch blocks when these areas are requested by parameter inputs. The entire sequence of audits are run whenever parameters are changed. Otherwise, they are a low priority background task providing recovery from errors.

# **PROTOCOL BLOCK ROUTINES**

6.14 The duties of a protocol block are to take data from a destination buffer and send it over a data link and to take data from the link and record it in the SCAM. The protocol block includes whatever routines are necessary to implement a protocol handshake and a transfer of communication to a standby link without loss of data. The diagnostic programs for the LIU are considered part of a protocol block although they may be shared between protocols using the same DL interface hardware.

#### A. Communicate

6.15 The first action is to empty the LIU receiver FIFO buffer. If the resulting words complete a data link frame, a reply is assembled and sent. There is a separate receive subroutine for each of the seven data frame types. These carry out the actions pertinent to that message and reply by selecting the appropriate send subroutine. There are send subroutines for all frame types except "receiver not ready." This response is never required since it is assumed that the ESS input routine will never let the SCAM buffers overflow; thus the PUC/DL is always ready for another message. The SCAM buffers are circular. Each is provided with a load pointer, updated by the protocol routines, when a data frame is received error-free. The pointer specifies where the ESS input routine is to stop reading.

6.16 Data is transmitted when two conditions are met. There must be room for an entire data frame in the LIU send FIFO buffer and the destination buffer associated with this link must have data ready to send. When this is true, one frame will be sent. It will carry a maximum of 16 data bytes.

#### B. Handshake

6.17 The handshake function is called whenever an order is processed to make a link active. The protocol block subroutine is selected by reference to the protocol parameter for the link specified in the maintenance message. The handshake routine resets all protocol variables and attempts to initialize communication by sending a set asynchronous response mode data link frame. If the handshake is successfully answered, a link-restored message is returned to the ESS. If the handshake does not complete properly, a protocol impasse report is returned to the ESS. This indicates that either the link or the remote

end device is inoperative. A portion of the code which initializes certain variables is called when processing a clear destination buffer maintenance message. This prevents generating confused output if the buffer is cleared when sending is active.

# C. Switch Links

**6.18** This protocol block is specific to applications using standby links. It comes as a response to a maintenance order requesting a soft (no data loss) switch to a standby link. A switch request is set pending until the data exchange is at a point where the switch can be accomplished with no loss or repetition of data. The protocol routines then alter the link status, setting the present link out of service and making the standby link active.

# D. Line Interface Units Diagnostics

6.19 The LIU diagnostics come as time permits near the end of a program cycle. The common routines record the arrival of a diagnostic request application maintenance message. When time is available, the diagnostic is run in segments. There may be any number of segments but each segment must take no longer than 3 milliseconds to complete. Diagnostic routines return a pass/fail report accompanied by two bytes of data. The interpretation of the data varies according to what is being tested. Separate LIU diagnostics are provided to locate a faulty circuit pack and to make an error rate check on a DL. Diagnostics are run only on inactive links.

#### **PROGRAM TIME SEQUENCE**

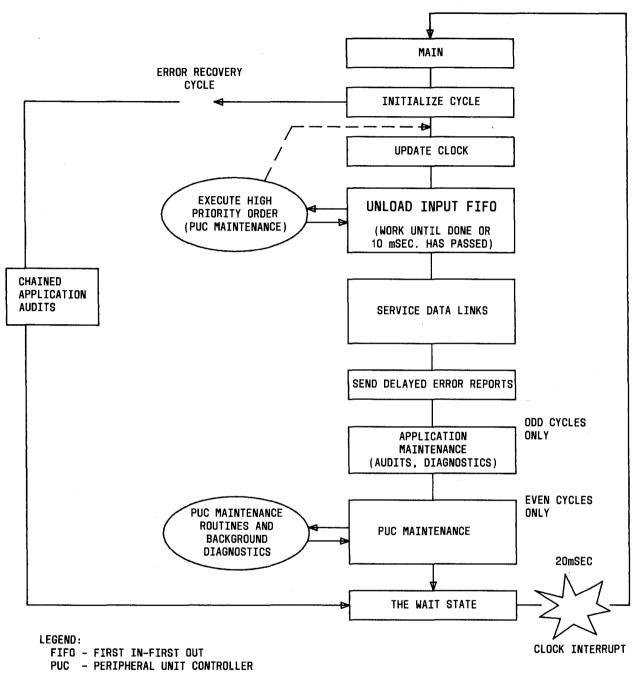

6.20 All application firmware activities are based on a 20-millisecond main program cycle (Fig. 19). This cycle time is enforced by a hardware timer. At the beginning of the cycle this timer is initialized and set running. Twenty milliseconds later the timer generates an interrupt, bringing control back to the start of the cycle and causing the sequence to repeat. If all goes well, all tasks scheduled will be completed and the processor will have halted (the wait state) when the timer interrupt occurs. If it is found still running, an error has presumably occurred placing the routine in a long or unending loop. In such an event, the next cycle is dedicated to running audits, which hopefully will remedy the difficulty. These actions occupy the initialize cycle block in the diagram.

mSEC - MILLISECOND

Fig. 19—Peripheal Unit Controller/Data Link Main Program Cycle

6.21 The main program itself is mostly a series of subroutine calls. After initialization, the next routine called unloads the ESS input FIFO buffer. The input words are read and sorted. Data words are deposited in destination buffers. Application maintenance orders involving little processing are executed at once. Others are recorded for attention later in the cycle. Parameters are written into the parameter table. When a parameter is received, the audit cycle is restored to the beginning and audits are increased in priority. The PUC maintenance orders are sorted by priority. High priority orders are executed as they are received with a call to a PUC maintenance program. Low priority orders are stored. They will be executed when time permits at the end of the cycle. As words are removed from the FIFO buffer, the unload word count is advanced. This is a word in the SCAM needed by the ESS output programs to keep record of empty words and prevent overflowing the FIFO buffer. Unloading terminates when the FIFO buffer is found empty or after 10 milliseconds have been spent in this task.

Control then passes to the DL service routine 6.22 whose responsibility is to locate the active DL and run the communicate section of their corresponding protocol blocks. The active indicator is a bit in the parameter table. This table is searched in numerical sequence. When an active link is found, its protocol number is retrieved and control is given to the specified protocol block. When its activity completes, the search is resumed, finding the next active link. Data link service terminates when 16 links have been serviced or if less than 5 milliseconds remain in the program cycle. This implies that a protocol block communicate entry must always complete in less than 5 milliseconds. When DL service is resumed in the next program cycle, the search for active links will start where it left off. Thus, high-numbered links will not receive nonuniformly degraded service as the communication load increases.

6.23 The next action will not usually occur. A delayed error report is sent only in cases where an error report was suppressed because the SCAM maintenance output buffer was full when the report was generated.

6.24 When DL service has completed, the hardware clock is read. If less than 3 milliseconds remain in the present cycle, no more tasks are entered and the processor is halted. If enough time remains, maintenance routines are run. This service alter-

nates between PUC maintenance and application maintenance. If the cycle number, as read from the software clock is even, control is given to the PUC maintenance routines. If a low priority PUC maintenance order has been received, it is executed at this time. Otherwise, background diagnostics are called. When the cycle count is odd, application maintenance runs. This task is either an audit segment or executing a deferred application maintenance order. If a parameter has been received since a complete cycle of audit segments has run, the next audit segment receives control, regardless of pending maintenance orders. If this is not the case, the choice is between a deferred order and an audit segment. If a deferred order exists, it is executed. This could be a request to make a DL active or an LIU diagnostic request. Either results in a call to a protocol block routine. When no such order is waiting, the application maintenance time is given to the next audit segment.

**6.25** After completing PUC or application maintenance routines, the cycle is terminated. An indicator is set marking that the cycle was successfully completed. The processor then halts. When the 20-millisecond hardware timer expires, a new cycle will begin.

# **INPUT FORMAT**

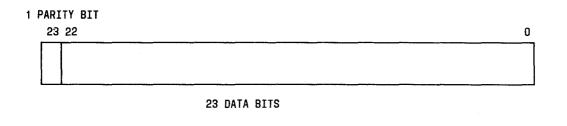

6.26 All application input to the PUC/DL enters through the input FIFO buffer. This first infirst out buffer is 256 words deep. It is completely a hardware function, providing time buffering of messages which is invisible to both the ESS and the PUC/DL software. Input to the FIFO buffer comes from the PUAB in short binary format. This supplies 23 bits of data plus one parity bit. The PUC/DL firmware interprets each such word as three 8-bit bytes. The application firmware recognizes the byte boundaries as delimiting message data fields (Fig. 20).

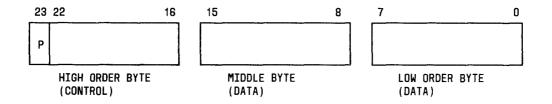

6.27 The first sort is on the basis of the leftmost byte of the input heading control field (Fig. 21). If the parity is incorrect (it should be odd), the word is discarded and an error report returned to the ESS. The next separation is governed by the maintenance/data bit. Data messages have a zero in this position.

#### A. Data Messages

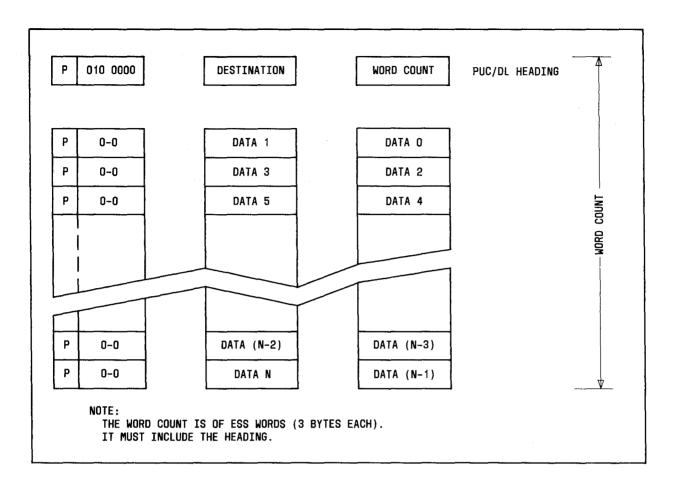

6.28 A data message must begin with a heading, a word with only the application bit in the left

SHORT BINARY WORD AS SENT BY NO. 1 ELECTRONIC SWITCHING SYSTEM

Fig. 20—Peripheral Unit Controller/Data Link Input Format

byte set. Any word with zero in the maintenance bit and one or more nonzero data bits in the left byte will be interpreted as a data message heading (Fig. 22). The middle field of the heading contains the destination number. This specifies the transmit (destination) buffer where the words following will be stored. The heading is interpreted by the PUC/DL and discarded. It is never put in a destination buffer and therefore will not appear in a DL message. The right (low order) byte of the data message heading contains a word count. This is for error checking and must include the heading. This is a count of 24-bit ESS words written into the FIFO buffer. It is not a data link byte count. A data message having an incorrect word count will be discarded and an error reported.

6.29 The data words following the heading are identified by all data bits zero in the left byte. The low order two bytes will be placed in the destination buffer. They may be transparent data or protocol level control, depending on the protocol being used.

#### B. Maintenance Messages

6.30 A one in the maintenance bit marks a nondata message (Fig. 21). Such an item is always a one-word unit, never accompanied by data words. The next division in the category of maintenance messages separates application and PUC orders. This is sorted bit 22, which is one for application maintenance orders.

6.31 Application maintenance messages perform a variety of functions. All orders to activate and reconfigure data links are of this type, as are the messages which present and update parameters. Each application maintenance message is discussed in detail in the following sections.

# **OUTPUT FORMAT**

**6.32** Output of all data and control information is passed through the SCAM from the PUC/DL

to the ESS. Output is of three types, incoming DL messages, error and status reports, and special indi-

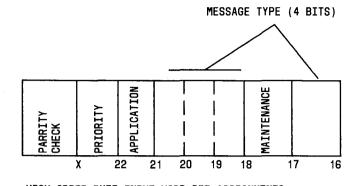

HIGH ORDER BYTE INPUT WORD BIT ASSIGNMENTS

- PARITY CHECK: SUBSTITUTED FOR PARITY BIT BY FIFO BUFFER HARDWARE. THIS BIT = 1 IF INCOMING PARITY WAS CORRECT.

- PRIORITY: APPLICABLE TO PUC MAINTENANCE ORDERS ONLY - IF SET THE ORDER IS EXECUTED IMMEDIATELY.

- APPLICATION: SIGNIFICANT ONLY WHEN MAINTENANCE BIT IS SET. IT DISTINGUISHES PUC AND APPLICATION (=1) ORDERS.

- MAINTENANCE: SEPARATES MAINTENANCE ORDERS (=1) FROM DATA INPUT.

- MESSAGE TYPE: 4-BIT CODE TO IDENTIFY MESSAGES WITHIN THE GROUPS PROVIDED ABOVE.

- LEGEND:

FIFO - FIRST IN-FIRST OUT PUC - PERIPHERAL UNIT CONTROLLER

#### Fig. 21—Input Heading Control Field

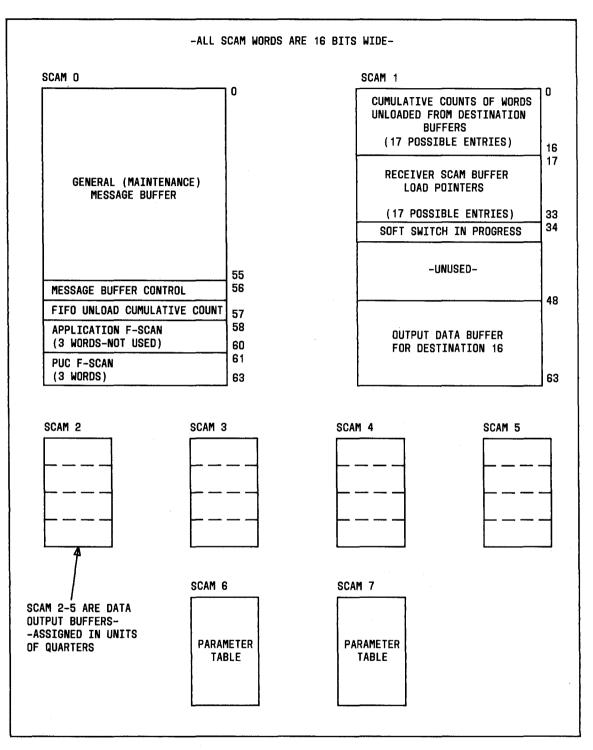

cators. The latter are items such as buffer load and unload counts. Figure 23 is a layout map of the SCAM.

#### A. Incoming Data from Data Links

6.33 Incoming data is deposited in per-destination circular buffers in the SCAM. The length and position of these output buffers are specified in a parameter. There are certain restrictions placed on these values by the readout algorithm used in the ESS. Each data output buffer is provided with a load pointer, also located in the SCAM. This points to the location where the next word (as yet unreceived) is to be written. The output buffer unload pointer exists solely within the ESS. It is expected that the unload routine will always be able to keep up with the PUC/DL and never allow overwriting to occur.

#### **B.** Maintenance Messages

# 6.34 Maintenance messages are all communication

that does not originate at the far end of a DL. They are delivered in the general reply buffer, located in a different part of the SCAM. Maintenance messages are error reports and parameter acknowledgments. They are considered to be of lower urgency than incoming data. Thus the general reply buffer is provided with both a load and an unload pointer, both recorded in a dedicated word in SCAM. Maintenance messages are sent only when there is space available in the buffer. If one or more reports have been supressed because the buffer was full, a message to this effect will be sent when buffer space becomes free. The identity of the original reports is lost.

#### C. Special Indicators

6.35 Several examples of the special indicator output type have just been mentioned. They are the data output buffer load pointers (arrayed in a table) and the general reply buffer load and unload pointers (combined in the general buffer control word). Other special words in the SCAM are the FIFO buffer unload count and the table of destination buffer unload counts. These are used to determine how many words are available in the input FIFO buffer and in each destination buffer. A special word is provided to indicate when a DL switch is in progress. This is necessary because only one link switch can be performed at a time.

# PARAMETERS

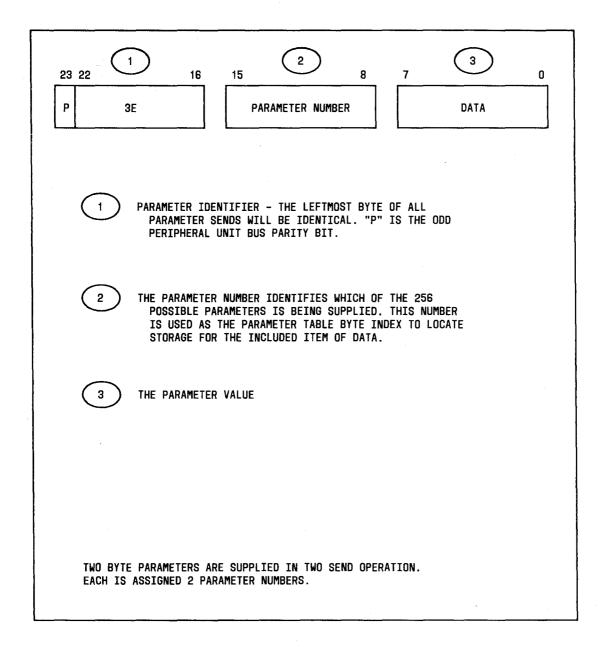

6.36 Parameters are application maintenance messages bringing items of data to the PUC/DL as the controller is being brought into service. Their purpose is to tailor the PUC/DL memory allocation to the needs of the DL applications which it serves and to specify the characteristics of the individual DLs. Items such as the length of a transmit buffer or the type of protocol to be used on link number three are typical parameters.

**6.37** All parameters are in the form of single word messages which communicate one byte of parameter information. The remaining two bytes of the input word are needed to distinguish the parameter from other types of messages and to specify which parameter is being communicated. The present layout of the parameter address space will accommodate

Fig. 22—Input Data Message

a total of 256 parameters. These parameters are subdivided into four categories. They are: general parameters, destination parameters, data link basic parameters, and data link protocol parameters. Figure 24 outlines the data fields in a typical parameter.

# A. General Parameters