# CENTRAL PROCESSOR PROCESSOR CAPACITY CONSIDERATIONS NETWORK SWITCHING ENGINEERING NO. 1A ``ESS\*'' SWITCH

|      | CONTENTS P                                             | AGE    | CONTENTS                                                                  | AGE |

|------|--------------------------------------------------------|--------|---------------------------------------------------------------------------|-----|

| 1.   | GENERAL                                                | 2      | CALL PROCESSING CAPACITY ESTIMATION<br>AN INTRODUCTION TO ESTIMATION AIDS |     |

| 2.   | EQUIPMENT ARRANGEMENTS                                 | 2      | · · · · · · · · · · · · · · · · · · ·                                     | 8   |

|      | GENERAL                                                | 2      | A. Precutover Aids                                                        | 8   |

|      | CENTRAL PROCESSOR                                      | 2      | B. Postcutover Aids                                                       | 9   |

|      | MEMORY                                                 | 3      | RECOMMENDATIONS AND DATA CONSIDER-                                        | 9   |

|      | PROGRAMS                                               | 3.     | A. Processor Occupancy                                                    | 9   |

|      | REAL TIME AND PROCESSING CAPACITY .                    | 4      | B. Processor Busy Hour                                                    | 9   |

| 3.   | PROGRAM PHILOSOPHY AND ORGANIZA-<br>TION               | 4      | C. Quarter-Hour-to-Hour Conversion Factor                                 | 9   |

|      | GENERAL                                                | 4      | D. Peak Factor                                                            | 10  |

|      | CATEGORIES OF WORK AND PROGRAMS .                      | 5      | E. Capacity Utilization                                                   | 10  |

|      | SCHEDULING                                             | 5      | F. Cutover Capacity Recommendations                                       | 10  |

| 4.   | ENGINEERING CONSIDERATIONS                             | 7      | Figures                                                                   |     |

|      | GENERAL                                                | 7<br>7 | 1. No. 1A ESS Switch—Processor Community<br>Block Diagram                 | 12  |

|      | A. Types of Calls and Equipment                        | 7      | 2. No. 1A Processor Program Control Plan .                                | 13  |

|      | B. Generic Program                                     | 8      | 3. No. 1A Processor Program Priority Structure                            | 14  |

|      | C. Network and Trunk Blocking                          | 8      | 4. No. 1A ESS Switch—Division of Total Real                               | 17  |

|      | D. False Cross and Ground and Restore-<br>Verify Tests | 8      | Time                                                                      | 15  |

| * Tr | ademark of Western Electric                            |        | 5. No. 1A ESS Switch—Processor Capacity His-<br>tory                      | 16  |

# NOTICE

Not for use or disclosure outside the Bell System except under written agreement

Printed in U.S.A.

CONTENTS PAGE

6. Service Improvement with IOS . . . 17

Tables

A. Interrupt Levels-No. 1A ESS Switch . . 18

# 1. GENERAL

1.01 This section provides a general description of network switching engineering principles for the central processor of the No. 1A ESS switch. Included in this section is a discussion of the organization of the stored program and the concepts applicable to the determination of the call-processing capacity of a No. 1A ESS switch. This section supplements Section 231-062-410 and Section 231-062-420 which describe precutover and postcutover call-processing capacity estimation methods respectively.

1.02 This section is being reissued to include the addition of Improved Overload Strategy (IOS) and Essential Service Protection (ESP) as well as the latest processor capacity determination models. Revision arrows are used to emphasize significant changes.

1.03 Part 2 of this section contains a description of the hardware components of the central processor community and a general discussion of realtime utilization in the No. 1A ESS switch.

**1.04** Part 3 describes the organization of stored program control, including program structure, with emphasis on the concepts of program hierarchy, and scheduling.

1.05 Part 4 of this section contains discussions of various engineering considerations applicable to determining the call processing capacity of a No. 1A ESS switch.

1.06 References in this section to methods, planning, data requirements, service levels, and equipment quantities are based on American Telephone and Telegraph Company recommendations.

**1.07** The title for each figure includes a number(s) in parentheses which identifies the paragraph(s) in which the figure is referenced.

#### 2. EQUIPMENT ARRANGEMENTS

# GENERAL

2.01 The central processor community of the No.

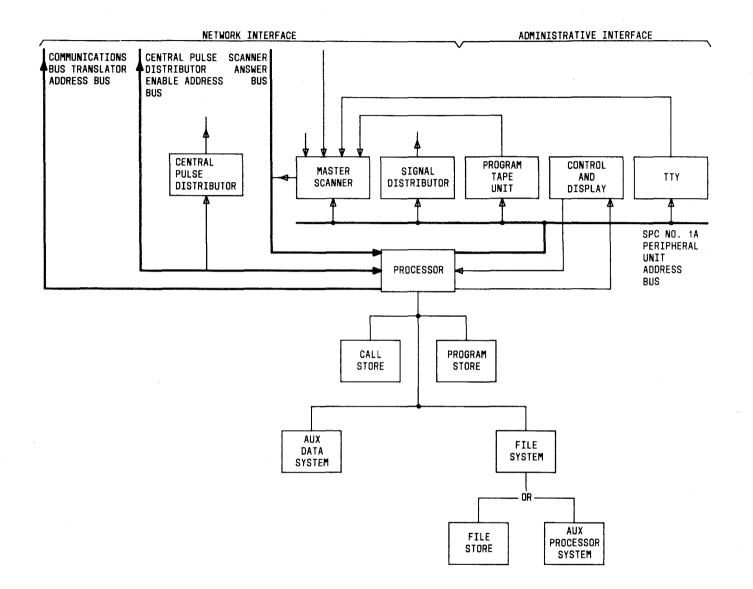

1A ESS switch is a stored program control system (SPCS). This system employs memory units for storing instructions and data and a logic unit which monitors and controls peripheral equipment. The logic unit exercises its control through a set of operations dictated by a sequence of program instructions. The central processor community (Fig. 1) consists of a 1A processor, program stores, call stores (duplicated and unduplicated), file stores (disk units), and an auxiliary data system (tape units). Beginning with generic 1AE7, the file stores are replaced by the auxiliary processor system (APS) in new-start offices and 1A processor retrofits. The central processor community also includes the system controls (master control center and input-output terminals), the processor peripheral interface frame, and the power conversion and distribution frame (neither of which is shown on Fig. 1).

2.02 Input information for the 1A processor is provided by scanning various points in the peripheral system. These points include lines, trunks, and receivers. The scanners are directed periodically to scan the lines to detect service requests, the trunks to detect incoming calls, and the receivers for detecting dialed digits and other control information. The process of collecting this input information involves periodic scanning and the recording of results of these scans in temporary (duplicated call store) memory.

2.03 The signal distributor (SD) operates in reverse of the scanner. It is connected to the various points in the peripheral system where actions must be controlled by the processor. The processor can direct (address) the SD to a particular terminal to prepare it for receipt of an execution signal. At a later time, the processor can address the SD to send the execution signal.

# **CENTRAL PROCESSOR**

2.04 The No. 1A ESS switch contains two identical processors. Central Control (CC) 0 and Central Control (CC) 1 The two processors are contained in a single, double-bay frame, 6 feet 6 inches wide; each bay contains one processor.

**2.05** Both processors operate simultaneously. One, called the active processor, controls the office,

while the other, called the standby processor, decodes the same instructions as the active processor, but does not perform any control actions. If the active and standby processors decode an instruction differently, an interrupt occurs, and a fault recognition program is called in to determine which one of the processors is malfunctioning and should be switched out of service. When the active processor is switched out of service, the standby processor becomes active, and diagnostic procedures are instituted to determine the location of the malfunction. After the malfunction is corrected, the corrected processor assumes standby status.

2.06 The processor is the primary data processing, controlling, timing, logic, and arithmetic unit of the central processor community. It receives inputs (from line, trunk, junctor, or master scanners), initiates (via the central pulse distributor and the signal distributor) the sending of pulses which establish and supervise network connections, and detects and analyzes faults, using the program instructions contained in program store. It is a word-organized, 24-bit data processor with a cycle time of 700 nanoseconds (0.7 microseconds).

#### MEMORY

2.07 The memory units contained in the central processor community include: program stores,

¢call stores (duplicated and unduplicated), file stores or the APS, and an auxiliary data system.

2.08 The program store is a read/write memory unit containing most of the generic program which controls the operation of the system.

2.09 Call stores have read/write capability, and are divided into two categories (duplicated and unduplicated), each with a specific function:

- (a) Duplicated call stores are used primarily for the storage of transient data related to call processing.

- (b) Unduplicated call stores contain translation information as well as some parameter information.

2.10 The file store is a medium-speed data storage system used for those situations in which a longer access time will not adversely affect the highspeed performance of the 1A processor. These situations include:

- (a) Backup of program stores (generic)

- (b) Backup of unduplicated call stores (translations)

- (c) Primary storage for programs such as diagnostics.

2.11 ♦The APS will replace the file store system starting with the 1AE7 generic program. The APS has moving head disks and slightly larger disk delay and pump-up time. This will result in a slightly increased processor time for processor diagnostics and recent changes. The APS is available only for initial offices and 1A processor retrofits with the 1AE7 generic.

2.12 The auxiliary data system is a flexible, medium speed, data storage system employing magnetic tape units with the following applications:

- (a) Automatic message accounting (AMA)

- (b) System reinitialization

- (c) Program updating

- (d) Periodic documentation

- (e) Other administrative and maintenance routines.

#### PROGRAMS

2.13 The stored program for the No. 1A ESS switch constitutes the operating intelligence of the system. The stored program must perform switching functions reliably and promptly. In addition, the stored program must have the capability to recognize malfunctions within the system, diagnose the problem, and direct corrective action in such a way that the primary work of processing calls is not significantly affected.

2.14 The processor of the No. 1A ESS switch uses an executive control main program. This program, commonly referred to as the main program, coordinates all work, including input and output work, by dispensing control to appropriate application programs. Each application program performs a specific type of work called a task. Input and output work involves application programs which receive or transmit information to or from an external source. The dispensing of control by the main program is referred to as transferring to, or calling, an application program. This is accomplished according to a schedule, also encoded in memory, which defines the order (when and how often) in which the application programs should be called. The execution of all necessary programs in the schedule during a particular pass through the schedule is called a schedule cycle or main program cycle.

2.15 The No. 1A ESS switch employs a form of multiprogramming. During the execution of an application program, the application program returns (transfers) control to the main program when the work is completed, or when it can do no more until it receives the result of some input or output operation. Execution of the initial application program continues when the desired input is made available (or the desired output is completed) by other application programs called in by the main program. This process of seemingly performing many operations at once by interleaving them is often referred to as *multiprogramming*, and the time spent in a particular application program before it transfers controls to the main program is referred to as a *time* segment.

2.16 To give seemingly instantaneous response to input, control can be transferred from a program performing some less critical function to a program that must deal with a situation with a higher priority. This transfer process is referred to as an *interrupt*. Time is divided into time slots, and at the end of a time slot, the processor will interrupt the current program and give control to another program.

# REAL TIME AND PROCESSING CAPACITY

2.17 The organization of the program of the No. 1A ESS switch is influenced by the fact that it must operate in *real time*. That is, the program must respond promptly to signals and data submitted to it by customers and other switching systems. Failure to do so may result in improper handling of calls and a general degradation of service. For example, failure to detect dialed digits may result in directing a call to a wrong number, or failure to outpulse digits to another office will cause the other office to return overflow tone to the calling subscriber. Delays in performing some program tasks have more impact on the quality of service rendered than others. Therefore, all program tasks are organized

into a hierarchy of execution; some tasks are executed on a strict schedule, while others may be delayed without significant adverse effects on the service rendered.

2.18 Another more important use of the term real time relates to the availability and use of processor cycles. The basic processor unit of measurement used to describe the time required to execute an instruction is called a processor cycle. The base processor cycle time in a No. 1A ESS switch is 700 nanoseconds. To execute a specific program instruction, a fixed amount of processor cycles are expended; the more complex the instruction to be executed, the more processor cycles are required to complete the instruction. The relative complexity of the task to be performed by the program can best be measured by the number of processor cycles required to process the task.

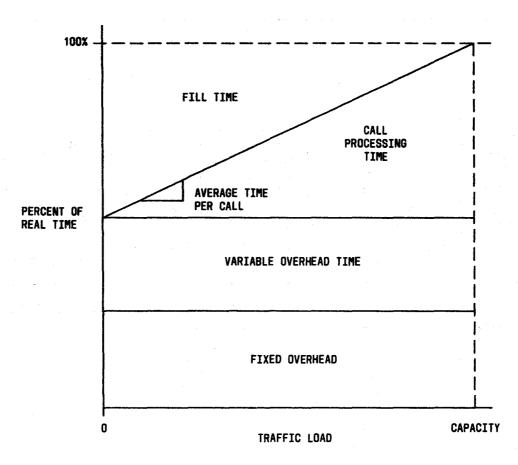

- **2.19** Generally speaking, total real time may be segmented into the following categories:

- Call processing work

- Overhead work

- Fill work.

## 3. PROGRAM PHILOSOPHY AND ORGANIZATION

### GENERAL

**3.01** The stored program for the No. 1A ESS switch

constitutes the operating intelligence of the system. The stored program must direct switching functions reliably and promptly, require minimal memory space and execution time, and accommodate office growth easily. In addition, the stored program must have the capability to recognize malfunctions within the system, diagnose the problem, and dictate corrective actions in such a way that the primary work of processing calls is not significantly affected.

# **3.02** The stored program is considered *generic* in

the sense that the instructions which control the operation of the system are the same for any office with the same generic program and selected features. Specific equipment quantities, subscriber features, routing patterns, etc, which are unique to a particular office, are looked up in separate tables (translations and parameters) and are not embedded in the program itself. Therefore, during office growth, the central processing community is able to recognize equipment additions and new subscriber lines by changes in the translation and parameter tables and updates in the call store to accommodate the additional demand. No modifications to the existing generic program are required.

3.03 Historically, the generic program of the No. 1A ESS switch has undergone modifications which affect the call processing capacity of the system. These modifications include new feature capability and improved programming and scheduling strategies. Furthermore, effective with generic program 1AE4, it is possible to "customize" the generic program selected for an office using the concept of feature loading. Feature loading is a concept whereby certain features of the generic program are designated as "base" and are required for all offices using the No. 1A ESS switch, while others are obtained via "feature groups" which are optionally loaded, based on the particular needs of the office. Feature loading differs significantly from previous programs which required that all features offered be installed in all offices with the same issue of a generic program, whether required or not.

# CATEGORIES OF WORK AND PROGRAMS

**3.04** The total amount of time utilized by a 1A processor can be divided into one of the four following classifications.

(1) Fixed overhead is the time used by the processor which is independent of the amount of traffic (number and type of calls), the amount of equipment, and memory configuration. Examples of tasks included in fixed overhead are: basic logic time utilized by the main program schedule, and time utilized to increment certain standard traffic, network maintenance, or administrative measurement counters.

(2) Variable overhead is the time utilized by functions which are constant for a particular No. 1A ESS switch but may vary office to office dependent upon equipment configuration. An example of variable overhead time is time utilized for scanning line or trunk equipments.

(3) Call processing is the time utilized by all tasks which are generated by the call load on the office. When there is no demand for service, there is no requirement for call-processing time. Thus, call-processing time required is completely dependent on the offered load.

(4) *Fill* is that amount of time which remains after all the above classifications (fixed and variable overhead, and call processing) have been satisfied. During fill time, deferrable tasks such as audits are performed.

# SCHEDULING

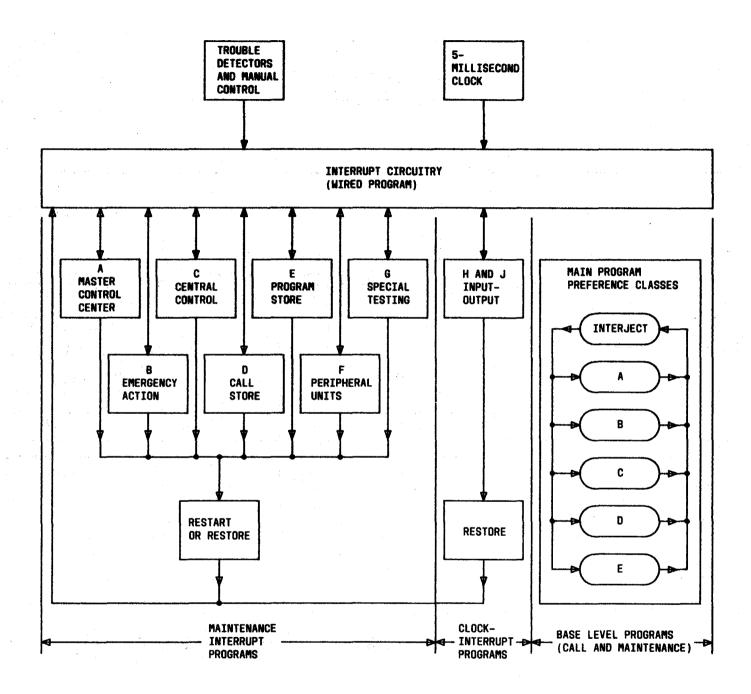

3.05 The 1A processor operates within its program hierarchy to use its time among the four basic classifications of use described in paragraph 3.04. Figure 2 illustrates the overall plan of base-level programs (interject and A through E) and the interrupt programs (A through F and H and J). Table A presents the source conditions for the interrupt levels for No. 1A ESS switches.

**3.06** All base-level programs are controlled by the executive control main program. The interrupt levels and their associated programs are arranged in a hierarchy of ten (in descending alphabetical order).

The call processing function of the processor 3.07 is associated mainly with the J-level interrupt and base level (L). The No. 1A ESS switch, unlike the No. 1 ESS switch, does not follow a predetermined order for base-level program execution. The No. 1A ESS switch has refined and enlarged the design of base-level programs. The base-level frequency classes are retained and remain internally intact from a functional viewpoint. However, the method of visiting the classes is changed. In general, a given class is not entered unless a flag has been set by a Jlevel routine to execute that particular class or job. This results in performing or looking for work "only when it is time to do so." See Section 231-045-000 for more details on processor operation. See Section 231-061-400 for a description of hierarchy of visitation of the No. 1 ESS switch, for comparison.

3.08 Input work involves the detection of inputs (such as on-hooks, off-hooks, and digit pulses) via the peripheral equipment scanners, and reporting the occurrence of these inputs to call processing programs. Output work involves the transmission of output information, often in the form of requests for equipment relay actions from other programs (such as call processing) to the peripheral equipment. The deferrable (base level) programs process data which are already registered in the system and, on this basis, are not as critical with respect to real time as nondeferrable programs.

**3.09** The execution of the steps necessary for call

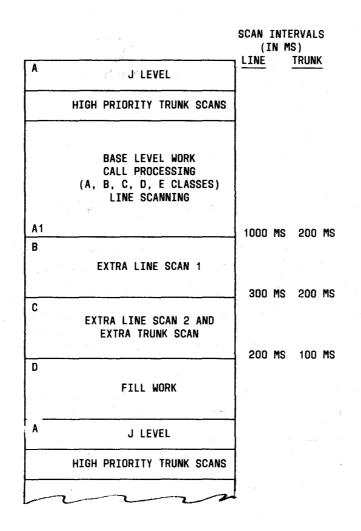

processing is under the direction of the executive control (main) program. Input work (scanning of lines and trunks) is scheduled at a variable interval in relationship to the offered load. Figure 3, discussed later in greater detail, depicts the tasks associated with input/output and call-processing which may be included in a main program cycle. These tasks, entered at the J-level interrupt, include high priority trunk scans, base-level work (call processing), additional line and trunk scans, and fill work. Figure 3 also depicts the change in the scan interval of lines and trunks, as the offered load increases. During periods of a very high volume of traffic (load), only the mandatory tasks (A-A1) may be performed with a line scan interval of 1000 ms and a trunk scan interval of 200 ms. The tasks, depicted in Fig. 3, are arranged in descending order of priority.

3.10 A large number of peripheral equipment items must be monitored at precisely defined intervals by input-output programs at the J level. Two programming techniques have been incorporated into the stored program to satisfy the strict timing requirements:

(a) The individual tasks performed by input/ output programs are of relatively short duration in comparison with tasks performed in base level.

(b) Base-level programs are periodically interrupted so the system can transfer control to the J level for input/output work. A clock interrupt control triggers the interrupt sequencing circuit every 5 milliseconds. This allows the current base level instruction to be completed, inhibits the next instruction, stores the address of the next instruction, and transfers control to the J level. This time-table interrupt scheme, for example, ensures that dial pulse receivers involved in a call are scanned for pulse detection at a 10-millisecond rate. When all input/output work has been completed, control is returned to base level at the point at which the interrupt occurred.

3.11 At the beginning of the J-level interrupt (Fig. 3) in the mandatory range of tasks is the high-priority trunk scan. This is related to the variable

trunk scan, and is given this priority to ensure that the trunk scan rate does not exceed 200 milliseconds.

3.12 Next in the order of priorities are the base-

level programs. Most of the nondeferrable work performed in the base level is call processing work initiated by input programs. Due to delay tolerance of the various application programs, the base level tasks are categorized into one of five classes, designated a, b, c, d, and e.

**3.13** During periods of a low volume of traffic, the

various base-level classes are scheduled to provide a minimum interval between successive executions of a particular task. These minimum intervals are: class a, 10 milliseconds; class b, 20 milliseconds; class c, 40 milliseconds; class d, 50 milliseconds; and class e, 100 milliseconds. Thus, when traffic is light, the remaining real time is used by the processor to scan additional lines, trunks, and to perform maintenance and administrative (fill) tasks.

3.14 During periods of low traffic volume, the processor time available allows additional line scanning (item B, Fig. 3), and lines in the office will be scanned once every 300 milliseconds. When processor time permits item C to be completed, all lines in the office are scanned every 200 milliseconds and all trunks every 100 milliseconds, with the exception of operator trunks which are scanned at a 50-millisecond interval.

**3.15** The scheduling of programs utilizes the following concepts to achieve the call processing design objective:

(a) Fixed minimum interval between baselevel class execution rates—to achieve maximum additional scanning and maintenance activities during periods of low traffic.

(b) **Variable line and trunk scan**—to maintain balance between these tasks and the call processing capability.

(c) High priority trunk scanning and line scanning—to ensure a minimum line and trunk scan interval.

**3.16** A fixed amount of overhead per class visit is spent scanning hoppers, queues, etc, for work during periods of low volume of traffic. As the traffic

volume increases, more work is found in each class, therefore more time is spent in each class. During peak loads, a limitation on the number of originating and incoming calls per main program cycle is imposed, which reduces the work to be processed per class visit, thus reducing the time spent in each class. As class intervisit times decrease, due to less work per class, the traffic allowed into the system increases; thus, producing a self-regulating control mechanism or dynamic processor equilibrium.

# 4. ENGINEERING CONSIDERATIONS

# GENERAL

**4.01** The primary goal of processor traffic engineering is to realize the maximum number of main stations and/or trunks, with given calling characteristics, that can be handled by the processor without exceeding service constraints placed upon the system.

4.02 The call processing capacity (hereafter referred to as capacity) of the processor is the maximum number of originating plus incoming (0 +I) calls which the processor can process in some fixed interval of real time while all service criteria, such as dial-tone delay have been satisfied. The fixed interval of time used in capacity estimation is the peak hour. The capacity of a processor also may be defined as the number of calls which the processor can process as spare real time approaches zero (that is, as spare real time is exhausted). This level of capacity is expressed as a percentage termed 100 percent occupancy. Beyond this level, the processor can still process calls, but service criteria may not be met; if service criteria cannot be met, the processor is said to be overloaded.

**4.03** The projected or forecasted main station and trunk call volumes (types and mixes) for a control group may exceed the capacity of the processor. In this case, consideration must be given to changing the office call and equipment mix by moving some types of traffic (coin, etc) to another switching entity, restricting traffic, or establishing a new control group.

4.04 Service criteria have been established providing a standard measurement of system performance, as discussed in Section 231-060-100. As with all traffic (load) sensitive components, the selection of service objectives for processors is the result of adjustments balancing customer performance requirements and the economics of achieving specific service objectives. The major service objective that limits processor capacity is a maximum of 20 percent dial-tone delay greater than 3 seconds in the busiest hour of the highest day of the year.

4.05 When the demand for service requires more processor time than is available to process the demand, pulses are missed, and ringing and recognition of trunk and line service requests are delayed for unacceptable periods. To avoid such a situation, overload controls are designed into the processor. When it is determined that certain constraints are not being met, the number of service requests accepted by the processor is decreased until an equilibrium point is reached. See paragraph 4.11 for a description of IOS and ESP.

4.06 Although overload strategies are not the sub-

ject of this document, they, in conjunction with service criteria, have a major influence on the program organization.

# **INFLUENCING FACTORS**

#### A. Types of Calls and Equipment

4.07 For a given office, the capacity of the processor is dependent upon the types and relative proportions of calls (aggregately referred to as the call mix) offered to the office, the quantity and types of lines and trunks, and the associated switching equipment in the office.

4.08 A major portion of real time is used for scanning equipment for changes in state, ie, scanning for line originations or disconnects on existing connections. The amount of time utilized by this function is directly related to the amount of equipment in the office. An overprovision of equipment has an adverse effect on real-time capacity; thus, it is important that the amount of equipment provided be in harmony with the total design of the office, particularly as an office approaches real-time capacity.

**4.09** The call mix offered to an office determines the average amount of real time that is utilized per call by the processor. The average time spent per call corresponds to the slope of the call processing line on Fig. 4. The average amount of real time utilized per call is directly related to the number of processor cycles that must be executed to process the call. In general, the more complex the call the greater the number of processor cycles required. The fewer processor cycles required for the average call, the greater the call capacity. This accounts for the capacity differential between an office serving an area which consists mainly of centrex, coin, and other more complex services, and an office which serves a primarily residential area.

# B. Generic Program

4.10 The generic program installed in an office will affect the call-processing capacity. The number of cycles required for a particular type call is dependent on the program and may vary from one issue of the generic program to the next. A history of call processing capacities of the No. 1A ESS switch is shown in Fig. 5. The capacities are shown as ranges that correspond to some hypothetical, but realistic, call mixes. The real time impact of optional features is not reflected. The most significant improvement in call capacity occurred with the introduction of fast 256K program store and call store frames. The call capacity improvement may only be obtained in a pure community of fast 256K call stores. See Section 231-062-473 for a detailed discussion on fast 256K stores.

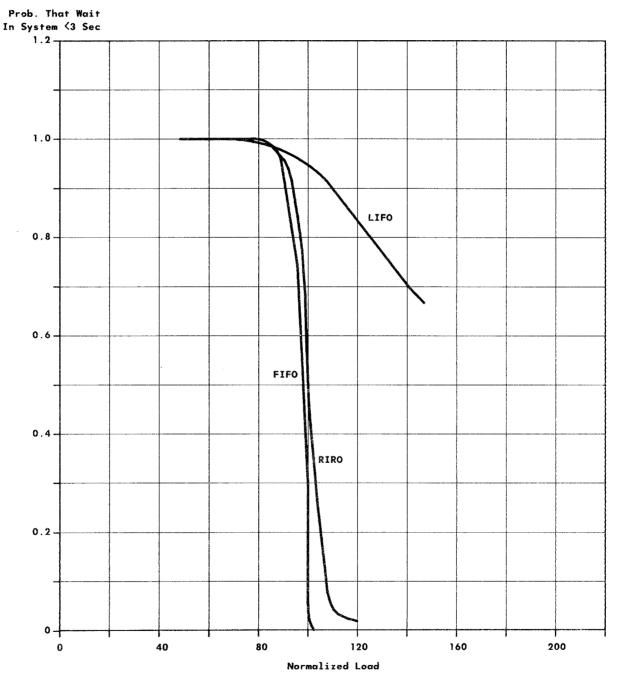

Starting with the 1AE6, Issue 5B generic, 4.11 Improved Overload Strategy (IOS) will be available in the offices of the No. 1A ESS switch. The line servicing strategy in the No. 1A ESS switch prior to IOS is random-in-random-out (RIRO) with a queue available when there are no available customer digit receivers (CDRs) for dial tone service. With the implementation of IOS, a line service request hopper (LSRH) will be instituted in the No. 1A ESS switch. The IOS consists of Last-In-First-Out (LIFO) servicing of the LSRH and the elimination of the CDR queue. The IOS in the No. 1A ESS switch maintains the line scan rate at a maximum interval of one second. Figure 6 illustrates a comparison of the probability of providing dial-tone delay at less than three seconds under the three conditions, LIFO, first infirst out (FIFO) (No. 1 ESS switch prior to IOS) and RIRO. Included with IOS is priority service for essential lines, Essential Service Protection (ESP), that provides dynamic and continuous overload protection and replaces line load control. See Feature Document Section 231-090-195 for more details on IOS/ESP.

# C. Network and Trunk Blocking

**4.12** Network blocking also may affect processor capacity. Blocking creates excessive path

hunts, resulting in the use of more real time to establish calls. In addition, excessive alternate routing reduces the capacity of the processor. Assuming proper traffic engineering of both networks and trunk groups, network blocking and alternate routing normally have a small effect on processor capacity, and are ignored in the processor capacity estimation procedures.

#### D. False Cross and Ground and Restore-Verify Tests

4.13 A false cross and ground test is made by the processor on new network paths to check for damaging voltages (foreign potentials). In addition, the processor makes a restore-verify test after a line disconnects to ensure that the connection between the line and its ferrod have been properly restored. Both of these tests are preventive maintenance techniques. They are not considered to be essential during a period of high-traffic volume and are temporarily suspended as the processor approaches its call-processing capacity. This has the effect of reducing the average work time per call, ie, the number of processor cycles per call.

# CALL PROCESSING CAPACITY ESTIMATION AN INTRO-DUCTION TO ESTIMATION AIDS

# A. Precutover Aids

4.14 Precutover aids, also referred to as model methods, use mathematical models and user supplied call type, call mix, and equipment data to estimate the call processing capacity of a processor. Precutover aids can be used for initial office installation planning, for offices scheduled for generic retrofits, and for in-service offices anticipating substantial amounts of additional equipment or a call mix different from that currently being served. Computerized precutover aids exist which minimize the possibility of calculation errors, and allow investigation of the effects of alternate call mixes (often to reflect the uncertainties of predictions). They also allow for ease of update of internal coefficients for new generic programs.

4.15 For 1A processor precutover capacity estimation, manual methods are not available. The GO CALL CAPACITY function of the Central Office Equipment Engineering System (COEES) is the mechanized tool available. This method is described in Section 231-062-410.

# B. Postcutover Aids

Postcutover aids, also referred to as measured 4.16 data analysis methods, use measured data from the processor of an in-service office to determine the call processing capacity of that processor. Postcutover aids are used for in-service office ultimate capacity estimation when there is no significant change contemplated in the call mix, the equipment relationship, and the generic program issue from that existing during the data collection periods. Postcutover aids are available in both a computerized and manual version. The computerized version reduces calculation errors, removes unacceptable data, and reduces the amount of administrator work time that is required with the manual method.

For the 1A processor estimation of ultimate 4.17 capacity, CAPFIT is the mechanized system and C<sub>FUTURE</sub> is the manual procedure. The CAPFIT is the more accurate method and is the preferred, recommended method, but is available only in those offices with the Engineering and Administrative Data Acquisition System/Network Operations Report Generator System (EADAS/NORGEN). For those offices without EADAS/NORGEN, the manual calculation of C<sub>FUTURE</sub> must be used. The CAPFIT uses half-hourly data collected for the entire day and internally produces a peak hour call capacity statement. C<sub>EUTURE</sub> requires the use of quarter-hour data and produces a peak quarter-hour call capacity statement. The CAPFIT is available in the Stored Program Control System-Central Office Equipment Reports (SPCS-COER). Both methods are discussed in detail in Section 231-062-420.

#### **RECOMMENDATIONS AND DATA CONSIDERATIONS**

# A. Processor Occupancy

4.18 To measure the load on a processor of the No. 1A ESS switch, a measurement called processor occupancy has been developed and incorporated on the TC-15 output message format, as defined in the OM-6A001-01. Prior to 1AE4, this value is stated as a 2-digit number; with 1AE4, this value is expanded to include a decimal value, eg, 82.64. Processor occupancy, expressed in terms of a percent, is defined as the amount of time utilized in the mandatory range of tasks, divided by the total time in the real-time period. This value reflects the processor real time utilized in relation to the total real time available, based on the existing office configuration. To illustrate, as the amount of time spent in the loop  $A-A_1 \blacklozenge$  (Fig. 3) increases, less time is spent in the loop  $A_1 - A. \blacklozenge$  When all available time is utilized by  $A-A_1$ , the processor is at 100-percent occupancy.

#### B. Processor Busy Hour

- 4.19 Data used in processor capacity estimation should include the processor busy periods; the period of highest percent occupancy for the processor. Periods of highest percent processor occupancy may not necessarily correspond to periods of highest originating plus incoming calls. This may be true when such call types as plain old telephone service (POTS), coin, tandem, centrex, and bylink are served by the same office but have noncoincident busy periods.

- **4.20** The data collection and validation used by CAPFIT ensures the inclusion of the processor busy hour with the observation of many hours. For the  $C_{FUTURE}$  calculation, the period of highest percent processor occupancy and its corresponding O+I calls must be used as explained in Section 231-062-420. It is the responsibility of the network administrator to furnish this information.

- 4.21 For precutover estimation, the call mix corresponding to the busy hour with the highest O+I calls may be used for initial office installations or for growth situations where the mix will change significantly. In this case, other hours with different call volumes and mixes should also be analyzed when possible. For other growth situations using precutover estimation aids, the mixes corresponding to the known processor busy periods can be used.

# C. Quarter-Hour-to-Hour Conversion Factor

4.22 It is desirable to express the processor O+ I call capacity of a central office in terms of a peak hour. When manual capacity determination methods are used, the input data is peak quarterhour and the capacity is stated as peak quarter-hour capacity. In order to obtain peak-hour capacity output, the peak quarter-hour calls must be converted to peak-hour calls.

**4.23** When it is necessary to make conversions

from quarter-hour calls to peak hour calls, the following example illustrates the calculation. If a processor has a capacity of N calls in a quarter hour, it would seem that it has a capacity of four times N calls for the hour. However, call volume is generally not uniformly distributed over the four quarter hours in an hour. That is, there would never be four quarter hours with exactly N calls each, where N calls are the maximum that can be handled in a quarter hour and still satisfy service criteria. *Thus, the peak hour capacity is less* than four times N calls.

**4.24** To compensate for this problem, a quarterhour to hour conversion factor is applied when using  $C_{FUTURE}$ . The peak-hour capacity is estimated by multiplying the peak quarter-hour estimated capacity by this conversion factor. A method of calculating this quarter-hour conversion factor from measured call volume data for an in-service office is described in Section 231-062-420.4

# D. Peak Factor

**4.25** To determine the equivalent Average Busy Season (ABS) call processing capacity from the peak-hour estimated capacity, a conversion factor is required.

4.26 For an existing office, the high day (HD)/ABS peak factor is derived from data listed on the Office Count Data output from COER. ♦The data selected should be obtained from the processor busy hour.

**4.27** For an initial office, data gathered from an office with similar characteristics may be used. When data are unavailable, an HD/ABS peak factor of 1.3 is recommended.

4.28 ♦To state the peak-hour processor capacity in terms of ABS calls, divide the peak-hour calls by the HD/ABS peak factor.

# E. Capacity Utilization

4.29 Capacity utilization is the relationship of the actual (or expected) O+I calls processed to the maximum number of O+I calls which could be processed, meeting established service objectives. To determine the percent utilization of the call-processing capacity for an office, divide the highest

number of hourly O+I calls processed (or expected to be processed) by the ultimate peak-hour call capacity and multiply by 100. Using postcutover data, should the result differ greatly from the precutover utilization figure, it is likely that the call mix of the

office differs from that used as input to the precutover capacity determination procedure. If this occurs, an analysis of the call mix should be undertaken to resolve the discrepancy.

### **F.** Cutover Capacity Recommendations

**4.30** It is important that data used in estimating the call capacity of the processor represent the

true calling characteristics of the office. This is extremely critical in those cases where a substantially large portion of the processor call capacity is expected to be utilized during the engineering interval. Because of the relative uncertainties and inaccuracies which are part of any data projection, guidelines relating to processor loading for new offices (and some growth jobs) have been established. These guidelines provide a safety margin to minimize the possibility of overloading a processor at cutover, or shortly thereafter. These guidelines, which vary by office function are as follows:

- A local-only office is any end office which serves no class 4 or higher switching functions and where twice the total trunk to trunk junctor CCS is less than 20 percent of the total trunk link network CCS load. All local offices should be cut over with that quantity of main stations and trunks which will utilize no more than 90 percent of the calculated peak-hour processor call capacity.

- All other offices, ie, those that serve a class 4 or higher function or where twice the total trunk to trunk junctor CCS is 20 percent or more of the total trunk link network CCS load (local/tandem), should be cut over with that quantity of main stations or trunks which will utilize no more than 80 percent of the calculated peak-hour processor call capacity.

**4.31** The same loading thresholds discussed above for initial offices are also applicable to large growth additions in cases where there is doubt as to the applicability of the data available. The growth addition should be planned such that the forecasted processor utilization does not exceed the recommended percentages of processor capacity utilization discussed above for the corresponding office type.

**4.32** There may be situations where enough confidence in the engineering data exists to permit

initial cutovers or large growth additions to exceed the recommended percentages of processor utilization. This may be possible where the engineering data can be compared to a similar working No. 1A ESS switch. However, due to the severe service impact caused by an overloaded processor, this should be done with extreme caution.

**4.33** Once the cutover of the initial job or large growth unit has been completed, and accurate

machine data are available to permit validation of processor call capacity, additional growth may be planned to fully utilize the processor capacity. The precutover call capacity forecast should be validated by comparison with CAPFIT outputs when sufficient data is available. Care should be exercised not to exceed the engineered main station capacity of other machine components.

Fig. 1—No. 1A ESS Switch—Processor Community Block Diagram (2.01)

Fig. 2-No. 1A Processor Program Control Plan (3.06)

Fig. 3—No. 1A Processor Program Priority Structure (3.10, 3.12, 3.15)

Fig. 4-No. 1A ESS Switch-Division of Total Real Time (4.09)

CALL CAPACITY\* (PEAK CALLS/HOUR X 1000) 350 300 WITH FAST STORES **1AE6** 1AE 1 1AE4 **1AE5** 240 1AE7 1AE8 180 120 DEVELOPMENT GOAL 60 0 '78 '79 '80 '81 '82 '83 1984 1977 \* TYPICAL OFFICE SIZES AND BASE FEATURE CALL MIX ARE ASSUMED

Page 16

LIFO VERSUS FIFO OR RIRO

Fig. 6—Service Improvement with IOS (4.11)

# TABLE A

| LEVEL | SOURCE CONDITION                                                                                                           |

|-------|----------------------------------------------------------------------------------------------------------------------------|

| А     | Manually Initiated                                                                                                         |

| В     | Processor Configuration                                                                                                    |

| С     | Central Control Mismatch                                                                                                   |

| D     | Call Store Read/Write Failure<br>Auxiliary Unit Read/Write Failure<br>Protected Area Violation<br>Pushdown Stack Violation |

| Ε     | Program Store Read/Write Failure                                                                                           |

| F     | Peripheral Unit Failure                                                                                                    |

| G     | Maintenance Clock Time-Out<br>Special Match Function<br>Utility Computer                                                   |

| Н     | Interrupt J Level After 5 ms                                                                                               |

| J     | Interrupt Periodically After 5 ms                                                                                          |

# INTERRUPT LEVELS - NO. 1A ESS

Page 18 18 Pages