# Critical Release Notice

Publication number: 297-8991-805 Publication release: Standard 11.03

# The content of this customer NTP supports the SN06 (DMS) software release.

Bookmarks used in this NTP highlight the changes between the LEC0015 baseline and the current release. The bookmarks provided are color-coded to identify release-specific content changes. NTP volumes that do not contain bookmarks indicate that the LEC0015 baseline remains unchanged and is valid for the current release.

### **Bookmark Color Legend**

Black: Applies to new or modified content for LEC0015 that is valid through the current release.

Red: Applies to new or modified content for SN04 (DMS) that is valid through the current release.

Blue: Applies to new or modified content for SN05 (DMS) that is valid through the current release.

Green: Applies to new or modified content for SN06 (DMS) that is valid through the current release.

Attention!

Adobe® Acrobat® Reader<sup>TM</sup> 5.0 or higher is required to view bookmarks in color.

### **Publication History**

### **June 2005**

Standard release 11.03 for software release SN06 (DMS). Updates made for this release are shown below:

### Volume 5

Added NTDX16AA (Q00946403)

### March 2004

Standard release 11.02 for software release SN06 (DMS). Updates made for this release are shown below:

### Volumes 1-3

No changes

### Volume 4

Card NT9X30AB is Manufacture Discontinued and is replaced by new card NT9X30AC.

### Volume 5

No changes

### September 2003

Standard release 11.01 for software release SN06 (DMS). Updates made for this release are shown below:

### Volumes 1-4

No changes

### Volume 5

Updates were made to NT9X76AA according to CR Q00177945.

### 297-8991-805

DMS-100 Family

### **Hardware Description Manual**

Volume 5 of 5

2001Q1 Standard 09.01 March 2001

DMS-100 Family

### **Hardware Description Manual**

Volume 5 of 5

Publication number: 297-8991-805

Product release: 2001Q1

Document release: Standard 09.01

Date: March 2001

Copyright © 1994-2001 Nortel Networks, All Rights Reserved

Printed in the United States of America

**NORTEL NETWORKS CONFIDENTIAL:** The information contained herein is the property of Nortel Networks and is strictly con dential. Except as expressly authorized in writing by Nortel Networks, the holder shall keep all information contained herein con dential, shall disclose the information only to its employees with a need to know, and shall protect the information, in whole or in part, from disclosure and dissemination to third parties with the same degree of care it uses to protect its own con dential information, but with no less than reasonable care. Except as expressly authorized in writing by Nortel Networks, the holder is granted no rights to use the information contained herein.

Information is subject to change without notice. Nortel Networks reserves the right to make changes in design or components as progress in engineering and manufacturing may warrant. Changes or modi cations to the DMS-100 without the express consent of Nortel Networks may void its warranty and void the user's authority to operate the equipment

Nortel Networks, the Nortel Networks logo, the Globemark, How the World Shares Ideas, Uni ed Networks, DMS, DMS-100, Helmsman, MAP, Meridian, Nortel, Northern Telecom, NT, and SuperNode are trademarks of Nortel Networks.

### **Contents**

### Volume 5 of 5

```

1

1-1

NT9Xnnaa (continued)

NT9X74CA through NT9X98AA (continued from Vol. 4) 1-1

NT9X74CA 1-2

NT9X74DA 1-9

NT9X75AA 1-15

NT9X76AA 1-22

NT9X76BA 1-27

NT9X76CA 1-32

NT9X77AA 1-36

NT9X77AB

1-40

NT9X77BA 1-44

NT9X78AA 1-49

NT9X78BA 1-55

NT9X78CA 1-60

NT9X79AA 1-65

NT9X79BA

1-71

NT9X79BB

1-78

NT9X80CA 1-84

NT9X84AA 1-88

NT9X85AA 1-93

NT9X86AA 1-100

NT9X87AA 1-111

NT9X88AA 1-116

NT9X89AA 1-126

NT9X89BA 1-132

NT9X91AA 1-140

NT9X91AB 1-147

NT9X95AA 1-154

NT9X95SA

1-164

NT9X96AA 1-167

NT9X98AA 1-176

2

2-1

NTAXnnaa

NTAX78AA through NTAX87AA 2-1

NTAX78AA 2-2

```

NTAX78BA 2-10

NTAX87AA 2-18

| 3 | NTBXnnaa                  | 3-1 |

|---|---------------------------|-----|

|   | NTBX01AA through NTBX72AA | 3-1 |

|   | NTBX01AA 3-2              |     |

|   | NTBX01AB 3-7              |     |

|   | NTBX01AC 3-14             |     |

|   | NTBX01BA 3-21             |     |

|   | NTBX02AA 3-28             |     |

|   | NTBX02BA 3-34             |     |

|   | NTBX25AB 3-40             |     |

|   | NTBX26AA 3-44             |     |

|   | NTBX27AA 3-51             |     |

|   | NTBX30AB 3-54             |     |

|   | NTBX31AA 3-57             |     |

|   | NTBX31AC 3-60             |     |

|   | NTBX31BA 3-64             |     |

|   | NTBX32BA 3-68             |     |

|   | NTBX34AA 3-73             |     |

|   | NTBX34AB 3-75             |     |

|   | NTBX34BA 3-77             |     |

|   | NTBX34BC 3-79             |     |

|   | NTBX34CA 3-81             |     |

|   | NTBX34CB 3-83             |     |

|   | NTBX34DA 3-85             |     |

|   | NTBX35AA 3-87             |     |

|   | NTBX36AA 3-89             |     |

|   | NTBX36BA 3-91             |     |

|   | NTBX37AB 3-98             |     |

|   | NTBX40AA 3-101            |     |

|   | NTBX71AA 3-104            |     |

|   | NTBX72AA 3-109            |     |

| 4 | NTCXnnaa                  | 4-1 |

|   | NTCX07AB through NTCX50BA | 4-1 |

|   | NTCX07AB 4-2              |     |

|   | NTCX08AB 4-7              |     |

|   | NTCX50AA 4-15             |     |

|   | NTCX50AB 4-19             |     |

|   | NTCX50BA 4-24             |     |

| 5 | NTDXnnaa                  | 5-1 |

|   | NTDX15AA through NTDX15AB | 5-1 |

|   | NTDX15AA 5-2              |     |

|   | NTDX15AB 5-9              |     |

| 6 | NTEXnnaa                  | 6-1 |

|   | NTEX01AB through NTEX78AA | 6-1 |

|   | NTEX01AB parts 6-2        |     |

|   | NTEX17AA 6-7              |     |

|    | NIEX1/BA     | 6-12             |      |      |

|----|--------------|------------------|------|------|

|    | NTEX17CA     |                  |      |      |

|    | NTEX17DA     | 6-23             |      |      |

|    | NTEX20AA     | 6-29             |      |      |

|    | NTEX20BA     | 6-32             |      |      |

|    | NTEX22AA     | 6-35             |      |      |

|    | NTEX22BA     | 6-41             |      |      |

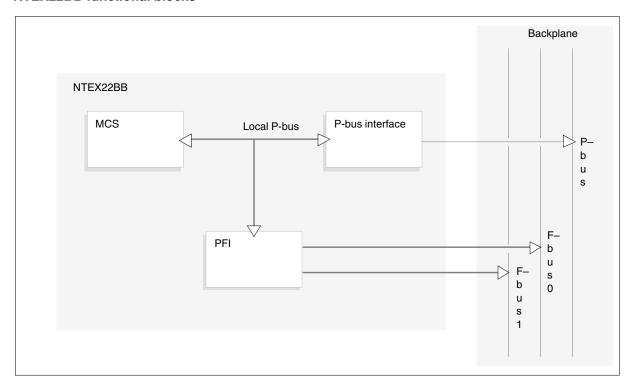

|    | NTEX22BB     | 6-45             |      |      |

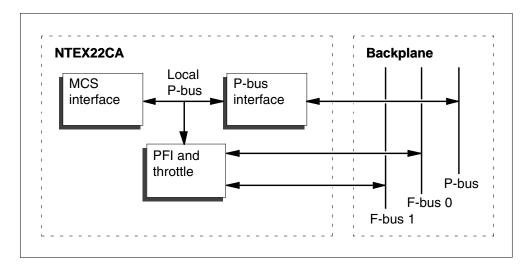

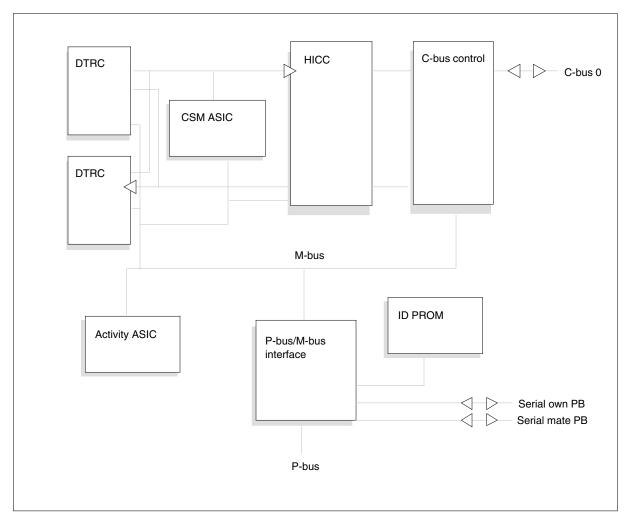

|    | NTEX22CA     | 6-50             |      |      |

|    | NTEX25AA     | 6-56             |      |      |

|    | NTEX25BA     | 6-60             |      |      |

|    | NTEX26AA     | 6-64             |      |      |

|    | NTEX26BA     | 6-68             |      |      |

|    | NTEX28AA     | 6-79             |      |      |

|    | NTEX30AA     | 6-88             |      |      |

|    | NTEX31AA     | 6-95             |      |      |

|    | NTEX31BA     | 6-104            |      |      |

|    | NTEX54AA     | 6-110            |      |      |

|    | NTEX54AB     | 6-114            |      |      |

|    | NTEX54BA     |                  |      |      |

|    | NTEX54CA     |                  |      |      |

|    | NTEX76AA     |                  |      |      |

|    | NTEX78AA     |                  |      |      |

| 7  | NTFXnnaa     |                  |      | 7-1  |

|    | NTFX09AA     | through NTFX44AA | 7-1  |      |

|    | NTFX09AA     |                  |      |      |

|    | NTFX10AA     |                  |      |      |

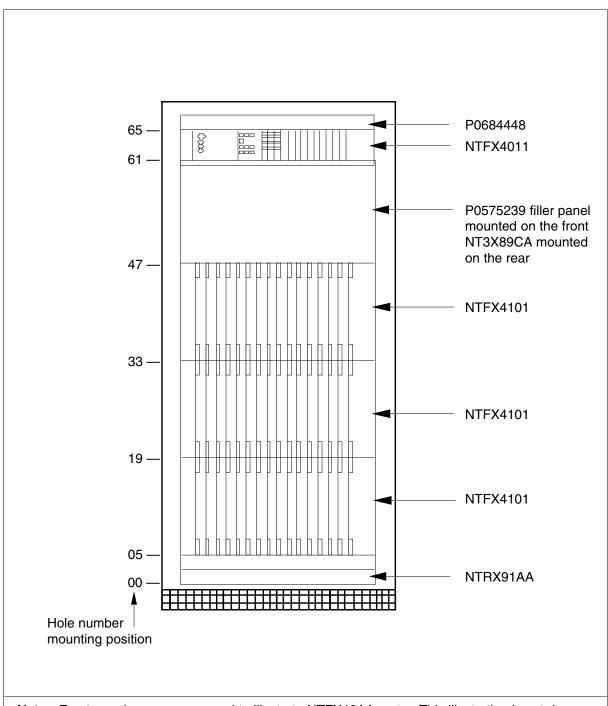

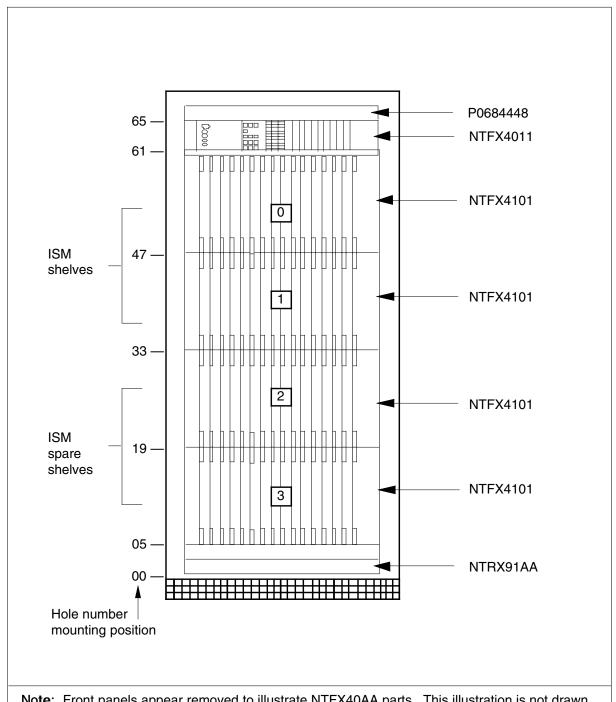

|    | NTFX40AA     |                  |      |      |

|    | NTFX40BA     |                  |      |      |

|    | NTFX40EA     |                  |      |      |

|    | NTFX40FA     |                  |      |      |

|    | NTFX4101     |                  |      |      |

|    | NTFX42AA     |                  |      |      |

|    | NTFX43AA     |                  |      |      |

|    | NTFX44AA     |                  |      |      |

| 8  | NTKXnnaa     |                  |      | 8-1  |

| •  |              | 8-1              |      |      |

|    |              | 8-2              |      |      |

| 9  | NTGXnnaa     |                  |      | 9-1  |

| -  | NTGX01AA     | 9-1              |      |      |

|    | NTGX01AA     |                  |      |      |

| 10 | NTMXnnaa     |                  |      | 10-1 |

|    |              | through NTMX99AA | 10-1 |      |

|    | NTMX45AA     | •                |      |      |

|    | NTMX43AA     |                  |      |      |

|    | NTMX71AA     |                  |      |      |

|    | INTIVIAL IDA | 10 10            |      |      |

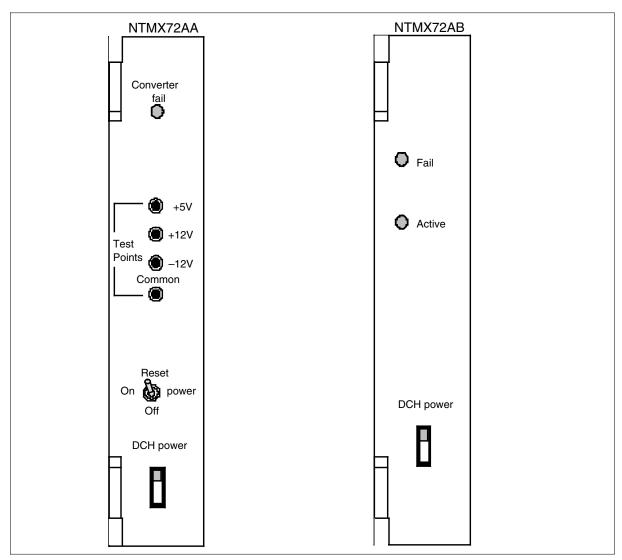

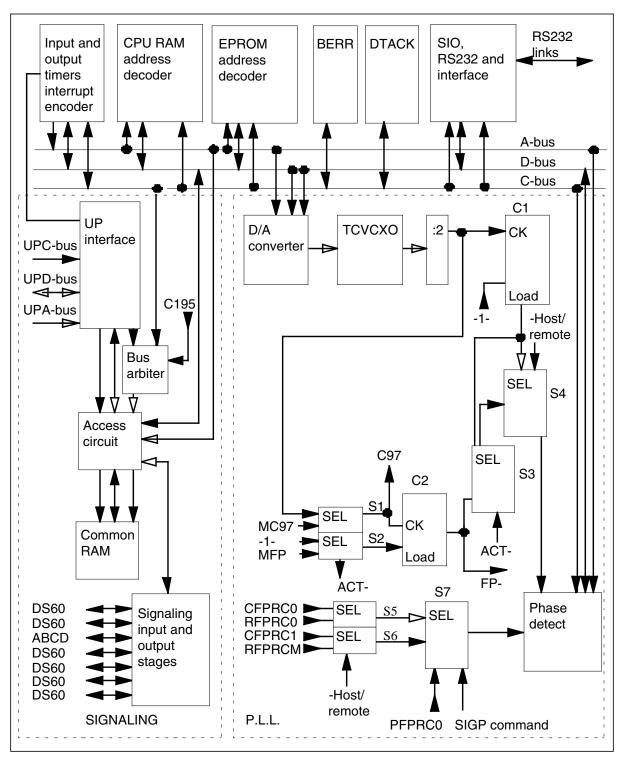

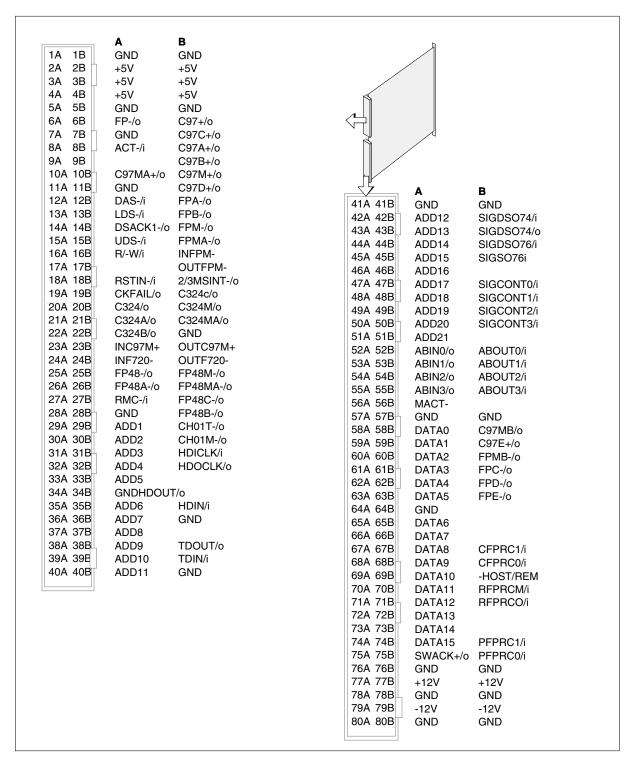

|    | NTMX72AA 10-16 NTMX72AB 10-23 NTMX73AA 10-30 NTMX74AA 10-37 NTMX75AA 10-43 NTMX76AA 10-49 NTMX76BA 10-56 NTMX76CA 10-62 NTMX77AA 10-66 NTMX79AA 10-75 NTMX81AA 10-81 NTMX82AA 10-86 NTMX82CA 10-91 NTMX87AA 10-96 NTMX97AA 10-99 NTMX99AA 10-107 |      |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 11 | NTNPnnaa                                                                                                                                                                                                                                         | 11-1 |

|    | NTNP20AA through NTNP50AA                                                                                                                                                                                                                        |      |

|    | NTNP20AA 11-2                                                                                                                                                                                                                                    |      |

|    | NTNP32AA 11-4                                                                                                                                                                                                                                    |      |

|    | NTNP44AA 11-8                                                                                                                                                                                                                                    |      |

|    | NTNP50AA 11-12                                                                                                                                                                                                                                   |      |

| 12 | NTNXnnaa                                                                                                                                                                                                                                         | 12-1 |

|    | NTNX13CA through NTNX65BA                                                                                                                                                                                                                        | 12-1 |

|    | NTNX13CA 12-2                                                                                                                                                                                                                                    |      |

|    | NTNX14AA 12-6                                                                                                                                                                                                                                    |      |

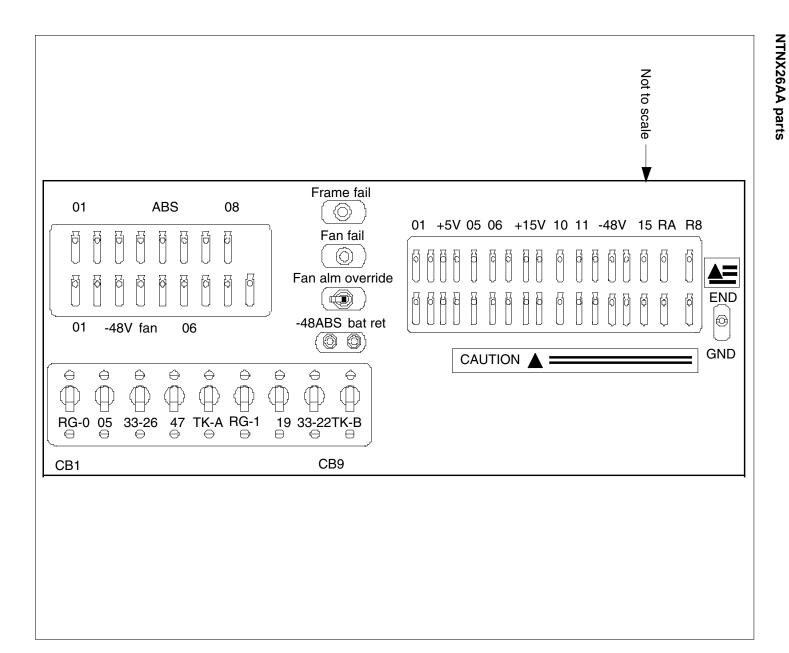

|    | NTNX26AA 12-9                                                                                                                                                                                                                                    |      |

|    | NTNX27AA 12-12                                                                                                                                                                                                                                   |      |

|    | NTNX27CA 12-14                                                                                                                                                                                                                                   |      |

|    | NTNX27DA 12-16                                                                                                                                                                                                                                   |      |

|    | NTNX51BD 12-18<br>NTNX63AB 12-30                                                                                                                                                                                                                 |      |

|    | NTNX65BA 12-34                                                                                                                                                                                                                                   |      |

|    | NTINAOSDA 12-54                                                                                                                                                                                                                                  |      |

| 13 | NTNYnnaa                                                                                                                                                                                                                                         | 13-1 |

|    | NTNY01AA through NTNY23AA                                                                                                                                                                                                                        | 13-1 |

|    | NTNY01AA 13-2                                                                                                                                                                                                                                    |      |

|    | NTNY17AA 13-9<br>NTNY23AA 13-13                                                                                                                                                                                                                  |      |

|    | NTINYZJAA 13-13                                                                                                                                                                                                                                  |      |

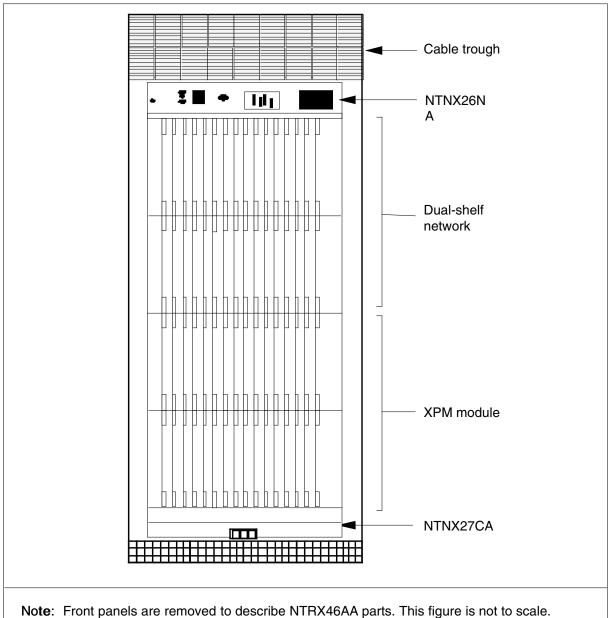

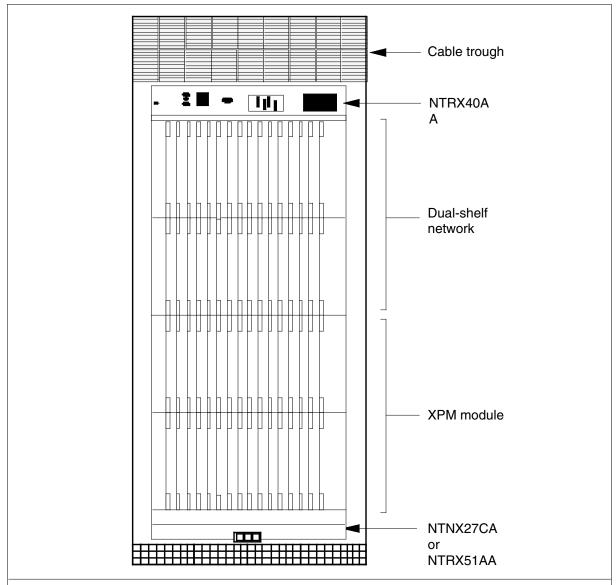

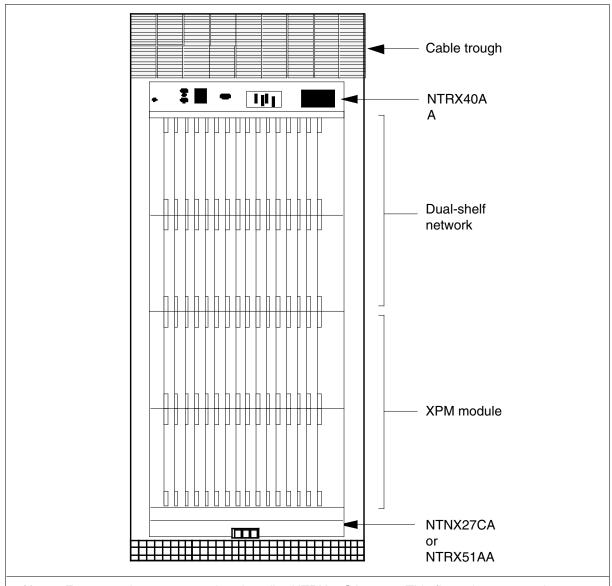

| 14 | NTRXnnaa                                                                                                                                                                                                                                         | 14-1 |

|    | NTRX2572 through NTRX91AA                                                                                                                                                                                                                        | 14-1 |

|    | NTRX2572 14-2                                                                                                                                                                                                                                    |      |

|    | NTRX30AA 14-8                                                                                                                                                                                                                                    |      |

|    | NTRX30BA 14-11                                                                                                                                                                                                                                   |      |

|    | NTRX30CA 14-14                                                                                                                                                                                                                                   |      |

|    | NTRX30DA 14-17                                                                                                                                                                                                                                   |      |

|    | NTRX31AA 14-20                                                                                                                                                                                                                                   |      |

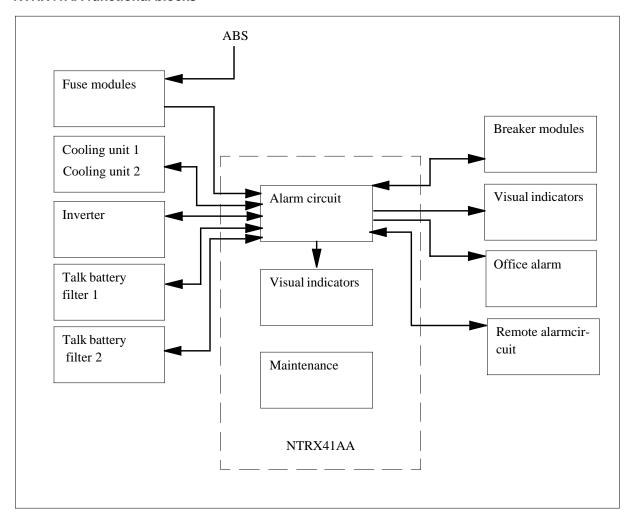

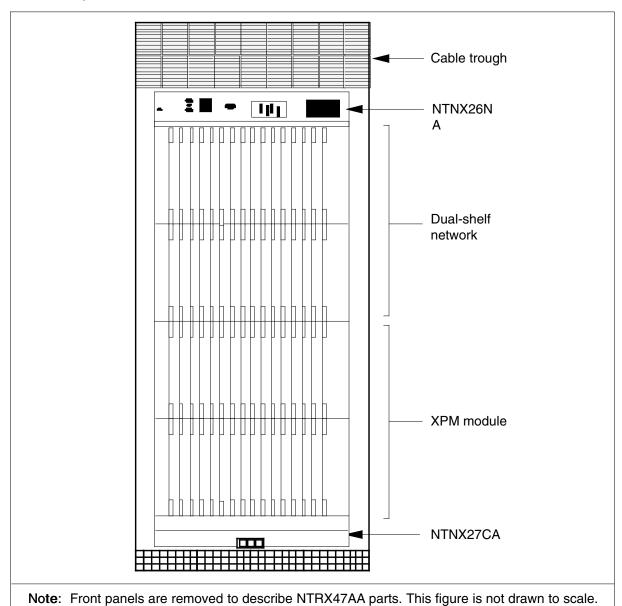

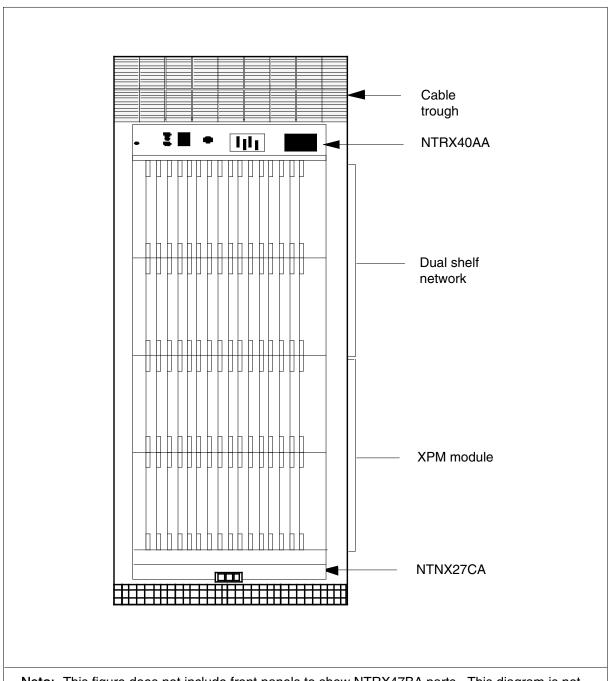

NTRX31BA 14-32 NTRX31CA 14-44 NTRX31DH 14-53 NTRX32AA 14-56 NTRX32BA 14-59 NTRX32CA 14-62 NTRX33AA 14-65 NTRX33CA 14-69 NTRX33DA 14-73 NTRX34AB 14-77 NTRX34BA 14-82 NTRX35AA 14-86 NTRX35BA 14-89 NTRX35CA 14-92 NTRX36AB 14-95 NTRX36BA 14-98 NTRX37AA 14-101 NTRX37BA 14-104 NTRX37CA 14-109 NTRX38AA 14-112 NTRX38BA 14-115 NTRX38CA 14-119 NTRX40AA 14-122 NTRX41AA 14-130 NTRX42AA 14-134 NTRX42BA 14-138 NTRX42CA 14-142 NTRX43AA 14-146 NTRX44AA 14-148 NTRX46AA 14-152 NTRX46BA 14-154 NTRX46CA 14-157 NTRX47AA 14-160 NTRX47BA 14-162 NTRX48AA 14-165 NTRX48BA 14-167 NTRX49AA 14-169 NTRX49BA 14-172 NTRX50FA 14-175 NTRX54AA 14-184 NTRX54BA 14-190 NTRX56AA 14-194 NTRX90AA 14-199 NTRX91AA 14-203

15 NTSXnnaa 15-1

NTSX05 through NTSX06 15-1 NTSX05 15-2 NTSX06 15-13

16-1 16 **NTTRnnaa** NTTR40AA through NTTR87AA 16-1 NTTR40AA 16-2 NTTR45AA 16-5 NTTR46AA 16-7 NTTR47AA 16-10 NTTR60AA 16-13 NTTR66AA 16-28 NTTR67AA 16-30 NTTR70AA 16-33 NTTR71AA 16-37 NTTR72AA 16-41 NTTR73AA 16-47 NTTR74AA 16-58 NTTR75AA 16-60 NTTR76AA 16-61 NTTR77AA 16-62 NTTR80AA 16-68 NTTR87AA 16-71

## 1 NT9Xnnaa (continued)

NT9X74CA through NT9X98AA (continued from Vol. 4)

### NT9X74CA

### **Product description**

The NT9X74CA frame transport bus (F–bus) repeater card buffers and reclocks signals between the intershelf F–bus and the intrashelf F–bus.

The CA version of the repeater card is like the BA version. The BA version has added firmware function to query the identification (ID) PROM of the NTEX20AA and BA.

### Location

The NT9X74CA is on each link interface shelf (LIS) at card locations 07 and 32. These card locations correspond to card slots 1 and 26.

### **Functional description**

The NT9X74CA provides the following functions:

- buffer and reclock the F-bus signals

- loopback capabilities

- access to card IDs

The system requires only one version of the repeater board. This requirement occurs because of the way the two independent F-buses are run across the link interface shelf backplane (9X72AA). The repeater board in slot 07 drives the F-bus 0. The same repeater board in slot 32 drives the F-bus 1. The far-end terminations for each F-bus are available on the EX20AA and the BA paddle boards.

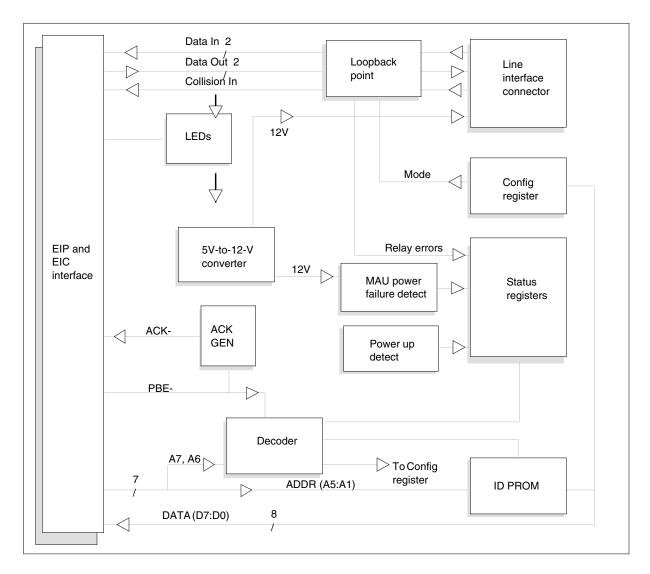

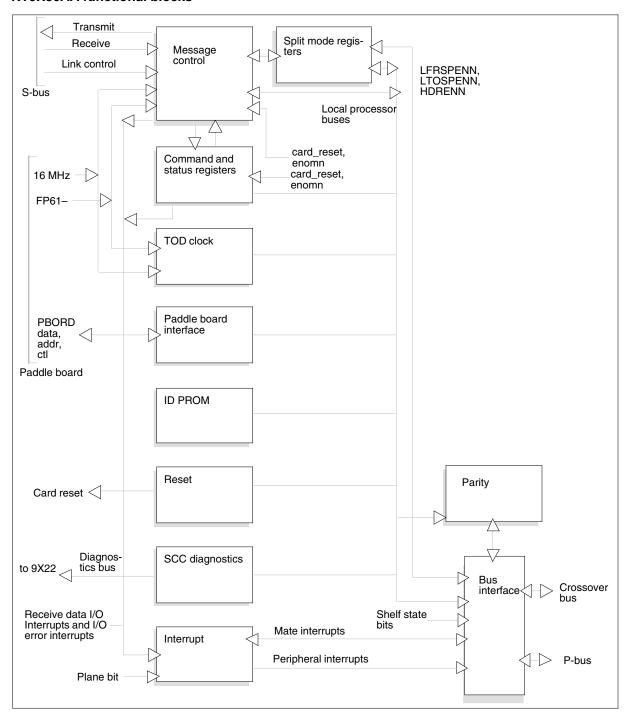

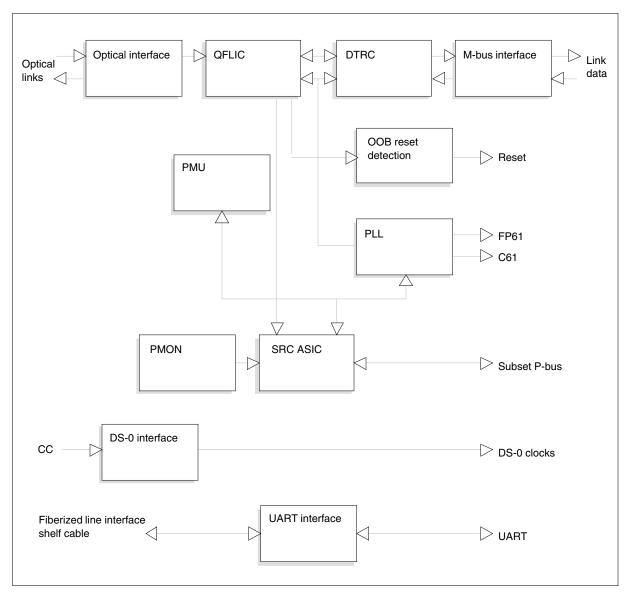

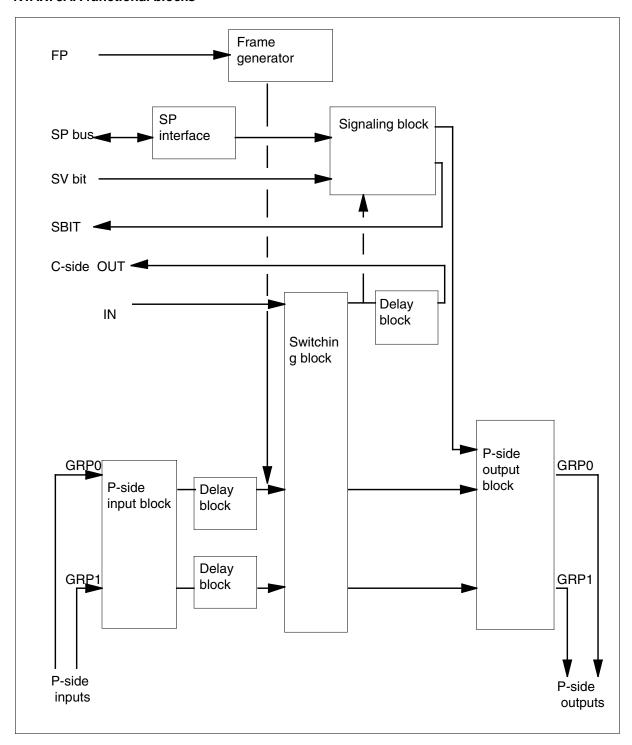

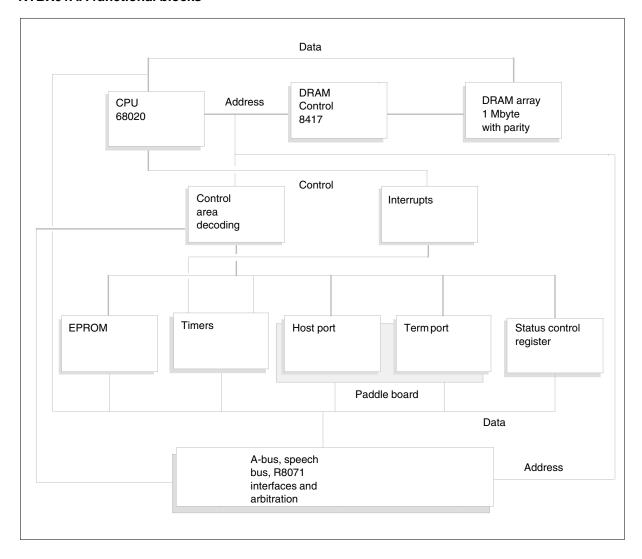

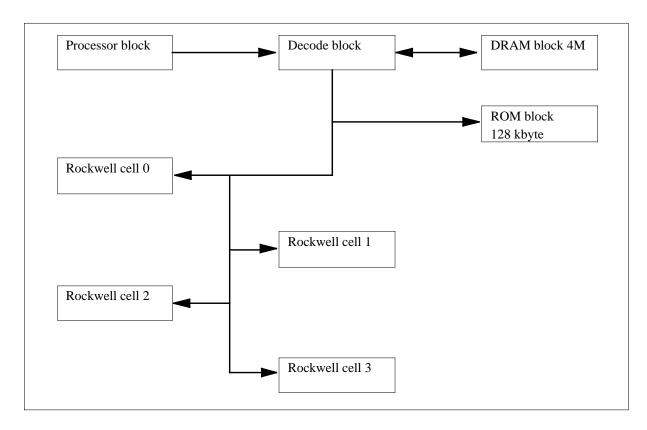

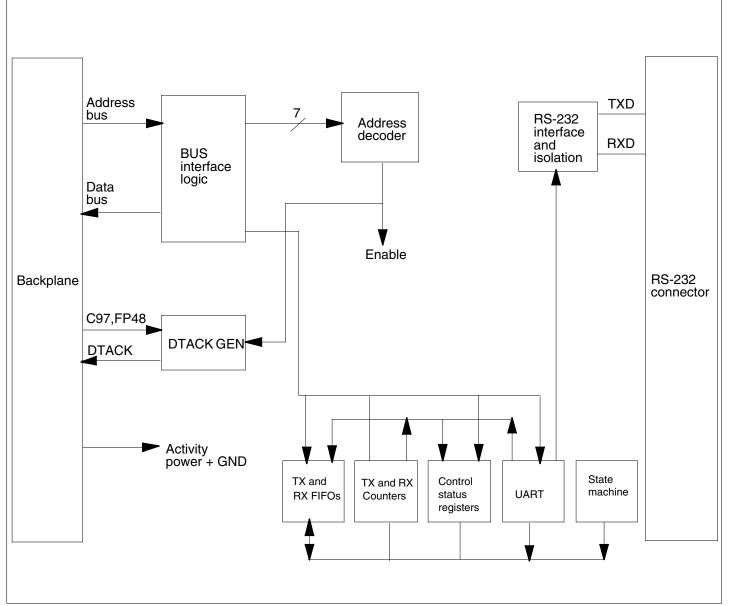

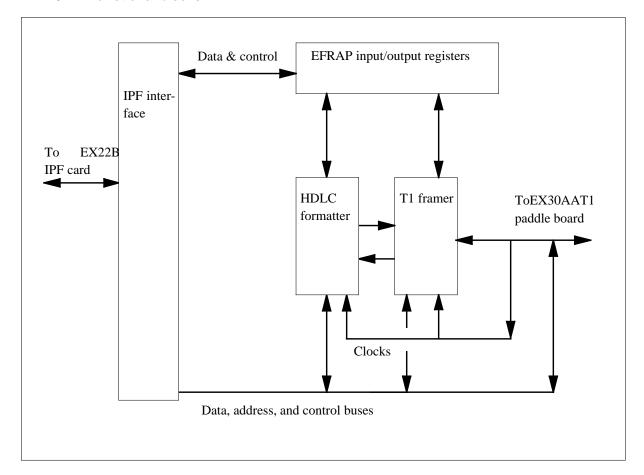

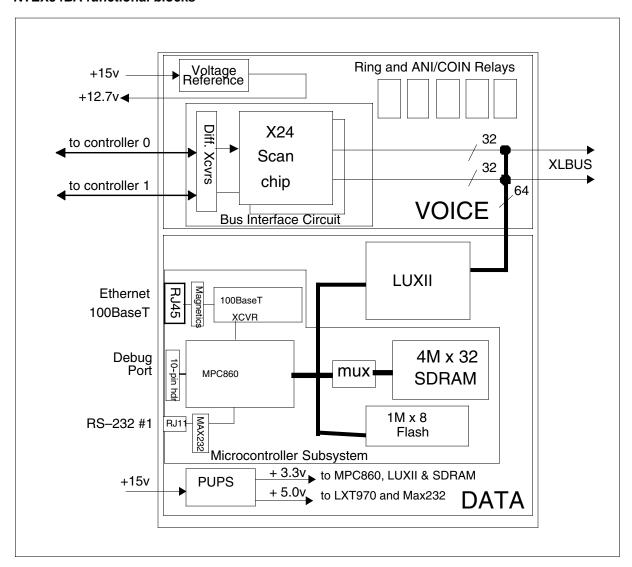

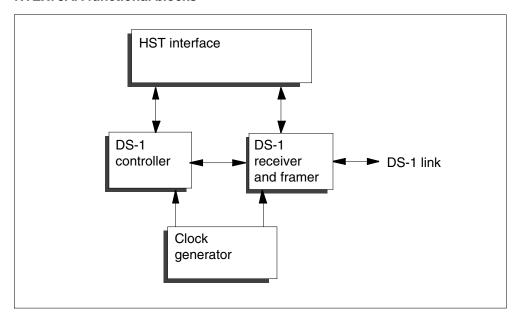

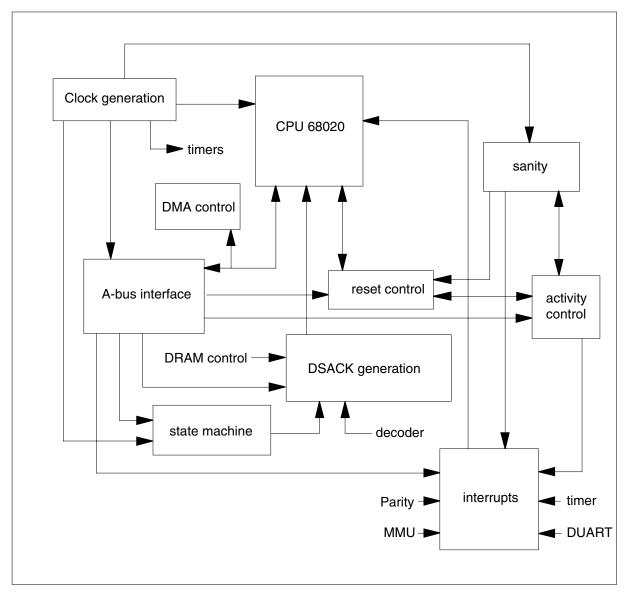

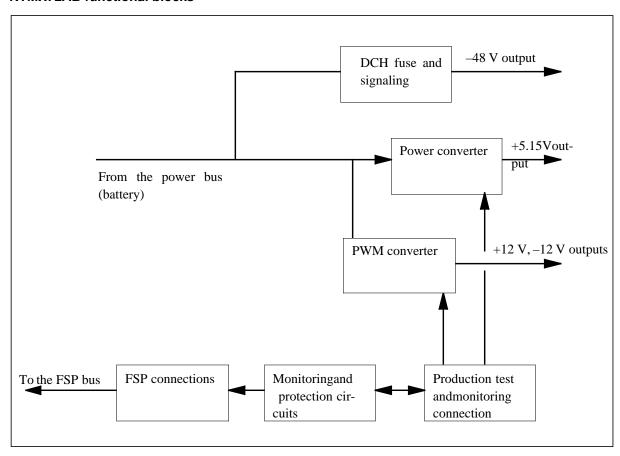

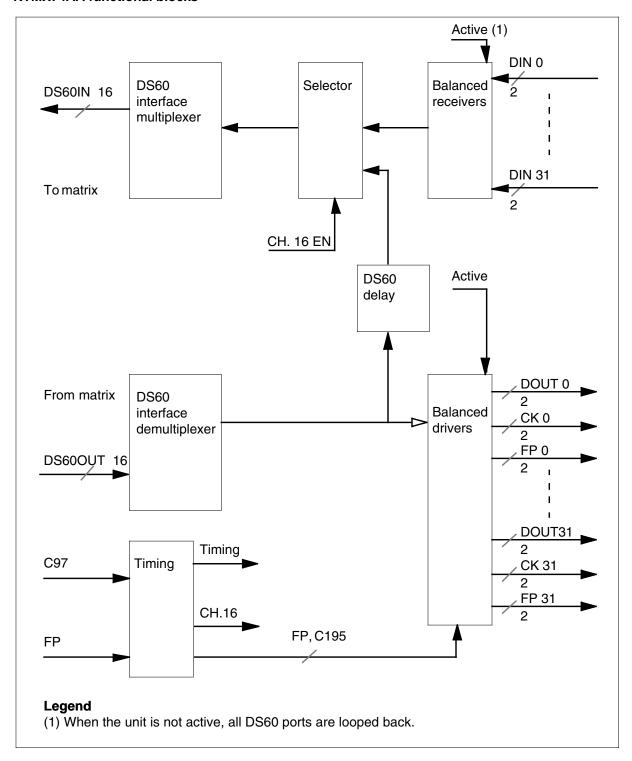

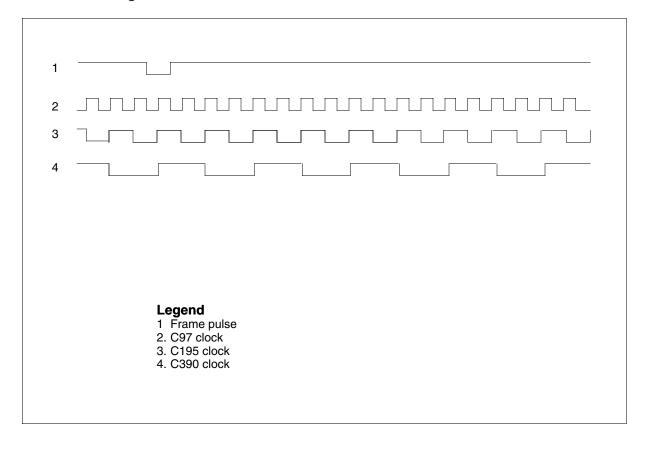

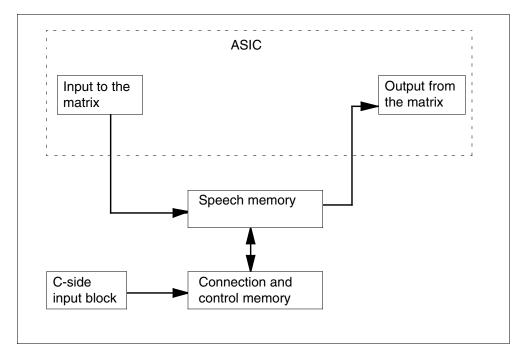

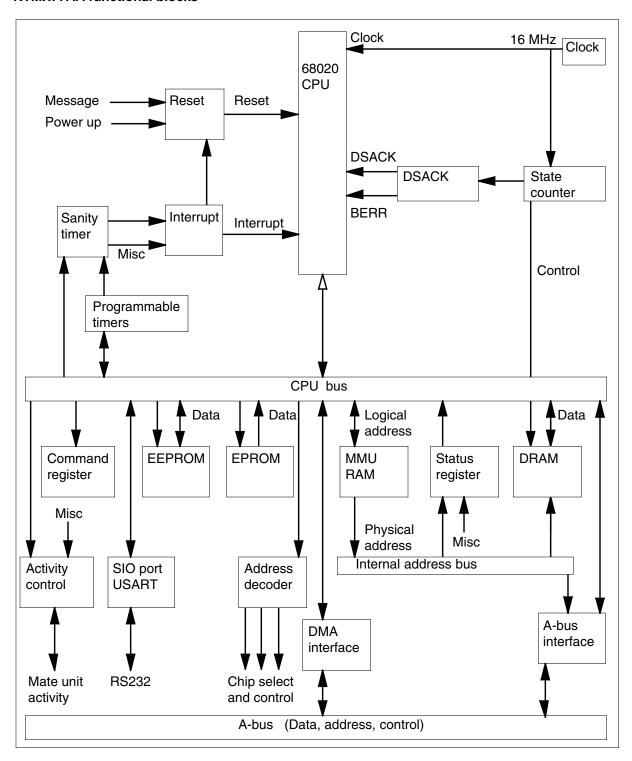

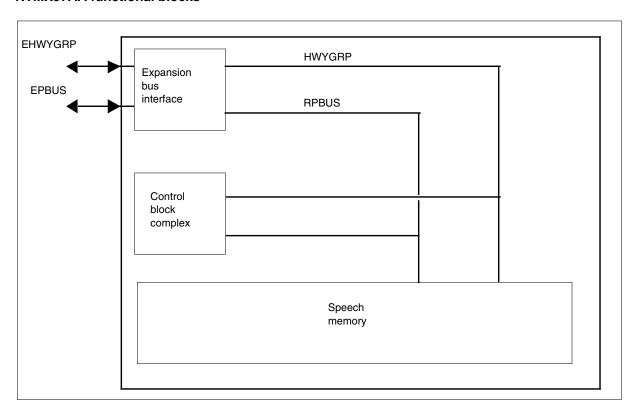

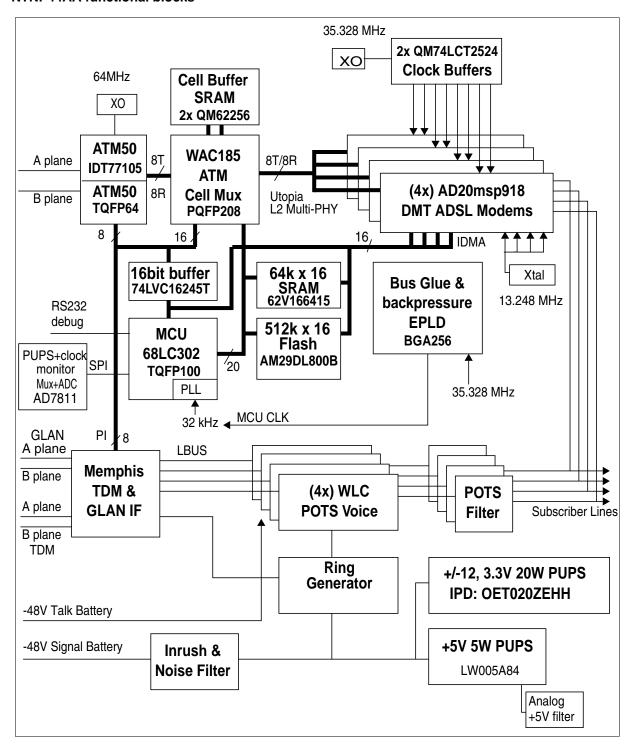

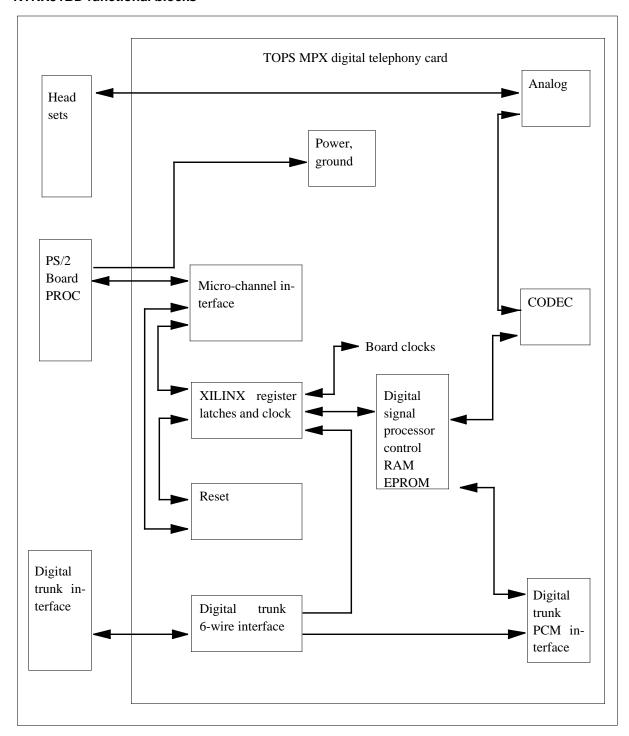

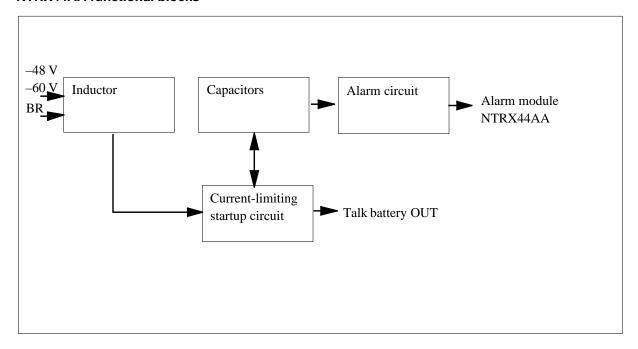

### **Functional blocks**

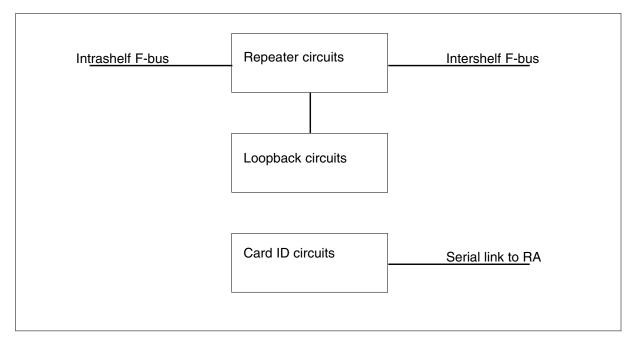

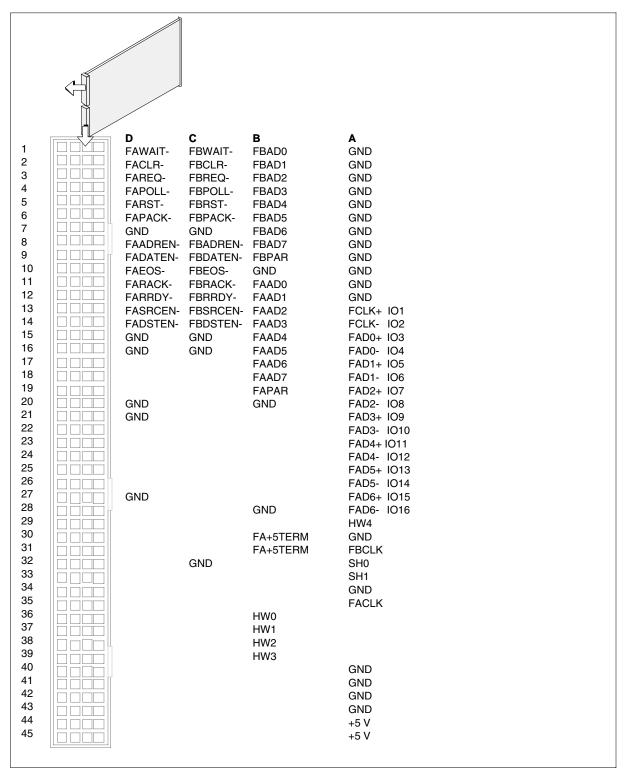

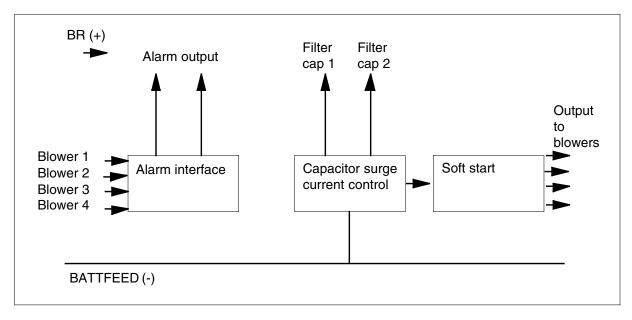

The NT9X74CA has the following functional blocks:

- repeater circuits

- loopback circuits

- card ID circuits

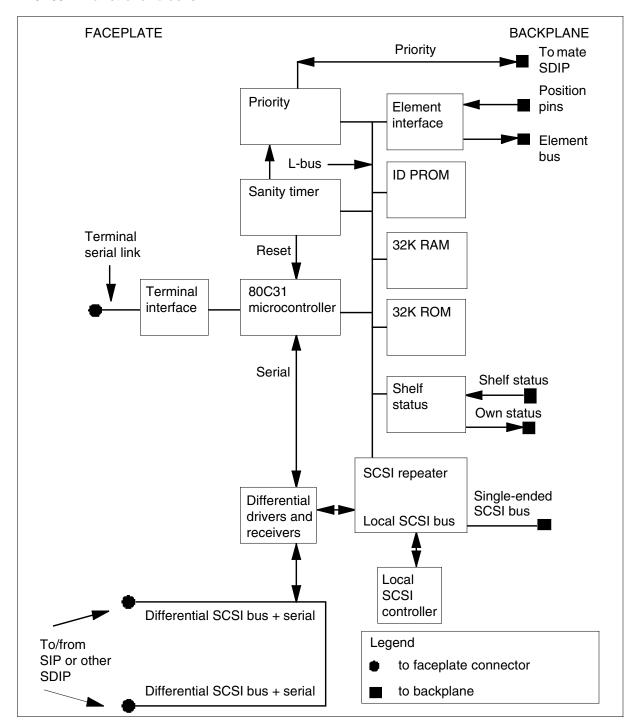

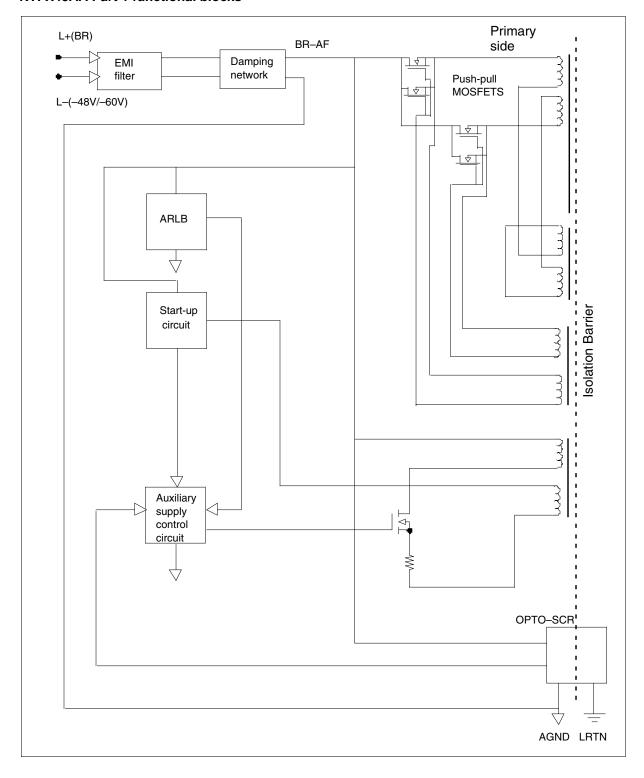

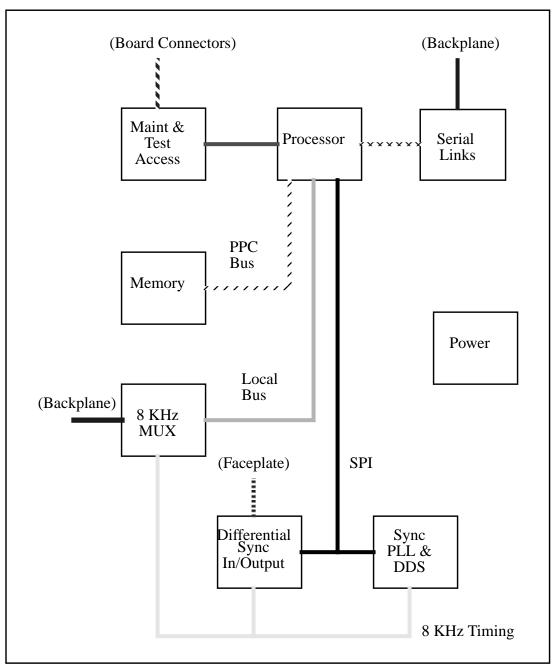

The relationship between the functional blocks appears in the following figure.

#### NT9X74CA functional blocks

### Repeater circuits

The repeater circuits buffers and reclocks signals between the intershelf F–bus and the intrashelf F-bus. The application specific unit (ASU) (FxDSTEN and FxSRCEN) controls two signals that select the direction of the buffers.

### **Loopback circuits**

The loopback circuits receives messages from the RA and transmits them back to the RA. A loopback can occur on the intershelf or the intrashelf side. This capability allows tests of the F-bus that do not rely on the ASUs. Use of the two types of loopback allows the system to isolate intrafaults or interfaults.

### **Card ID circuits**

The card ID circuits reads the card IDs of the following:

- the 9X74 (repeater),

- the 9X79 (F–bus extension paddle board)

- the 9X30 (5–V power converter)

- the EX20 (F-bus to C-bus termination paddle board).

The card ID circuits use a microcontroller to communicate with the RA over a serial link.

### **Signaling**

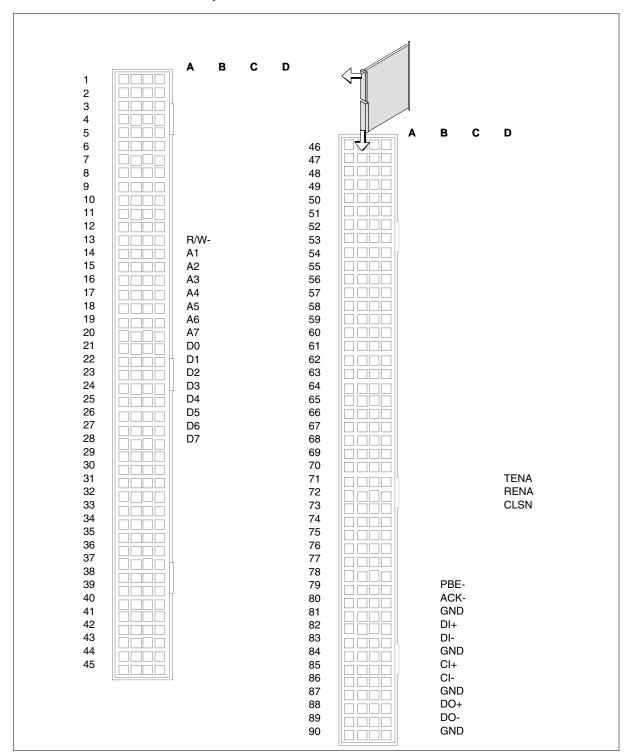

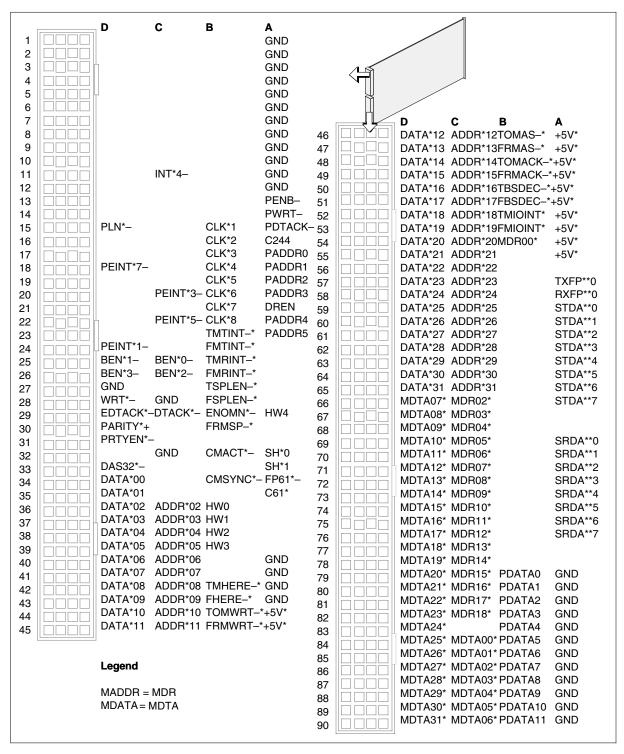

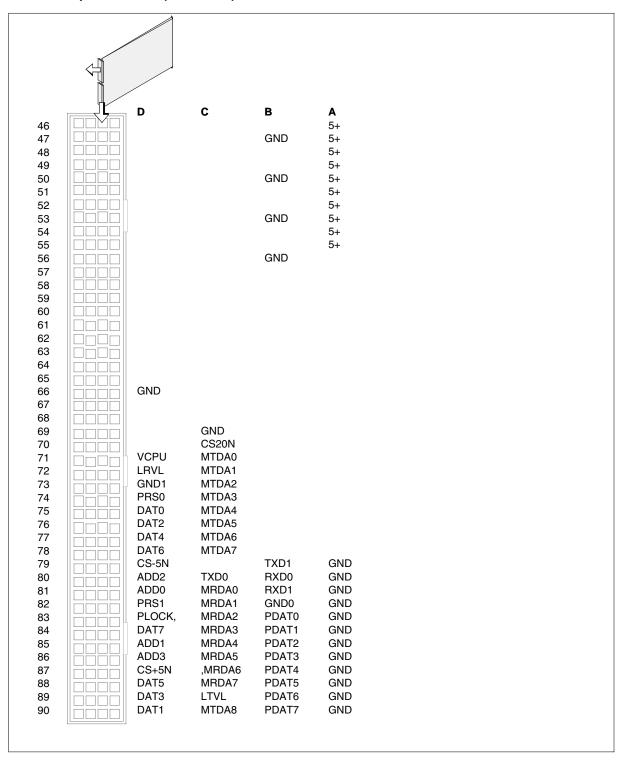

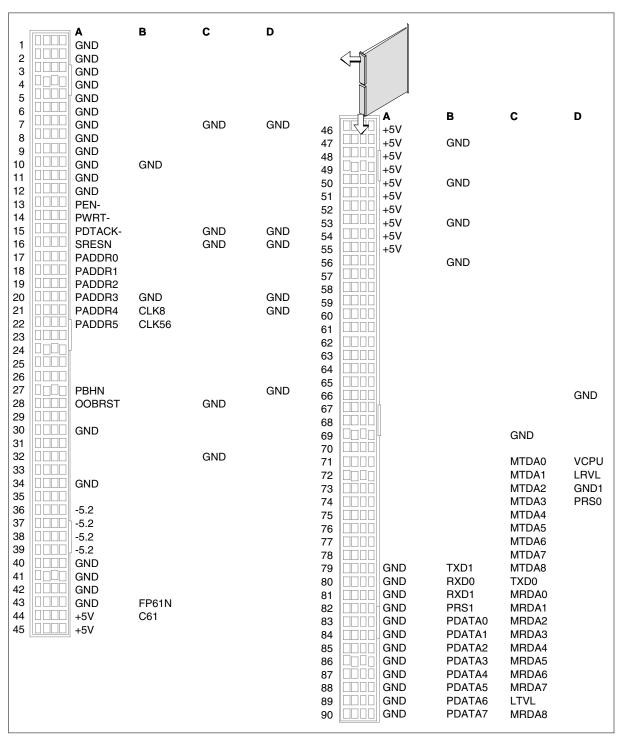

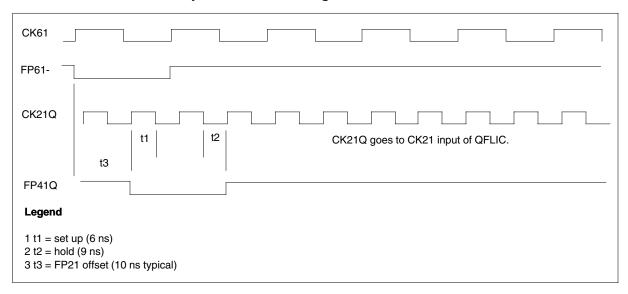

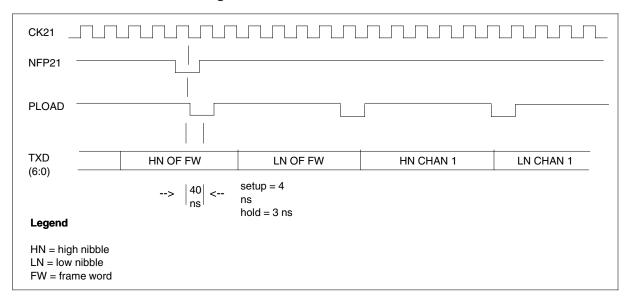

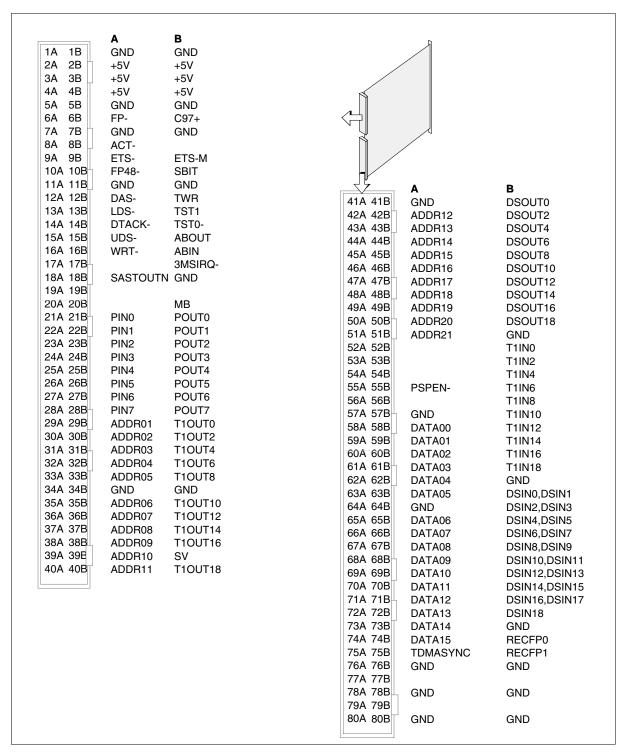

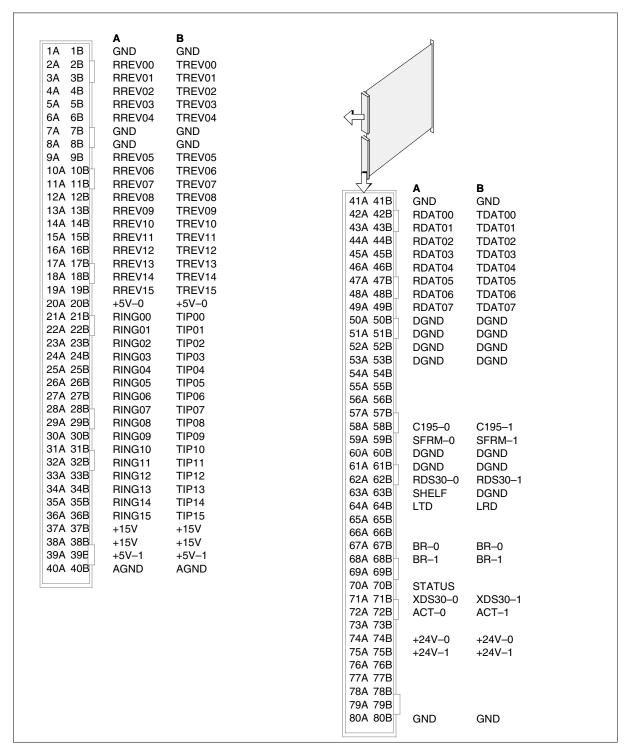

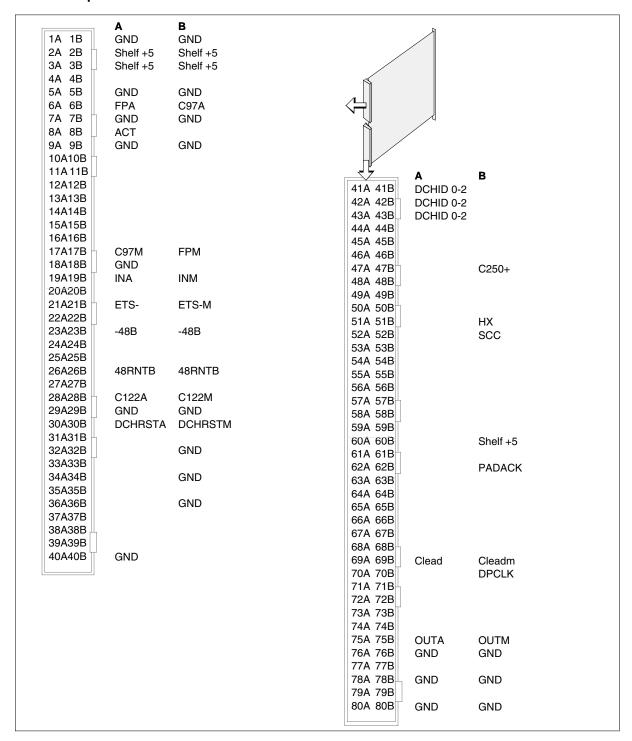

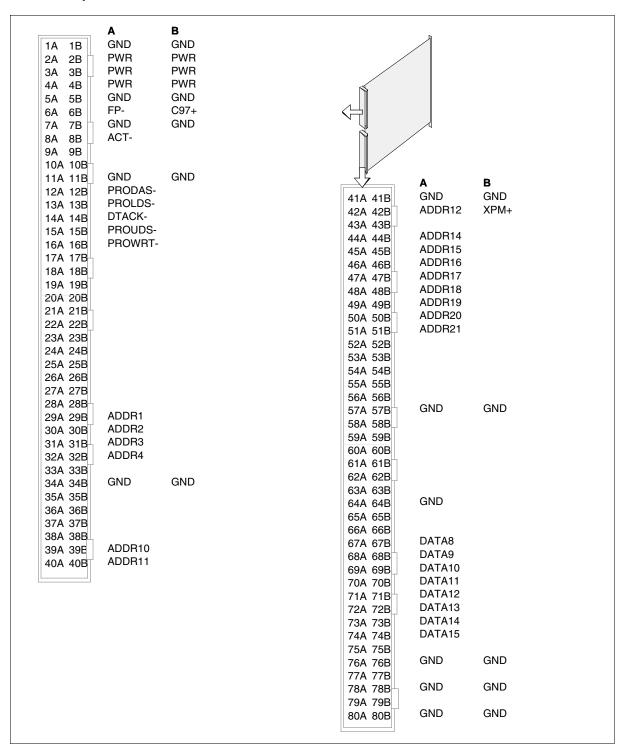

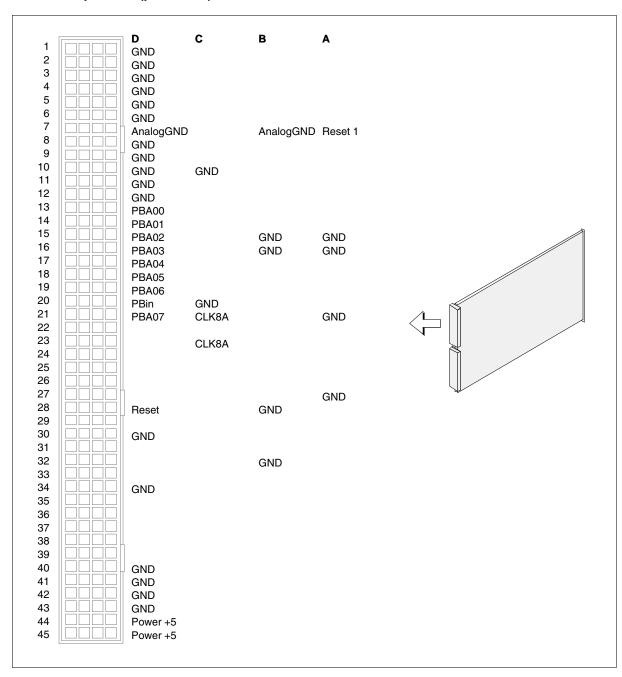

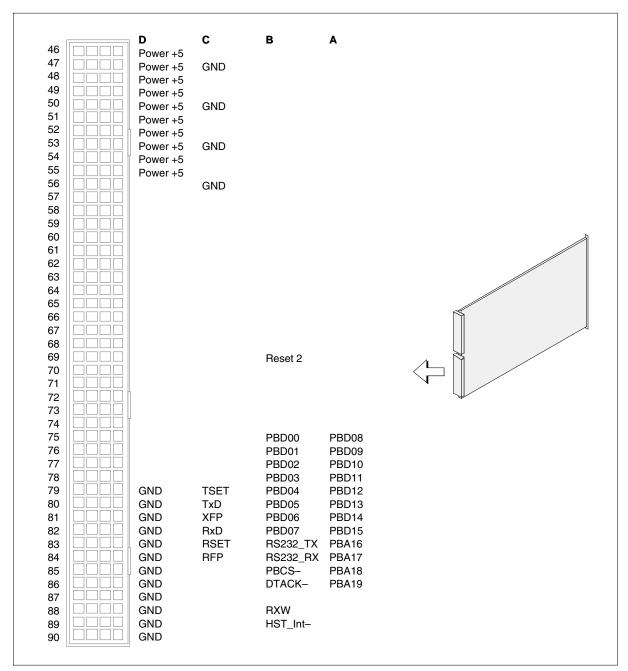

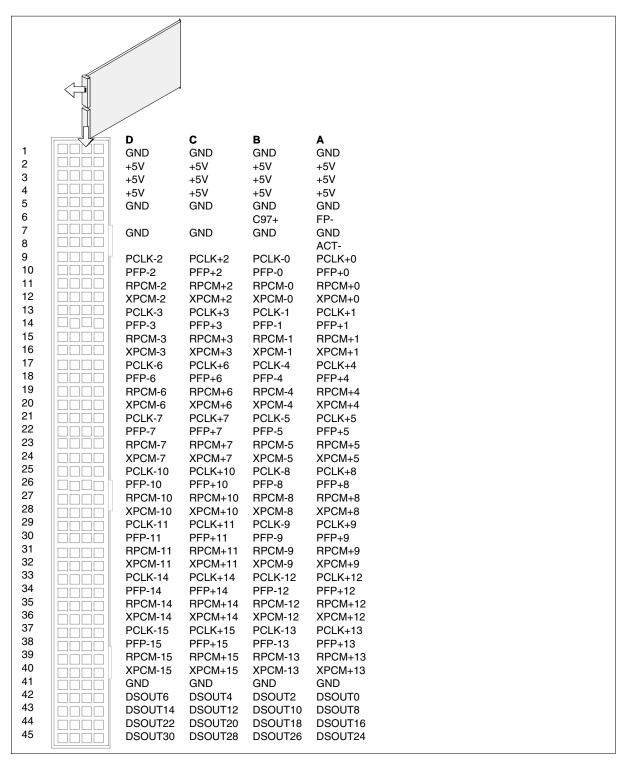

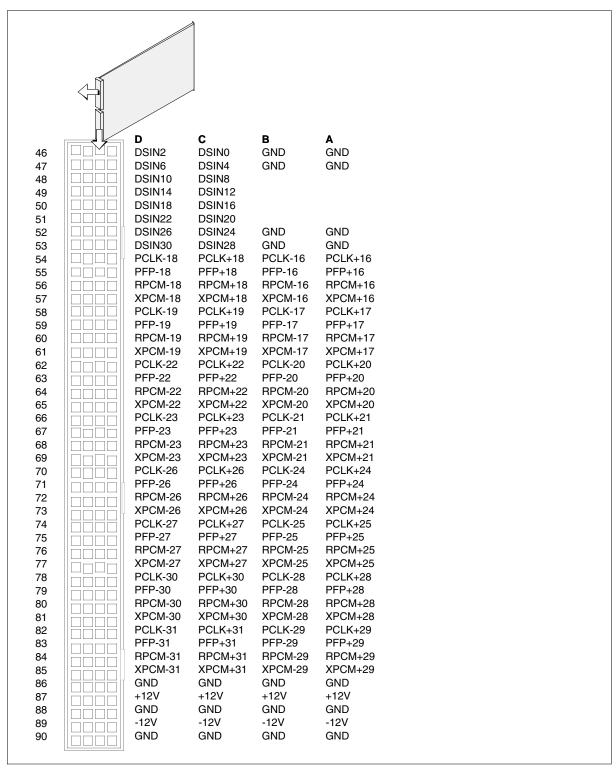

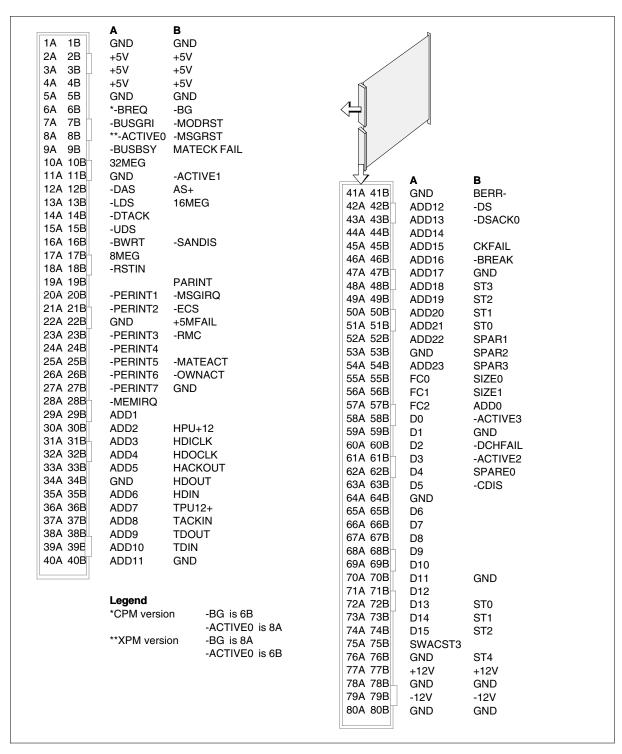

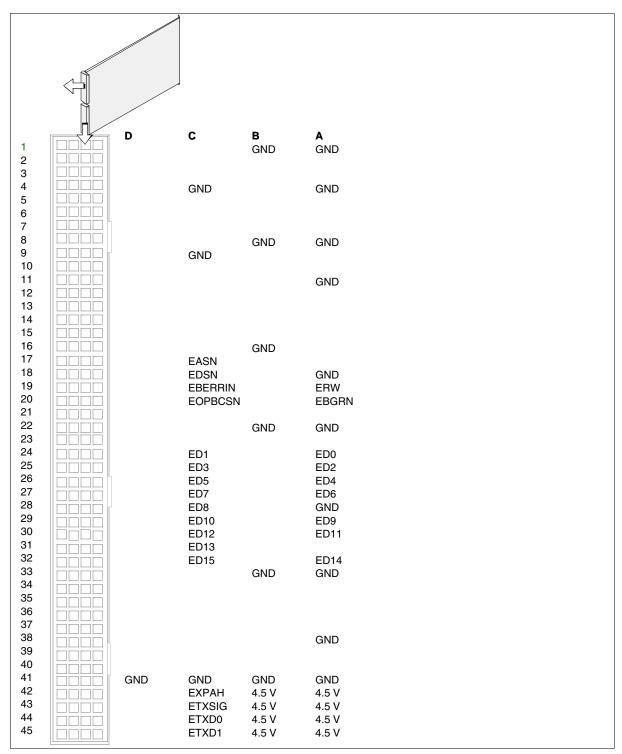

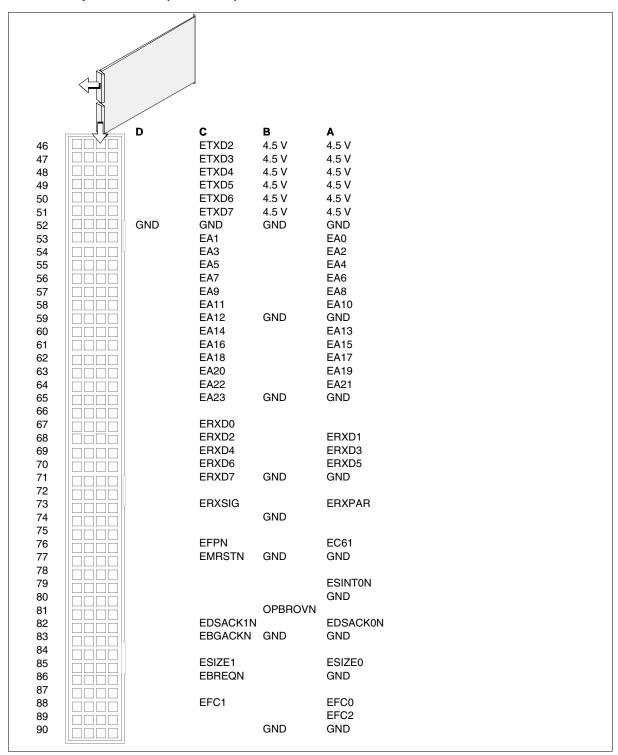

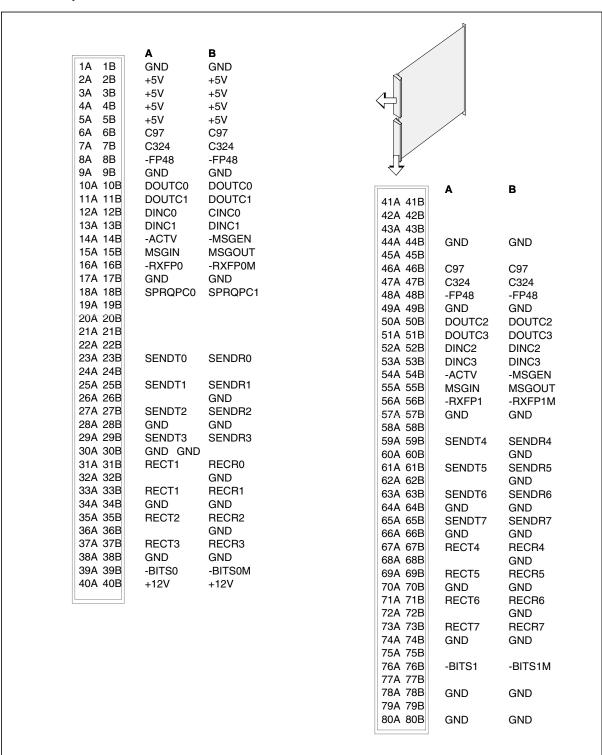

### Pin numbers

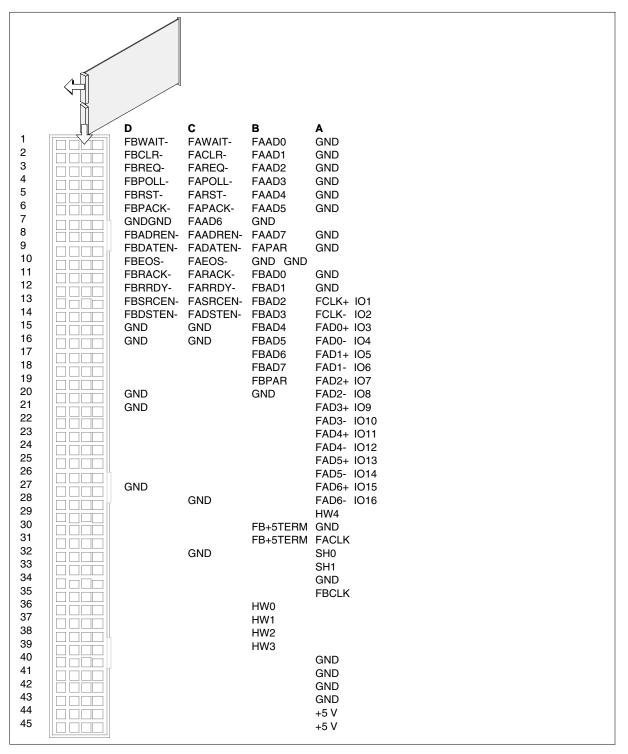

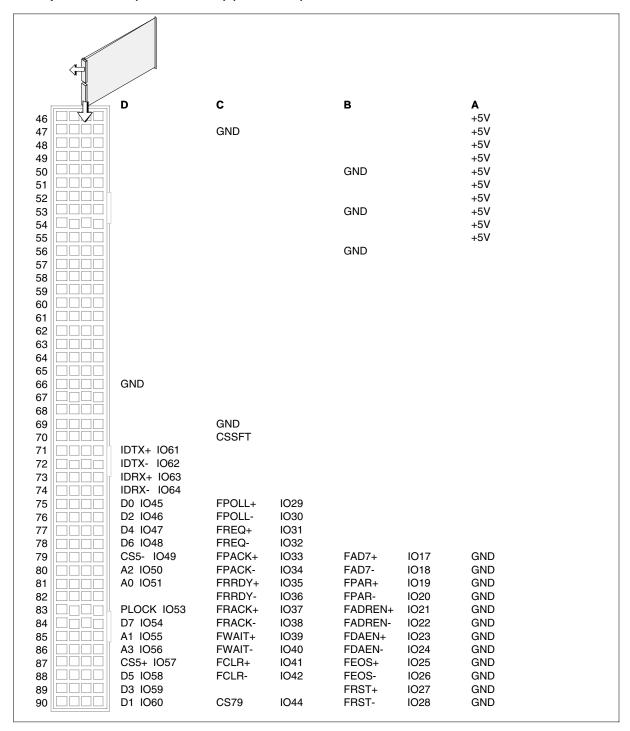

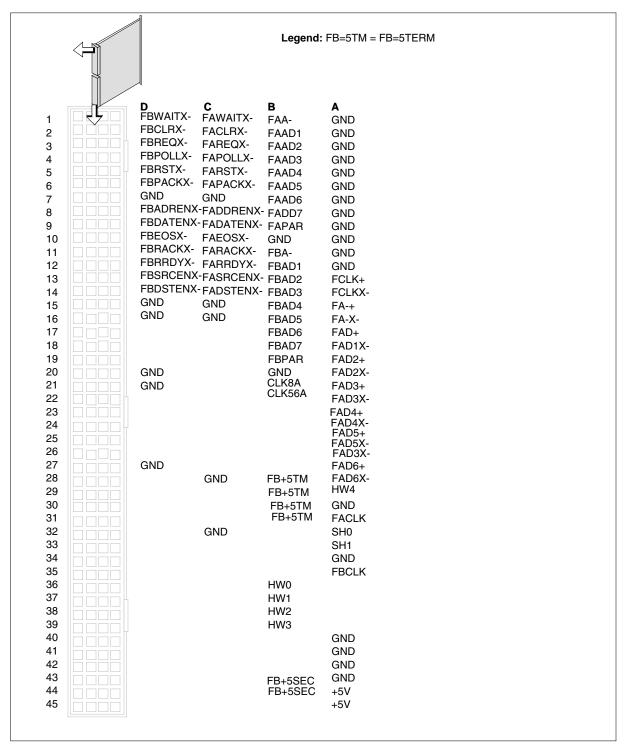

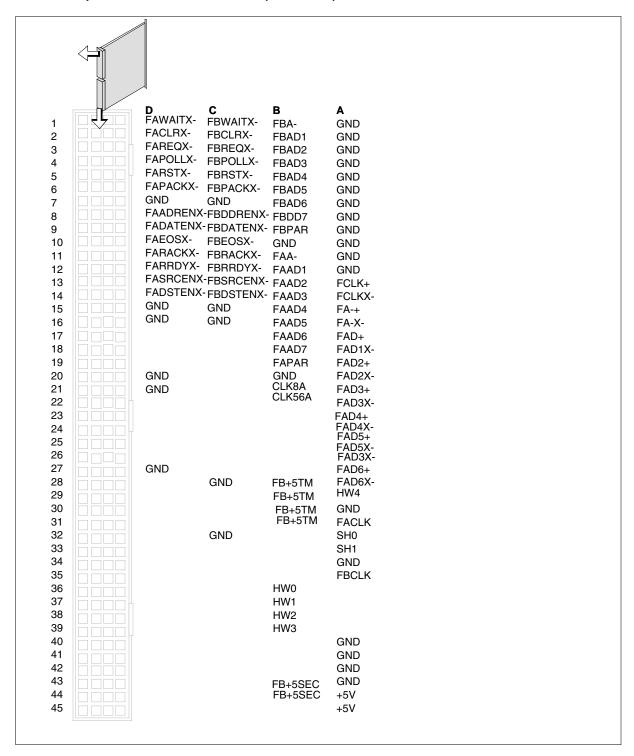

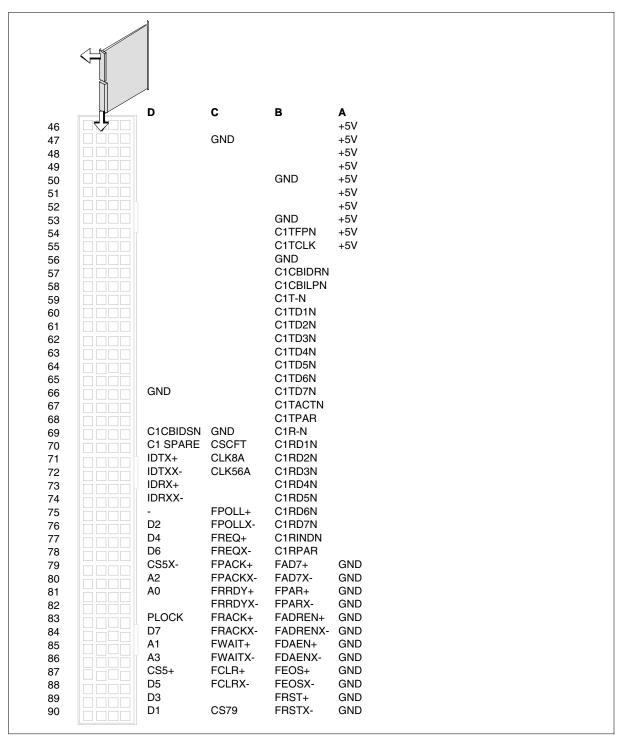

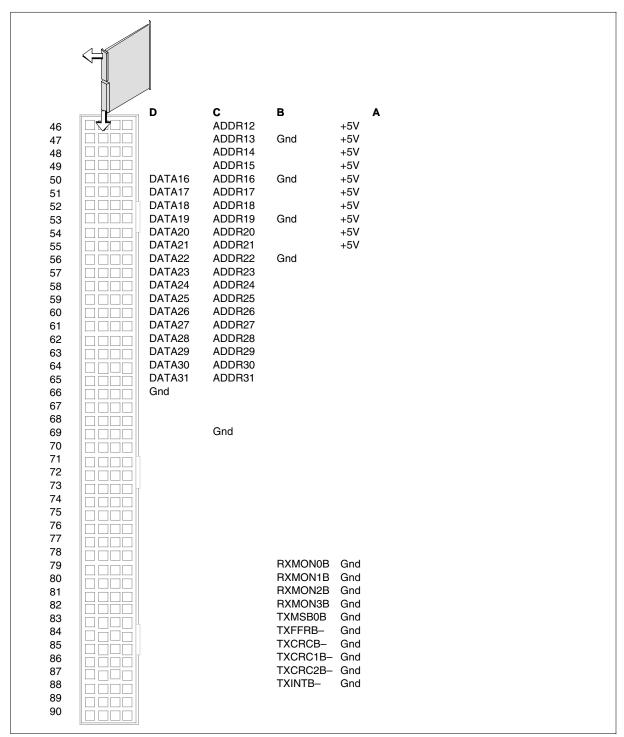

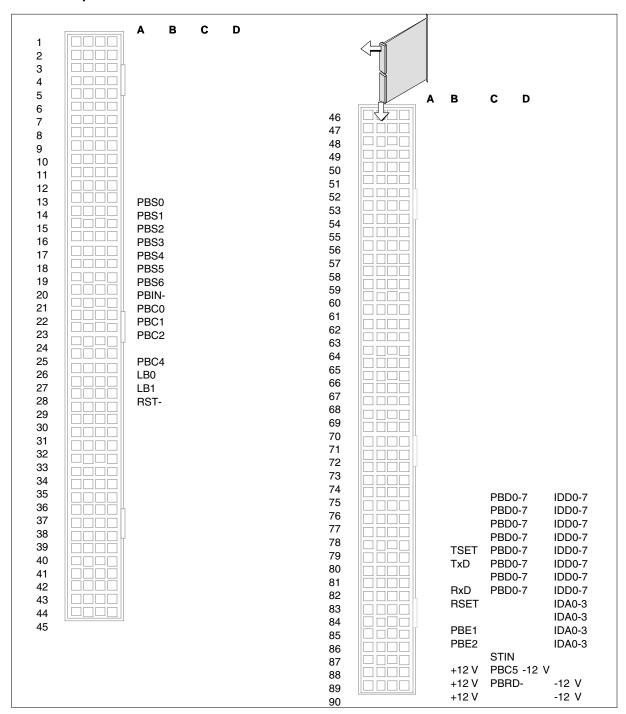

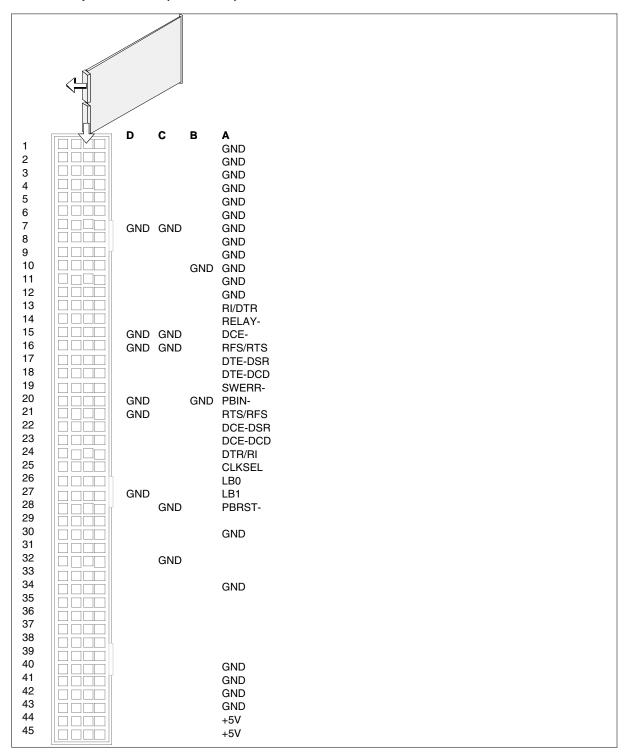

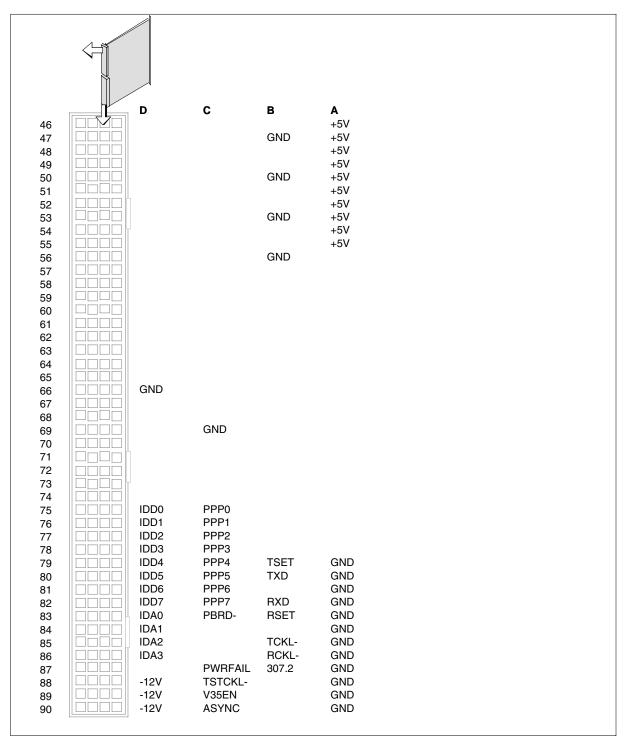

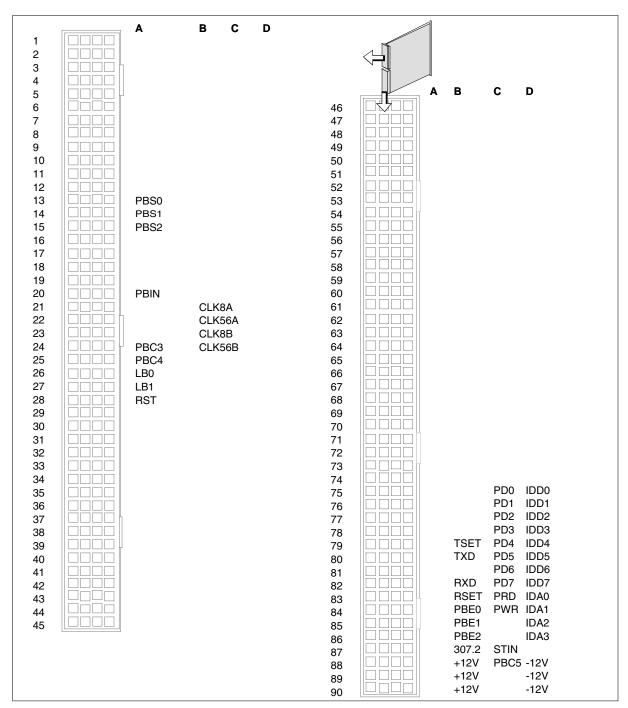

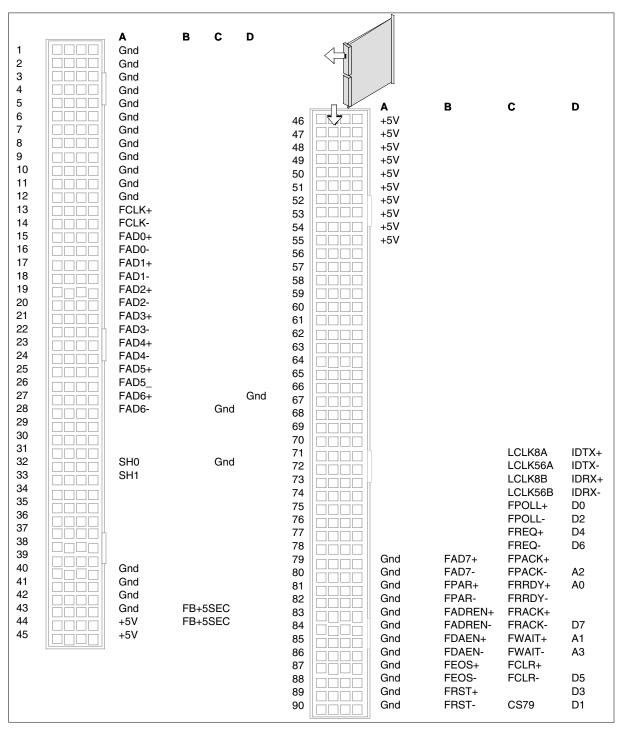

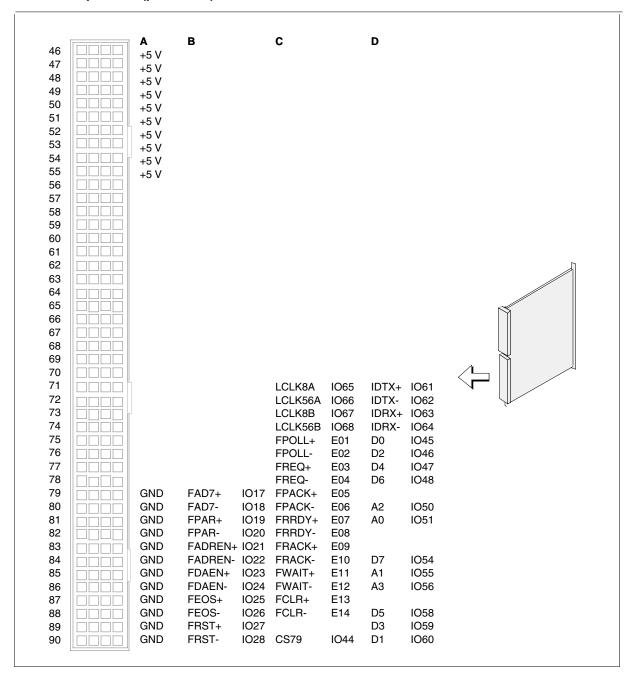

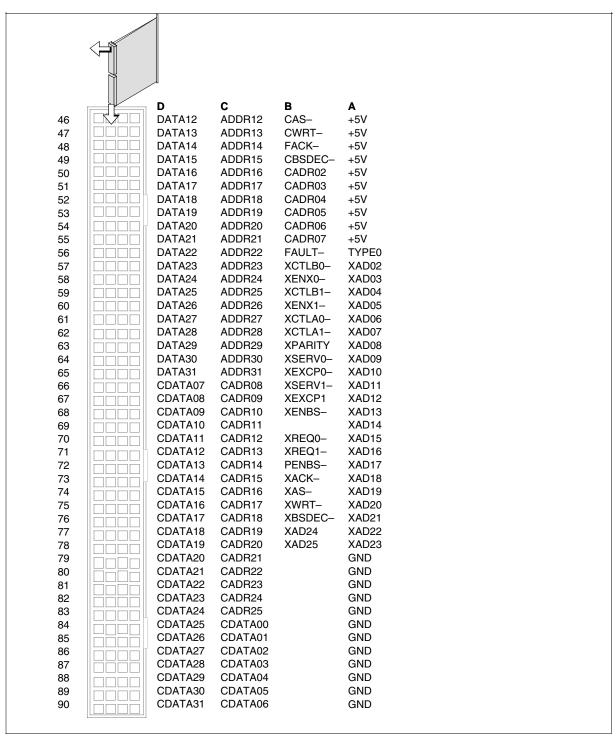

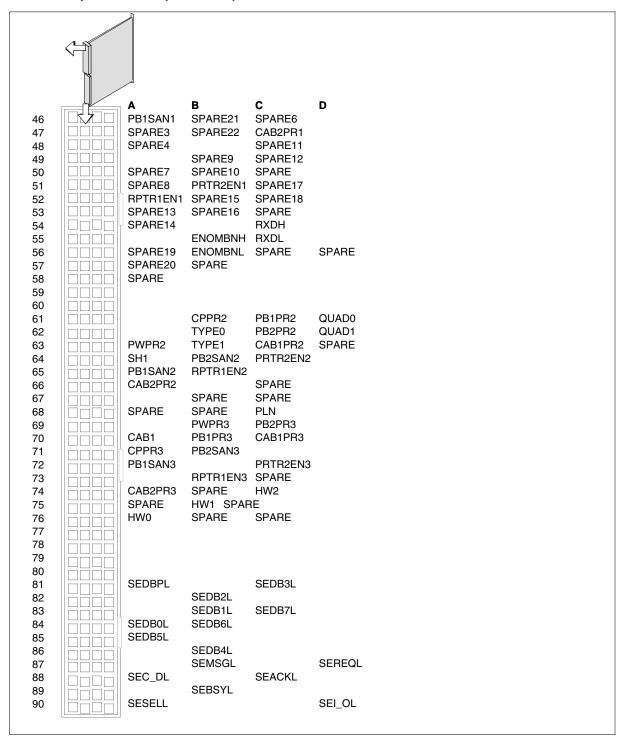

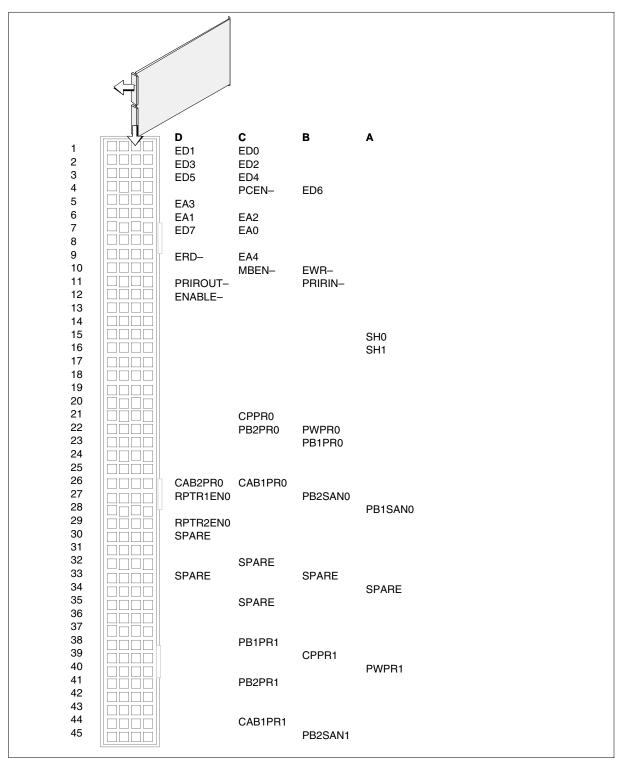

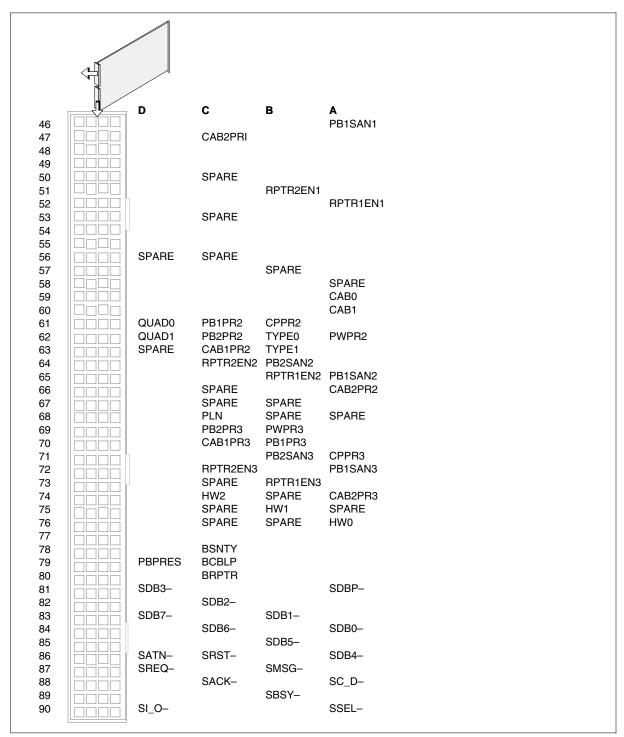

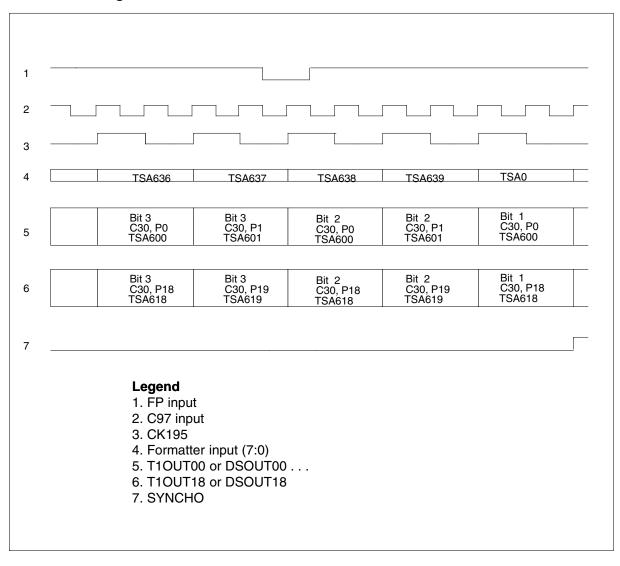

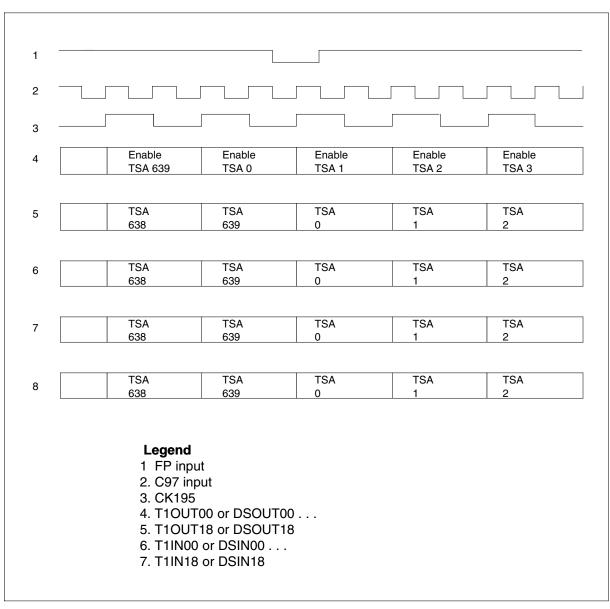

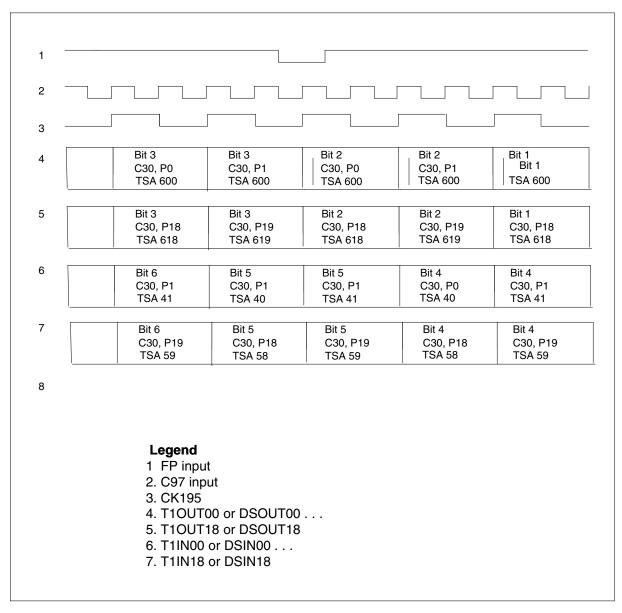

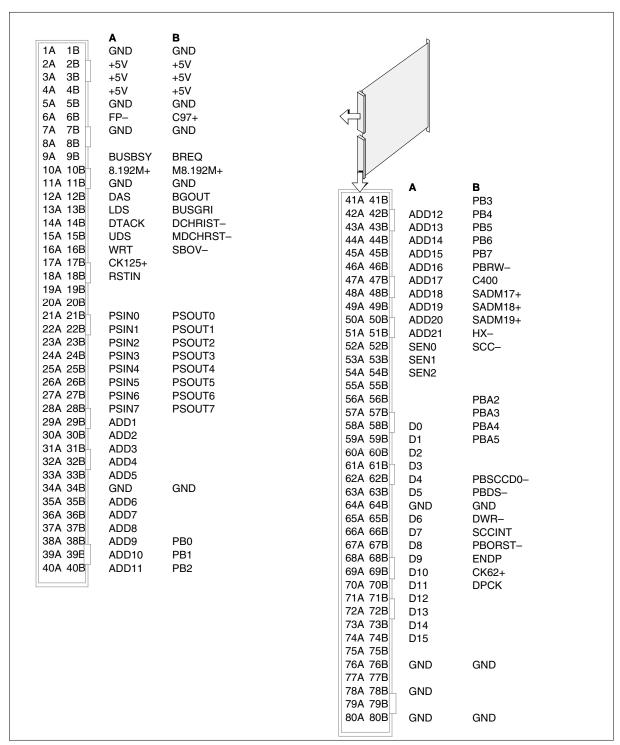

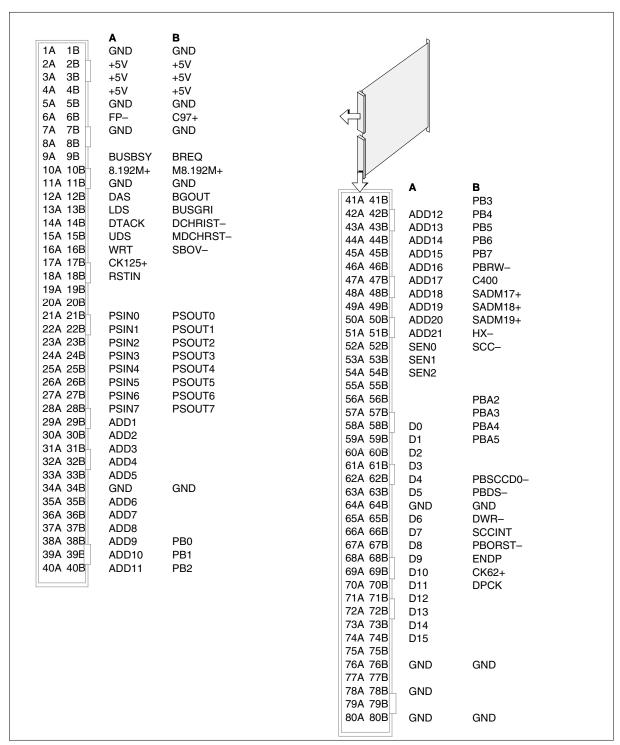

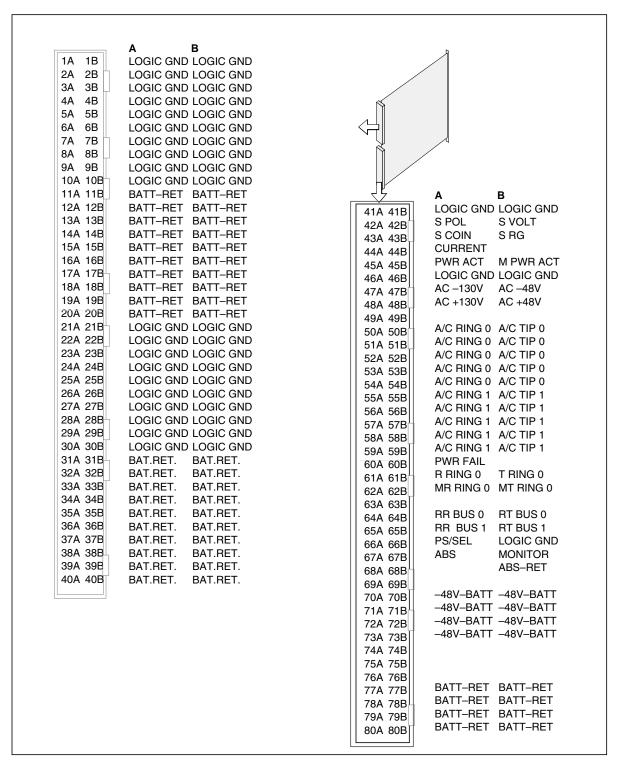

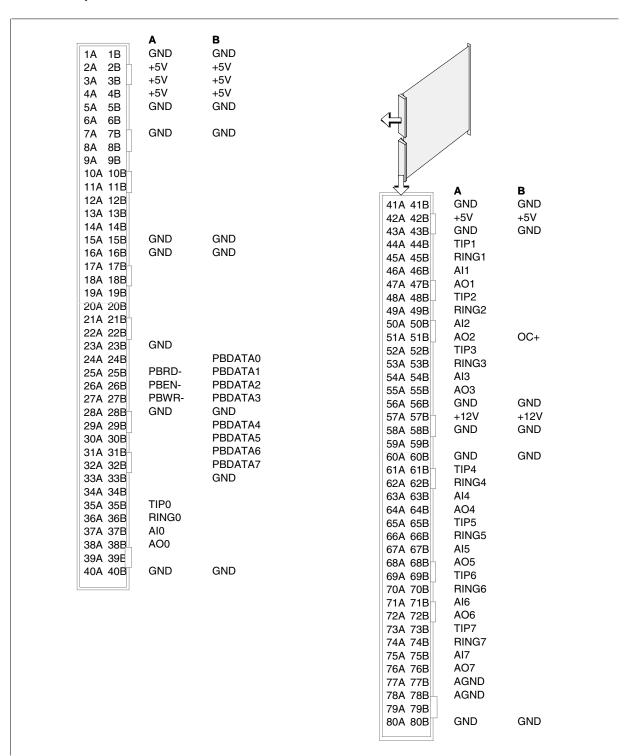

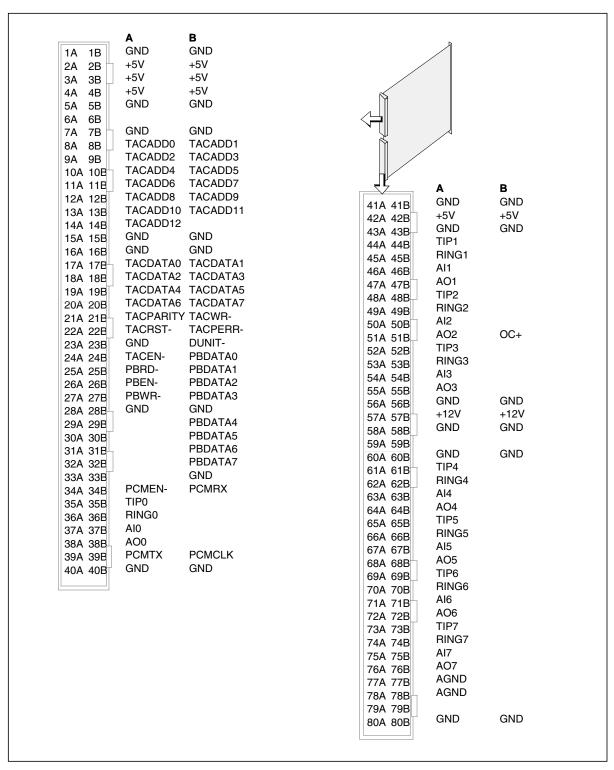

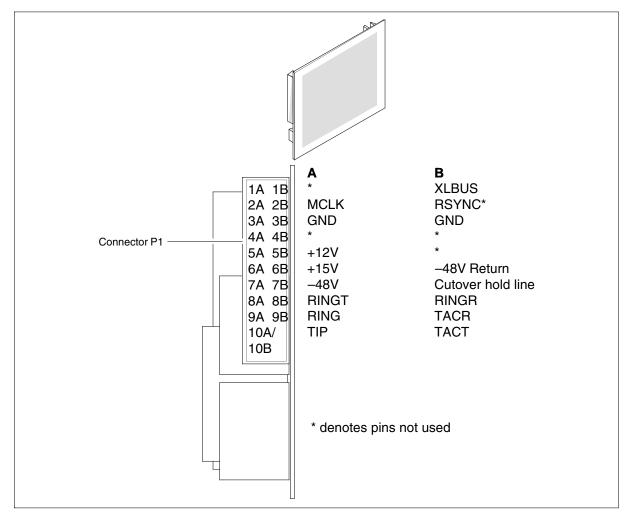

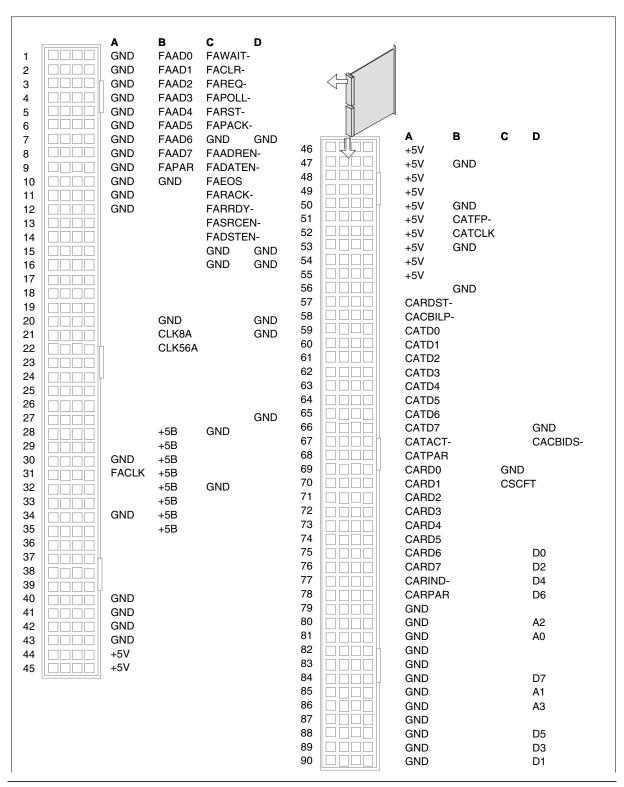

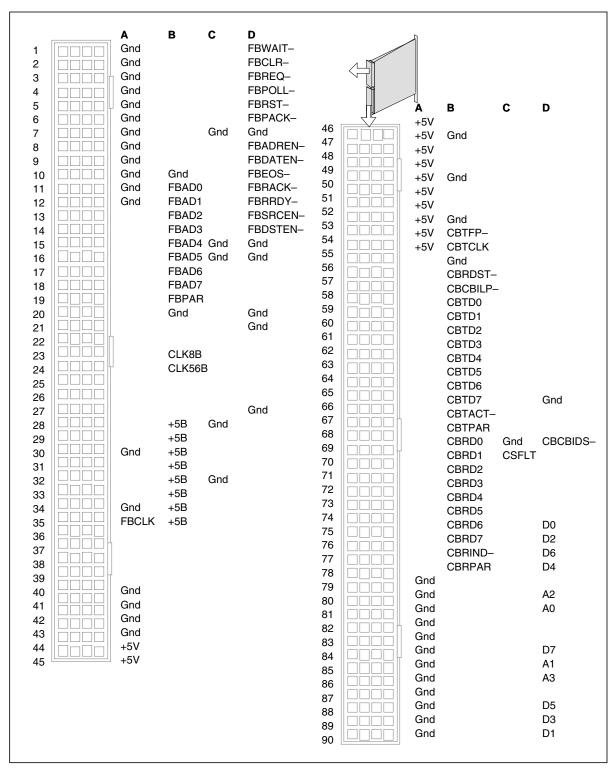

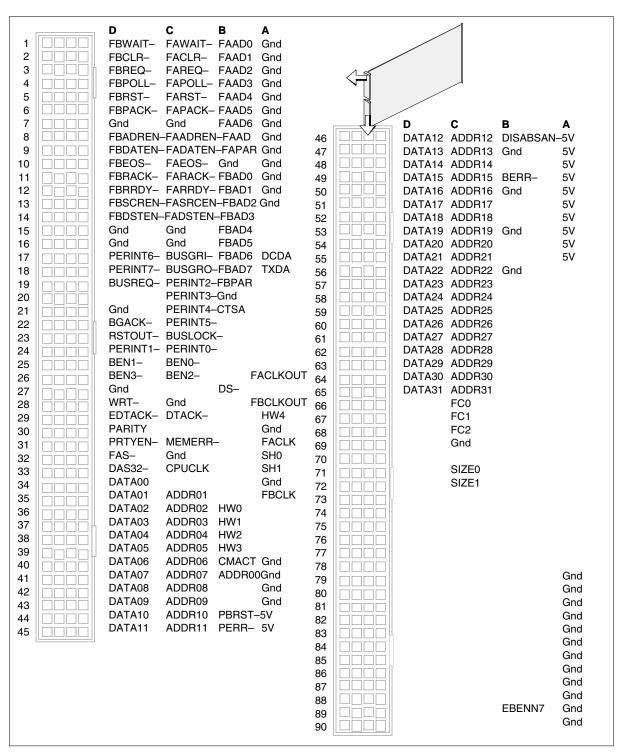

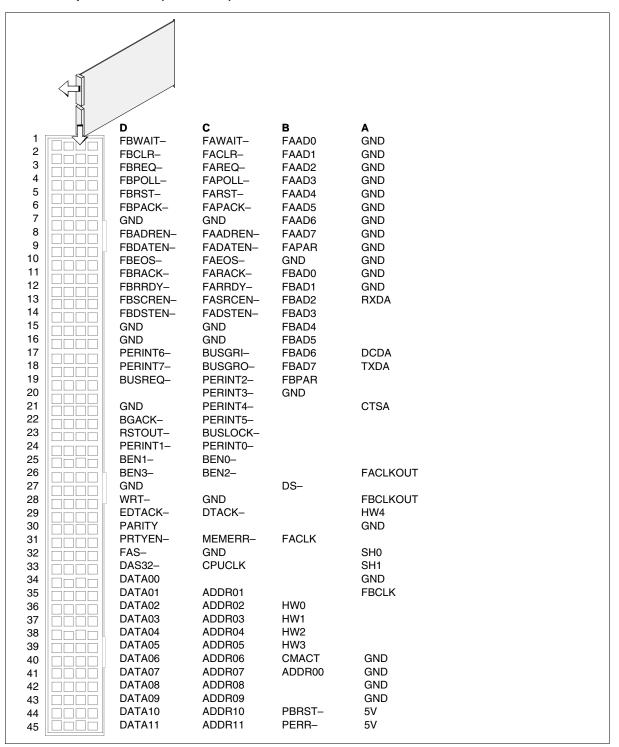

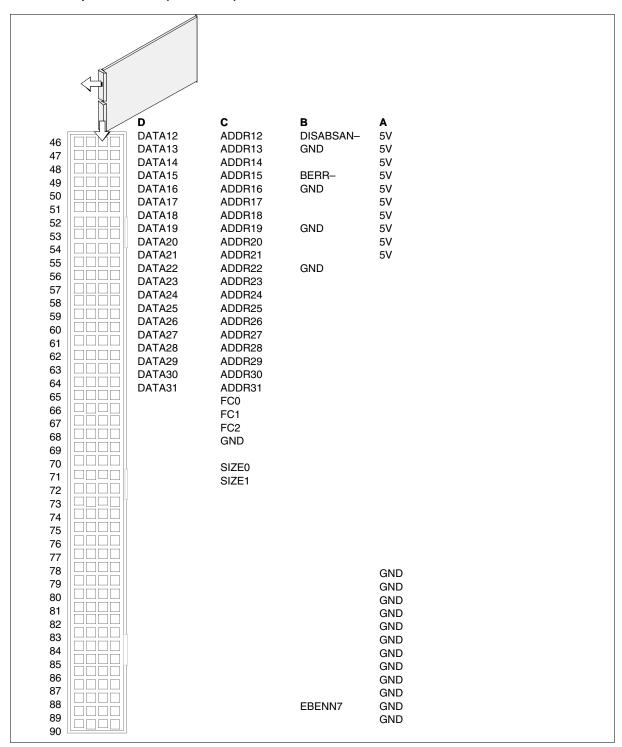

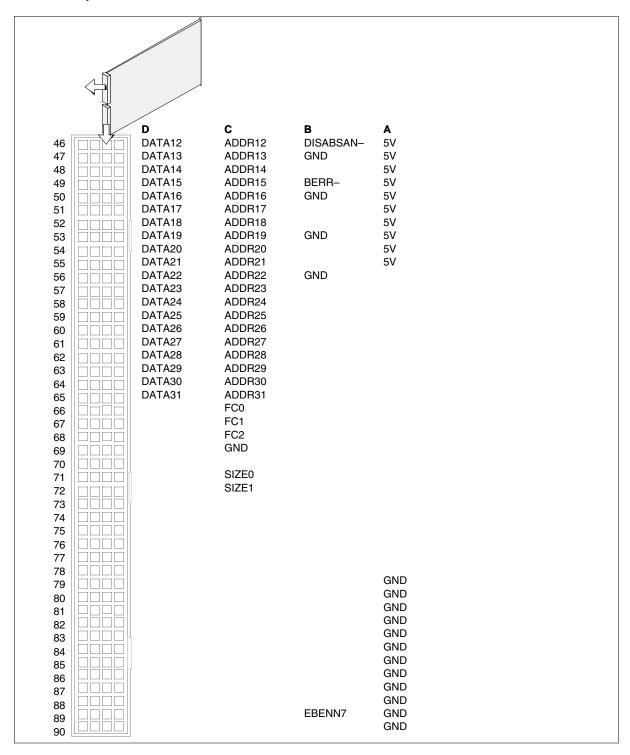

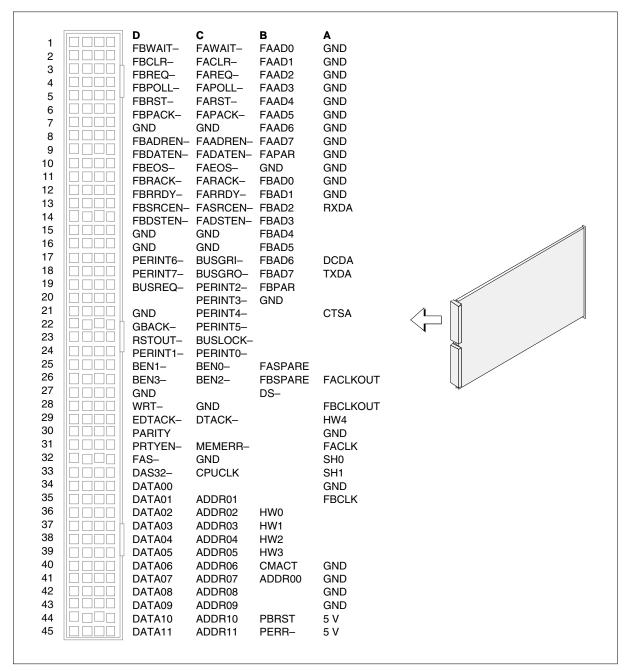

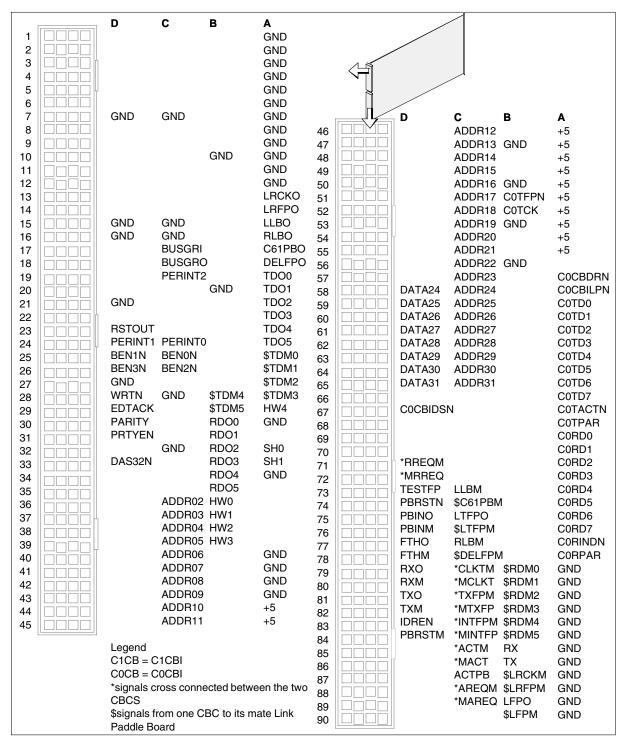

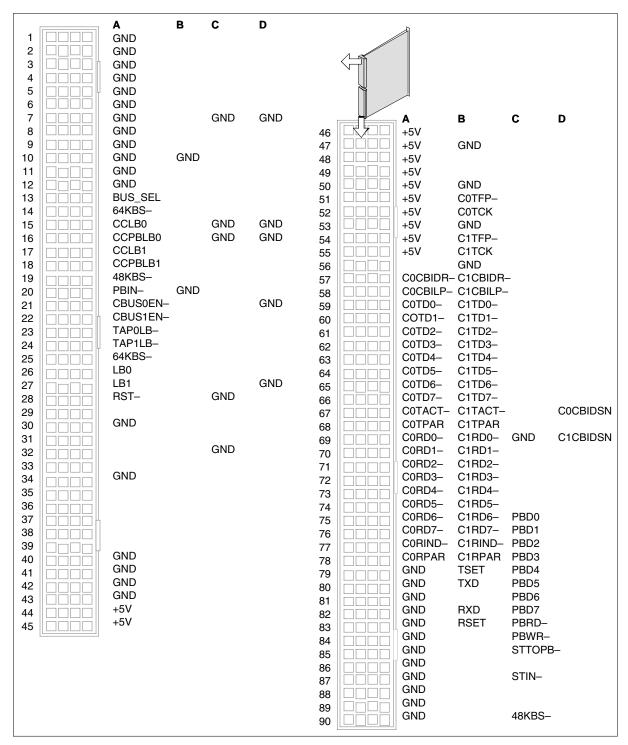

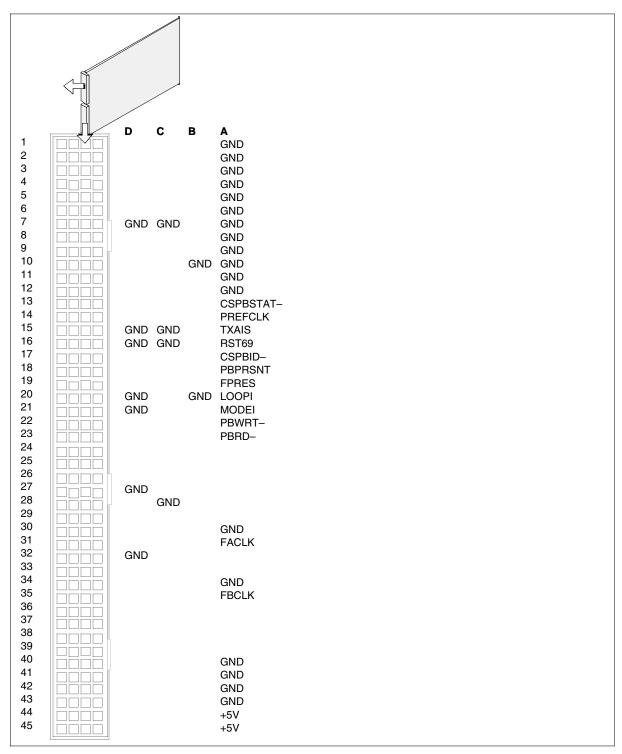

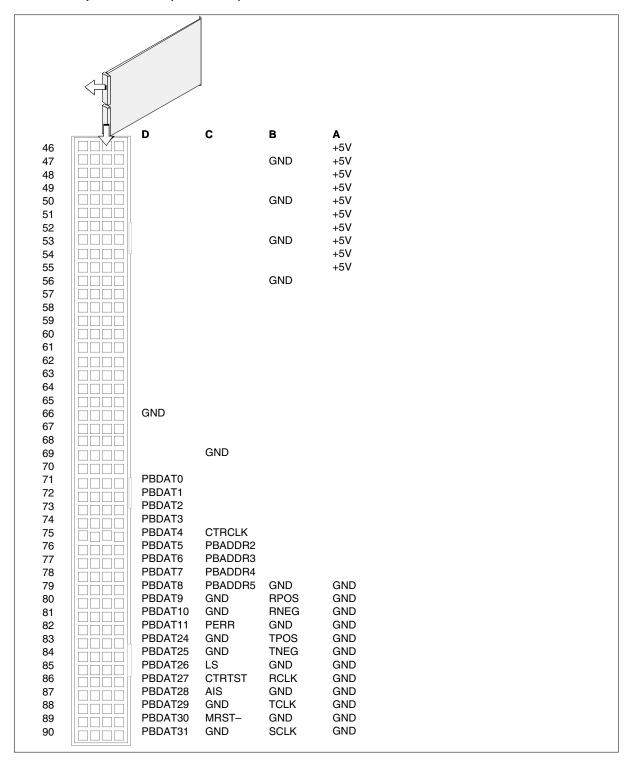

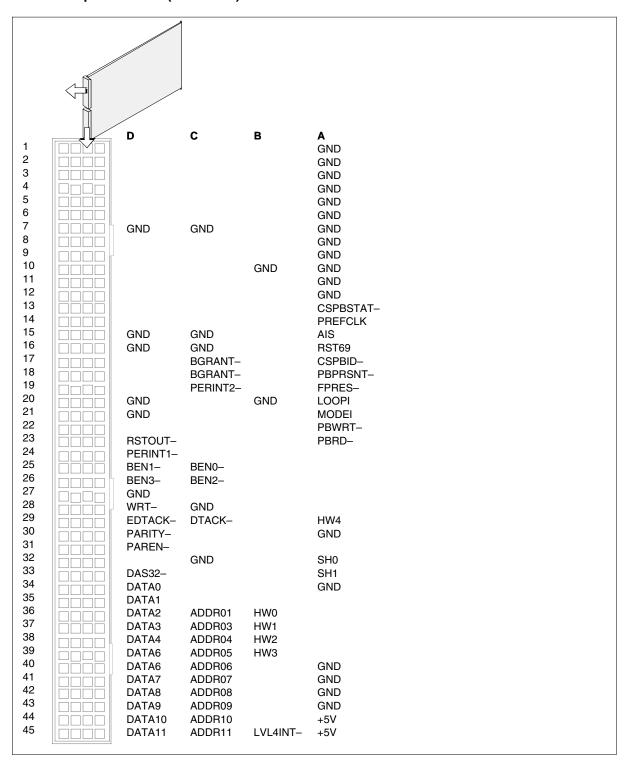

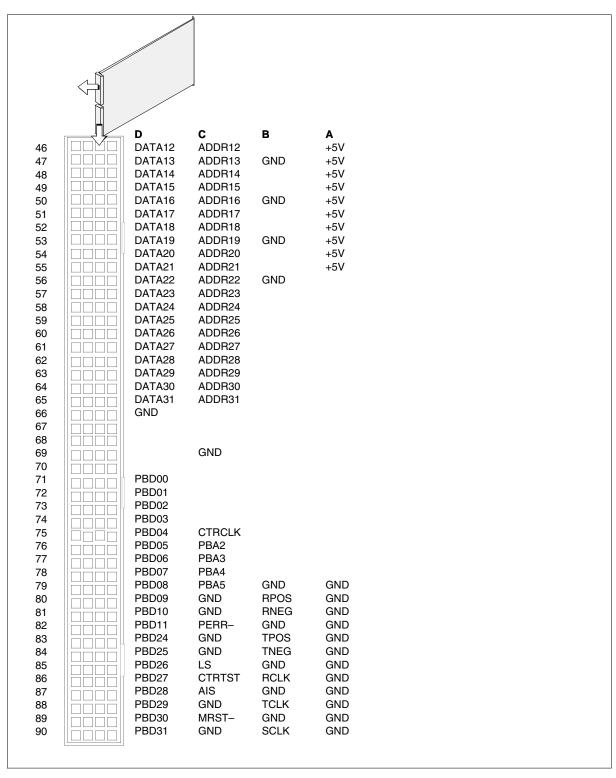

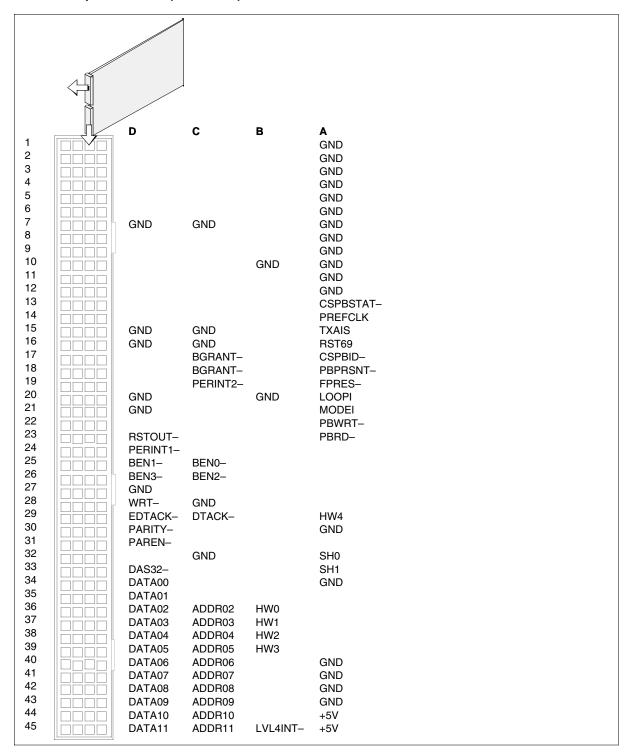

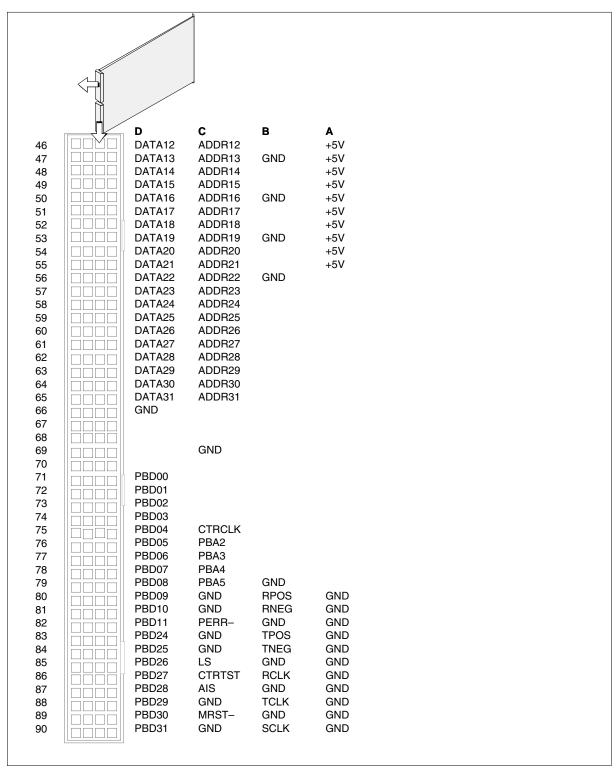

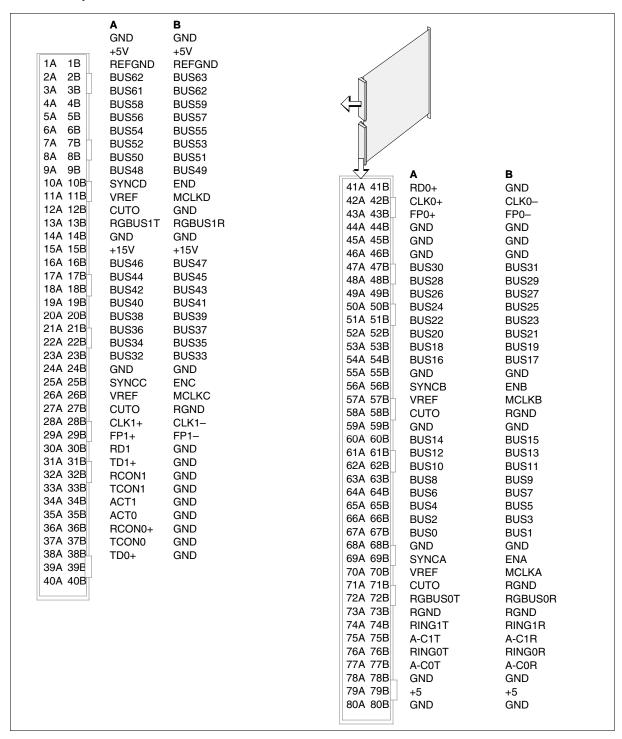

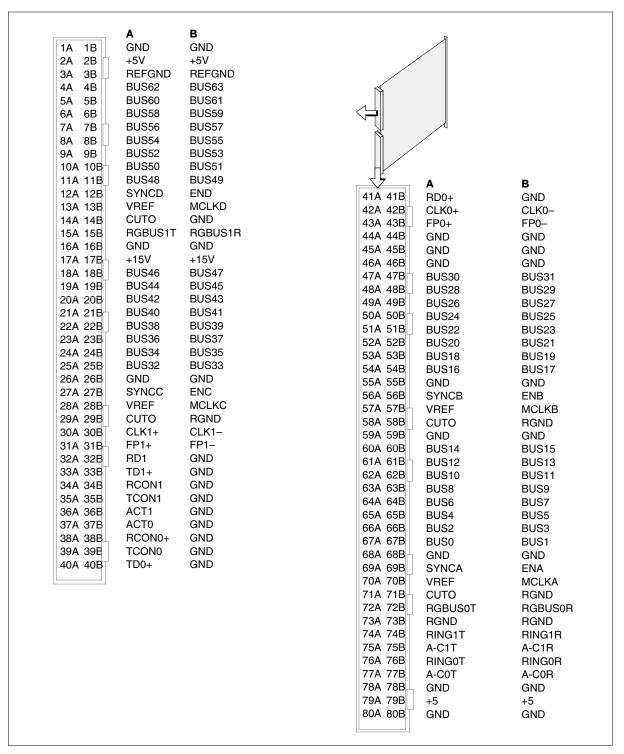

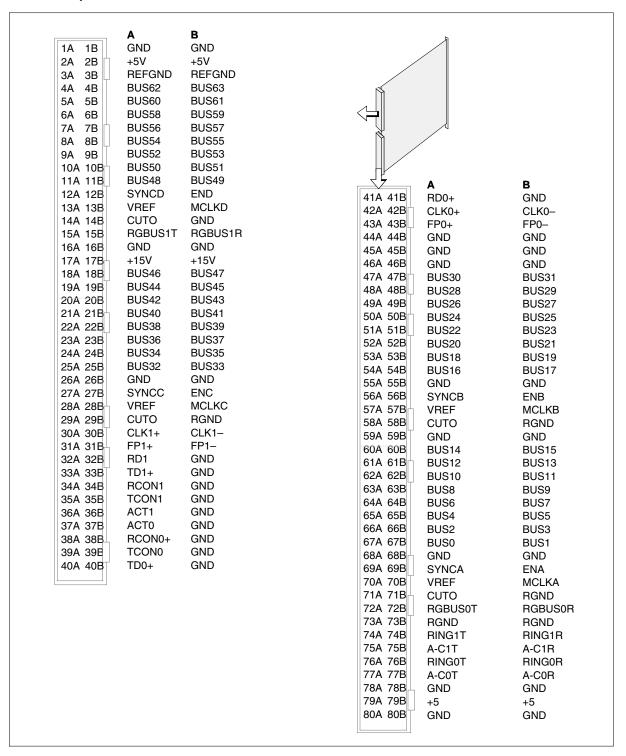

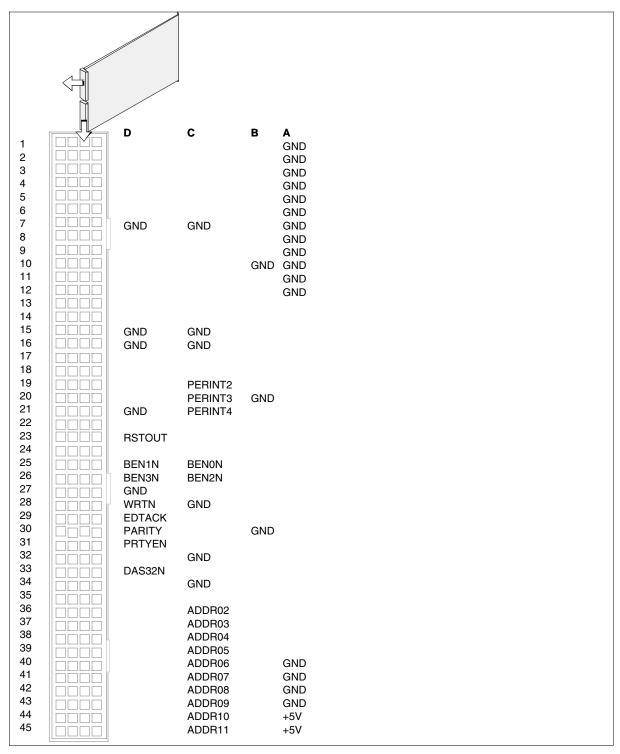

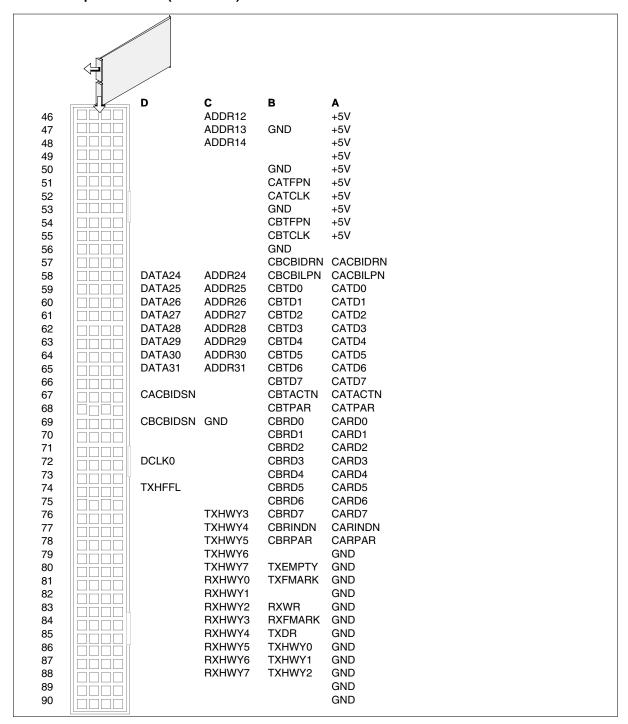

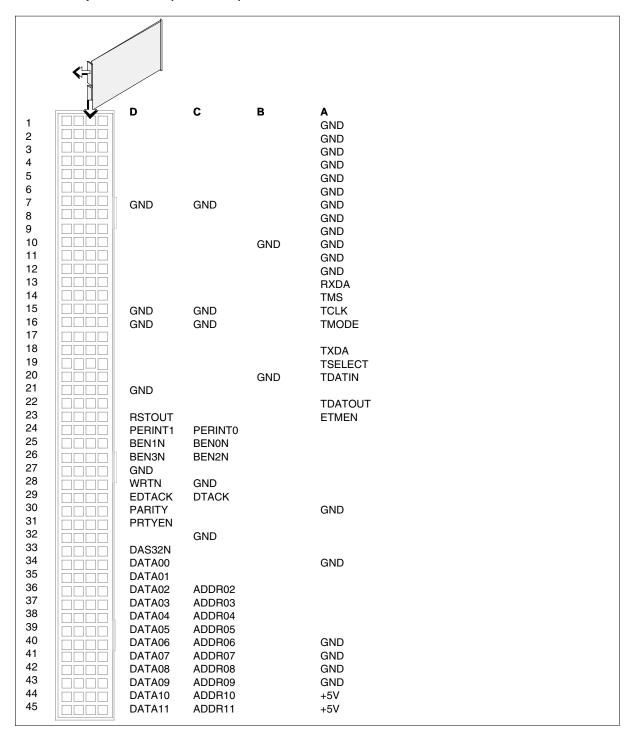

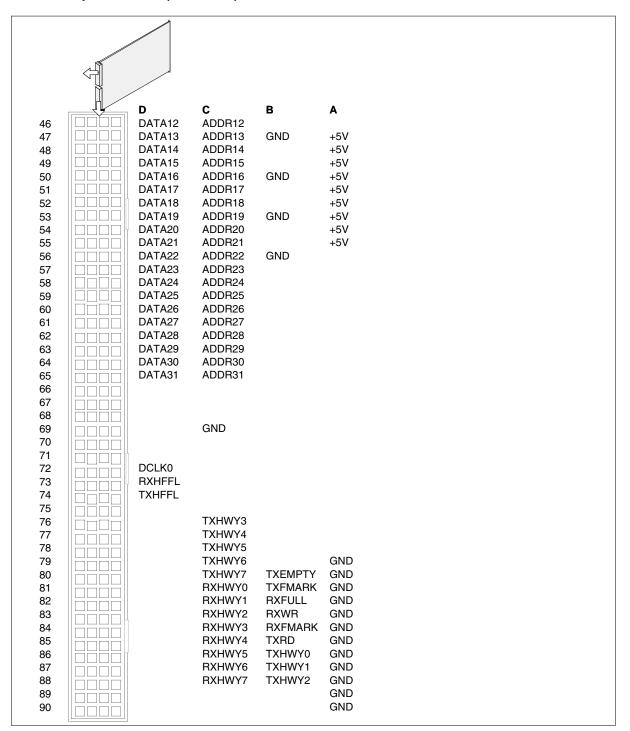

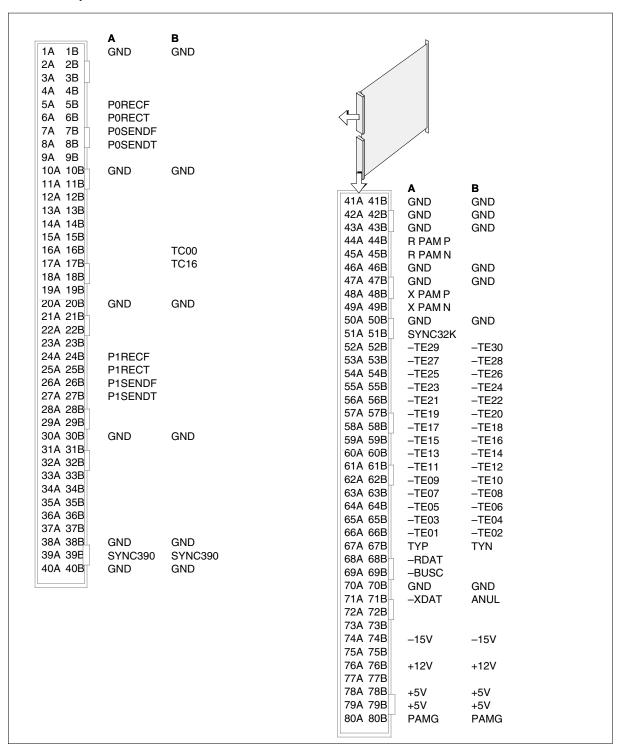

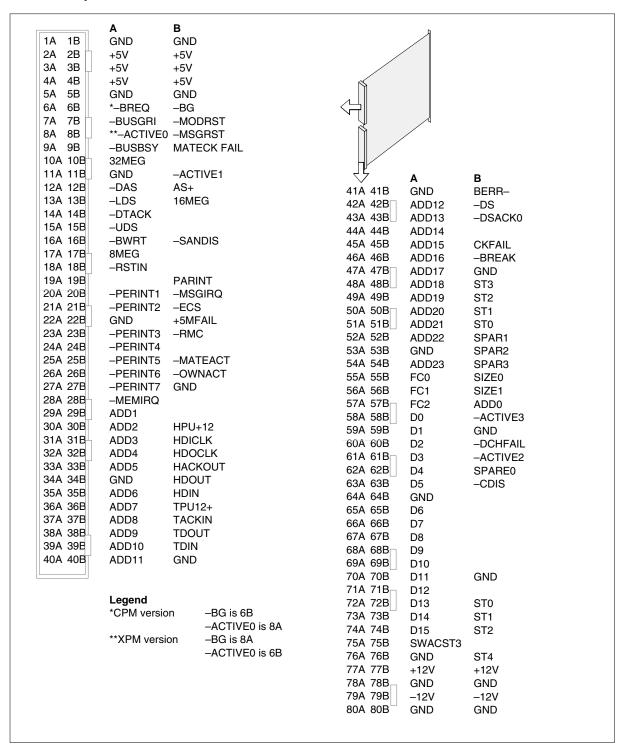

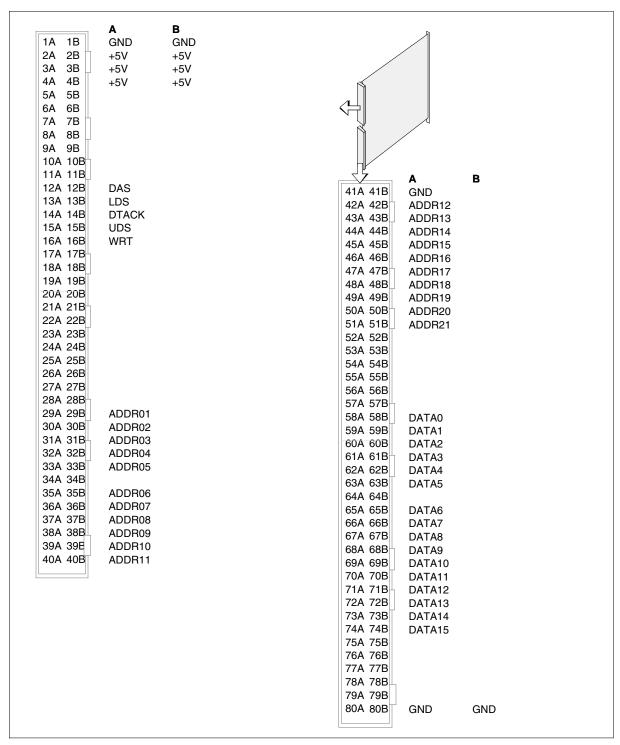

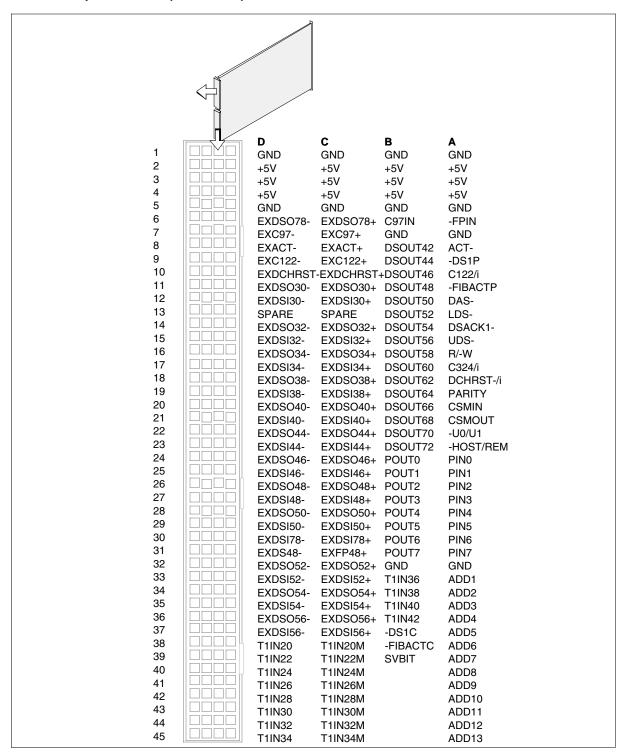

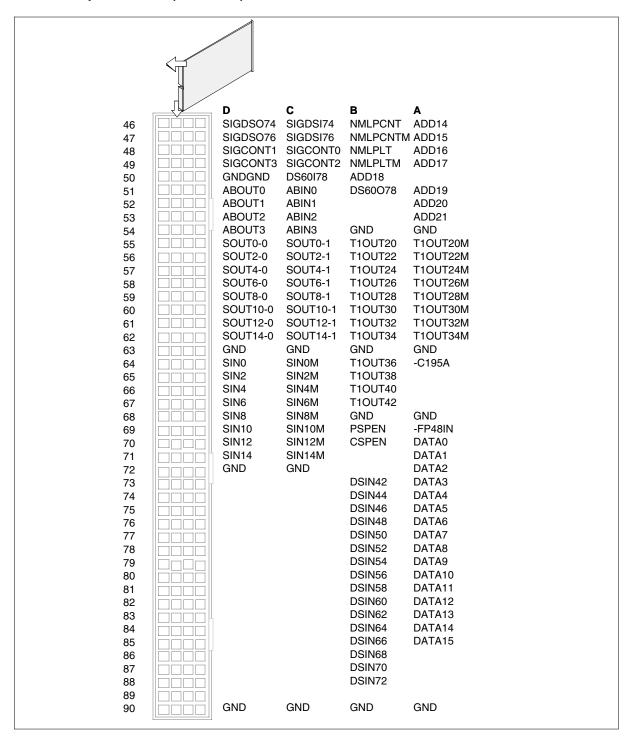

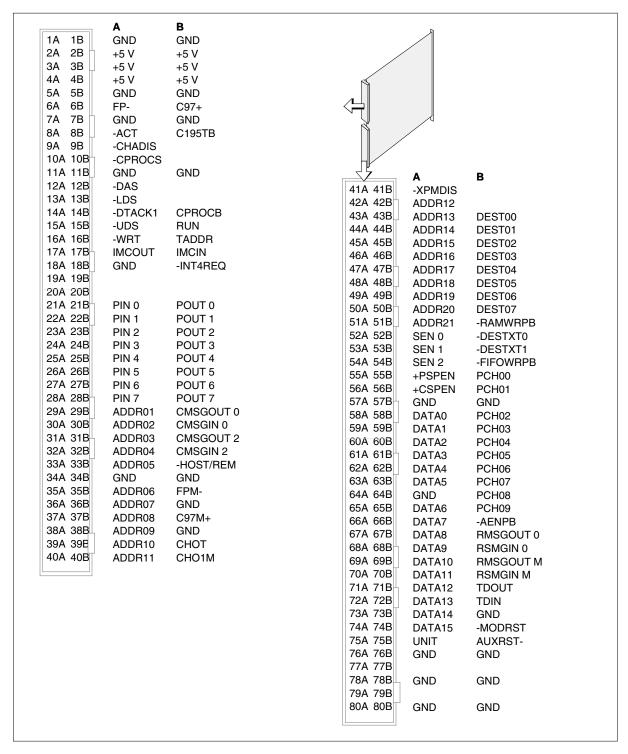

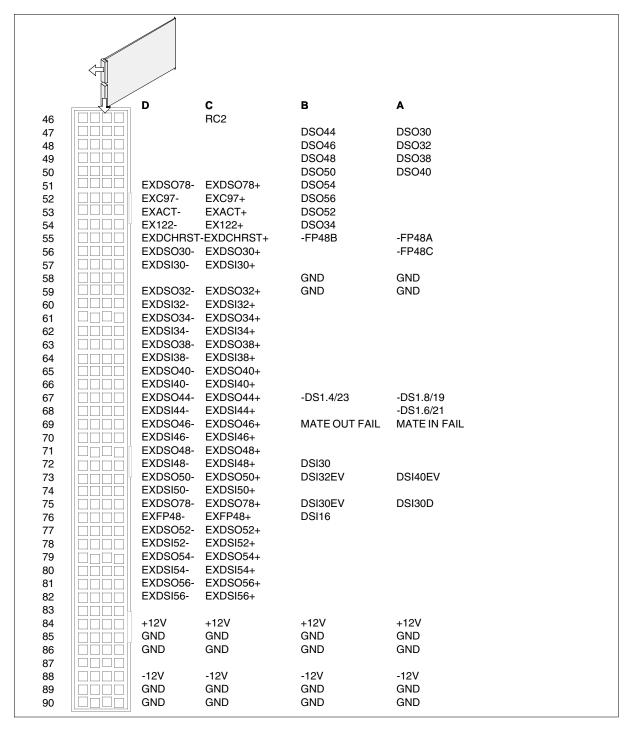

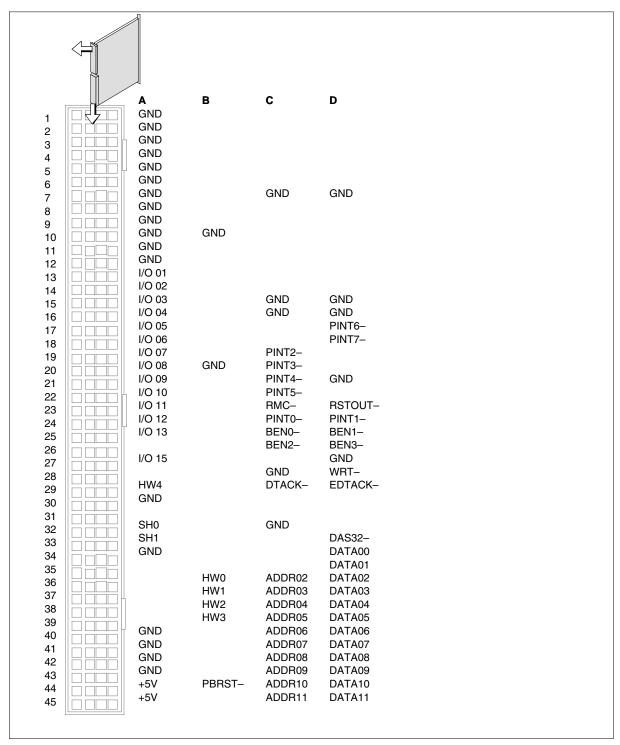

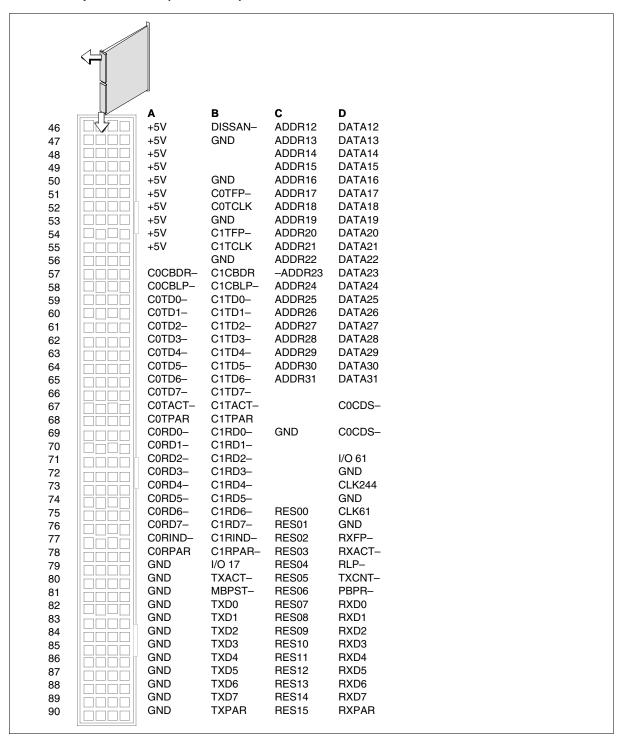

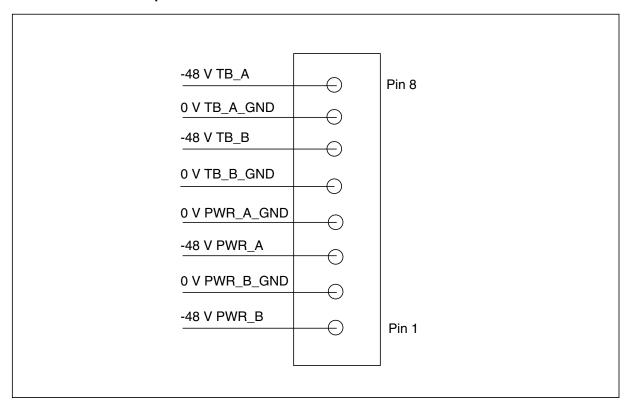

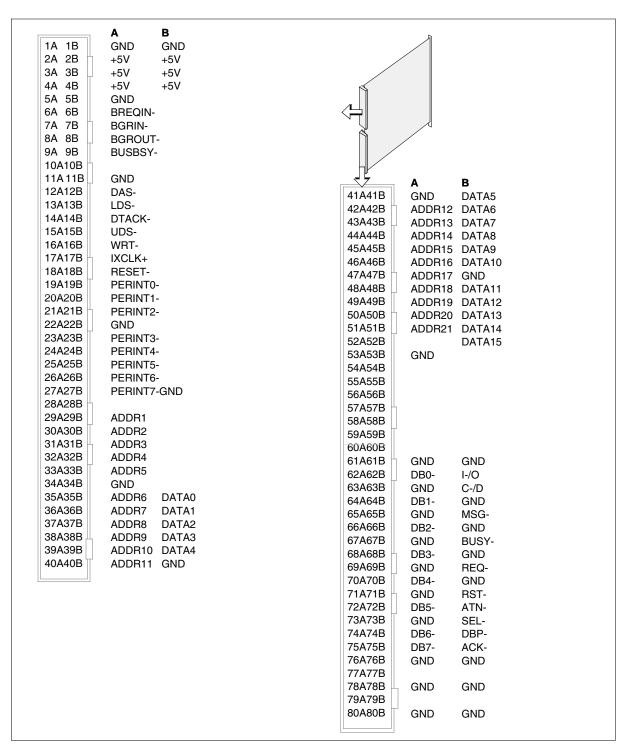

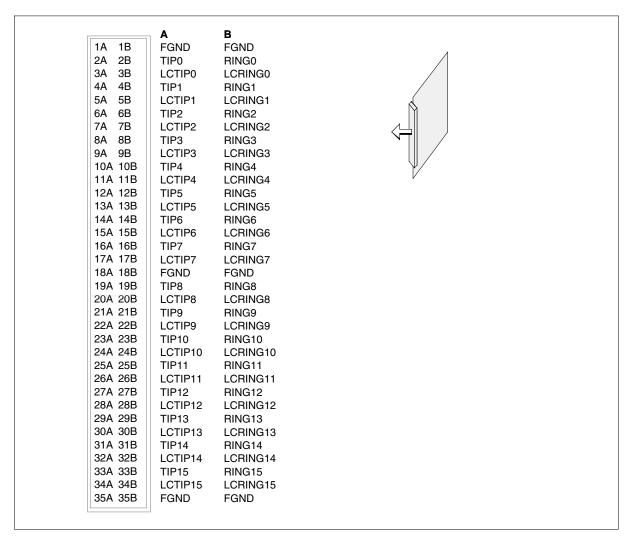

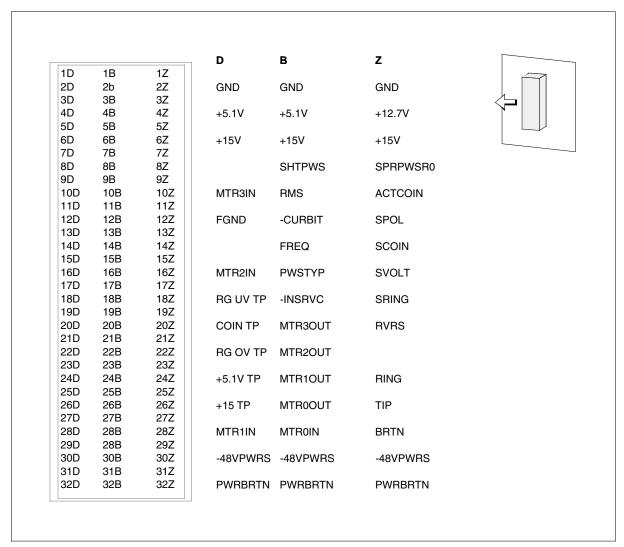

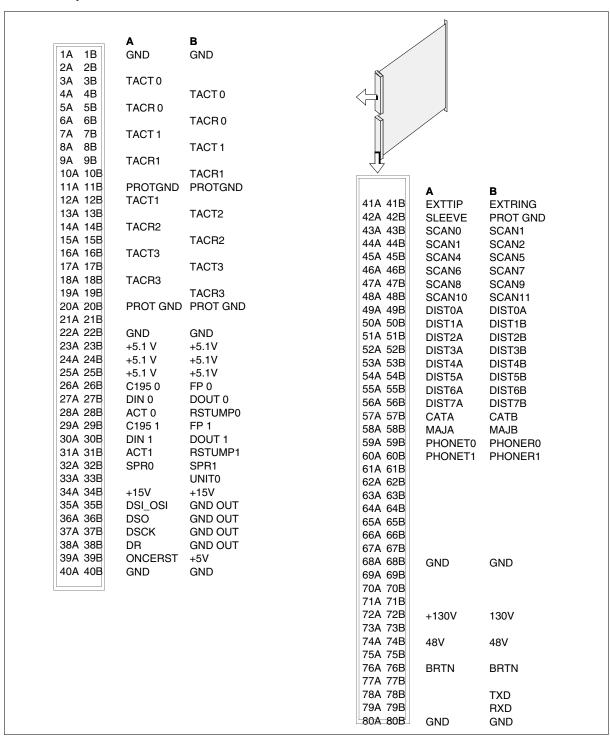

The pin numbers for the NT9X at card locations 07 and 32 appear in the following figures.

### NT9X pin numbers (in location 07) (Part 1 of 2)

### NT9X pin numbers (in location 07) (Part 2 of 2)

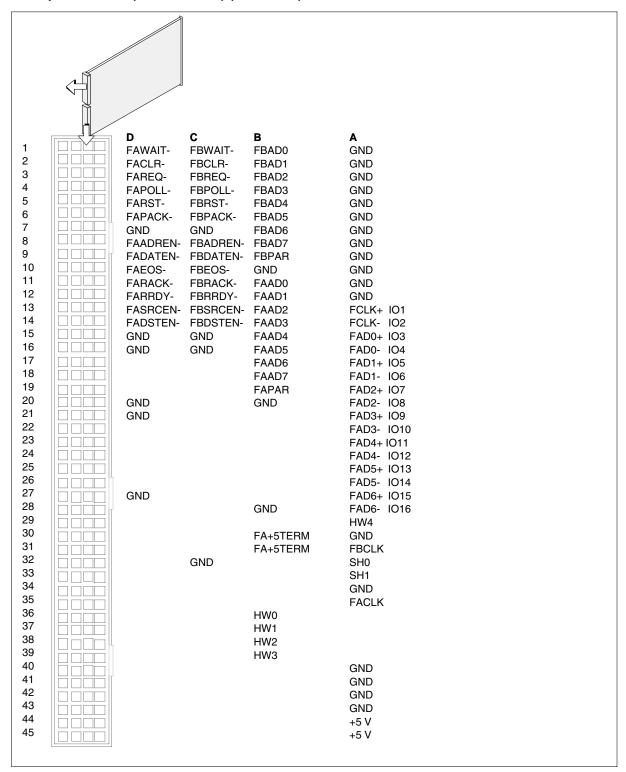

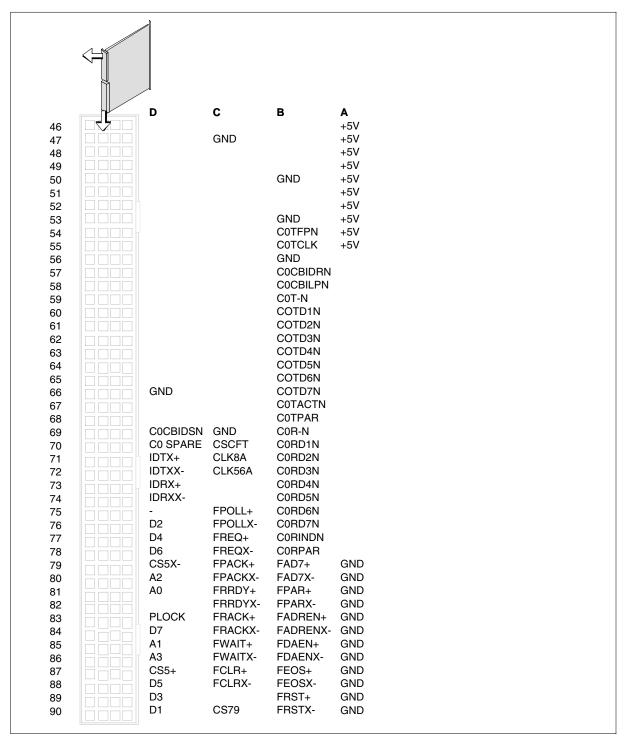

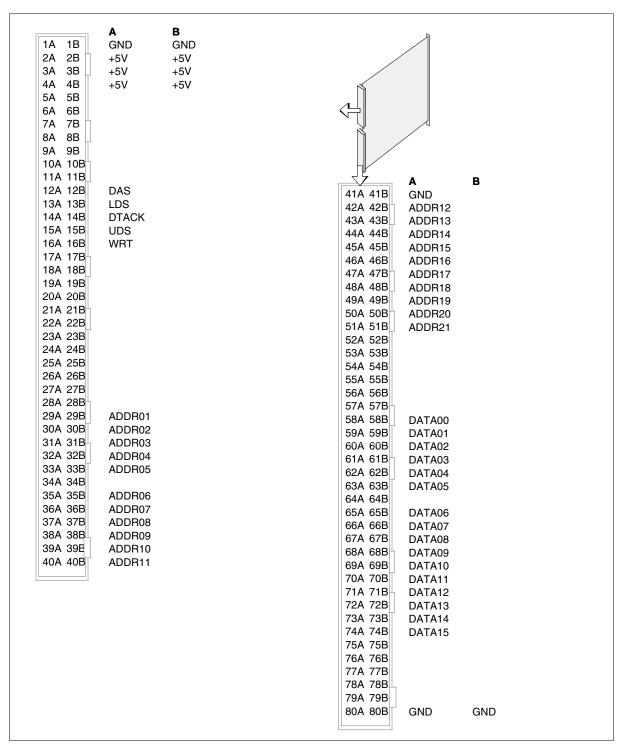

#### NT9X pin numbers (in location 32) (Part 1 of 2)

### NT9X74CA (end)

### NT9X pin numbers (in location 32) (Part 2 of 2)

### **Product description**

The NT9X74DA reclocks and repeats all frame bus (F-bus) communication between the intershelf F-bus and the intrashelf F-bus. Each NT9X74DA contains the circuits to drive one of the two separate F-buses.

The NT9X74DA supercedes the NT9X74CA. The NT9X74DA has channel bus (C-bus) terminations for link peripheral processor (LPP) channel access.

### Location

The NT9X74DA is in the CCS7 link interface unit 7 (LIU7) shelf in card slot 07 or 32.

### **Functional description**

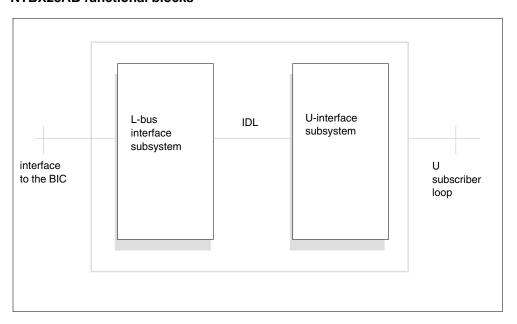

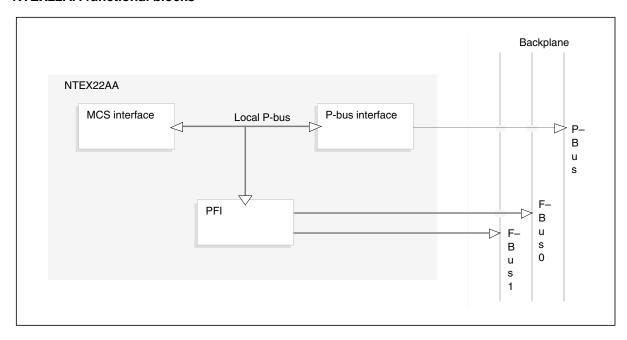

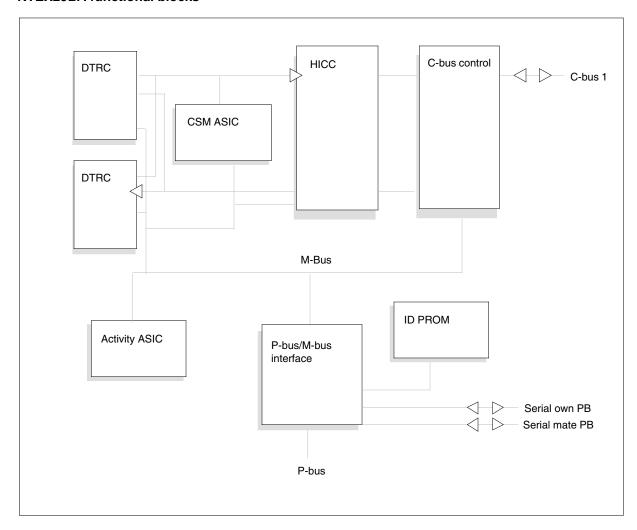

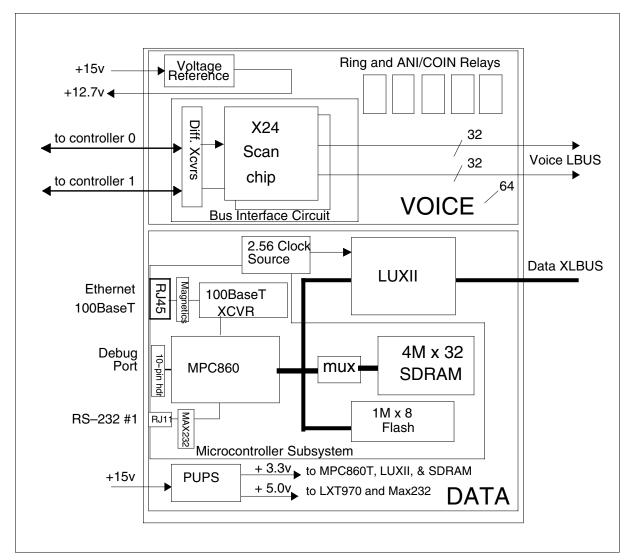

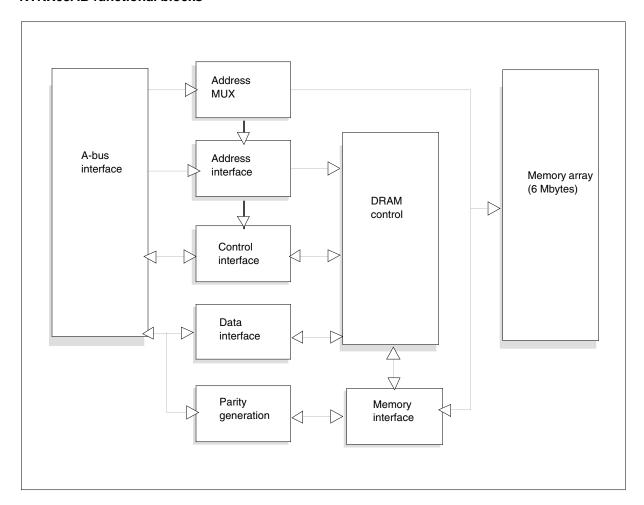

### **Functional blocks**

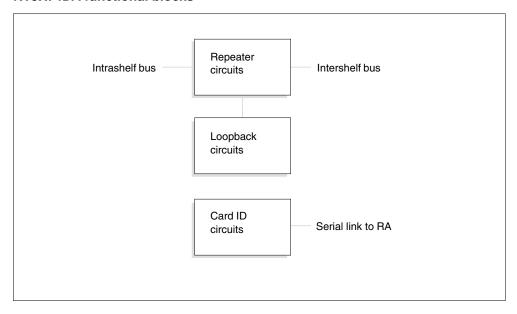

The NT9X74DA has the following functional blocks:

- repeater circuits

- loopback circuits

- card ID circuits

### Repeater circuits

The repeater circuits buffers and reclocks signals between the intershelf F-bus (RA) and the intrashelf F-bus (PFI). The PFIs, FxDSTEN and FxSRCEN control two signals to select the direction of the buffers.

### Loopback circuits

The loopback circuits permits the repeater to communicate with the RA. Loopback can occur on the intershelf side or on the intrashelf side. This capability allows testing of the F-bus which do not rely on the application-specific units (ASU). Use of the two types of loopback allows the system to isolate intrashelf faults or intershelf faults.

#### Card ID circuits

The card ID circuits allows the repeater to read the card IDs of the following:

- NT9X74

- NT9X79

- NT9X30

- NTEX20

The card ID circuits use a microcontroller to communicates with the RA over a serial link.

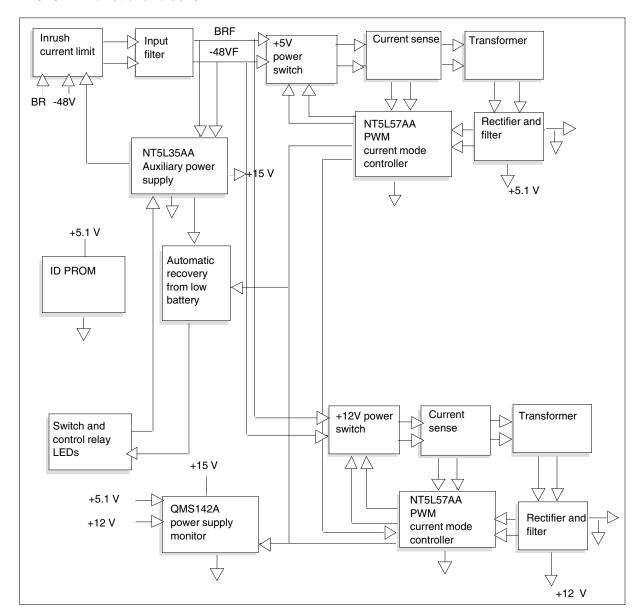

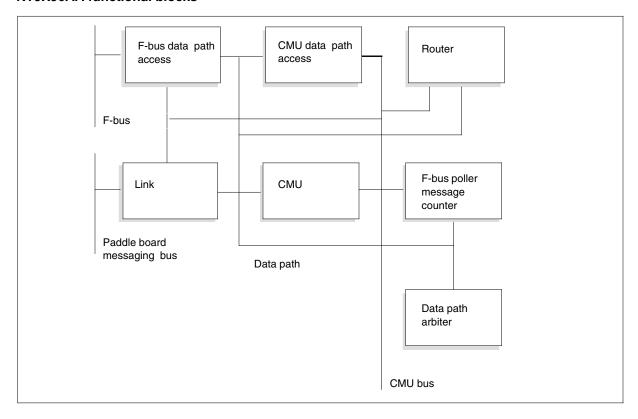

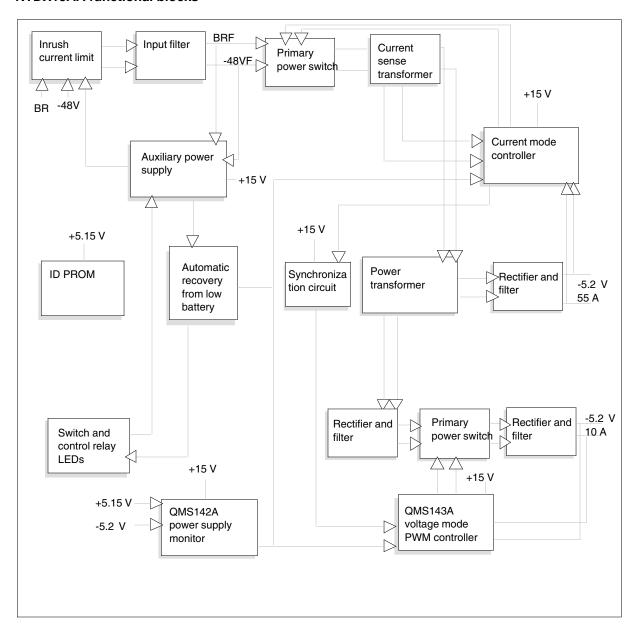

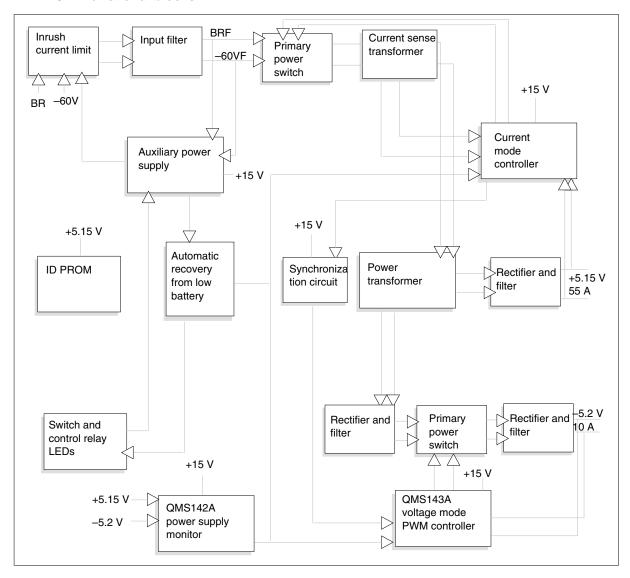

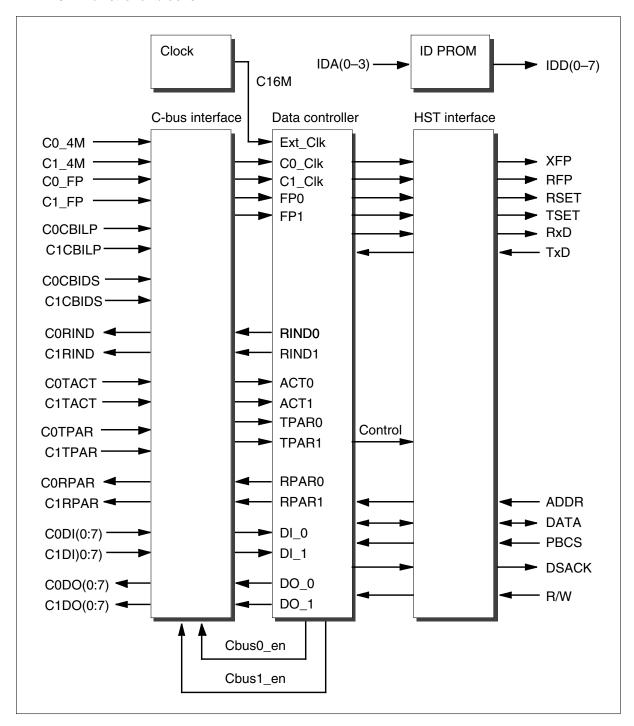

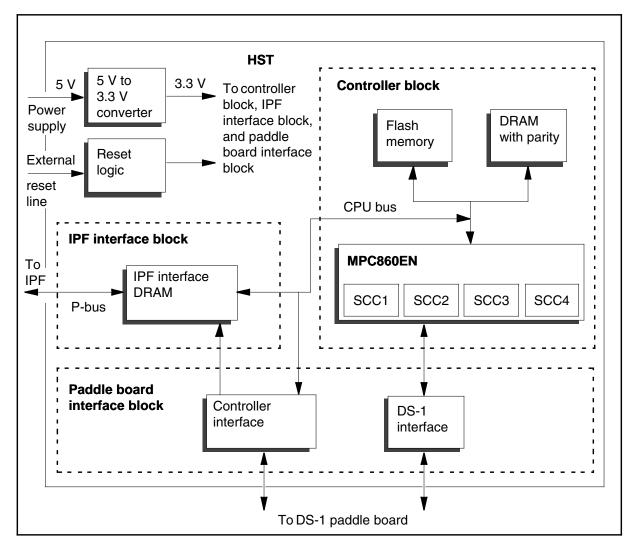

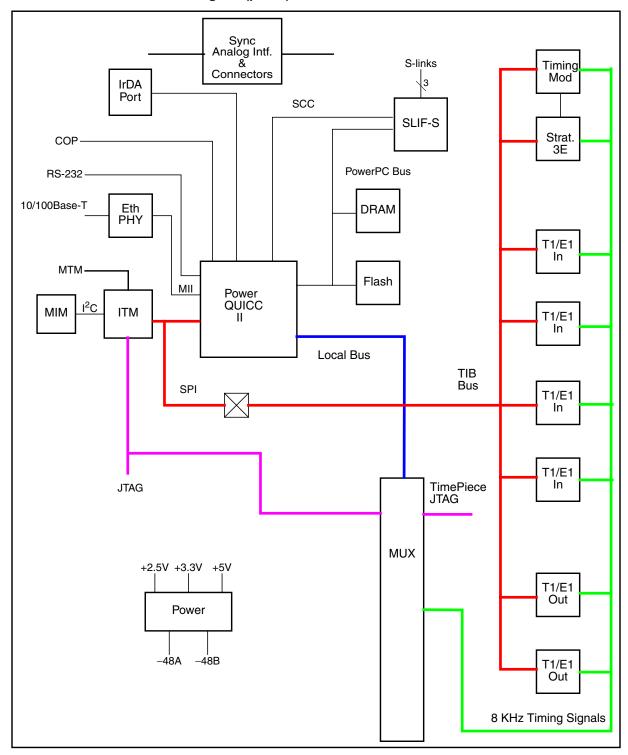

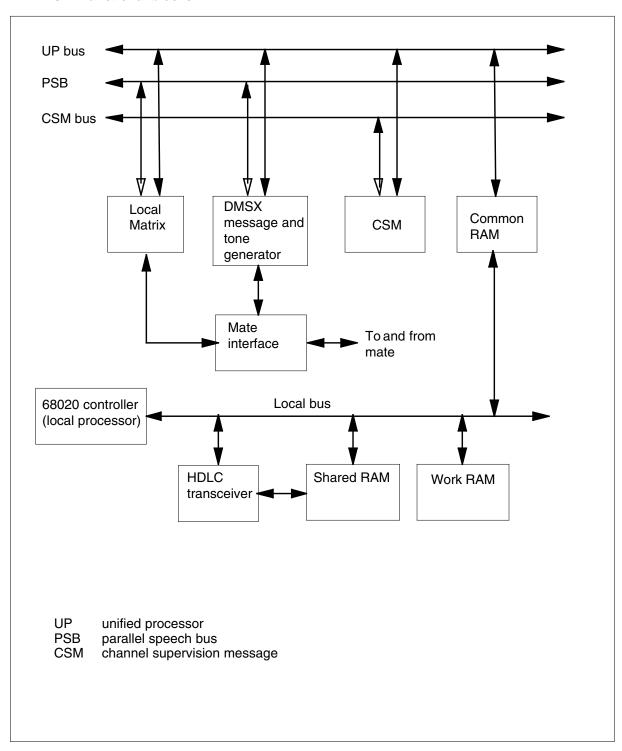

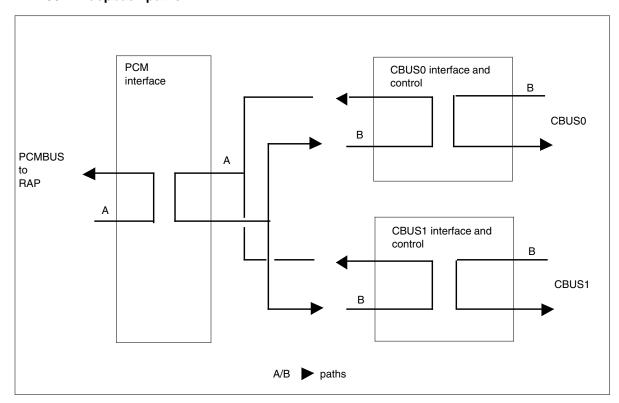

The relationship between the functional blocks appears in the following figure.

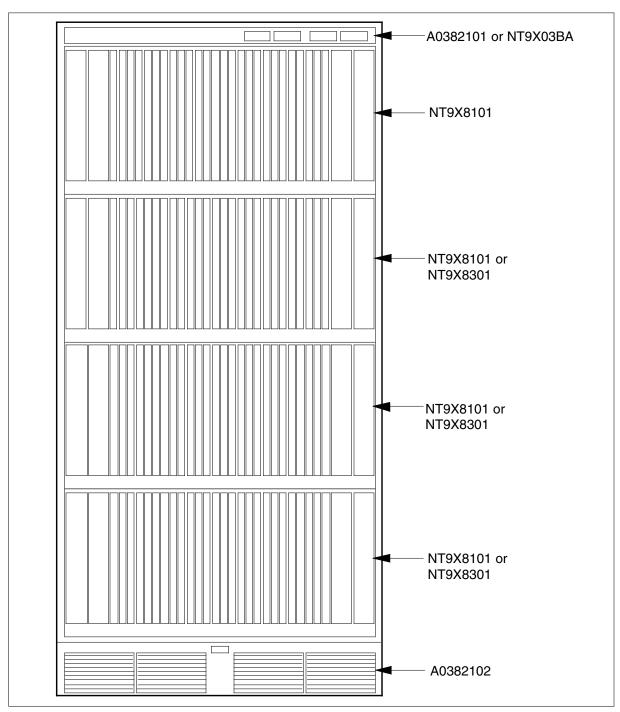

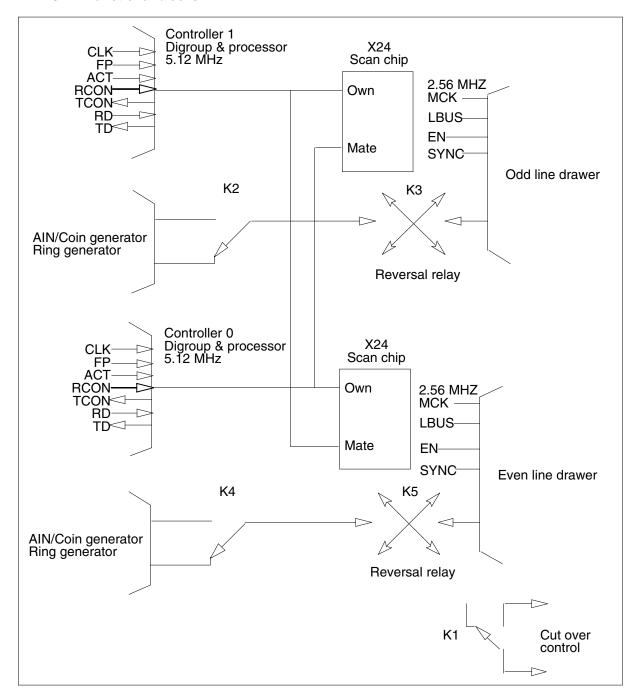

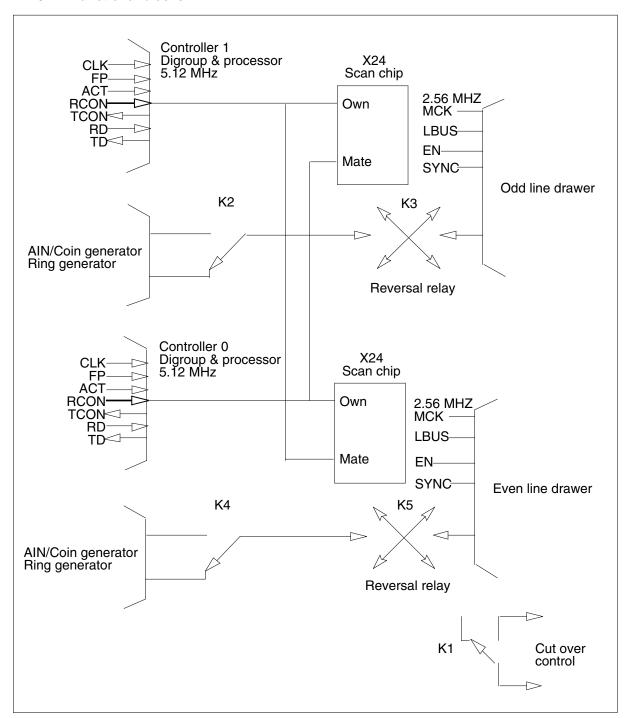

### NT9X74DA functional blocks

### **Signaling**

### Pin numbers

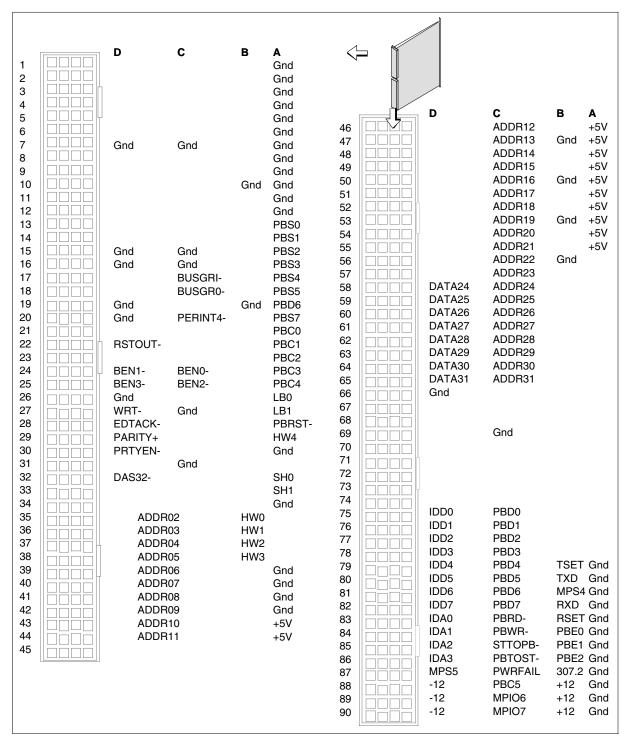

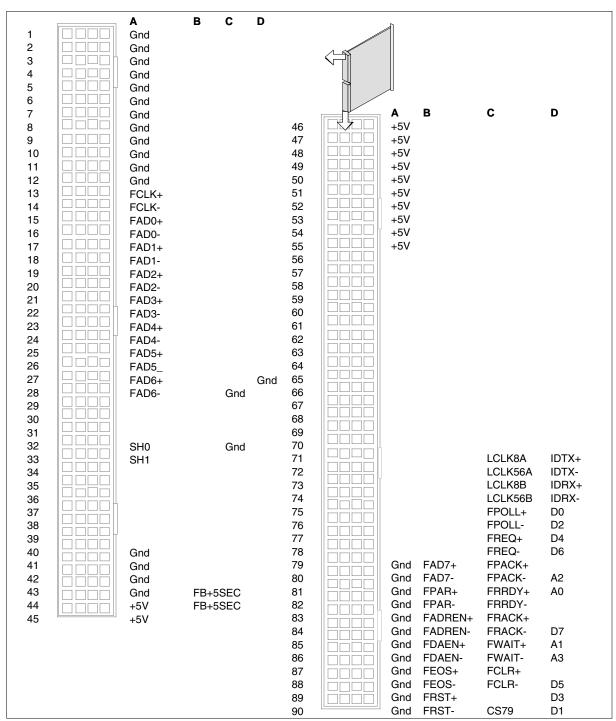

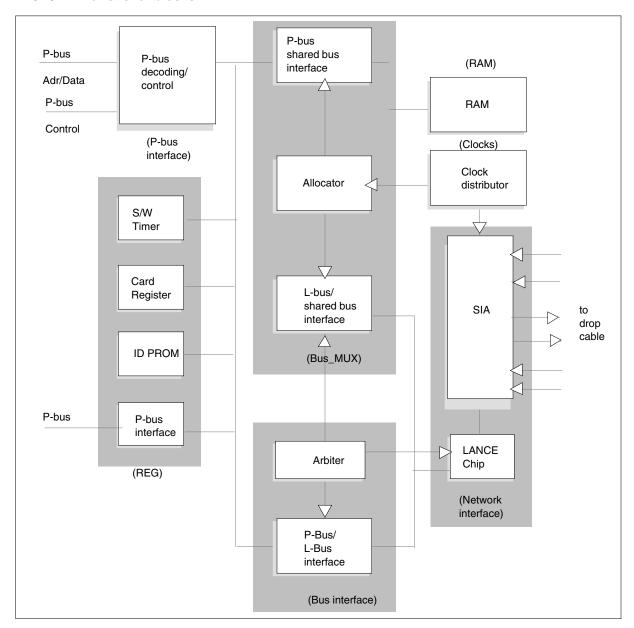

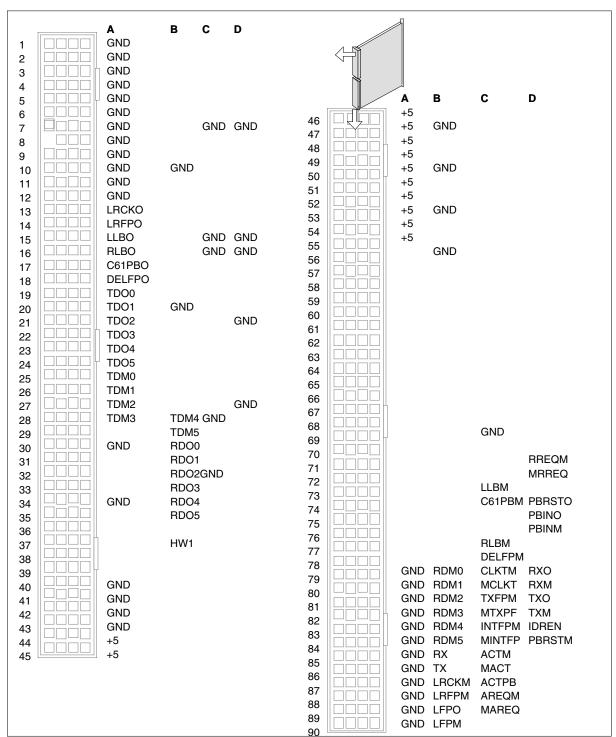

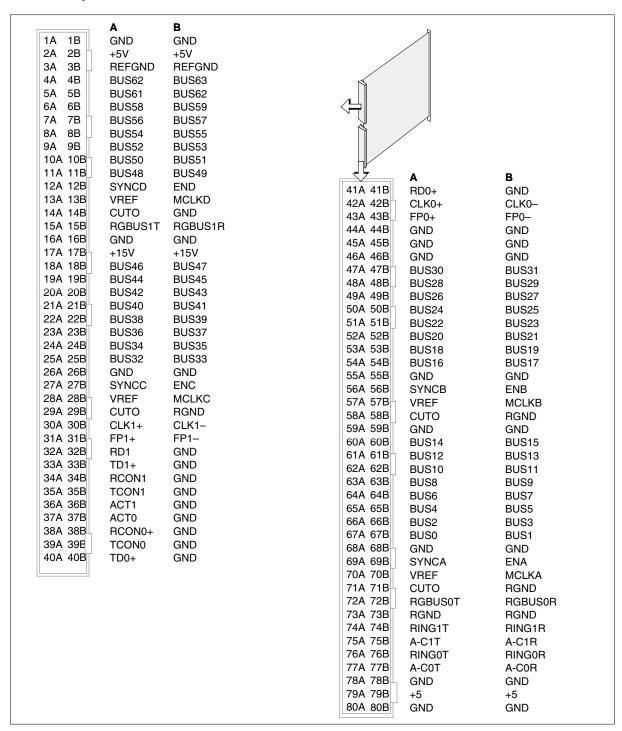

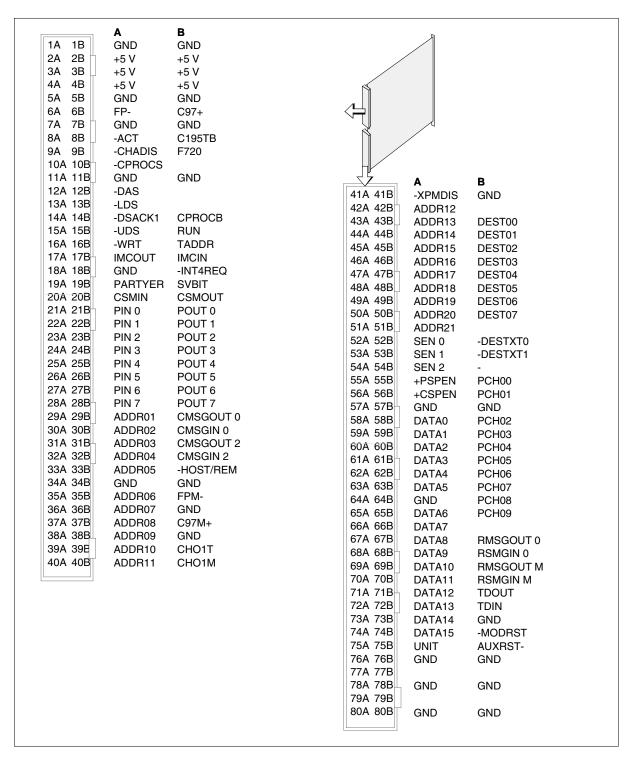

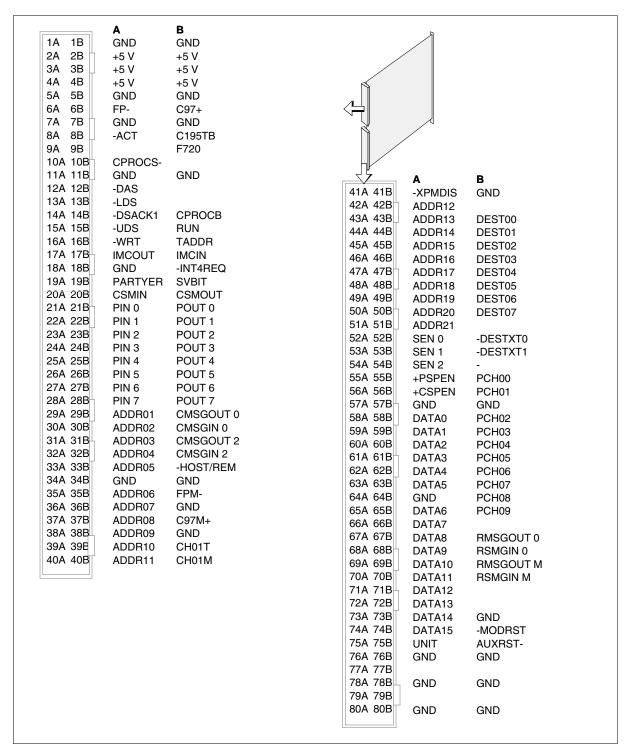

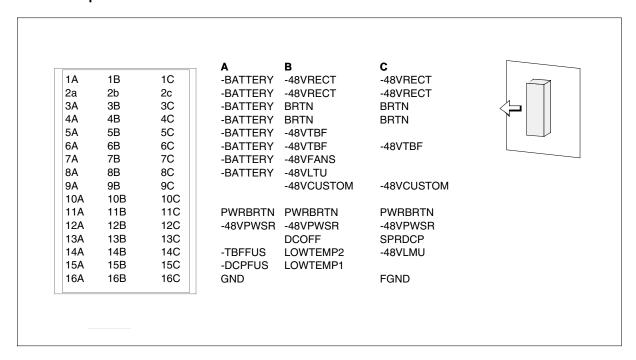

The pin numbers for the NT9X74DA at card locations 07 and 32 appear in the following figure.

### NT9X74DA pin numbers for location 7 (Part 1 of 2)

### NT9X74DA pin numbers for location 7 (Part 2 of 2)

### NT9X74DA pin numbers for location 32 (Part 1 of 2)

### NT9X74DA (end)

### NT9X74DA pin numbers for location 32 (Part 2 of 2)

### **Product description**

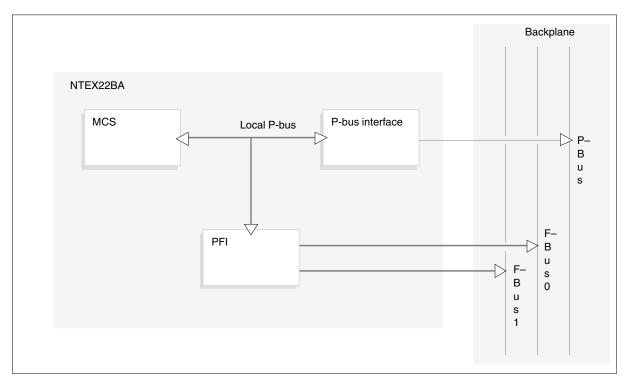

The NT9X75AA is a processor bus (P-bus) to frame transport bus (F-bus) interface (PFI) card. This card is a part of the signal transfer point (STP) link interface unit (LIU7). The NT9X75AA card provides an interface between a P-bus and the two instances of the F-bus. The two instances of the F-bus are F-bus A and F-bus B.

The system duplicates the F-bus interfaces, which are fully independent. This condition allows the P-bus to access one of the F-bus interfaces. This action continues when other F-bus or the hardware associated with the other F-bus do not operate. The card provides a path to allow the F-bus master to reset an LIU7. The F-bus master is the rate adaptor (RA).

### **Functional description**

The PFI consists of a P-bus interface and duplicated F-bus interfaces. Each F-bus interface has a transmit block and a receive block. The P-bus interface provides access from the P-bus to the two F-bus interfaces. The P-bus provides two different sets of ports. Each set associates with one of the F-bus interfaces. The PFI appears in the P-bus as a 16-bit slave.

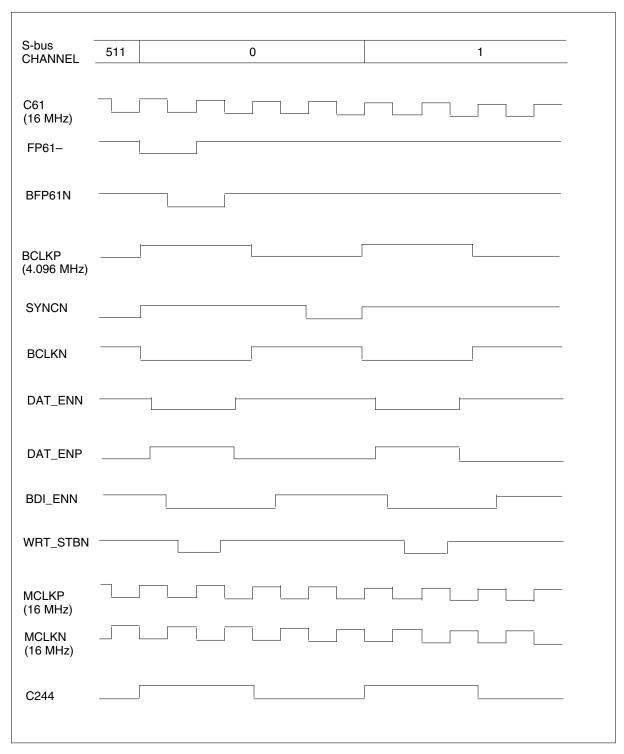

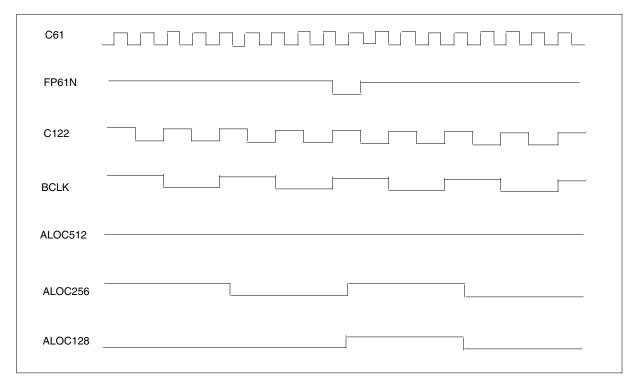

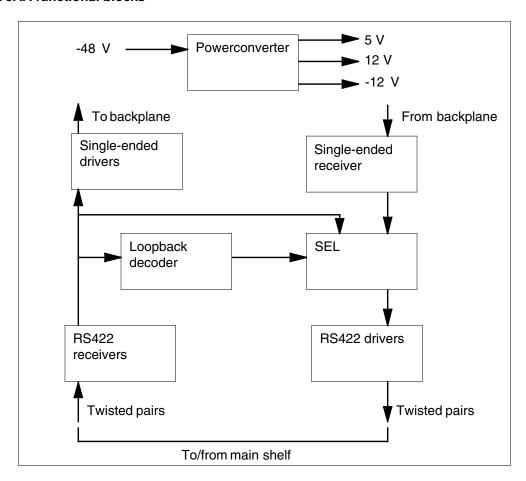

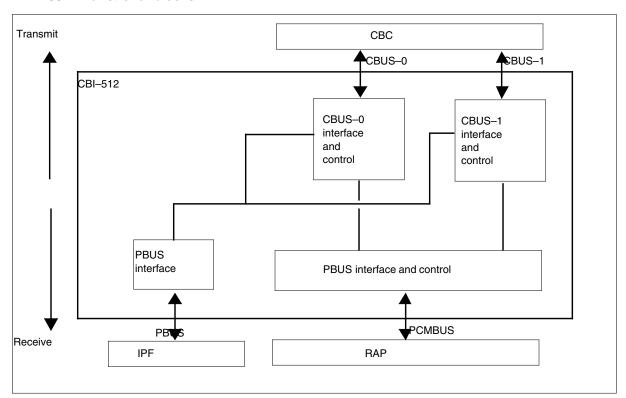

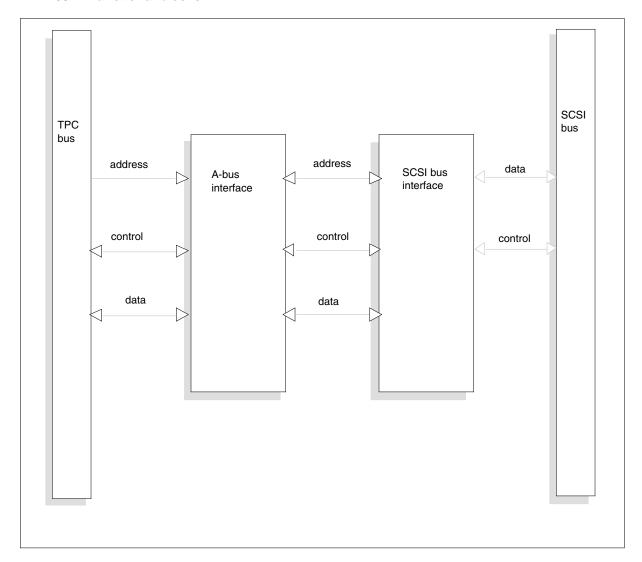

### **Functional blocks**

The NT9X75AA has the following functional blocks:

- F-bus transmit blocks A and B

- F-bus transmit block B

- F-bus receive block A and B

- F-bus receive block B

- P-bus interface

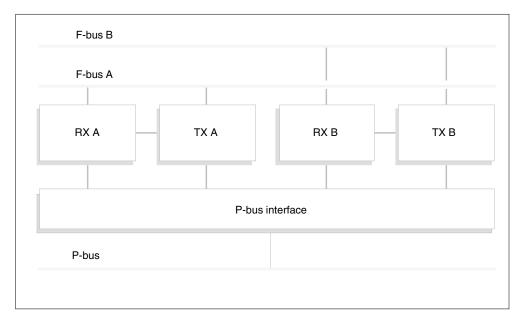

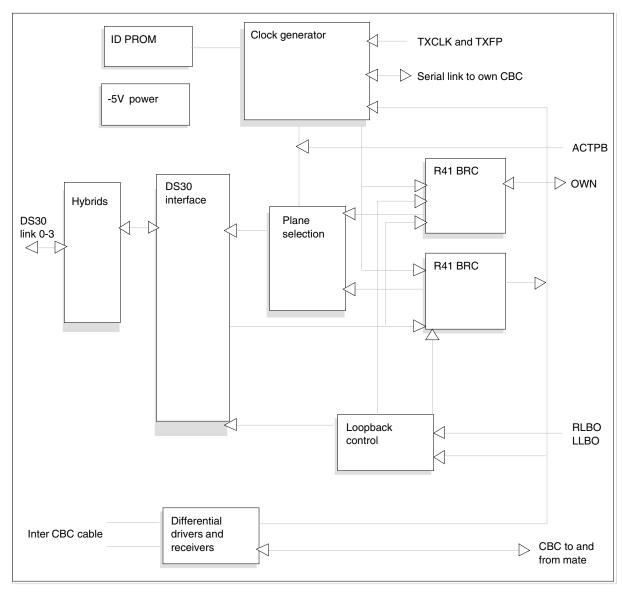

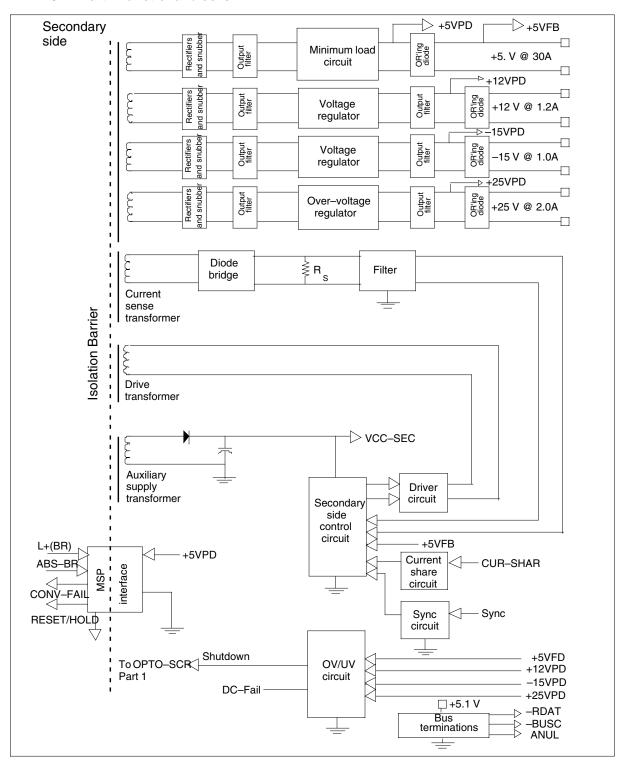

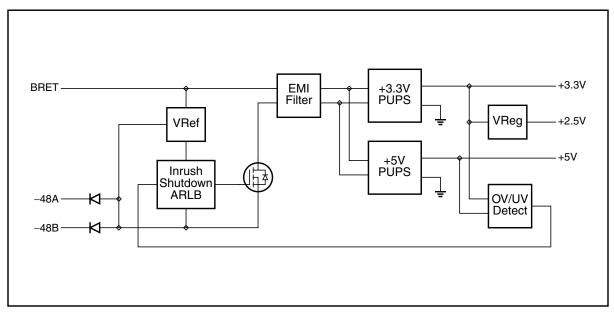

The functional relationship between the blocks appears in the following figure.

#### NT9X75AA functional blocks

### **Transmit blocks**

Transmit blocks A and B relate to logic functions that send messages to the F-bus. Transmit blocks contain the following elements:

- buffer space

- buffer space protection logic, which protects with parity the data stored in the first-in first-out (FIFO) queue

- bus request logic, which generates a request for the use of the F-bus

- poll monitor logic, which allows an LIU7 to use the F-bus

- cyclic redundancy check (CRC) generator/checker, which acts as a CRC generator for the transmit block. The check acts as a CRC checker for the receive block. This check computes the CRC over the data as the data read occurs from the FIFO.

- transmit finite state machine. This machine controls the FIFO read and drive of data, CRC, parity. This machine controls F-bus control signals after the system grants the F-bus.

- bus monitor/error logger logic, which monitors F-bus and internal signals from the time the F-bus request occurs until the end of transmission

### **Receive blocks**

The receive blocks include logic functions that receive messages from the F-bus. The F-bus reset logic and grant logic are in the receive block. The grant

logic is in the receive block even while the grant logic function normally belongs to the transmit block.

The receive blocks contain the following elements:

- buffer space

- buffer space protection logic protects the data in the FIFO with an 8-bit CRC code (CRC8)

- CRC generator/checker is in the transmit block and shared with the receive block

- receive finite state machine controls data writing from the F-bus to the receive FIFO, CRC and CRC8 calculation. This machine drives F-bus response signals RACK and PACK. This machine also routes receive message status register contents and calculates CRC8 to the FIFO.

- receive message status register. The register constructs a message-by-message record of errors. The system routes the register to the receive FIFO after the last byte of the message.

- F-bus command logic, which monitors the F-bus control lines ADEN, POLL, and RESET

#### P-bus interface

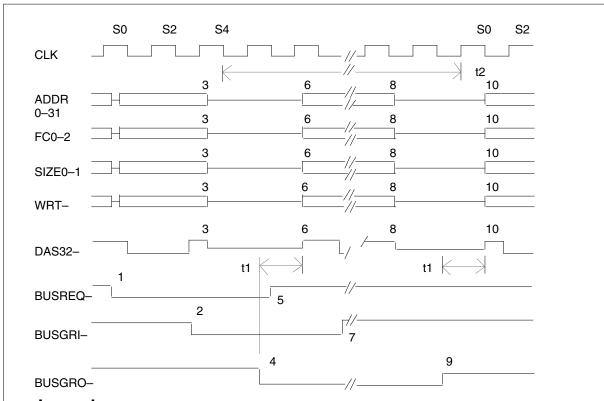

The PFI appears as a 16-bit P-bus slave on the P-bus. The P-bus interface generates parity. Parity is an optional feature of the P-bus. The P-bus signal DAS32- derives the timing of the P-bus interface through the delay lines. The design provides a high degree of immunity against noise glitches in the P-bus signals.

### Data flow control

Data travel between the PFI and the P-bus occurs through transceivers. The system enables the transceivers when the system addresses card and signal and asserts the CARD-. The latched version of P-bus signal WRT- completes the direction control.

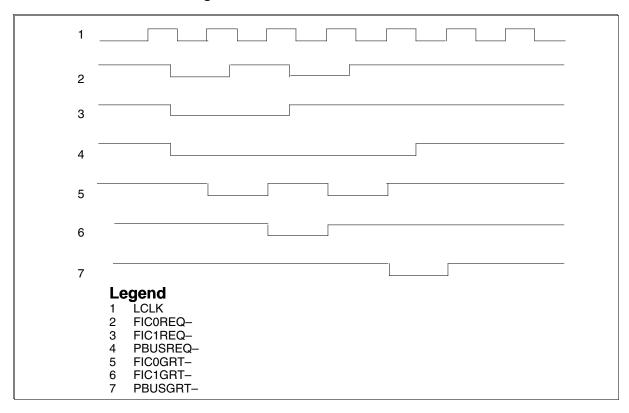

### Interrupt logic

The system generates interrupts in the receive and transmit blocks. Similar interrupts from the A and B side are ORed together. The system can mask interrupts on each F-bus basis with the use of the control port.

### Reset logic

Reset logic meets the timing requirements to reset the FIFOs. Resets are classified into global reset and selective resets. Power up and P-bus Signal RSTOUT- causes global resets. The voltage monitor initiates the global reset.

Selective resets require that the important enable bit in the control register be set.

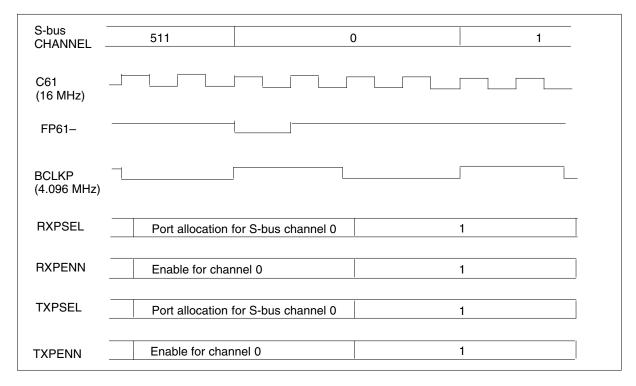

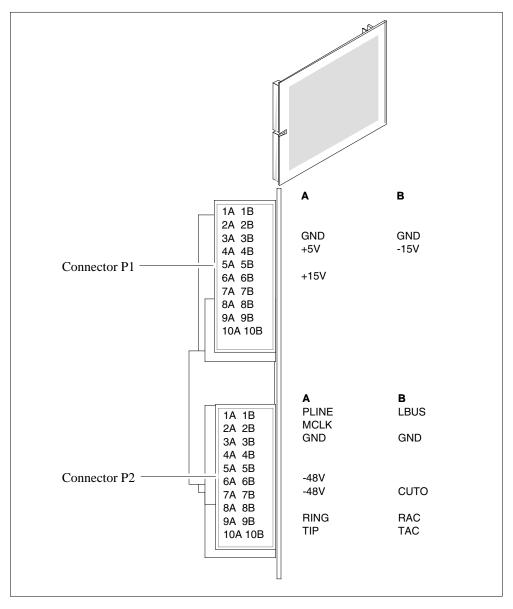

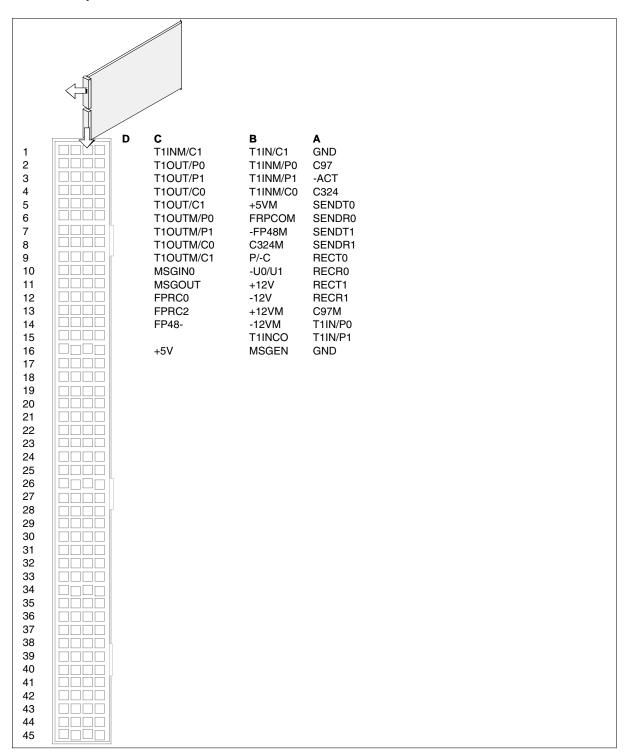

### **Signaling**

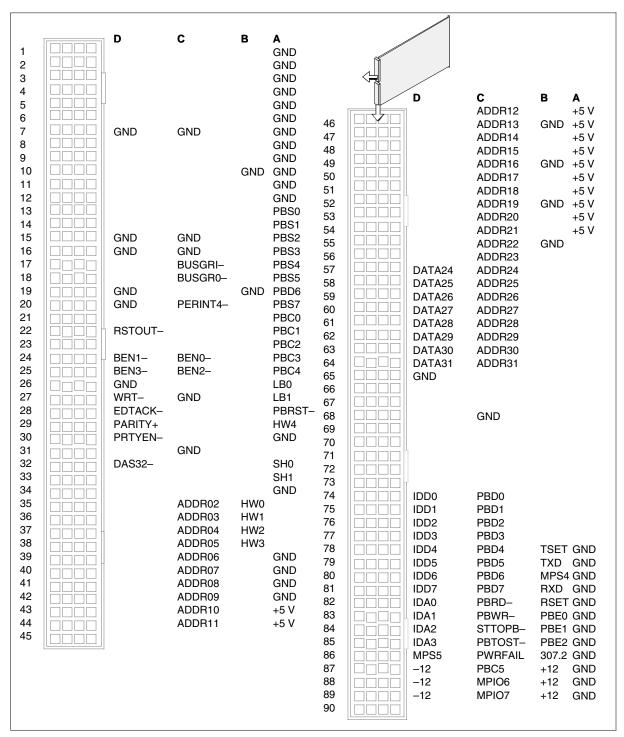

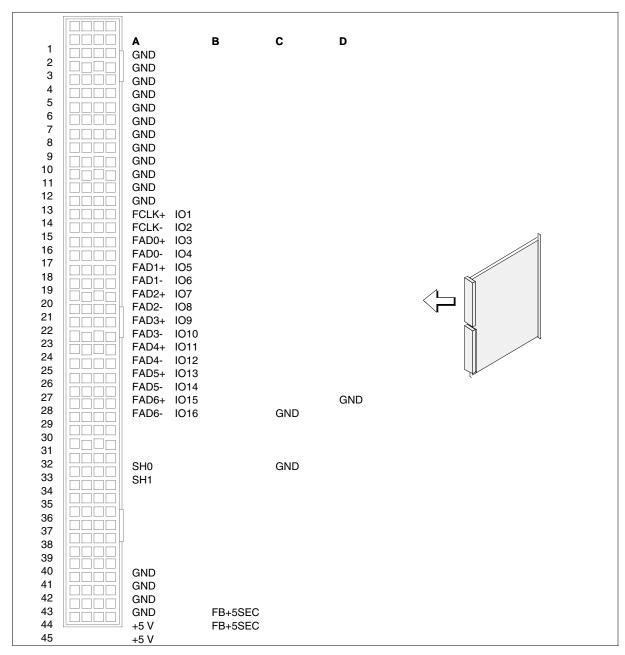

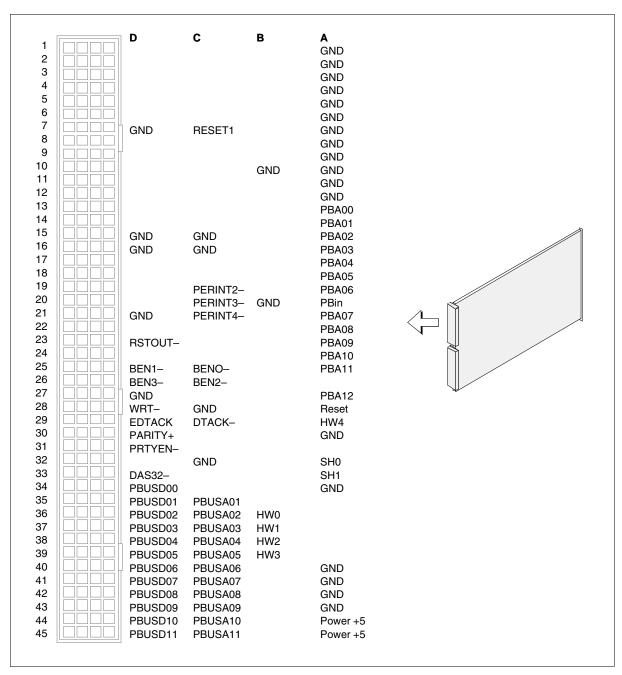

### Pin numbers

The pin numbers for NT9X75AA. appear in the following figures.

#### NT9X75AA pin numbers (Part 1 of 2)

### NT9X75AA pin numbers (Part 2 of 2)

NT9X75AA (end)

### **Technical data**

### **Power requirements**

The normal power requirements for the NT9X75AA are 6.5 A from a +5V supply, with a maximum of 10 A.

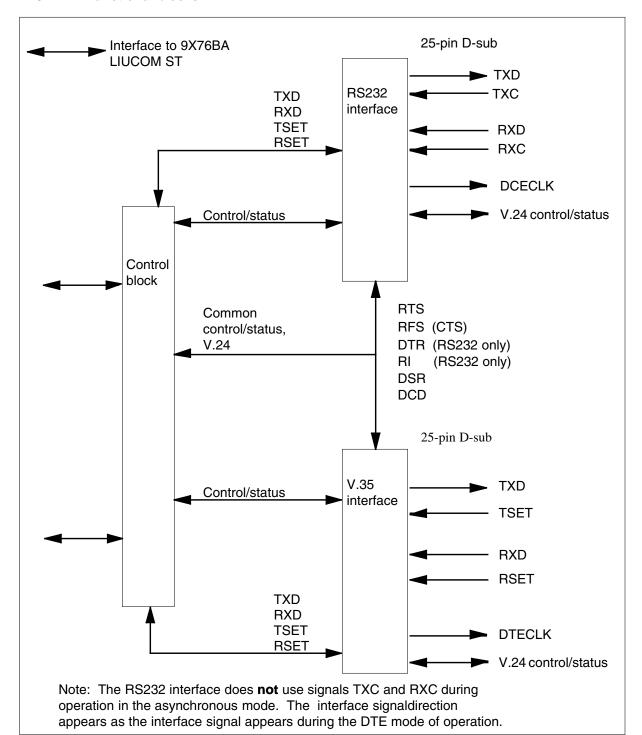

### **Product description**

The signaling transfer point (STP) connects to each CCS7 link through an NT9X76AA signaling terminal (ST) card. This card is a single board with two processors that handle the data link level functions of the CCS7 protocol. The link general processor (LGP) performs higher level servicing. The LGP is an external processor. The LGP communicates with the ST through a two-ported RAM accessible through the processor bus (P-bus).

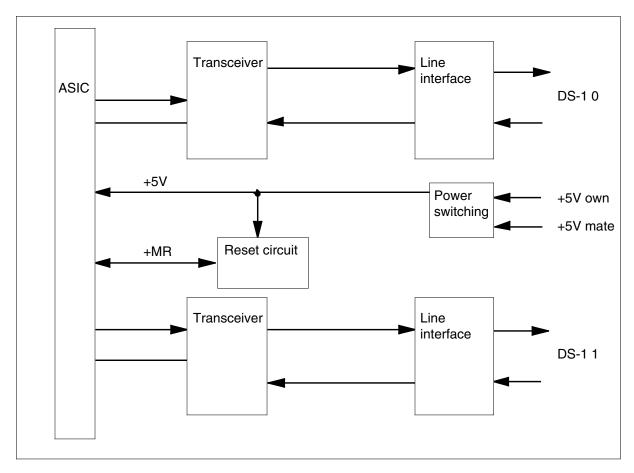

### **Functional description**

The ST sends and receives messages to and from an associated link paddle board (PB). The two processors move the data. The two processors perform the data link level functions of the CCS7 protocol.

Incoming data passes through the PB from a link. The PB performs the electrical conversion. This conversion passes the data to the serial communications controller (SCC) of the ST. The SCC handles the following functions:

- converts serial/parallel data

- detects flags

- generates and checks CRC

- inserts and deletes zero bits

The data link processor (DLP) services the SCC. The DLP sends the data through the DLP/master processor (MP) first-in first-out (FIFO) device to the MP. The MP can pass the data to the LGP through the MP/LGP interface RAM. Data that goes to the link flows in the opposite direction. This DLP services the SCC. The DLP sends the data through the DLP/master processor (MP) first-in first-out (FIFO) device to the MP. The MP can pass the data to the LGP through the MP/LGP interface RAM. Data that goes to the link flows in the opposite direction. Data passes through the MP/DLP interface RAM, and does not pass through the FIFO.

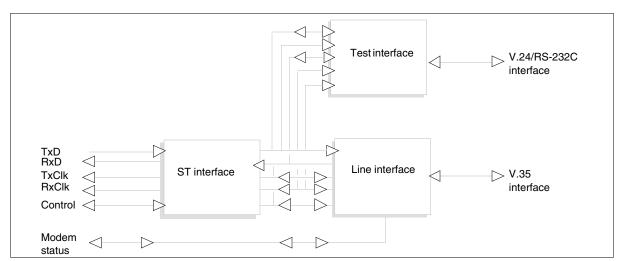

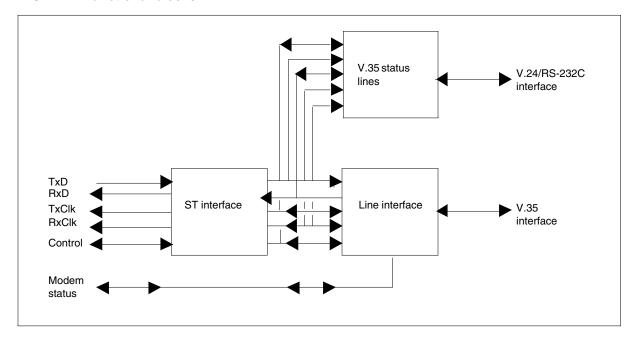

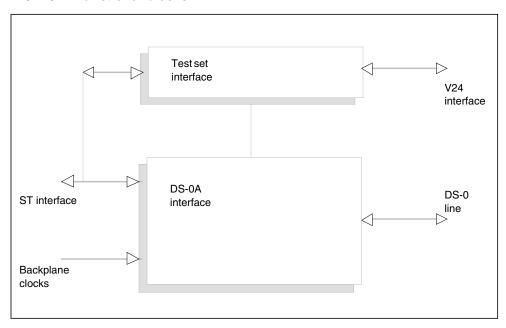

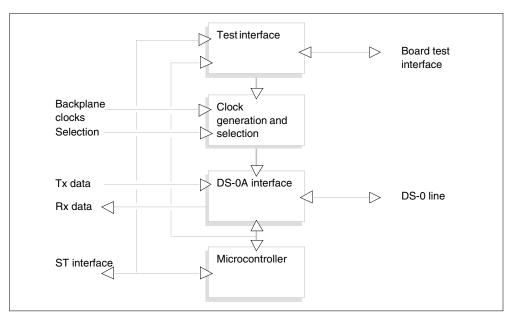

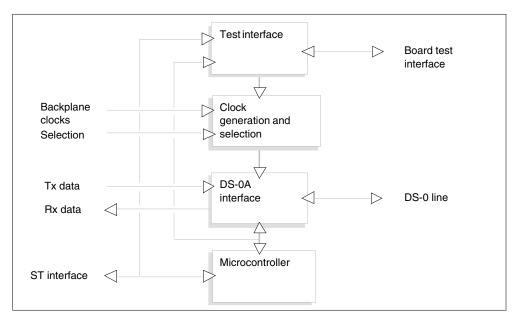

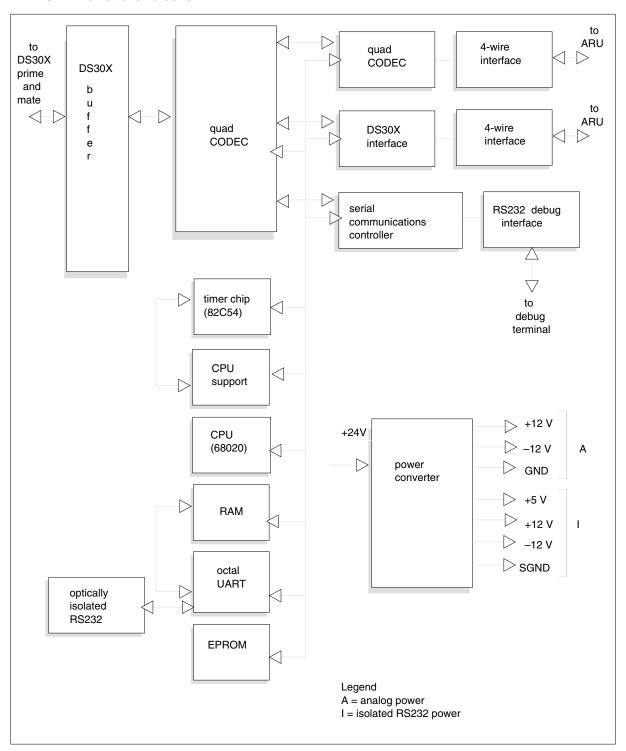

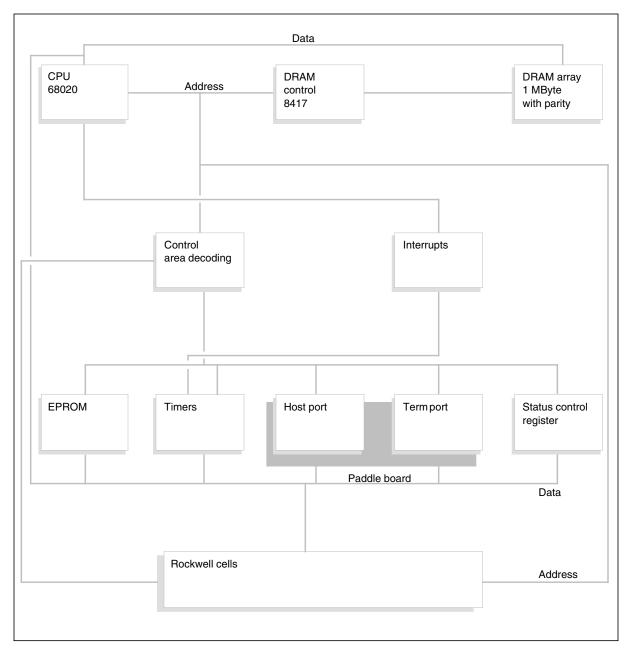

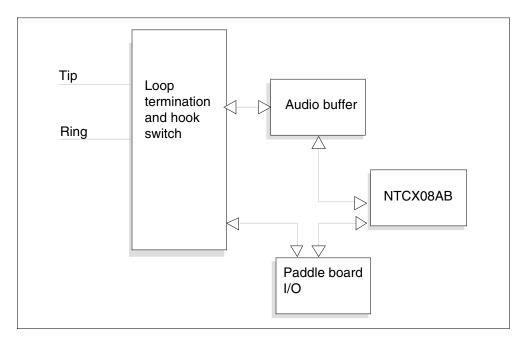

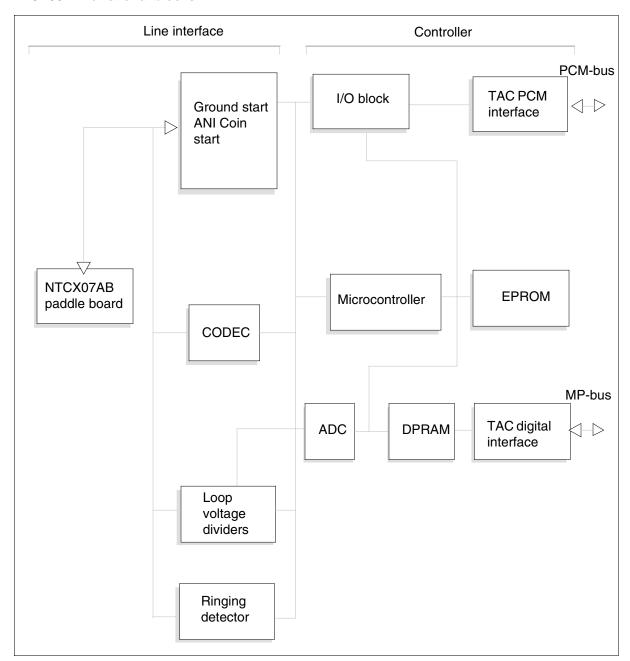

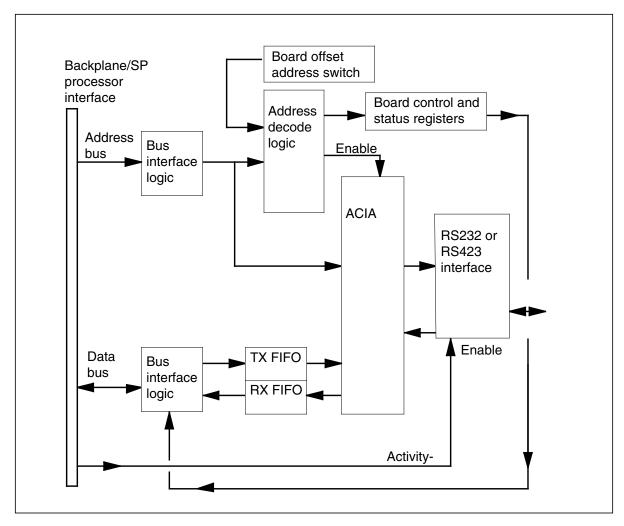

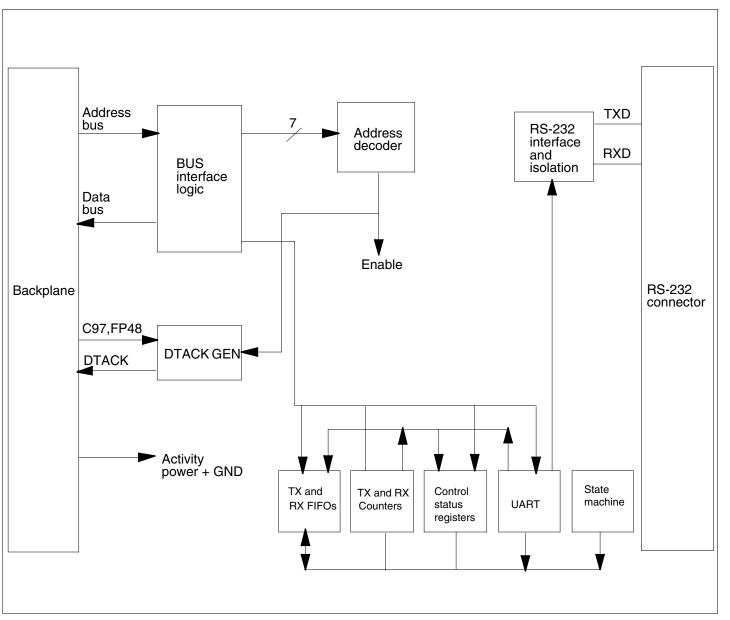

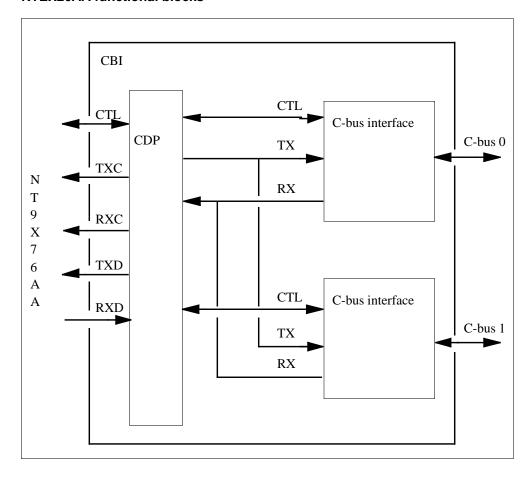

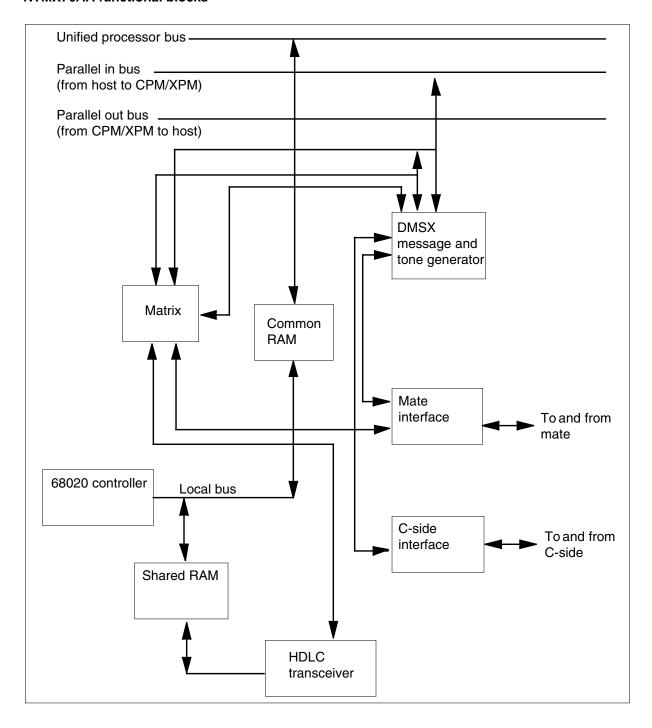

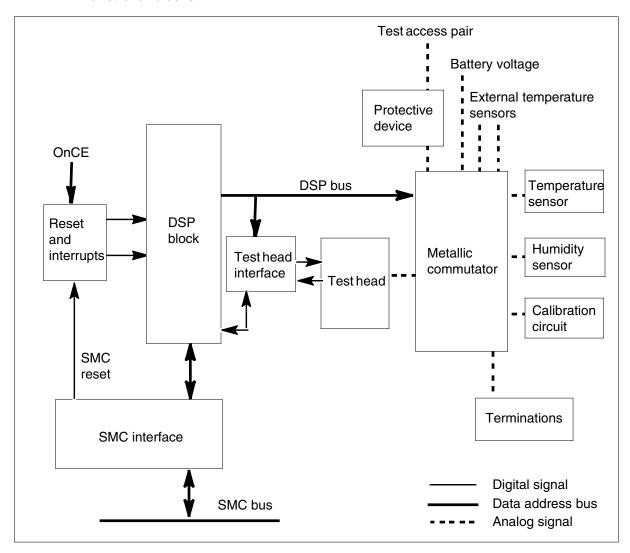

### **Functional blocks**

The NT9X76AA has the following functional blocks:

- P-bus interface

- LGP/MP interface RAM

- MP

- MP/DLP interface RAM

- DLP

- SCC

- test card

### **Processor bus interface**

The NT9X76AA has an 8-bit slave-only P-bus interface that returns the parity. The interface decodes three separate address spaces. The three address spaces follow:

- the interface port address space

- the dual-port memory address space (for the MP/LGP interface RAM)

- the PB port address space

### Link general processor/master processor interface RAM

The LGP/MP interface RAM is a 64 Kbyte array composed of two 32 Kbyte ×8 bit static RAM chips. The system switches access to the memory by a bank of 74ALS257 quad two-to-one multiplexers. The EXTG- controls these multiplexers. The multiplexers select the correct source of address bits. The multiplexers select read/write and chip select strobes. During a P-bus access, the system takes 16 bits of address directly from the P-bus. During MP access, the address forms when 13 bits of MP address merge with three bits of the page register occurs.

### **Master processor**

The MP is designed around an 8085 processor. A 63S841 1Kbyte ×4-bit PROM decodes the top 8 bits of the 16-bit address bus. This action occurs in the MP system, and provides active-low strobes for the following:

- the MP static RAM

- the MP input/output (IO) space

- the MP/DLP interface memory

- the MP/EXT interface memory

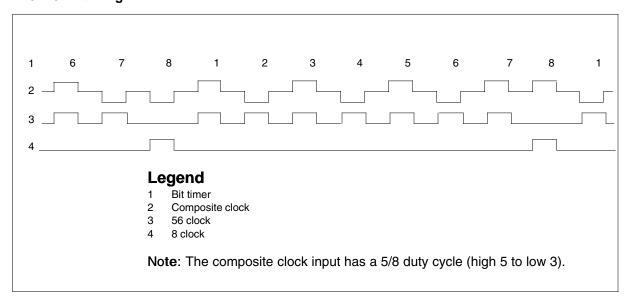

The system uses 4.915 MHz MP system clock as the clock for the 8530 SCC. Each MP cycle can incur wait states based on the address of the device. The MP watchdog timer checks the sanity of the processor. A 74HC4040 12-stage ripple counter implements this check. The MP has access to three Intel 82C54 programmable interval timers. Each timer has three channels, for a total of nine timers.

The center of the MP reset is a TL7705 supply voltage supervisor. The supervisor monitors the 5V supply and generates a reset pulse after power-up and after any transients below 4.6V.

#### MP/DLP interface RAM

The 4Kbyte × 8-bit MP/DLP interface RAM is an array of two 1423-35 4Kx4 static RAMs. A bank of 74ALS257 quad two-to-one multiplexers switches the address bus of the RAMs. A 74F257 quad two-to-one multiplexer switches the chip select and writes enable signals.

### Data link processor

A 74F139 two-to-four decoder decodes the top three bits of the 16-bit address bus. This action occurs in the DLP system. The 74F139 decodes the bits to provide four active-low strobes for the following:

- the EPROM

- the SCC

- the MP/DLP interface memory

- the test card interface

The system uses a high level on address bit 15 to enable the DLP/MP FIFO. The DLP system uses a single 12.000 MHz clock. The processor does not support wait states. The SCC, with a 4.915 MHz clock, has a 1.35 ms recovery time after each access. The DLP has two hardware interrupt lines. The two hardware interrupt lines are not in use.

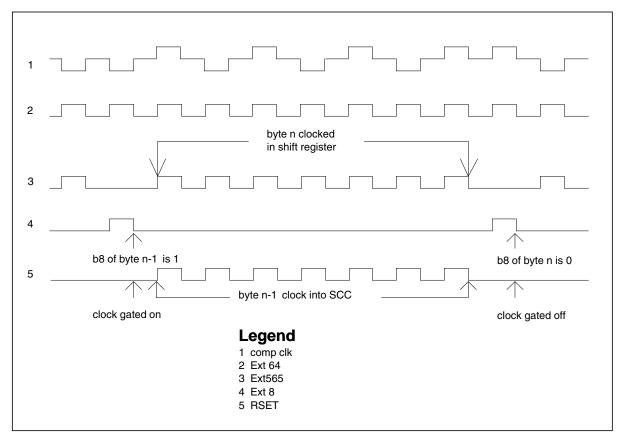

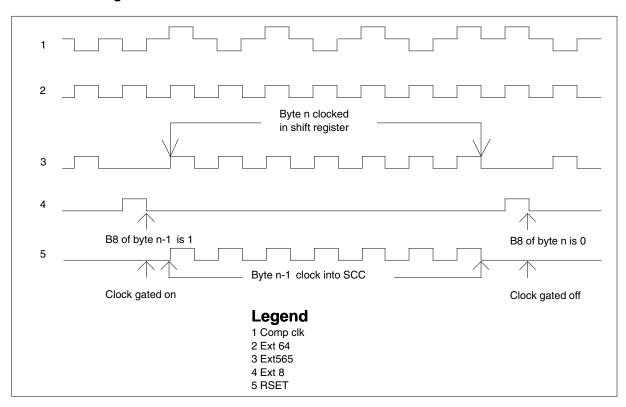

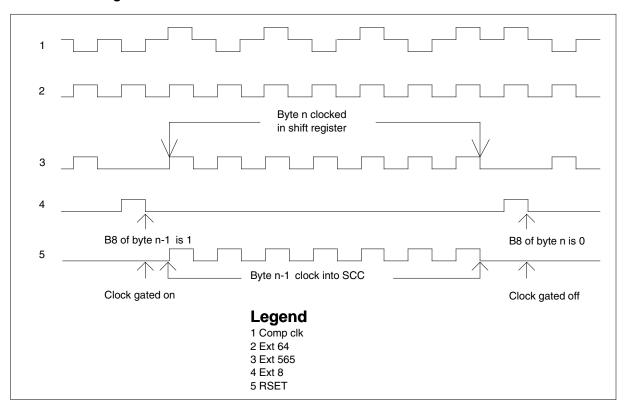

#### Serial communications controller

The 8530 SCC is a dual-channel device. Channel A receives communications. Channel B transmits communications. This process makes the receiver and transmitter seaparate. In addition to the normal mode of operation, three types of loopback are supported. These loopbacks are: ST loopback, PB loopback and line loopback. In all modes of operation, the SCC requires a clock from the PB.

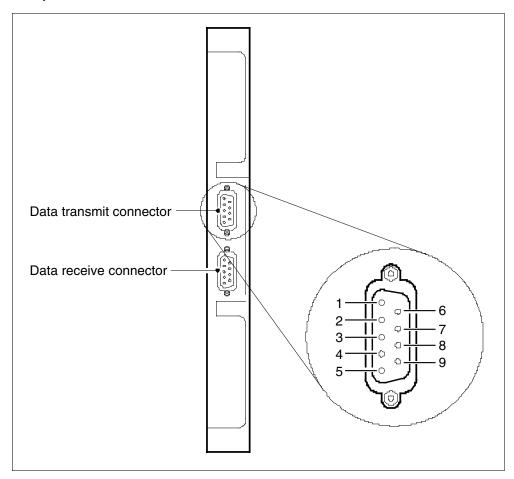

#### **Test card**

The test card contains two common synchronous asynchronous receiver transmitters (USART) and the RS232 interfaces. These elements provide terminal and host computer access to the MP or DLP firmware. Connections occur through two 16-pin sockets. Add a test card strap to the ST card when the test card is present.

There is a bank of 8 DIP switches with the Test Card to control baud rates and terminal breaks. Details on setting these switches may be found in the tables below. The baud rates for the two ports, as determined by the switches, are independently selected by two 74ALS151 eight-to-one multiplexers (U106

## NT9X76AA (continued)

and U111). Note that for firmware performance reasons, the baud rates should be set to 9600 or 19200 baud if the Test Card is not used.

### DIP switch functions for switches 1-6

| TERMINAL<br>HOST | 1 4 | 2<br>5 | 3<br>6 | RATE  |

|------------------|-----|--------|--------|-------|

|                  | ON  | ON     | ON     | 19200 |

|                  | ON  | ON     | OFF    | 9600  |

|                  | ON  | OFF    | OFF    | 4800  |

|                  | ON  | ON     | OFF    | 2400  |

|                  | OFF | ON     | ON     | 1200  |

|                  | OFF | ON     | OFF    | 600   |

|                  | OFF | OFF    | ON     | 300   |

|                  | OFF | OFF    | OFF    | 0     |

### DIP switch functions for switches 7 and 8

| SWITCH       | FUNCTION                     |  |

|--------------|------------------------------|--|

| SWITCH 7     | UNUSED                       |  |

| SWITCH 8 ON  | TERMINAL BREAK RESETS ST     |  |

| SWITCH 8 OFF | TERMINAL BREAK HAS NO EFFECT |  |

The terminal port is configured as a DCE device. Since the 8251 USART is designed for DTE use, the link DTR and DSR circuits are connected to DSR and DTR, respectively, on the 8251. The link DTR line is pulled up so as to be asserted if the terminal does not drive it. Note that no support is offered for RTS/CTS handshaking (also because the 8251 is designed for DTEs). The CTS line may simply be tied to DSR to accommodate terminals needing a CTS signal. Note that with most terminals, only circuits BA (TxD), BB (RxD), and

AB (GND) need be connected to EIA pins 2, 3, and 7, respectively. The table below shows the signals used in each port.

## RS-232C signals used in Test Card ports

| DIP16 PIN | TERM PORT U131            | HOST PORT U138 | EIA PIN |

|-----------|---------------------------|----------------|---------|

| 1, 9      | AB (GND)                  | AB (GND)       | 7       |

| 2, 10     | CC (DSR) (see note below) | CB (CTS)       | 5       |

| 3, 11     | CC (DSR)                  | CC (DSR)       | 6       |

| 4, 12     | BB (RXD)                  | BB (RXD)       | 3       |

| 5, 13     | AB (GND)                  | AB (GND)       | 7       |

| 6, 14     | BA (TXD)                  | BA (TXD)       | 2       |

| 7, 15     | CD (DTR)                  | CD (DTR)       | 20      |

| 8, 16     | NC                        | CA (RTS)       | 4       |

Note: Connect DSR to EIA pin 5 to emulate CTS and to EIA pin 8 to emulate RLSD.

## **Technical data**

## **Power requirements**

The power use of the NT9X76AA is 19W standard, and 37W maximum.

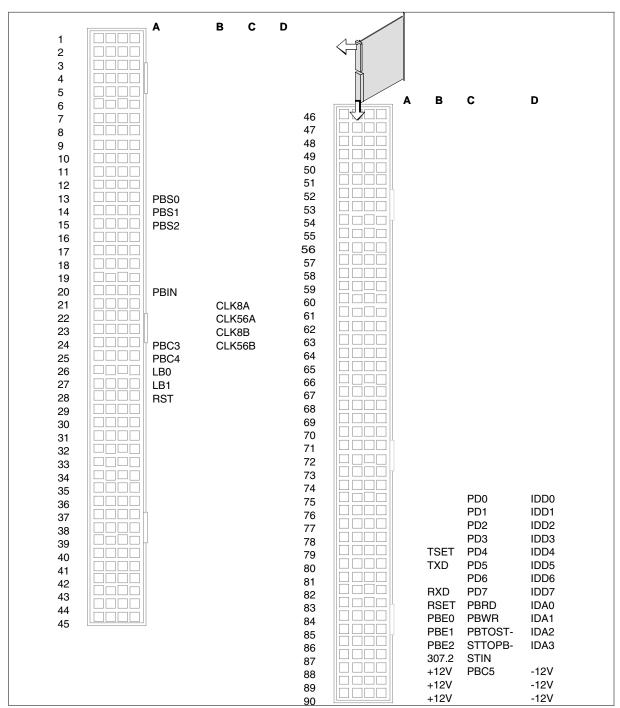

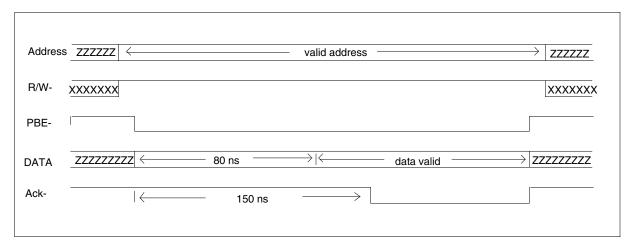

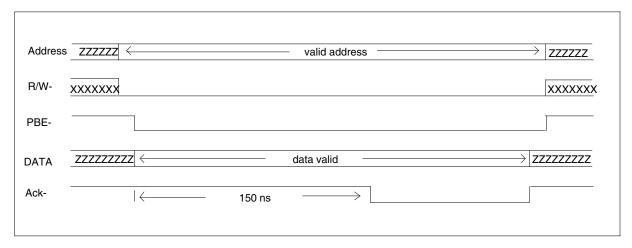

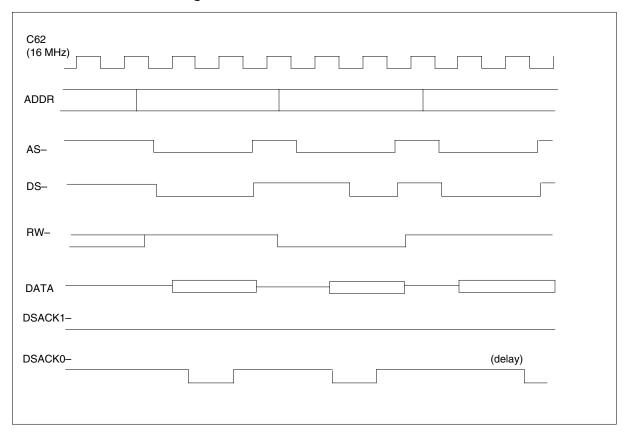

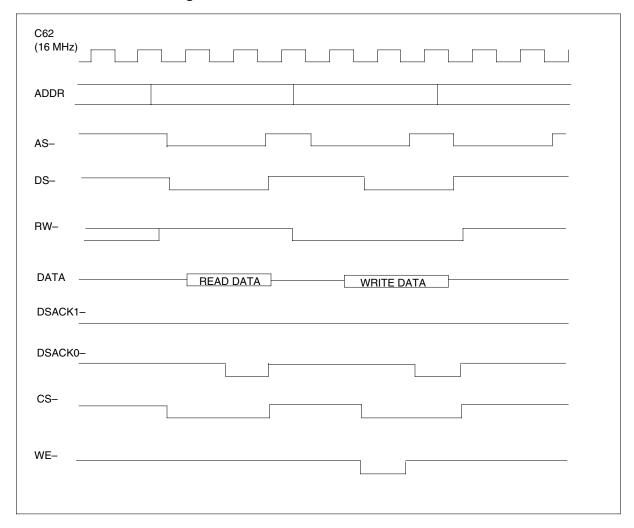

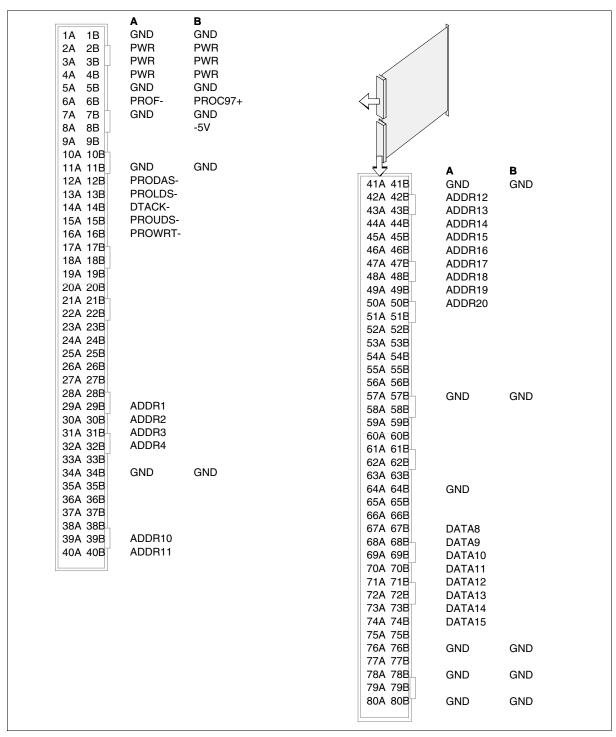

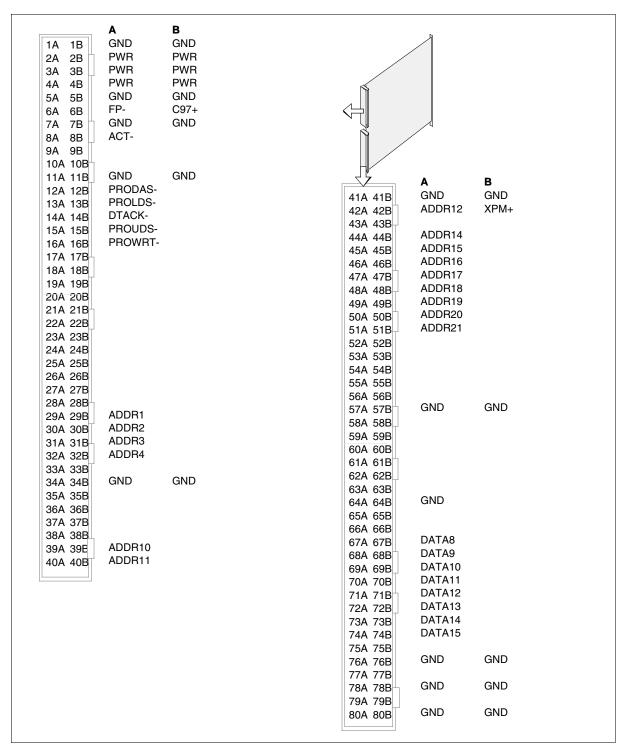

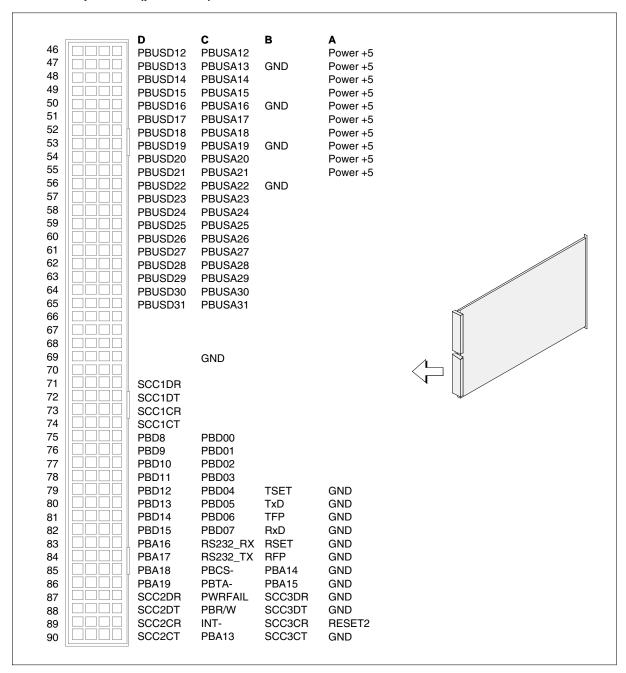

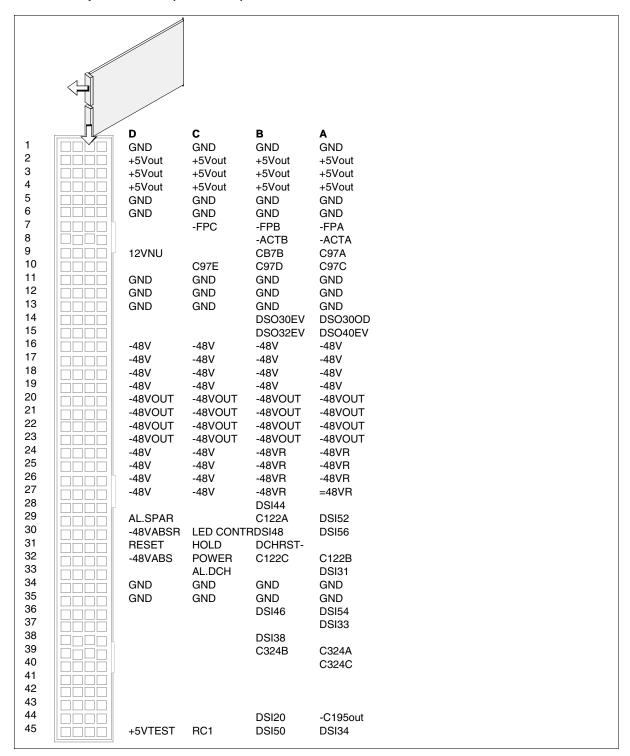

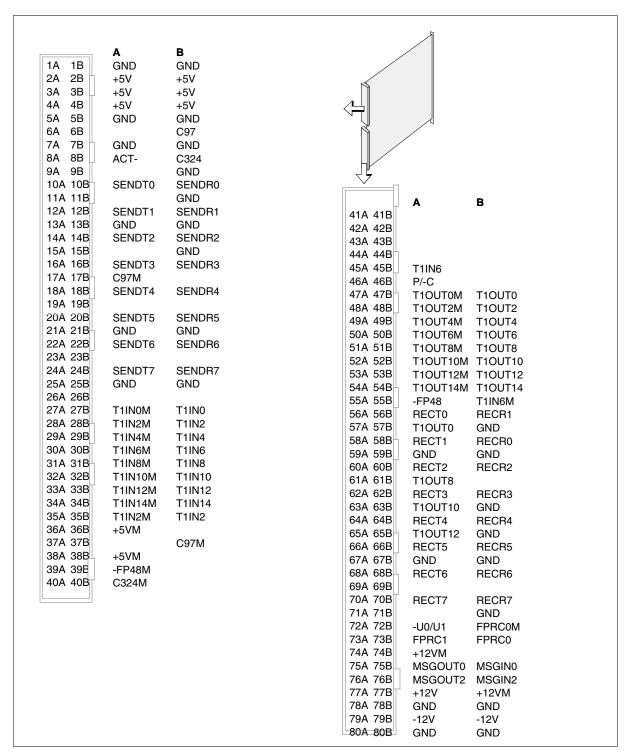

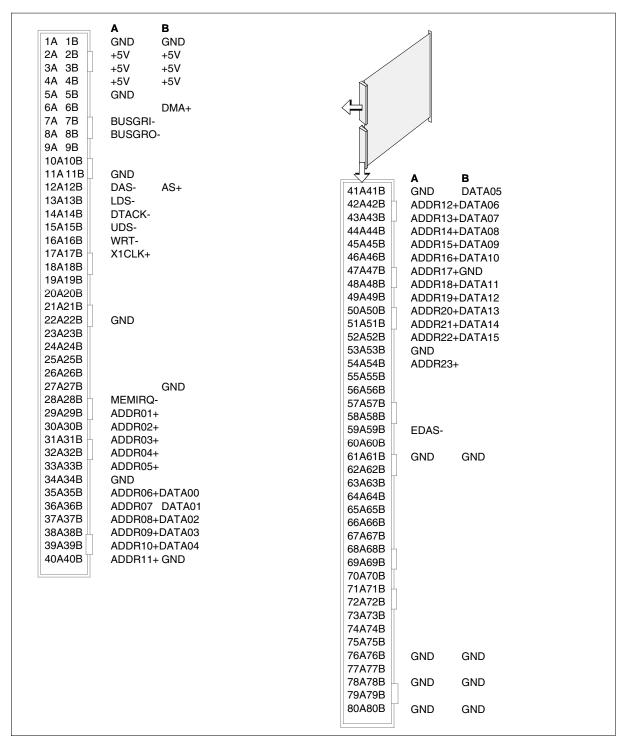

# **Signaling**

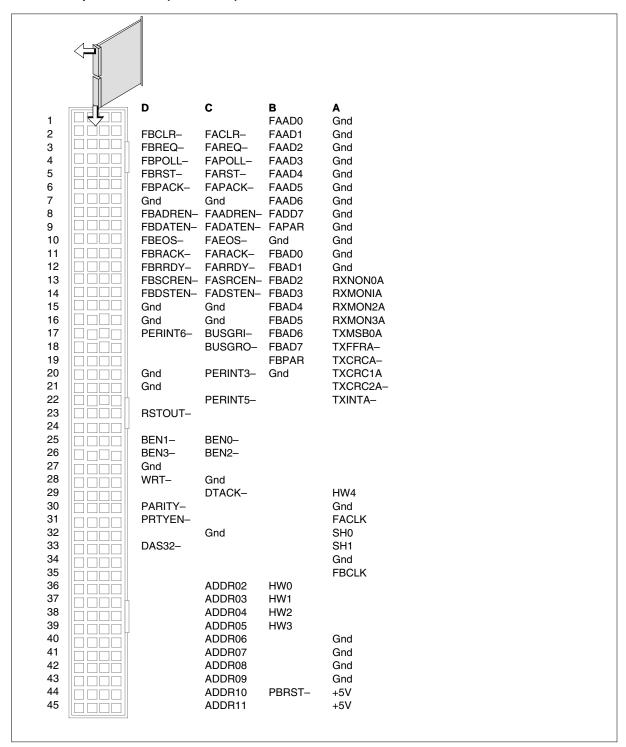

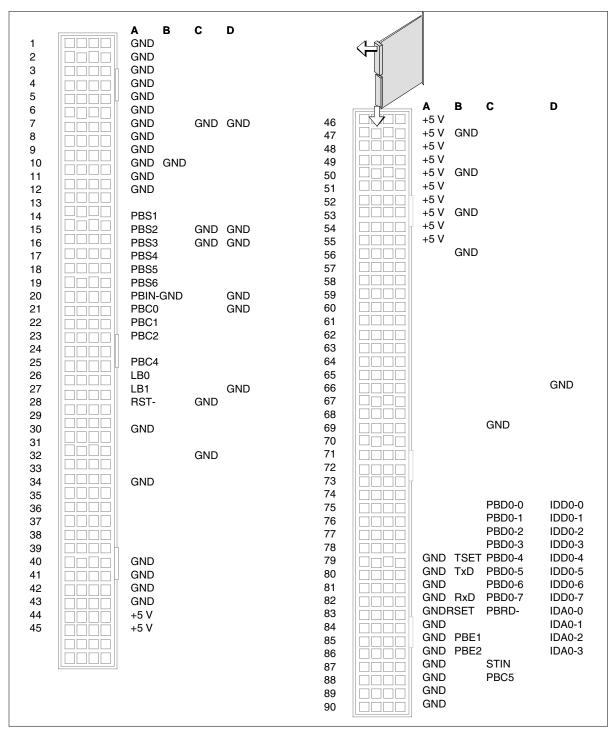

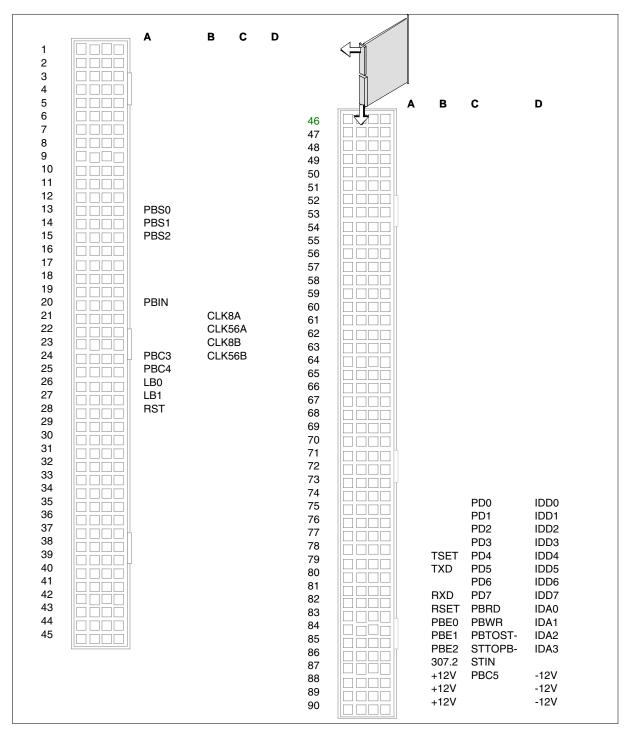

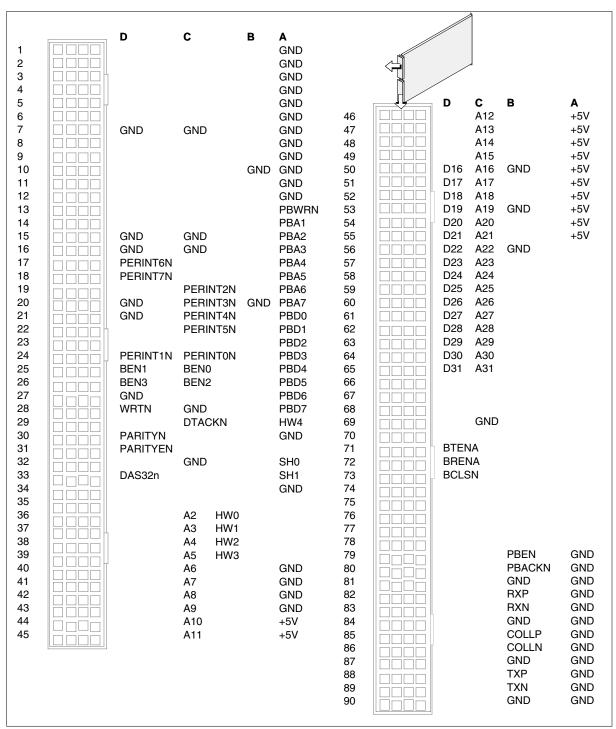

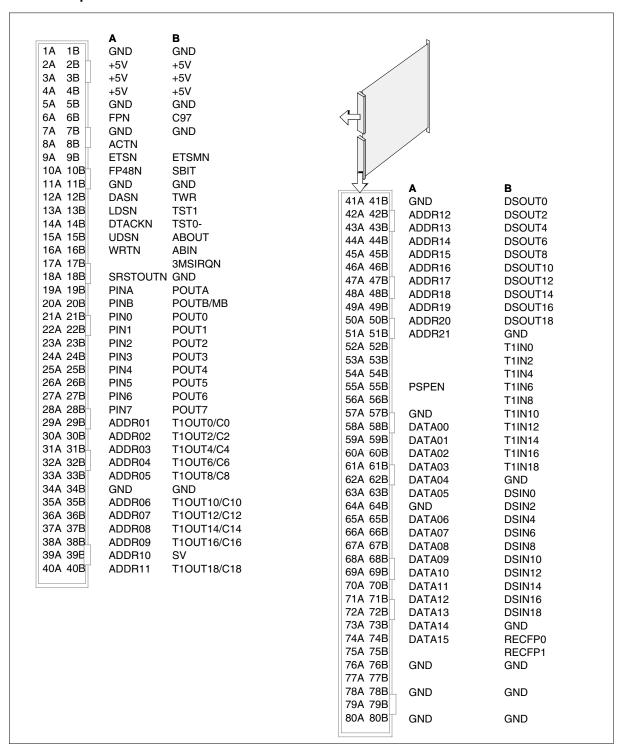

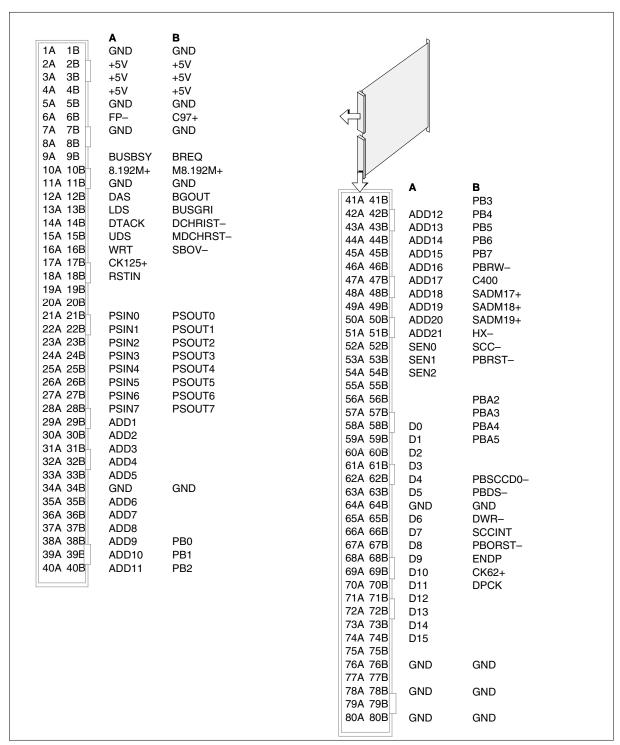

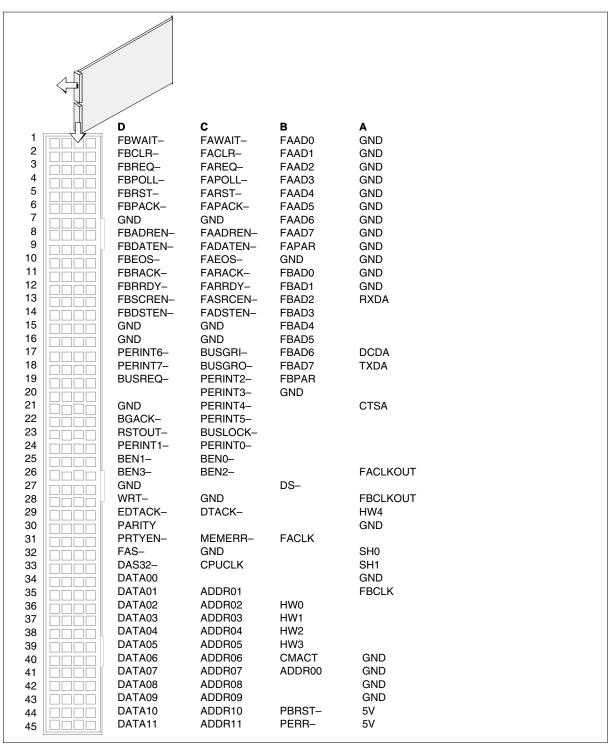

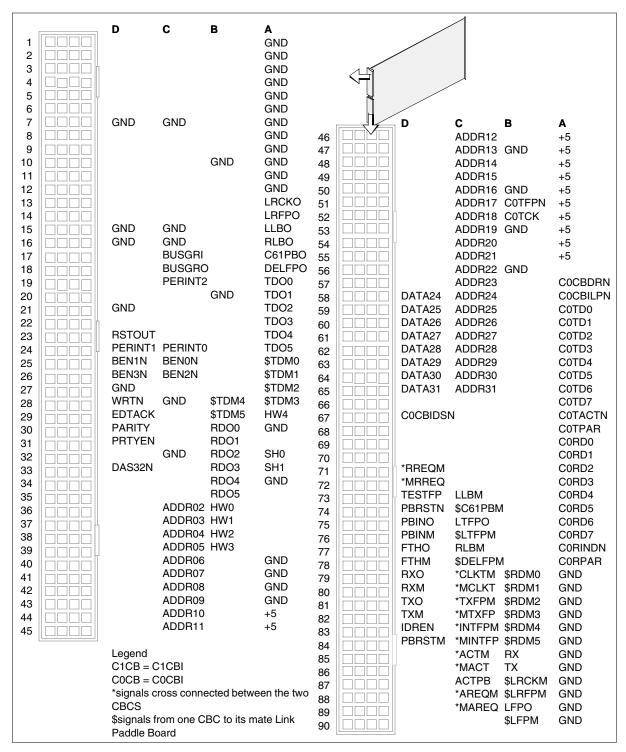

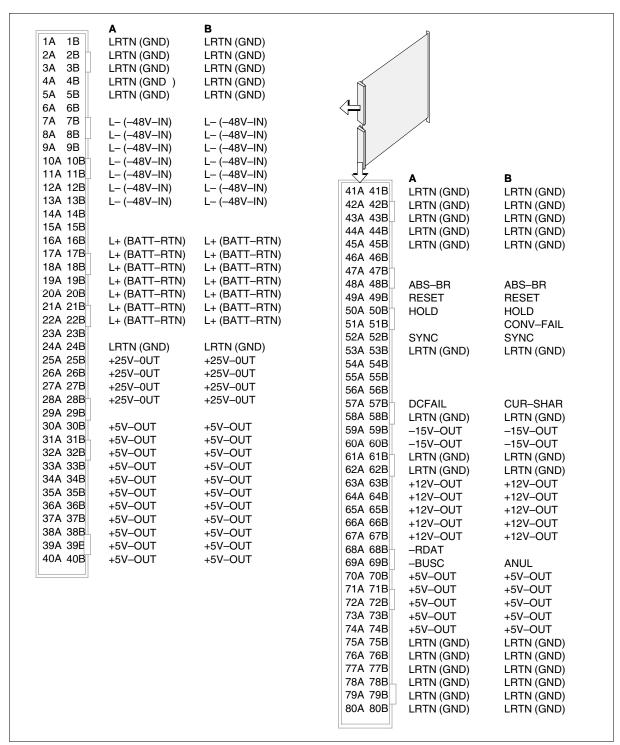

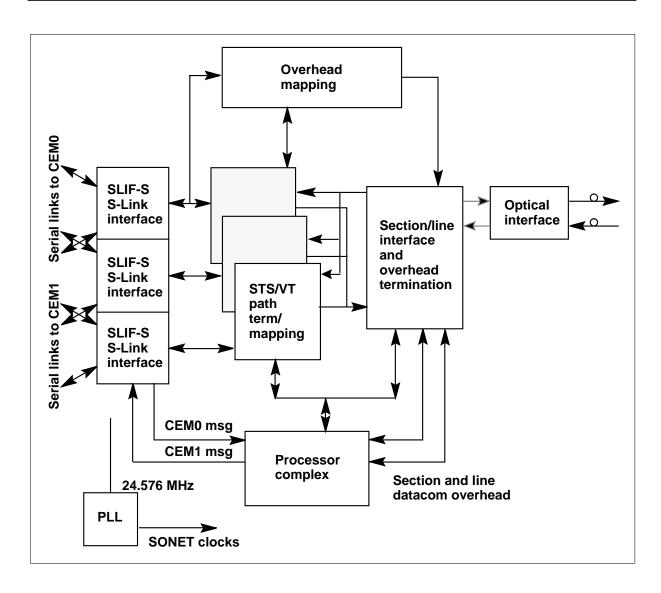

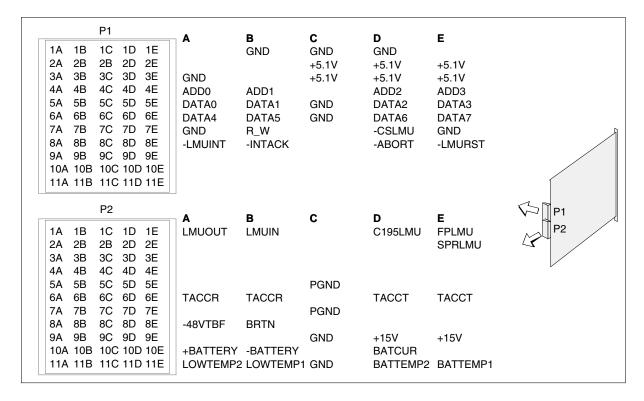

## Pin numbers

The pin numbers for NT9X76AA appear in the following figure.

# NT9X76AA pin numbers

| D C B A Gnd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |                                         |           |         |        |    |   |        |        |      |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|-----------------------------------------|-----------|---------|--------|----|---|--------|--------|------|------|

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |       |                                         |           |         |        |    |   |        |        |      |      |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |       | _                                       | _         | _       | _      | 4  |   |        |        |      |      |

| 2   Gnd   Gnd   Gnd   Gnd   Gnd   Gnd   Gnd   Gnd   46   Gnd   47   Gnd   48   ADDR13   Gnd   45   45   45   45   45   45   45   4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |       | D                                       | С         | В       |        | <  |   |        |        |      |      |

| Gnd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |       |                                         |           |         |        |    |   |        |        |      |      |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |       |                                         |           |         |        |    | ř |        |        |      |      |

| S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |       |                                         |           |         |        |    |   |        |        |      |      |

| Gind      |    |       |                                         |           |         |        |    |   | . D    | С      | В    | Δ    |

| Gnd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |       |                                         |           |         |        | 46 |   |        |        | _    |      |

| S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |       | 0 - 1                                   | 0 - 1     |         |        |    |   |        |        | Gnd  |      |

| Sind   49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |       | Gna                                     | Gna       |         |        |    |   |        |        |      |      |

| Sind      |    |       |                                         |           |         |        |    |   |        |        |      |      |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |       |                                         |           | Cnd     |        |    |   |        |        | Gnd  |      |

| 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |       |                                         |           | Gna     |        |    |   |        |        |      |      |

| 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |       |                                         |           |         |        |    |   |        |        |      |      |

| 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |       |                                         |           |         |        |    |   |        | ADDR19 | Gnd  | +5V  |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |       |                                         |           |         |        |    |   | T      | ADDR20 |      | +5V  |

| Since   Continue   C   |    |       | Gnd                                     | Gnd       |         |        |    |   |        | ADDR21 |      | +5V  |

| 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |       |                                         |           |         |        |    |   |        | ADDR22 | Gnd  |      |

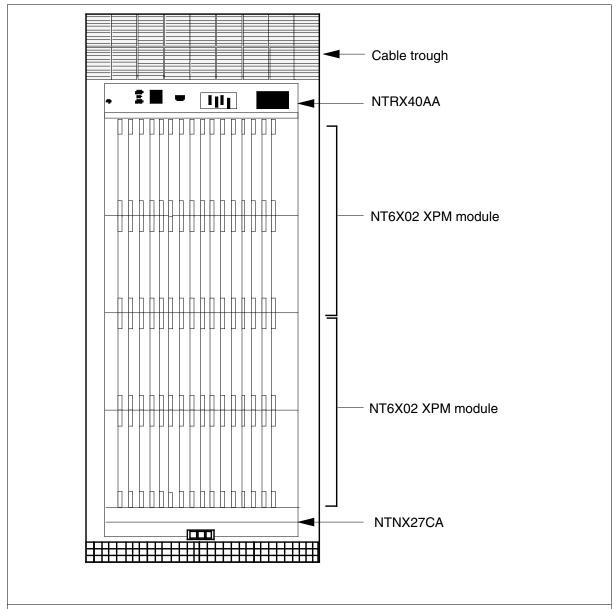

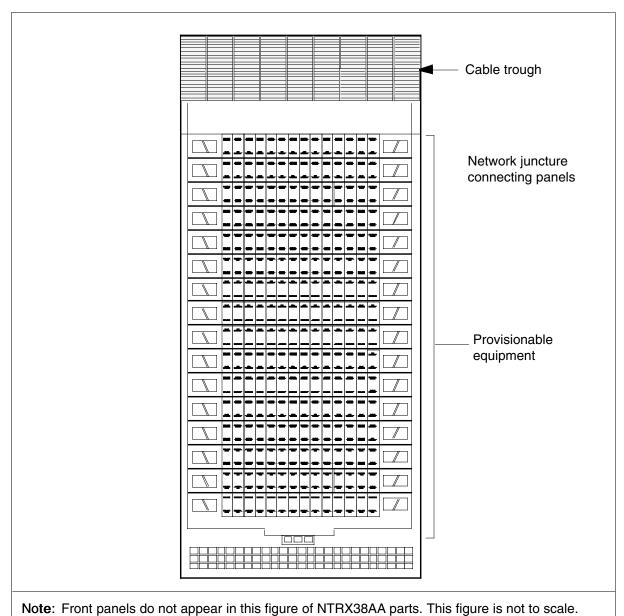

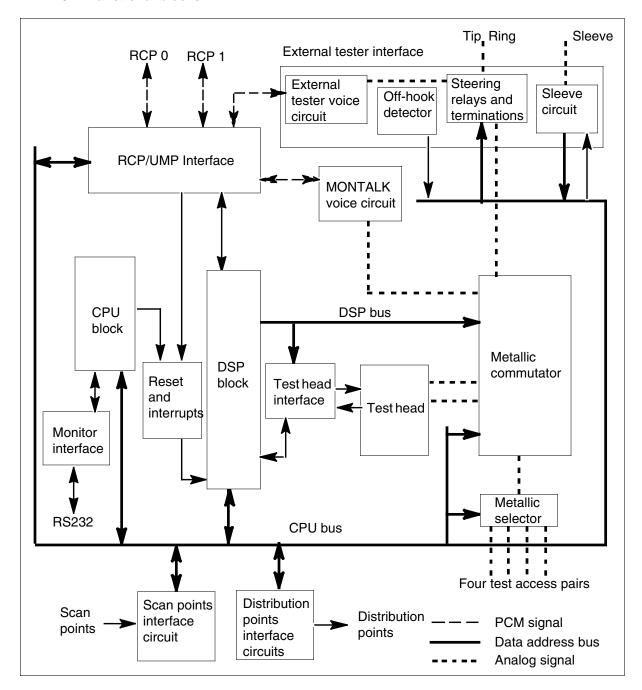

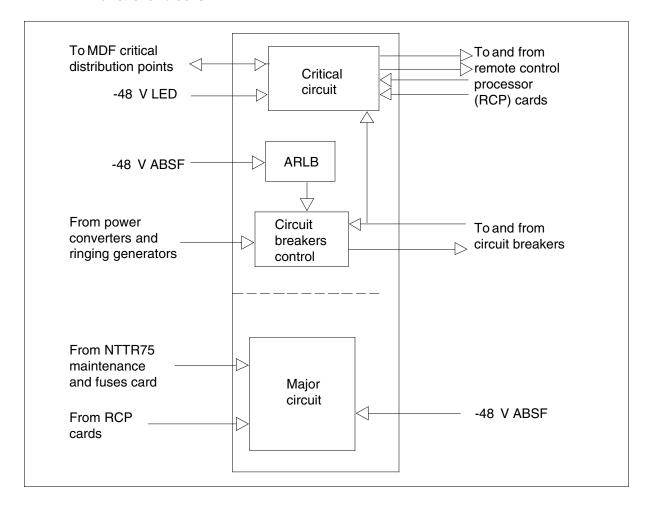

| 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |       | GIIG                                    |           |         |        |    |   |        | ADDR23 |      |      |