# **Wide Bus Applications Using Parallel BLVDS SerDes Devices**

National Semiconductor Application Note 1238 May 2002

Currently, BLVDS SerDes devices from National Semiconductor are available in 10-bit and 16-bit configurations. In cases where there are more parallel bits to transmit than a single SerDes can handle, multiple SerDes pairs can be used in parallel to perform the task provided certain constraints are met. The problem is clock to data skew. Not the skew between a deserializer's recovered clock (RCLK) and it's recovered data, but rather, between the RCLK of one deserializer and the data recovered by a second deserializer operating in parallel. For each SerDes pair the phase between the RCLK and the recovered data is relatively constant, but any difference in delay from one serial stream to another will result in skew between the RCLKs of the deserializers and hence the data of one deserializer and the RCLK of another. Since the client receive device must ultimately use only 1 RCLK, skew between the serial streams will affect the setup and hold times of the parallel data presented to it.

This application note will show how to use the datasheet parameters t<sub>SD</sub> (Serializer Delay) and t<sub>DD</sub> (Deserializer Delay) to determine the timing constraints at the client receiver parallel interface when using SerDes in parallel.

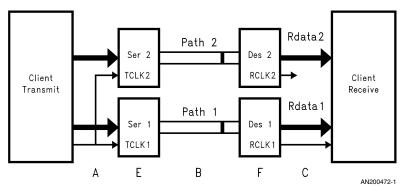

FIGURE 1. Parallel Serializers and Deserializers

## SOURCES OF PATH SKEW

First let's look at the sources of phase offset (skew) in the paths. The diagram in Figure 1 shows two SerDes being used in parallel to transmit data from the client transmit device to the client receive device.

- A is the flight time between TCLK1 and TCLK2 from the Client Transmit.

- **E** is the serializer delay t<sub>SD</sub>. The deserializer delay consists of a fractional number of clock cycles whose delay is proportional to the clock rate, and, a constant delay which is the result of propagation delays in the serializer.

- B is the flight time from serializer 2 to deserializer 2 or from serializer 1 to deserializer 1. This may be over PCB traces or through cables.

- F is the deserializer delay t<sub>DD</sub>. The deserializer delay consists of a fractional number of clock cycles whose delay is proportional to the clock rate, and, a constant delay which is the result of propagation delays in the deserializer.

- C is the RCLK flight time from Deserializer 2 or Deserializer 1 to the client receive.

In this example the RCLK from deserializer 1 (RCLK1) is used to clock all of the recovered data from both deserializers into the client device. The recovered clock from deserializer two (RCLK2) is not connected. Since the recovered data (Rdata2) from deserializer 2 is in phase with RCLK2, the phase difference between RCLK 1 and RCLK 2 can be used to determine the timing constraints between data from deserializer 2 and the RCLK from deserializer 1.

The total time for data passing through path 1 is the sum of the flight times of PCB traces and other interconnections, and the delays of the serializer and deserializer.

Path

$$1 = A_1 + B_1 + C_1 + E_1 + F_1$$

The total time for data through path 2 is the sum of the flight times and the delays through those devices.

Path

$$2 = A_2 + B_2 + C_2 + E_2 + F_2$$

So the phase difference  $(\Delta\phi)$  at the client receive is the difference of the overall delays in path 1 and path 2.

$$\Delta \phi = (A_1 + B_1 + C_1 + E_1 + F_1) - (A_2 + B_2 + C_2 + E_2 + F_2)$$

With careful PCB layout, the flight times within the two paths can be made so that  $A_1 = A_2$ ,  $B_1 = B_2$ , and  $C_1 = C_2$  now the phase difference contributed by these segments will be negligible and any phase difference between the paths can be attributed solely to the serializer and deserializer delays  $t_{SD}$

If  $(A_1 + B_1 + C_1) = (A_2 + B_2 + C_2)$

and  $t_{DD}$  (E + F).

$$\Delta \phi = (E_1 + F_1) - (E_2 + F_2)$$

$\Delta \phi = (t_{SD1} + t_{DD1}) - (t_{SD2} + t_{DD2})$

### **DETERMINING THE WORST CASE SKEW**

The worst case phase difference will occur when the minimum delays are experienced in the serializer and deserializer in one path, the MIN path, and the maximum delays are experienced in the serializer and deserializer in the other

path, the MAX path. These worst case delays are specified by  $t_{\text{SDmin}}$  and  $t_{\text{SDmax}}$  for the serializers and by  $t_{\text{DDmin}}$  and  $t_{\text{DDmax}}$  for the deserializers.

$$\Delta \phi = (t_{\text{SDmax}} + t_{\text{DDmax}}) - (t_{\text{SDmin}} + t_{\text{DDmin}})$$

The maximum skew between serial streams in an otherwise skew controlled design can be determined using the maximum and minimum values of the Serializer Delay and Deserializer Delay parameters.

In Figure 1 RCLK1 (the recovered clock from deserializer 1) is selected as the reference clock for the client receive

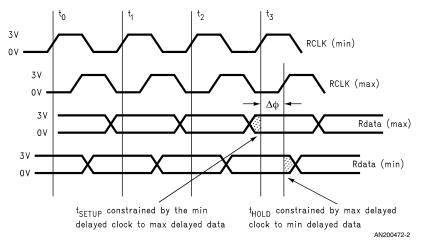

device. All data presented to the client receive device is referenced to RCLK1. Assume that Path 1 is the MIN path and has the SerDes pair with the minimum delay and that Path 2 is the MAX path; its SerDes pair has the maximum delay. This means that RCLK2 and Rdata2 will trail RCLK1 by  $\Delta \phi$ . The setup time for Rdata2 will be degraded by as much as  $\Delta \phi$ . See *Figure 2*.

FIGURE 2. RCLK and Rdata Timing

The assumption that Path 1 is the MIN path and Path 2 is the MAX path could be wrong however. In fact, it could be that Path 1 is the MAX Path and Path 2 is the MIN path in which case RCLK1 will trail RCLK2 by  $\Delta \phi$ . Now it is the hold time for Rdata2 that could be degraded by as much as  $\Delta \phi$ . (Figure 2).

To be sure that either case is accounted for, both conditions must be considered. See *Figure 2*. If the MAX path is chosen as the reference then the clock and data from the MIN path will lead the clock and data from the MAX path by  $\Delta \varphi$ . The hold parameter of the MIN path data will be degraded by  $\Delta \varphi$  ns.

$$t_{ROH'} = t_{ROH} - \Delta \phi$$

Conversely, if the MIN path clock is chosen as the reference, then the MAX path clock and data will trail the clock and data from the MIN path by  $\Delta \phi$ . The setup parameter of the MAX path data will be degraded by  $\Delta \phi$  ns.

$$t_{ROS'} = t_{ROS} + \Delta \phi$$

Note: Since  $t_{ROS}$  is the data valid time before the reference clock it is specified as a negative number. Therefore  $\Delta \phi$  is added to  $t_{ROS}$ .

Since the setup and hold parameters are specified in relation to the recovered clock period, it is convenient to use only the delay portion of the Serializer Delay and Deserializer Delay parameters. Both  $t_{\rm SD}$  and  $t_{\rm DD}$  are specified as a fractional number of clock cycles (xt<sub>CP</sub> and yt<sub>CP</sub>) plus a delay value (t<sub>S</sub> and t<sub>D</sub>).

$$t_{SDmin} = xt_{CP} + t_{Smin}, t_{SDmax} = xt_{CP} + t_{Smax}$$

$$t_{DDmin} = yt_{CP} + t_{Dmin}, t_{DDmax} = yt_{CP} + t_{Dmax}$$

So

$$\Delta \varphi = \left[ (xt_{CP} + t_{Smax}) + (yt_{CP} + t_{Dmax}) \right] - \left[ (xt_{CP} + t_{Smin}) + yt_{CP} + t_{Dmin}) \right]$$

Since the fractional clock cycle portion of the specs are proportional to the operating frequency they will be the same

for all devices of that type regardless of the operating frequency. This means that part of the parameter value can be eliminated from the skew calculation. Rewriting the equation for the overall phase difference and substituting for E and F, we can see that the overall difference in phase will be due to the difference in delays through the serializers plus the difference in delays through the deserializers.

$$\Delta \phi = (E_1 + F_1) - (E_2 + F_2)$$

$$\Delta \phi = (\mathsf{E}_1 - \mathsf{E}_2) + (\mathsf{F}_1 - \mathsf{F}_2)$$

$$\Delta \phi = (t_{SD1} - t_{SD2}) + (t_{DD1} - t_{DD2})$$

$$\Delta \phi = (t_{SDmax} - t_{SDmin}) + (t_{DDmax} - t_{DDmin})$$

$$\Delta \varphi = \left[ \left( xt_{CP} + t_{Smax} \right) - \left[ \left( xt_{CP} + t_{Smin} \right) \right] + \left[ \left( yt_{CP} + t_{Dmin} \right) - \left( yt_{CP} + t_{Dmin} \right) \right]$$

Since

$$xt_{CP1} = xt_{CP2}$$

and  $yt_{CP1} = yt_{CP2}$

$$\Delta \phi = \left(t_{Smax} - t_{Smin}\right) + \left(t_{Dmax} - t_{Dmin}\right)$$

So the maximum timing inpact on any number of serial paths can be calculated as follows:

$$t_{ROH'} = t_{ROH} - \Delta \phi = t_{ROH} - [(t_{Smax} - t_{Smin}) + (t_{Dmax} - t_{Dmin})]$$

$t_{ROS'} = t_{ROS} + \Delta \phi = t_{ROS} + [(t_{Smax} - t_{Smin}) + (t_{Dmax} - t_{Dmin})]$  *Table 1* summarizes the setup and hold time calculations for the 10-bit SerDes products at various frequencies.

TABLE 1. Maximum Phase Difference and the Impact on Deserializer Output Timing.

| Serializers | t <sub>SD</sub><br>Range<br>t <sub>SMIN</sub> /t <sub>SMAX</sub> | Deserializers | t <sub>DD</sub><br>Range<br>t <sub>DMIN</sub> /t <sub>DMAX</sub> | Δφ | 16 MHz<br>62.5 ns | 30 MHz<br>33.33 ns | 40 MHz<br>25 ns | 66 MHz<br>15.15 ns |

|-------------|------------------------------------------------------------------|---------------|------------------------------------------------------------------|----|-------------------|--------------------|-----------------|--------------------|

| DS92LV1021  | 0/5                                                              | DS92LV1212A   | 1.25/6.25                                                        | 10 | 15                | 2.12               | 0.0             | N/A                |

| DS92LV1023  | 1/3                                                              | DS92LV1224    | 1.25/6.25                                                        | 7  | N/A               | 5.12               | 3.0             | -1.24              |

|             | 1/3                                                              |               | 2.25/5.25                                                        | 5  | N/A               | 7.12               | 5.0             | N/A                |

|             | 1/3                                                              |               | 2.75/4.75                                                        | 4  | N/A               | N/A                | N/A             | 1.76               |

Note 1: Within temperature specification for t<sub>SD</sub> and t<sub>DD</sub>. Much of the variation in deserializer delay is due to variation over temperature. The basic t<sub>DD</sub> specification captures the entire range of variation. In application it is more likely that descrializers used in parallel will be located close together and therefore subject to the same temperature. The Within Temperature specification can be used under such conditions.

Example: Using the DS92LV1023 and DS92LV1224 SerDes chipsets in parallel with a 40 MHz clock.

To calculate the maximum phase difference ( $\Delta \phi$ ) between two '1023/'1224 serial links refer to the datasheet parameters  $t_{SD}$ ,  $t_{DD}$ ,  $t_{ROS}$ ,  $t_{ROH}$ , and  $t_{RCP}$ .

$$t_{SDMIN} = t_{TCP} + 1 \text{ ns}$$

$$t_{SDMAX} = t_{TCP} + 3 \text{ ns}$$

$$t_{DDMIN} = 1.75 * t_{RCP} + 1.25 \text{ ns}$$

$$t_{DDMAX} = 1.75 * t_{RCP} + 6.25 \text{ ns}$$

$$t_{BCP} = 1/40 \text{ MHz} = 25 \text{ ns}$$

$$t_{ROS} = -0.4 * t_{RCP} = -0.4 * 25 \text{ ns} = -10 \text{ ns}$$

$$t_{ROH} = 0.4 * t_{RCP} = 0.4 * 25 \text{ ns} = 10 \text{ ns}$$

Plug the values into the equations for t<sub>ROS'</sub> and t<sub>ROH'</sub>.

$$\Delta \phi = (t_{Smax} - t_{Smin}) + (t_{Dmax} - t_{Dmin})$$

$$= (3 - 1) + (6.25 - 1.25) = 7 \text{ ns}$$

$$t_{BOH'} = t_{BOH} - \Delta \phi = 10 - 7 = 3 \text{ ns}$$

$$t_{ROS'} = t_{ROS} + \Delta \phi = (-10) + 7 = -3 \text{ ns}$$

Therefore if the Client Receive ASIC supports a input set/ hold of -3/+3 ns, then the timing is validated.

If the assumption that the SerDes pairs will all be at the same temperature is valid, then the Within Temperature specifications can be used to get wider setup and hold numbers.

$$t_{SDMIN} = t_{TCP} + 1 \text{ ns}$$

$$t_{SDMAX} = t_{TCP} + 3 \text{ ns}$$

$$t_{DDMIN}$$

= 1.75 \*  $t_{TCP}$  + 2.25 ns

$$t_{DDMAX} = 1.75 * t_{TCP} + 5.25 \text{ ns}$$

$$\Delta \phi = (t_{Smax} - t_{Smin}) + (t_{Dmax} - t_{Dmin})$$

$$= (3 - 1) + (5.25 - 2.25) = 5 \text{ ns}$$

$$t_{ROH'} = t_{ROH} - \Delta \phi = 10 - 5 = 5 \text{ ns}$$

$t_{ROS'} = t_{ROS} + \Delta \phi = (-10) + 5 = -5 \text{ ns}$

Therefore if the client receive device supports a input set/hold of

$$-5/+5$$

ns, then the timing is validated.

#### CONCLUSION

For any parallel arrangement of BLVDS SerDes pairs (where the flight times throughout the path have been controlled) the maximum phase difference between any deserializer output to another deserializer output will occur when the serializer and deserializer in one path both have a minimum delay while the serializer and deserializer in the other path both have the maximum delay. The parameters  $t_{SD}$  and  $t_{DD}$ specify the minimum and maximum delays for BLVDS SerDes devices. Some of the delay variation can be eliminated by using the Within Temperature specifications. Parallel arrangements are feasible and greatly depend upon the clock rate and the required set/hold time at the client receive device. In practice clock rates up to 50-60 MHz may be supported depending upon the system timing.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Europe

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466

Email: ap.support@nsc.com

**National Semiconductor** Tel: 81-3-5639-7560 Fax: 81-3-5639-7507