Whether or not an op amp circuit is capable of driving a capacitive load successfully, depends on several factors:

- $\bullet$  Op amp internal architecture (e.g.  $R_{\mbox{\tiny OUT}},$  phase margin, compensation, etc.)

- · Closed loop gain and output loading

- Load capacitance value

Driving a capacitor also entails the op amp's output current capability since changing the voltage across a capacitor requires an adequate supply of current from the op amp. This article will present a lab method to measure amplifier stability under closed loop condition. In addition, a new op amp architecture will be presented that would ease this class of applications by using an internal mechanism to improve stability.

## **Closed Loop Phase Margin Measurement**

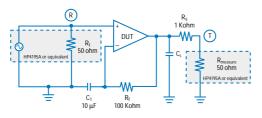

One of the internal op amp parameters which effects cap load drive performance is  $R_{\rm OUT}$ , output impedance. In fact, an ideal op amp with zero output impedance will be able to drive "any" capacitance with no phase margin (PM) degradation. However, in reality, for almost all cases,  $R_{\rm OUT}$  cannot be ignored. By using a network analyzer (HP4195A or equivalent) and the circuit shown in *Fig. 1*, it is possible to measure closed loop performance under capacitive loading:

Fig.1: Circuit To Measure Phase Margin Under Capacitive Loading

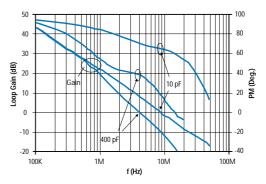

The DUT (device under test) will operate under closed loop DC and open loop AC conditions. Therefore, the measured results will be a true representation of loop gain including the effect of C<sub>L</sub>. The resultant T/R measurement (magnitude and phase) will aid in determining the PM for a given C<sub>L</sub>. One such plot done for LM8272, unlimited capacitance load drive op amp, is shown in *Fig. 2*:

Fig.2: LM8272 Loop Gain Vs. Frequency

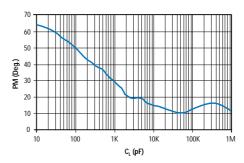

This plot has been corrected for 26 dB gain loss through  $R_s$  and the RHS axis is made to read phase margin directly. In fact, with the LM8272, the PM stays positive for any and all capacitors, as can be seen from Fig. 3 plot:

Fig.3: LM8272 Phase Margin Vs. Capacitive Loading

Advertisement

It can be shown that the PM degradation for LM8272 with the chosen capacitor values is less than what would be expected if the op amp open loop parameters (i.e. dominant pole frequency) stayed fixed. The LM8272 has specifically been designed such that a heavy capacitive load will internally shift the dominant pole frequency higher. This feature is intended to keep the phase shift around the loop to less than 180° under any capacitive load. The LM8272 architecture is explained further below.

However, it is important to remember that as in most op amps, the addition of a series isolation resistor between the output and the load improves the settling and overshoot performance.

## LM8272 Architecture

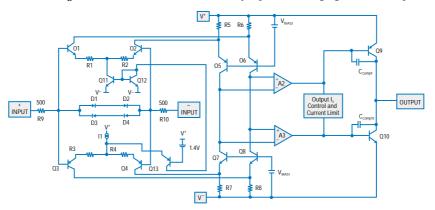

To understand how LM8272 achieves unlimited capacitive load drive capability, its internal block diagram is shown in Fig. 4:

the output transistors thus lowering the effective internal Miller capacitance. The internal pole frequency increases at the same time a low frequency pole is created at the op amp output due to the large load capacitor. In this fashion, the internal dominant pole compensation, which works by reducing the loop gain to less than 0 dB when the phase shift around the feedback loop is more than 180°, varies with the amount of capacitive load and becomes less dominant when the load capacitor has increased enough. Hence, the op amp is very stable even at high values of load capacitance resulting in the uncharacteristic feature of stability under all capacitive loads.

In conclusion, readily available op amps have always suffered from inability to drive capacitive loads and instabilities associated with that. A new op amp design, LM8272 (Dual) and LM8261 (Single) have mostly alleviated this problem to the extent that these devices can even be used as voltage buffers with heavy capacitors sitting right at their output.

Fig. 4: LM8272 Simplified Schematic

For more information, send email to: new.feedback@nsc.com

**National Semiconductor**

2900 Semiconductor Dr.

Santa Clara, CA 95052

Visit our web site at:

www.national.com

PO Box 58090

1-800-272-9959

The output stage is comprised of complementary NPN and PNP common-emitter stages to permit voltage swing to within a V<sub>ce (sat)</sub> of either supply rail. Q9 supplies the sourcing and Q10 supplies the sinking current load. Output current limiting is achieved by limiting the V<sub>ce</sub> of Q9 and Q10. The frequency compensation circuit includes Miller capacitors from collector to base of each output transistor ( $C_{comp^9}$  and  $C_{comp^{10}}$ ). At light capacitive loads, the high frequency gain of the output transistors is high, and the Miller effect increases the effective value of the capacitors thereby stabilizing the op amp. Large capacitive loads greatly decrease the high frequency gain of

## **Additional Information**

amplifiers.national.com www.national.com/pf/LM/LM8272.html www.national.com/pf/LM/LM8261.html

Visit The National Edge, our online technical journal for an archive of Application Briefs and other interesting information.

edge.national.com