# LMH6723

# 370MHz 1mA Current Feedback Op Amp

# **General Description**

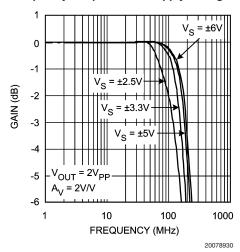

The LMH6723 provides a 260MHz small signal bandwidth at a gain of  $\pm 2V/V$  and a 600V/ $\mu$ s slew rate while consuming only 1mA from  $\pm 5V$  supplies.

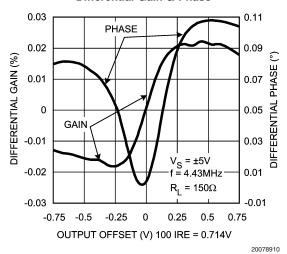

The LMH6723 supports video applications with its 0.03% and 0.11° differential gain and phase errors for NTSC and PAL video signals while driving a back terminated 75 $\Omega$  load. The LMH6723 also offers a flat gain response of 0.1dB to 100MHz. Additionally, the LMH6723 can deliver 100mA of linear output current. This level of performance, as well as a wide supply range of 4.5 to 12V, makes the LMH6723 an ideal op amp for a variety of portable applications. The LMH6723's small packages (SOIC & SOT23), low power requirement and high performance, allow the LMH6723 to serve a wide variety of portable applications.

The LMH6723 is manufactured in National's VIP  $^{\text{\tiny TM}}10$  complimentary bipolar process.

#### **Features**

- Large signal bandwidth and slew rate 100% tested

- 370MHz bandwidth ( $A_V = 1$ ,  $V_{OUT} = 0.5V_{PP}$ )

- 260MHz  $(A_V = +2V/V, V_{OUT} = 0.5V_{PP})$  -3dB BW

- 1mA supply current

- 110mA linear output current

- 0.03%, 0.11° differential gain, phase

- .1dB gain flatness to 100MHz

- Fast slew rate: 600V/µs

- Unity gain stable

- Single supply range of 4.5 to 12V

- Improved replacement for CLC450, CLC452

# **Applications**

- Line driver

- Portable video

- A/D driver

- Portable DVD

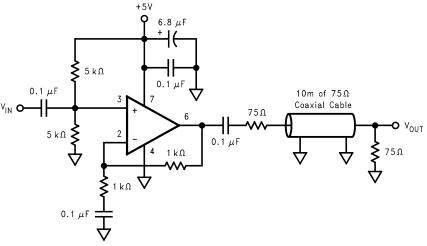

# **Typical Application**

Single Supply Cable Driver

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

±6.75V  $V_{CC}$ (Note 3)  $I_{OUT}$ Common Mode Input Voltage  $\pm V_{CC}$ Maximum Junction Temperature +150°C Storage Temperature Range -65°C to +150°C Lead Temperature (soldering 10 sec) +300°C ESD Tolerance(Note 4)

# **Operating Ratings** (Note 3)

Thermal Resistance

Human Body Model

Machine Model (Note 4)

Package  $(\theta_{\mathsf{JA}})$ 8-Pin SOIC 166°C/W 5-Pin SOT23 230°C/W Operating Temperature -40°C to +85°C 4.5V to 12V Nominal Supply Voltage

2000V

200V

## ±5V Electrical Characteristics

Unless specified,  $A_V$  = +2,  $R_F$  = 1200 $\Omega$ ,  $R_L$  = 100 $\Omega$ . **Boldface** limits apply at temperature extremes. (Note 2)

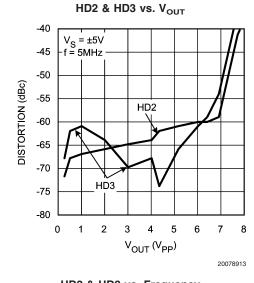

| Symbol           | Parameter                           | Conditions                      | Min | Тур  | Max  | Units   |

|------------------|-------------------------------------|---------------------------------|-----|------|------|---------|

| Frequenc         | y Domain Response                   | •                               |     | •    | •    | •       |

| SSBW             | -3dB Bandwidth Small Signal         | $V_{OUT} = 0.5V_{PP}$           |     | 260  |      | MHz     |

| LSBW             | -3dB Bandwidth Large Signal         | $V_{OUT} = 4.0V_{PP}$           | 90  | 110  |      | MHz     |

| UGBW             | -3dB Bandwidth Unity Gain           | $V_{OUT} = .2V_{PP} A_V = 1V/V$ |     | 370  |      | MHz     |

| .1dB BW          | .1dB Bandwidth                      | $V_{OUT} = 0.5V_{PP}$           |     | 100  |      | MHz     |

| DG               | Differential Gain                   | $R_L = 150\Omega, 4.43MHz$      |     | 0.03 |      | %       |

| DP               | Differential Phase                  | $R_L = 150\Omega, 4.43MHz$      |     | 0.11 |      | deg     |

| Time Don         | nain Response                       | •                               | '   | •    |      |         |

| TRS              | Rise and Fall Time                  | 4V Step                         |     | 2.5  |      | ns      |

| TSS              | Settling Time to 0.05%              | 2V Step                         |     | 30   |      | ns      |

| SR               | Slew Rate                           | 4V Step                         | 500 | 600  |      | V/µs    |

| Distortion       | and Noise Response                  |                                 |     | •    |      | '       |

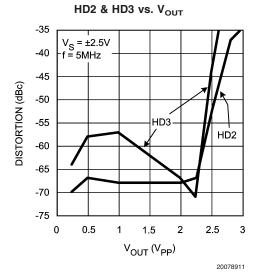

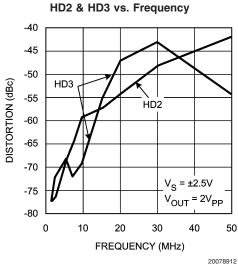

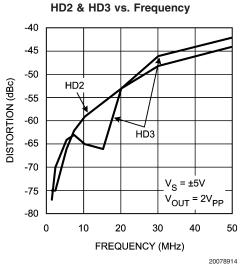

| HD2              | 2 <sup>nd</sup> Harmonic Distortion | 2V <sub>PP</sub> , 5MHz         |     | -65  |      | dBc     |

| HD3              | 3 <sup>rd</sup> Harmonic Distortion | 2V <sub>PP</sub> , 5MHz         |     | -63  |      | dBc     |

|                  | Equivalent Input Noise              |                                 |     |      |      |         |

| VN               | Non-Inverting Voltage               | >1MHz                           |     | 4.3  |      | nV/ √Hz |

| NICN             | Inverting Current                   | >1MHz                           |     | 6    |      | pA/ √Hz |

| ICN              | Non-Inverting Current               | >1MHz                           |     | 6    |      | pA/ √Hz |

| Static, DC       | Performance                         |                                 |     | •    | •    | '       |

| V <sub>IO</sub>  | Input Offset Voltage                |                                 |     | 1    | ±3   | mV      |

|                  |                                     |                                 |     |      | ±3.7 |         |

| I <sub>BN</sub>  | Input Bias Current                  | Non-Inverting                   |     | -2   | ±4   | μΑ      |

|                  |                                     |                                 |     |      | ±5   |         |

| I <sub>BI</sub>  | Input Bias Current                  | Inverting                       |     | 0.4  | ±4   | μΑ      |

|                  |                                     |                                 |     |      | ±5   |         |

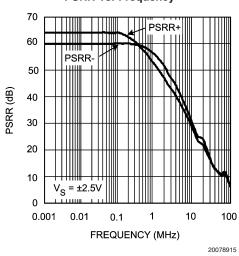

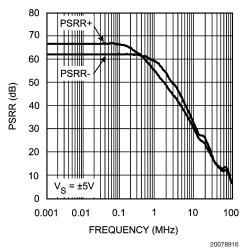

| PSRR             | Power Supply Rejection Ratio        | DC, 1V Step                     | 59  | 64   |      | dB      |

|                  |                                     |                                 | 57  |      |      |         |

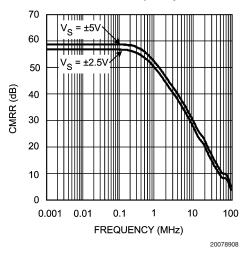

| CMRR             | Common Mode Rejection Ratio         | DC, 1V Step                     | 57  | 60   |      | dB      |

| _                |                                     |                                 | 55  |      |      |         |

| I <sub>CC</sub>  | Supply Current                      | R <sub>L</sub> = ∞              |     | 1    | 1.2  | mA      |

| 8.00             |                                     |                                 |     |      | 1.4  |         |

|                  | eous Performance                    | Tar                             |     | 100  | I    |         |

| R <sub>IN+</sub> | Input Resistance                    | Non-Inverting                   |     | 100  |      | kΩ      |

| $R_{IN-}$        | Input Resistance                    | Inverting                       |     | 500  |      | Ω       |

|                  | (Output Resistance of Input Buffer) | Non-Investing                   |     | 1.5  |      |         |

| C <sub>IN</sub>  | Input Capacitance                   | Non-Inverting                   |     | 1.5  |      | pF      |

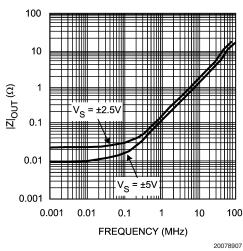

| R <sub>OUT</sub> | Output Resistance                   | Closed Loop                     |     | 0.01 |      | Ω       |

# **±5V Electrical Characteristics** (Continued)

Unless specified,  $A_V$  = +2,  $R_F$  = 1200 $\Omega$ ,  $R_L$  = 100 $\Omega$ . **Boldface** limits apply at temperature extremes. (Note 2)

| Symbol          | Parameter                  | Conditions         | Min   | Тур   | Max | Units |

|-----------------|----------------------------|--------------------|-------|-------|-----|-------|

| Vo              | Output Voltage Range       | R <sub>L</sub> = ∞ | ±4    | ±4.1  |     | V     |

|                 |                            |                    | ±3.9  |       |     |       |

| V <sub>OL</sub> | Output Voltage Range, High | $R_L = 100\Omega$  | 3.6   | 3.7   |     |       |

|                 |                            |                    | 3.5   |       |     | V     |

|                 | Output Voltage Range, Low  |                    | -3.25 | -3.45 |     | V     |

|                 |                            |                    | -3.1  |       |     |       |

| CMIR            | Input Voltage Range        | CMRR > 50dB        | ±4.0  |       |     | ٧     |

| Io              | Output Current             | Sourcing           | 95    | 110   |     |       |

|                 |                            |                    | 70    |       |     | m A   |

|                 |                            | Sinking            | -80   | 110   |     | mA    |

|                 |                            |                    | -70   |       |     |       |

# ±2.5V Electrical Characteristics

Unless otherwise specified,  $A_V = +2$ ,  $R_F = 1200\Omega$ ,  $R_L = 100\Omega$ . **Boldface** limits apply at temperature extremes. (Note 2)

| Symbol           | Parameter                           | Conditions                          | Min              | Тур  | Max  | Units   |

|------------------|-------------------------------------|-------------------------------------|------------------|------|------|---------|

| Frequenc         | y Domain Response                   | ·                                   | •                |      |      | •       |

| SSBW             | -3dB Bandwidth Small Signal         | $V_{OUT} = 0.5V_{PP}$               |                  | 210  |      | MHz     |

| LSBW             | -3dB Bandwidth Large Signal         | $V_{OUT} = 2.0V_{PP}$               | 95               | 125  |      | MHz     |

| UGBW             | -3dB Bandwidth Unity Gain           | $V_{OUT} = 0.5V_{PP}, A_{V} = 1V/V$ |                  | 290  |      | MHz     |

| .1dB BW          | .1dB Bandwidth                      | $V_{OUT} = 0.5V_{PP}$               |                  | 100  |      | MHz     |

| DG               | Differential Gain                   | $R_L = 150\Omega, 4.43MHz$          |                  | .03  |      | %       |

| DP               | Differential Phase                  | $R_L = 150\Omega, 4.43MHz$          |                  | .1   |      | deg     |

| Time Dor         | nain Response                       |                                     | •                |      |      | •       |

| TRS              | Rise and Fall Time                  | 2V Step                             |                  | 4    |      | ns      |

| SR               | Slew Rate                           | 2V Step                             | 275              | 400  |      | V/µs    |

| Distortio        | n and Noise Response                | ·                                   | •                |      |      |         |

| HD2              | 2 <sup>nd</sup> Harmonic Distortion | 2V <sub>PP</sub> , 5MHz             |                  | -67  |      | dBc     |

| HD3              | 3 <sup>rd</sup> Harmonic Distortion | 2V <sub>PP</sub> , 5MHz             |                  | -67  |      | dBc     |

|                  | Equivalent Input Noise              |                                     |                  |      |      |         |

| VN               | Non-Inverting Voltage               | >1MHz                               |                  | 4.3  |      | nV/ √Hz |

| NICN             | Inverting Current                   | >1MHz                               |                  | 6    |      | pA/ √Hz |

| ICN              | Non-Inverting Current               | >1MHz                               |                  | 6    |      | pA/ √Hz |

| Static, Do       | C Performance                       | ·                                   | •                |      |      | •       |

| V <sub>IO</sub>  | Input Offset Voltage                |                                     |                  | -0.5 | ±3   | mV      |

|                  |                                     |                                     |                  |      | ±3.4 |         |

| $I_{BN}$         | Input Bias Current                  | Non-Inverting                       |                  | -2.7 | ±4   | μΑ      |

|                  |                                     |                                     |                  |      | ±5   |         |

| I <sub>BI</sub>  | Input Bias Current                  | Inverting                           |                  | -0.7 | ±4   | μA      |

|                  |                                     |                                     |                  |      | ±5   |         |

| PSRR             | Power Supply Rejection Ratio        | DC, 0.5V Step                       | 59               | 62   |      | dB      |

| 01455            |                                     | DO 0.51/.0:                         | 57               |      |      | ļ       |

| CMRR             | Common Mode Rejection Ratio         | DC, 0.5V Step                       | 55<br><b>5</b> 3 | 59   |      | dB      |

| 1                | Supply Current                      | R <sub>1</sub> = ∞                  | 53               | .9   | 1.1  | mA      |

| I <sub>CC</sub>  | Supply Current                      | n <sub>L</sub> = ∞                  |                  | .9   | 1.3  | IIIA    |

| Miscellar        | eous Performance                    |                                     |                  |      | 1.5  |         |

| R <sub>IN+</sub> | Input Resistance                    | Non-Inverting                       |                  | 100  |      | kΩ      |

|                  | Input Resistance                    | Inverting                           |                  | 500  |      | Ω       |

| $R_{IN-}$        | (Output Resistance of Input Buffer) | Inverting                           |                  | 300  |      | 22      |

# **±2.5V Electrical Characteristics** (Continued)

Unless otherwise specified,  $A_V = +2$ ,  $R_F = 1200\Omega$ ,  $R_L = 100\Omega$ . **Boldface** limits apply at temperature extremes. (Note 2)

| Symbol           | Parameter                                             | Conditions         | Min   | Тур   | Max | Units |

|------------------|-------------------------------------------------------|--------------------|-------|-------|-----|-------|

| C <sub>IN</sub>  | Input Capacitance                                     | Non-Inverting      |       | 1.5   |     | pF    |

| R <sub>OUT</sub> | Output Resistance                                     | Closed Loop        |       | .02   |     | Ω     |

| V <sub>O</sub>   | Output Voltage Range                                  | R <sub>L</sub> = ∞ | ±1.55 | ±1.65 |     | V     |

|                  |                                                       |                    | ±1.4  |       |     |       |

| V <sub>OL</sub>  | Output Voltage Range, High  Output Voltage Range, Low | $R_L = 100\Omega$  | 1.35  | 1.45  |     |       |

|                  |                                                       |                    | 1.27  |       |     | V     |

|                  |                                                       |                    | -1.25 | -1.38 |     | V     |

|                  |                                                       |                    | -1.15 |       |     |       |

| CMIR             | Input Voltage Range                                   | CMRR > 50dB        | ±1.45 |       |     | V     |

| Io               | Output Current                                        | Sourcing           | 70    | 90    |     |       |

|                  |                                                       |                    | 60    |       |     | Л     |

|                  |                                                       | Sinking            | -30   | -60   |     | mA    |

|                  |                                                       |                    | -30   |       |     |       |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications, see the Electrical Characteristics tables.

Note 2: Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self heating where  $T_J > T_A$ . See Applications Section for information on temperature derating of this device. Min/Max ratings are based on product characterization and simulation. Individual parameters are tested as noted.

Note 3: The maximum output current (I<sub>OUT</sub>) is determined by device power dissipation limitations. See the Power Dissipation section of the Application Section for more details.

Note 4: Human body model,  $1.5k\Omega$  in series with 100pF. Machine model,  $0\Omega$  In series with 200pF.

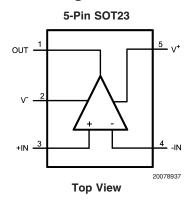

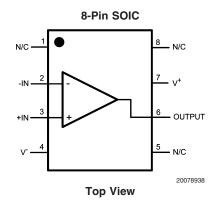

# **Connection Diagrams**

# **Ordering Information**

| Package      | Part Number | Package Marking | Transport Media          | NSC Drawing |  |

|--------------|-------------|-----------------|--------------------------|-------------|--|

| 5-Pin SOT23  | LMH6723MF   | AB1A            | 1k Units Tape and Reel   | MF05A       |  |

| 3-FIII 30123 | LMH6723MFX  | ADIA            | 3k Units Tape and Reel   |             |  |

| 8-Pin SOIC   | LMH6723MA   | LMH6723MA       | 95 Units/Rail            | M08A        |  |

| 6-FIII 30IC  | LMH6723MAX  | LIVINO723WA     | 2.5k Units Tape and Reel | IVIOOA      |  |

# **Typical Performance Characteristics**

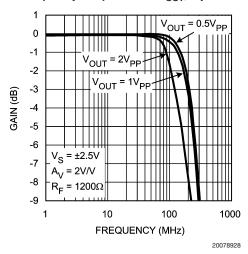

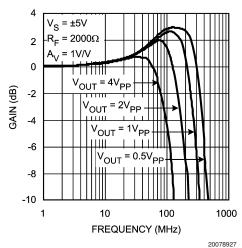

Frequency Response vs.  $V_{OUT}$ ,  $A_V = 2$

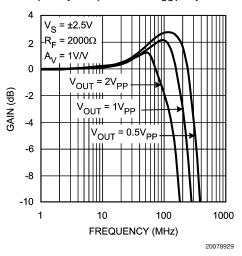

#### Frequency Response vs. $V_{OUT}$ , $A_V = 1$

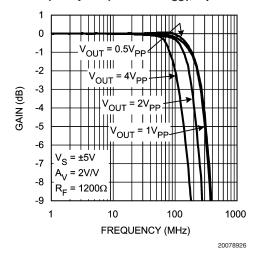

#### Large Signal Frequency Response

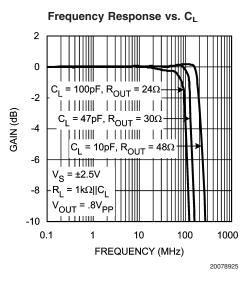

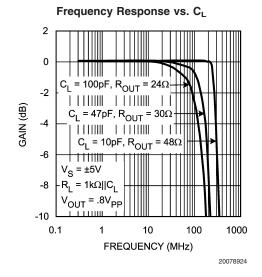

## Frequency Response vs. $V_{OUT}$ , $A_V = 2$

#### Frequency Response vs. $V_{OUT}$ , $A_V = 1$

#### Frequency Response vs. Supply Voltage

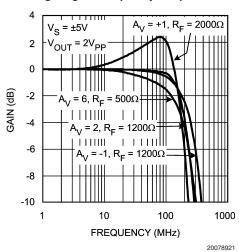

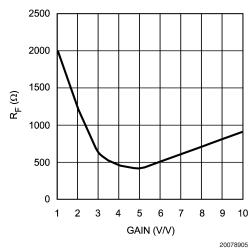

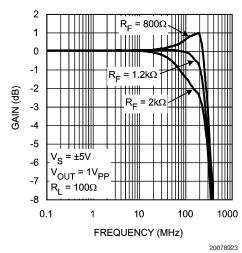

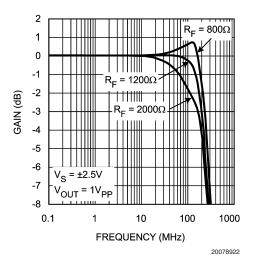

#### Frequency Response vs. R<sub>F</sub>

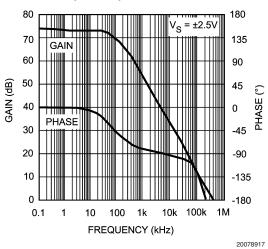

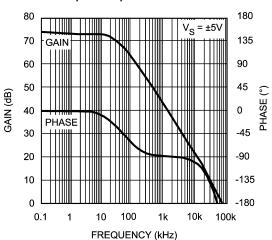

#### Open Loop Gain & Phase

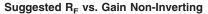

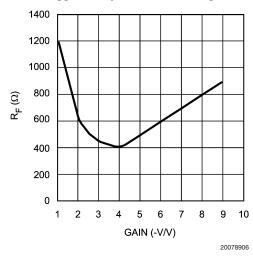

#### Suggested R<sub>F</sub> vs. Gain Inverting

#### Frequency Response vs. R<sub>F</sub>

#### Open Loop Gain & Phase

20078918

## PSRR vs. Frequency

#### **Closed Loop Output Resistance**

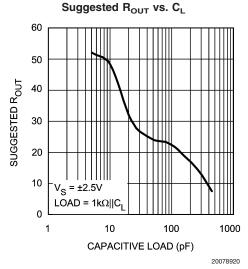

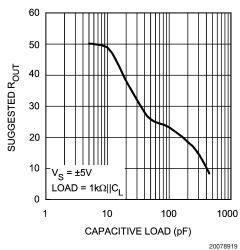

## Suggested R<sub>OUT</sub> vs. C<sub>L</sub>

#### PSRR vs. Frequency

#### CMRR vs. Frequency

#### **Differential Gain & Phase**

## **Application Section**

#### **GENERAL INFORMATION**

The LMH6723 is a high speed current feedback amplifier manufactured on National Semiconductor's VIP10™ (Vertically Integrated PNP) complimentary bipolar process. LMH6723 offers a unique combination of high speed and low quiescent supply current making it suitable for a wide range of battery powered and portable applications that require high performance. This amplifier can operate from 5V to 12V nominal supply voltages and draws only 1mA of quiescent supply current at 10V supplies (±5V typically). The LMH6723 has no internal ground reference so single or split supply configurations are both equally useful.

#### **EVALUATION BOARDS**

National Semiconductor provides the following evaluation boards as a guide for high frequency layout and as an aid in device testing and characterization. Many of the datasheet plots were measured with these boards.

| Device    | Package | Board Part # |

|-----------|---------|--------------|

| LMH6723MA | SOIC    | CLC730227    |

| LMH6723MF | SOT-23  | CLC730216    |

A free evaluation board is automatically shipped when a sample request is placed with National Semiconductor.

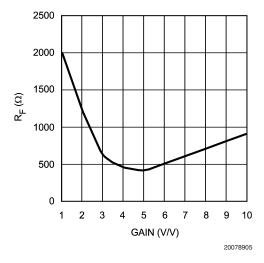

#### FEEDBACK RESISTOR SELECTION

One of the key benefits of a current feedback operational amplifier is the ability to maintain optimum frequency response independent of gain by using appropriate values for the feedback resistor (R $_{\rm F}$ ). The Electrical Characteristics and Typical Performance plots specify an R $_{\rm F}$  of 1200 $\Omega$ , a gain of +2V/V and ±5V or ±2.5V power supplies (unless otherwise specified). Generally, lowering R $_{\rm F}$  from it's recommended value will peak the frequency response and extend the bandwidth while increasing the value of R $_{\rm F}$  will cause the frequency response to roll off faster. Reducing the value of R $_{\rm F}$  too far below it's recommended value will cause overshoot, ringing and, eventually, oscillation.

FIGURE 1. Frequency Response vs. R<sub>F</sub>

The plot labeled "Frequency Response vs. R<sub>F</sub>" shows the LMH6723's frequency response as  $R_F$  is varied ( $R_L = 100\Omega$ ,  $A_V = +2$ ). This plot shows that an  $R_F$  of  $800\Omega$  results in peaking. An  $R_F$  of 1200 $\Omega$  gives near maximal bandwidth and gain flatness with good stability. Since all applications are slightly different it is worth some experimentation to find the optimal R<sub>F</sub> for a given circuit. In general a value of R<sub>F</sub> that produces ~.1dB of peaking is the best compromise between stability and maximal bandwidth. Note that it is not possible to use a current feedback amplifier with the output shorted directly to the inverting input. The buffer configuration of the LMH6723 requires a 2000 $\Omega$  feedback resistor for stable operation. For other gains see the charts "R<sub>F</sub> vs. Non Inverting Gain" and "R<sub>F</sub> vs. Inverting Gain". These charts provide a good place to start when selecting the best feedback resistor value for a variety of gain settings.

For more information see Application Note OA-13 which describes the relationship between  $R_{\rm F}$  and closed-loop frequency response for current feedback operational amplifiers.

# **Application Section** (Continued)

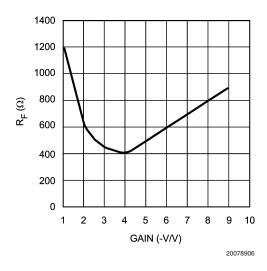

The value for the inverting input impedance for the LMH6723 is approximately  $500\Omega$ . The LMH6723 is designed for optimum performance at gains of +1 to +5V/V and -1 to -4V/V. Higher gain configurations are still useful, however, the bandwidth will fall as gain is increased, much like a typical voltage feedback amplifier.

FIGURE 2. RF vs. Non-Inverting Gain

Both plots show the value of  $R_{F}$  versus gain. A higher  $R_{F}$  is required at higher gains to keep  $R_{G}$  from decreasing too far below the input impedance of the inverting input. This limitation applies to both inverting and non-inverting configurations. For the LMH6723 the input resistance of the inverting input is approximately  $500\Omega$  and  $100\Omega$  is a practical lower limit for  $R_{G}$ . The LMH6723 begins to operate in a gain bandwidth limited fashion in the region where  $R_{F}$  must be increased for higher gains. Note that the amplifier will operate with  $R_{G}$  values well below  $100\Omega,$  however results will be substantially different than predicted from ideal models. In particular the voltage potential between the Inverting and Non-Inverting inputs cannot be expected to remain small.

For inverting configurations the impedance seen by the source is  $R_G$  II  $R_T$ . For most sources this limits the maximum inverting gain since  $R_F$  is determined by *Figure 3*. The value of  $R_G$  is then  $R_F/Gain$ . Thus for an inverting gain of -4V/V the input impedance is equal to  $100\Omega$ . Using a termination resistor this can be brought down to match a  $50\Omega$  or  $75\Omega$  source, however, a  $150\Omega$  source cannot be matched.

FIGURE 3. R<sub>F</sub> vs. Inverting Gain

#### **ACTIVE FILTERS**

When using any current feedback Operational Amplifier as an active filter it is necessary to be careful using reactive components in the feedback loop. Reducing the feedback impedance, especially at higher frequencies, will almost certainly cause stability problems. Likewise capacitance on the inverting input should be avoided. See Application Notes OA-7 and OA-26 for more information on Active Filter applications for Current Feedback Op Amps.

When using the LMH6723 as a low pass filter the value of  $R_{\rm F}$  can be substantially reduced from the value recommended in the  $R_{\rm F}$  vs. Gain charts. The benefit of reducing  $R_{\rm F}$  is increased gain at higher frequencies, which improves attenuation in the stop band. Stability problems are avoided because in the stop band additional device bandwidth is used to cancel the input signal rather than amplify it. The benefit of this change depends on the particulars of the circuit design. With a high pass filter configuration reducing  $R_{\rm F}$  will likely result in device instability and is not recommended.

### Application Section (Continued)

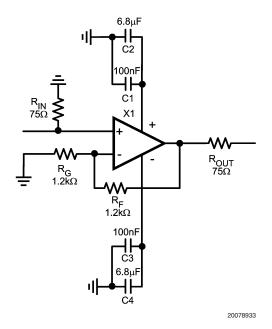

FIGURE 4. Typical Application with Suggested Supply Bypassing

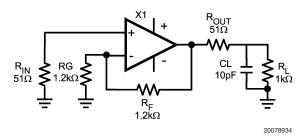

FIGURE 5. Decoupling Capacitive Loads

#### **DRIVING CAPACITIVE LOADS**

Capacitive output loading applications will benefit from the use of a series output resistor  $R_{OUT}.\ Figure\ 5$  shows the use of a series output resistor,  $R_{OUT}.\ Figure\ 5$  shows the use of a series output resistor,  $R_{OUT}.\$ to stabilize the amplifier output under capacitive loading. The charts "Suggested  $R_{OUT}$  vs. Cap Load" give a recommended value for selecting a series output resistor for mitigating capacitive loads. The values suggested in the charts are selected for .5dB or less of peaking in the frequency response. This gives a good compromise between settling time and bandwidth. For applications where maximum frequency response is needed and some peaking is tolerable, the value of  $R_{OUT}$  can be reduced slightly from the recommended values.

There will be amplitude lost in the series resistor unless the gain is adjusted to compensate; this effect is most noticeable with heavy loads ( $R_L < 150\Omega$ ).

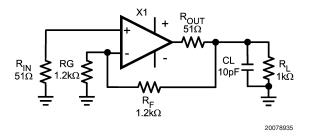

An alternative approach is to place Rout inside the feedback loop as shown in *Figure 6*. This will preserve gain accuracy, but will still limit maximum output voltage swing.

FIGURE 6. Series Output Resistor inside feedback loop

#### **INVERTING INPUT PARASITIC CAPACITANCE**

Parasitic capacitance is any capacitance in a circuit that was not intentionally added. It comes about from electrical interaction between conductors. Parasitic capacitance can be reduced but never entirely eliminated. Most parasitic capacitances that cause problems are related to board layout or lack of termination on transmission lines. Please see the section on Layout Considerations for hints on reducing problems due to parasitic capacitances on board traces. Transmission lines should be terminated in their characteristic impedance at both ends.

High speed amplifiers are sensitive to capacitance between the inverting input and ground or power supplies. This shows up as gain peaking at high frequency. The capacitor raises device gain at high frequencies by making  $R_{\rm G}$  appear smaller. Capacitive output loading will exaggerate this effect.

One possible remedy for this effect is to slightly increase the value of the feedback (and gain set) resistor. This will tend to offset the high frequency gain peaking while leaving other parameters relatively unchanged. If the device has a capacitive load as well as inverting input capacitance using a series output resistor as described in the section on "Driving Capacitive Loads" will help.

#### LAYOUT CONSIDERATIONS

Whenever questions about layout arise, use the evaluation board as a guide. Use the CLC730227 for SOIC and the CLC730216 for SOT 23 packages.

To reduce parasitic capacitances ground and power planes should be removed near the input and output pins. Components in the feedback loop should be placed as close to the device as possible. For long signal paths controlled impedance lines should be used, along with impedance matching at both ends.

Bypass capacitors should be placed as close to the device as possible. Bypass capacitors from each rail to ground are applied in pairs. The larger electrolytic bypass capacitors can be located anywhere on the board, the smaller ceramic capacitors should be placed as close to the device as possible.

#### **VIDEO PERFORMANCE**

The LMH6723 has been designed to provide good performance with both PAL and NTSC composite video signals. The LMH6723 is specified for PAL signals. NTSC performance is typically marginally better due to the lower frequency content of the signal. Performance degrades as the loading is increased, therefore best performance will be obtained with back terminated loads. The back termination reduces reflections from the transmission line and effectively masks transmission line and other parasitic capacitances

# **Application Section** (Continued)

from the amplifier output stage. Figure 4 shows a typical configuration for driving a 75 $\Omega$  Cable. The amplifier is configured for a gain of two to make up for the 6dB of loss in  $R_{OUT}$ .

#### SINGLE 5V SUPPLY VIDEO

With a 5V supply the LMH6723 is able to handle a composite NTSC video signal, provided that the signal is AC coupled and level shifted so that the signal is centered around  $V_{\rm CC}/2$ .

#### **POWER DISSIPATION**

Follow these steps to determine the Maximum power dissipation for the LMH6723:

- Calculate the quiescent (no-load) power: P<sub>AMP</sub> = I<sub>CC</sub> \* (V<sub>S</sub>) V<sub>S</sub> = V<sup>+</sup> - V<sup>-</sup>

- Calculate the RMS power dissipated in the output stage: P<sub>D</sub> (rms) = rms ((V<sub>S</sub>-V<sub>OUT</sub>)\*I<sub>OUT</sub>) where V<sub>OUT</sub> and I<sub>OUT</sub> are the voltage and current across the external load and V<sub>S</sub> is the total supply current.

3. Calculate the total RMS power:  $P_T = P_{AMP} + P_D$

The maximum power that the LMH6723, package can dissipate at a given temperature can be derived with the following equation:

$P_{MAX} = (150^{\circ}$  -  $T_{AMB})/$   $\theta_{JA},$  where  $T_{AMB} =$  Ambient temperature (°C) and  $\theta_{JA} =$  Thermal resistance, from junction to ambient, for a given package (°C/W). For the SOIC package  $\theta_{JA}$  is 148°C/W, for the SOT it is 250°C/W.

#### **ESD PROTECTION**

The LMH6723 is protected against electrostatic discharge (ESD) on all pins. The LMH6723 will survive 2000V Human Body model or 200V Machine model events.

Under closed loop operation the ESD diodes have no effect on circuit performance. There are occasions, however, when the ESD diodes will be evident. If the LMH6723 is driven into a slewing condition the ESD diodes will clamp large differential voltages until the feedback loop restores closed loop operation. Also if the device powered down and a large input signal is applied the ESD diodes will conduct.

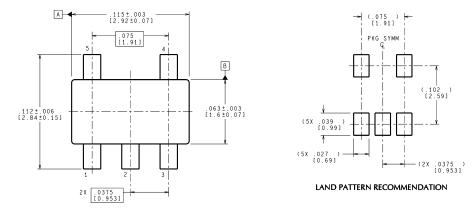

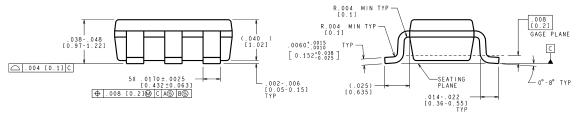

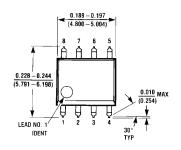

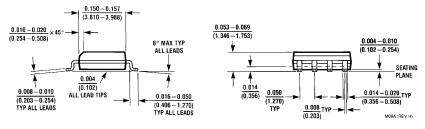

# **Physical Dimensions** inches (millimeters) unless otherwise noted

CONTROLLING DIMENSION IS INCH VALUES IN [ ] ARE MILLIMETERS

MF05A (Rev B)

5-Pin SOT23 **NS Product Number MF05A**

8-Pin SOIC **NS Product Number M08A**

## **Notes**

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor

Americas Customer

Support Center

Email: new feedback@nsc.c

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560