#### CDMA/FM LOW NOISE AMPLIFIER/MIXER

#### **Typical Applications**

- CDMA/FM Cellular Systems

- Supports Dual-Mode AMPS/CDMA

- Supports Dual-Mode TACS/CDMA

- General Purpose Down Converter

- Commercial and Consumer Systems

- Portable Battery Powered Equipment

### **Product Description**

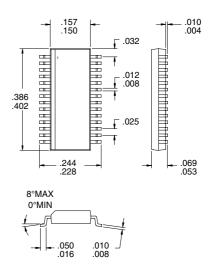

The RF2406 is a receiver front-end designed for the receive section of dual-mode CDMA/FM cellular applications. It is designed to amplify and down-convert RF signals while providing 30dB of stepped gain control range and features digital control of LNA gain, IF output selection, LO buffer enable, power down mode, and low current "lazy" mode. The digitally selected "lazy" mode reduces current drain by approximately 10mA, putting the IC in a lower current drain, noise and IP3 state. This gives the receiver designer added flexibility to dynamically optimize these downconverter parameters. Noise Figure, IP3, and other specs are designed to be compatible with the IS-95 Interim Standard for CDMA cellular communications. The IC is manufactured on an advanced Silicon Bipolar process and packaged in an SSOP-28.

#### **Optimum Technology Matching® Applied**

✓ Si BJT ☐ GaAs HBT ☐ GaAs MESFET☐ Si Bi-CMOS ☐ SiGe HBT ☐ Si CMOS

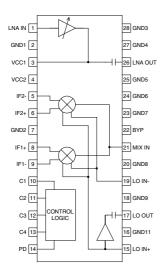

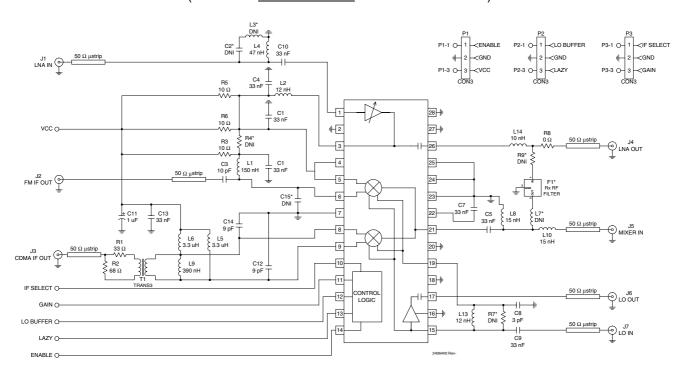

**Functional Block Diagram**

Package Style: SSOP-28

#### **Features**

- Complete Receiver Front-End

- Stepped LNA Gain Control

- Low Current-Drain "Lazy" Mode

- Buffered LO Output

- Digitally Selectable IF Outputs

- 500 MHz to 1100 MHz Operation

#### **Ordering Information**

RF2406 CDMA/FM Low Noise Amplifier/Mixer RF2406 PCBA Fully Assembled Evaluation Board

RF Micro Devices, Inc. 7625 Thorndike Road Greensboro, NC 27409, USA Tel (336) 664 1233 Fax (336) 664 0454 http://www.rfmd.com

Rev B7 991202

# **RF2406**

#### **Absolute Maximum Ratings**

| Parameter                     | Rating       | Unit     |

|-------------------------------|--------------|----------|

| Supply Voltage                | -0.5 to +5.0 | $V_{DC}$ |

| Input LO and RF Levels        | +6           | dBm      |

| Operating Ambient Temperature | -40 to +85   | °C       |

| Storage Temperature           | -40 to +150  | °C       |

RF Micro Devices believes the furnished information is correct and accurate at the time of this printing. However, RF Micro Devices reserves the right to make changes to its products without notice. RF Micro Devices does not assume responsibility for the use of the described product(s).

| assume responsibility for the use of the described product(s) |               |              |      |      | production and use of the described production.                           |

|---------------------------------------------------------------|---------------|--------------|------|------|---------------------------------------------------------------------------|

| Parameter                                                     | Specification |              |      | Unit | Condition                                                                 |

|                                                               | Min.          | Тур.         | Max. | 0    |                                                                           |

|                                                               |               |              |      |      | T=25°C, V <sub>CC</sub> =3.6V, RF=881MHz,                                 |

| Overall                                                       |               |              |      |      | LO=966MHz @-3dBm                                                          |

|                                                               |               |              |      |      | RF2=882 MHz for IIP3 Measurements                                         |

|                                                               |               |              |      |      | See Mode Control Logic Table                                              |

| RF Frequency Range                                            |               | 500 to 1100  |      | MHz  |                                                                           |

| LO Frequency Range                                            |               | 500 to 1100  |      | MHz  |                                                                           |

| IF Frequency Range                                            |               | 0.1 to 250   |      | MHz  |                                                                           |

| Power Supply                                                  |               |              |      |      |                                                                           |

| Voltage                                                       |               | 2.7 to 4.0   |      | V    |                                                                           |

| Current Consumption                                           |               | 20           |      | mA   | FM                                                                        |

|                                                               |               | 25           |      | mA   | CDMA Max. Gain                                                            |

|                                                               |               | 26           |      | mA   | CDMA Nom. Gain                                                            |

|                                                               |               | 18           |      | mA   | CDMA Min. Gain                                                            |

|                                                               |               | adds 4       |      | mA   | LO Buffer ON                                                              |

|                                                               |               | subtracts 10 |      | mA   | "Lazy" Mode                                                               |

|                                                               |               | < 20         |      | μΑ   | Power Down                                                                |

| Max Dynamic Range Mode                                        |               |              |      |      |                                                                           |

| Cascaded Perform. to IF1                                      |               |              |      |      | $1\mathrm{k}\Omega$ balanced load, 3.0dB Image Filter Loss CDMA Max. Gain |

| Cascade Conversion Gain                                       |               | 24           |      | dB   |                                                                           |

| Cascade Input IP3 to IF1                                      |               | -4           |      | dBm  |                                                                           |

| Cascade Noise Figure                                          |               | 4.3          |      | dB   |                                                                           |

| Cascaded Perform. to IF2                                      |               |              |      |      | 870Ω load, 3dB Image Filter Loss                                          |

| Cascade Conversion Gain                                       |               | 18           |      | dB   |                                                                           |

| Cascade Input IP3                                             |               | -4           |      | dBm  |                                                                           |

| Cascade Noise Figure                                          |               | 4.3          |      | dB   |                                                                           |

| First Section (LNA)                                           |               |              |      |      |                                                                           |

| Gain                                                          |               | 14.5         |      | dB   | FM and CDMA Max. Gain                                                     |

|                                                               |               | 7.5          |      | dB   | CDMA Nom. Gain                                                            |

|                                                               |               | -5           |      | dB   | CDMA Min. Gain                                                            |

| Noise Figure                                                  |               | 2.5          |      | dB   | FM and CDMA Max. Gain                                                     |

| 3                                                             |               | 4.5          |      | dB   | CDMA Nom. Gain                                                            |

|                                                               |               | 9.0          |      | dB   | CDMA Min. Gain                                                            |

| Input IP3                                                     |               | +7           |      | dBm  | FM and CDMA Max. Gain                                                     |

| •                                                             |               | >+14         |      | dBm  | CDMA Nom. Gain                                                            |

|                                                               |               | >+20         |      | dBm  | CDMA Min. Gain                                                            |

| Input P1dB                                                    |               | -11          |      | dBm  | FM and CDMA Max. Gain                                                     |

| Reverse Isolation                                             |               | 25           |      | dB   | FM and CDMA Max. Gain                                                     |

| Input VSWR                                                    |               | <4:1         |      |      | Internally matched for optimum noise figure from $50\Omega$ source        |

| Output VSWR                                                   |               | <1.5:1       |      |      | With external match (partial)                                             |

8-14 Rev B7 991202

| Second Section (Mixer, IF1            |           |     |                                                                    |

|---------------------------------------|-----------|-----|--------------------------------------------------------------------|

| or IF2 Output)                        |           |     |                                                                    |

| · · · · · · · · · · · · · · · · · · · | 10        | ID. |                                                                    |

| Conversion Gain                       | 16        | dB  | IF 1, 1kΩ balanced load.                                           |

|                                       | 7         | dB  | IF 2, 870Ω load.                                                   |

| Noise Figure                          | 11.5      | dB  | Single sideband.                                                   |

| Input VSWR                            | <1.5:1    |     | With external matching network                                     |

| Input IP3 to IF1                      | +7        | dBm |                                                                    |

| Input IP3 to IF2                      | +7        | dBm |                                                                    |

| Input P1dB, IF2                       | -4        | dBm |                                                                    |

| Input P1dB, IF1                       | -8        | dBm |                                                                    |

| MIX IN to IF1, IF2 Rejection          | 35        | dB  |                                                                    |

| IF1, IF2 Output Freq. Range           | 70 to 100 | MHz | With external IF interface network                                 |

| Output Impedance                      | >1        | kΩ  | IF1, balanced, open collector                                      |

|                                       | 870       | Ω   | IF2, single ended, with external inductor.                         |

| LO Input                              |           |     |                                                                    |

| LO Input Range                        | -6 to 0   | dBm |                                                                    |

| LO Output Level                       | 0         | dBm | Buffer ON, 0dBm input                                              |

| LO Output Level                       | -35       | dBm | Buffer OFF, 0dBm input                                             |

| LO IN to LNA Input Rejection          | 37        | dB  | ·                                                                  |

| LO IN to IF1, IF2 Rejection           | 15        | dB  |                                                                    |

| LO Input VSWR                         | <2:1      |     | With external matching network                                     |

| "Lazy" Mode                           |           |     | -                                                                  |

| Cascaded Perform, to IF1              |           |     | $1 k\Omega$ balanced load, 3.0dB Image Filter Loss.                |

| Cascaded Perioriii. to IF I           |           |     | CDMA Max. Gain                                                     |

| Cascade Conversion Gain               | 21        | dB  |                                                                    |

| Cascade Input IP3 to IF1              | -8        | dBm |                                                                    |

| Cascade Noise Figure                  | 4.1       | dB  |                                                                    |

| Cascaded Perform. to IF2              |           |     | 870Ω load, 3dB Image Filter Loss.                                  |

| Cascade Conversion Gain               | 15.3      | dB  |                                                                    |

| Cascade Input IP3                     | -8        | dBm |                                                                    |

| Cascade Noise Figure                  | 4.0       | dB  |                                                                    |

| First Section (LNA)                   |           |     |                                                                    |

| Gain                                  | 9.0       | dB  | FM and CDMA Max. Gain                                              |

| daiii                                 | 6.2       | dB  | CDMA Nom. Gain                                                     |

|                                       | -5        | dB  | CDMA Min. Gain                                                     |

| Noise Figure                          | 2.4       | dB  | FM and CDMA Max. Gain                                              |

| Noise rigure                          | 4.8       | dB  | CDMA Nom. Gain                                                     |

|                                       | 9.0       | dB  | CDMA Min. Gain                                                     |

| Input IDO                             | +1        | dBm | FM and CDMA Max. Gain                                              |

| Input IP3                             |           |     |                                                                    |

|                                       | >+6       | dBm | CDMA Min. Coin                                                     |

| January Dalaid                        | >+20      | dBm | CDMA Min. Gain                                                     |

| Input P1dB                            | -16       | dBm | FM and CDMA Max. Gain                                              |

| Reverse Isolation                     | 25        | dB  | FM and CDMA Max. Gain                                              |

| Input VSWR                            | <4:1      |     | Internally matched for optimum noise figure from $50\Omega$ source |

| Output VSWR                           | <1.5:1    |     | With external match (partial)                                      |

| S  |

|----|

| Ω  |

| Z  |

| Ш  |

| μ. |

| Ż  |

| ᇹ  |

| ĕ  |

| Second Section (Mixer, IF1   |       |     |     |                                            |

|------------------------------|-------|-----|-----|--------------------------------------------|

| or IF2 Output)               |       |     |     |                                            |

| Conversion Gain              | 1     | 4   | dB  | IF 1, 1 k $\Omega$ balanced load.          |

|                              | 5     | .5  | dB  | IF 2, 870Ω load.                           |

| Noise Figure                 | 9     | .5  | dB  | Single sideband.                           |

| Input VSWR                   | <1.   | 5:1 |     | With external matching network             |

| Input IP3 to IF1             | +     | 2   | dBm |                                            |

| Input IP3 to IF2             | +     | 2   | dBm |                                            |

| Input P1dB, IF2              | =     | 9   | dBm |                                            |

| Input P1dB, IF1              | -     | 6   | dBm |                                            |

| MIX IN to IF1, IF2 Rejection | 3     | 5   | dB  |                                            |

| IF1, IF2 Output Freq. Range  | 70 to | 100 | MHz | With external IF interface network         |

| Output Impedance             | >     | 1   | kΩ  | IF1, balanced, open collector              |

|                              | 87    | 70  | Ω   | IF2, single ended, with external inductor. |

| LO Input                     |       |     |     |                                            |

| LO Input Range               | -61   | 0 0 | dBm |                                            |

| LO Output Level              | (     | )   | dBm | Buffer On, 0dBm input                      |

| LO Output Level              | -3    | 35  | dBm | Buffer Off, 0dBm input                     |

| LO IN to LNA Input Rejection | 3     | 0   | dB  |                                            |

| LO IN to IF1, IF2 Rejection  | 1     | 5   | dB  |                                            |

| LO Input VSWR                | <2    | 2:1 |     | With external matching network             |

## **Mode Control Logic**

| MODE                      | C1 | C2 | C3 | C4 | PD |

|---------------------------|----|----|----|----|----|

| FM (IF2)                  | L  | Н  | Х  | Н  | Н  |

| CDMA Max. Gain (IF1)      | Н  | Н  | X  | Н  | Н  |

| CDMA Nom. Gain (IF1)      | Н  | L  | Х  | Н  | Н  |

| CDMA Min. Gain (IF1)      | L  | L  | Х  | Н  | Н  |

| Lazy FM (IF2)             | L  | Н  | X  | L  | Н  |

| Lazy CDMA Max. Gain (IF1) | Н  | Н  | X  | L  | Н  |

| Lazy CDMA Nom. Gain (IF1) | Н  | L  | Х  | L  | Н  |

| Lazy CDMA Min. Gain (IF1) | L  | L  | Х  | L  | Н  |

| LO Buffer ON              | Х  | Х  | Н  | Х  | Н  |

| LO Buffer OFF             | Х  | Х  | L  | Х  | Х  |

| Power Down                | L  | Х  | Χ  | Х  | L  |

8-16 Rev B7 991202

| Pin | Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Interface Schematic                       |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 1   | LNA IN   | RF Input pin. This pin is internally matched for optimum noise figure from a $50\Omega$ source. This pin is internally DC biased and, if connected to a device with DC present, should be DC blocked with a capacitor suitable for the frequency of operation.                                                                                                                                                                                                                                                                                                                                    | LNA IN O                                  |

| 2   | GND1     | Ground connection for the LNA circuits. Keep traces physically short and connect immediately to ground plane for best performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                           |

| 3   | VCC1     | Supply Voltage for the LNA. External inductance, ~12nH, is required in addition to internal inductance to achieve optimum LNA performance. This extra inductance can be easily achieved with a thin microstrip line. The value of this inductance will change with the frequency of operation. RF and IF bypassing is required on the supply side of the inductance. The ground side of the bypass capacitors should connect immediately to ground plane.                                                                                                                                         | See pin 1.                                |

| 4   | VCC2     | Supply Voltage for the LO buffer amplifier, bias circuits, and control logic. External RF and IF bypassing is required. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane.                                                                                                                                                                                                                                                                                                      | VCC2 BIAS CO OUT                          |

| 5   | IF2-     | Same as pin 6, except complementary output. For typical single ended operation, this pin is connected directly to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | See pin 6.                                |

| 6   | IF2+     | FM IF Output pin. This is a balanced output, but is typically used as a single-ended output. The internal circuitry, in conjunction with an external matching/bias inductor to $V_{CC}$ , sets the operating impedance. This inductor is typically incorporated in the matching network between the output and IF filter. The net output impedance, including the external inductor, is about $870\Omega$ at $85  \text{MHz}$ . Because this pin is biased to $V_{CC}$ , a DC blocking capacitor must be used if the IF filter input has a DC path to ground. See Application Schematic.          | 1F2+ 1F2-<br>0 8.5 pF<br>2.1 kΩ           |

| 7   | GND2     | Ground connection. Keep traces physically short and connect immediately to ground plane for best performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                           |

| 8   | IF 1+    | CDMA IF Output pin. This is a balanced output. The internal circuitry, in conjunction with an external matching/bias inductor to $V_{CC}$ , sets the operating impedance. This inductor is typically incorporated in the matching network between the output and IF filter. The net output impedance, including the external inductor, at 85MHz is higher than $1k\Omega$ , even though the part is designed to drive a $1k\Omega$ load. Because this pin is biased to $V_{CC}$ , a DC blocking capacitor must be used if the IF filter input has a DC path to ground. See Application Schematic. | IF1+ GND2 IF1-<br>1.2 1.2<br>pF pF        |

| 9   | IF 1-    | Same as pin 8, except complementary output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | See pin 8.                                |

| 10  | C1       | Control line for mode/gain select. See specification table for details. The threshold voltage is 1.6 V, and the pin draws less than $50\mu\text{A}$ when selected.                                                                                                                                                                                                                                                                                                                                                                                                                                | C1 Ο—VVV————————————————————————————————— |

| 11  | C2       | Control line for mode/gain select. See specification table for details. The threshold voltage is 1.6 V, and the pin draws less than $50\mu A$ when selected.                                                                                                                                                                                                                                                                                                                                                                                                                                      | C3 Ο—VVV————————————————————————————————— |

| 12  | C3       | Enable pin for the LO output buffer amplifier. This is a digitally controlled input. A logic "high" turns the buffer amplifier on, and the current consumption increases by 4mA (with 0dBm LO input). A logic "low" turns the buffer amplifier off. The threshold voltage is approximately 1.6 V.                                                                                                                                                                                                                                                                                                 | C3 Ο—VVV————————————————————————————————— |

# RF2406

| 13 C4 Enable pin for "Lazy Mode". This is a digitally controlled input. A logic "high" maintains the part in full performance mode. A logic "low" places the part in a reduced-current/reduced performance mode. See the specification table for details. The threshold voltage is 1.6V, and the pin draws less than 50μA when selected.  14 PD Power down pin. A logic "low" turns the part off. A logic "high" (>1.6V) turns the part on. In addition, pin 10 (C1) should also be taken low during power down.  15 LO IN+ Mixer LO Balanced Input Pin. For single-ended input operation, this pin is used as an input and pin 18 is bypassed to ground.  16 GND11 Ground connection for LO buffer ampliffer. Keep traces physically short and connect immediately to ground plane for best performance.  17 LO OUT Optional Buffered LO Output. This pin is internally DC blocked and matched to 50Ω. The buffer ampliffer is switched on or off by the voltage level at pin 12.  18 GND9 Die flag ground. Keep traces physically short and connect immediately to ground plane for best performance.  19 LO IN- Mixer LO bypass.  20 GND8 Ground connection for the mixer. Keep traces physically short and connect immediately to ground plane for best performance.  21 MIX IN Mixer RF Input Pin. This pin is internally DC blocked and should be DC blocked if connected to a device with DC present. External matching network sets RF and IF impedance for optimum performance.  22 BYP Internal voltage reference. External RF and IF bypassing is required. The trace length between the pin and the bypass capacitors should connect immediately to ground plane.  23 GND7 Same as pin 2.  24 GND6 Same as pin 2.  25 GND5 Same as pin 2.  26 LNA OUT LNA Output pin. This pin is internally DC blocked and externally matched to 50Ω at pin 3 in order to facilitate an easy interface to a 50Ω Image Filter.  27 GND4 Same as pin 25. |    |         |                                                                                                                                                                                                                                                                | 1                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| turns the part on. In addition, pin 10 (C1) should also be taken low during power down.    15   LO IN+   Mixer LO Balanced Input Pin. For single-ended input operation, this pin is used as an input and pin 18 is bypassed to ground.    16   GND11   Ground connection for LO buffer ampliffier. Keep traces physically short and connect immediately to ground plane for best performance.   17   LO OUT   Optional Buffered LO Output. This pin is internally DC blocked and matched to 50Ω The buffer amplifier is switched on or off by the voltage level at pin 12.    18   GND9   Die flag ground. Keep traces physically short and connect immediately to ground plane for best performance.   19   LO IN-   Mixer LO bypass.     20   GND8   Ground connection for the mixer. Keep traces physically short and connect immediately to ground plane for best performance.   21   MIX IN   Mixer RF Input Pin. This pin is internally DC biased and should be DC blocked if connected to a device with DC present. External matching network sets RF and IF impedance for optimum performance.   22   BYP   Internal voltage reference. External RF and IF bypassing is required. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane.   23   GND7   Same as pin 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |         | "high" maintains the part in full performance mode. A logic "low" places the part in a reduced-current/reduced performance mode. See the specification table for details. The threshold voltage is 1.6 V, and the pin draws less than $50\mu A$ when selected. | C4 Ο— VV — — — — — — — — — — — — — — — — — |

| is used as an input and pin 18 is bypassed to ground.  16 GND11 Ground connection for LO buffer ampliffer. Keep traces physically short and connect immediately to ground plane for best performance.  17 LO OUT Optional Buffered LO Output. This pin is internally DC blocked and matched to 50Ω The buffer ampliffer is switched on or off by the voltage level at pin 12.  18 GND9 Die flag ground. Keep traces physically short and connect immediately to ground plane for best performance.  19 LO IN- Mixer LO bypass. See pin 15.  20 GND8 Ground connection for the mixer. Keep traces physically short and connect immediately to ground plane for best performance.  21 MIX IN Mixer RF Input Pin. This pin is internally DC blosed and should be DC blocked if connected to a device with DC present. External matching network sets RF and IF impedance for optimum performance.  22 BYP Internal voltage reference. External RF and IF bypassing is required. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane.  23 GND7 Same as pin 2.  24 GND6 Same as pin 2.  25 GND5 Same as pin 2.  26 LNA OUT LNA Output pin. This pin is internally DC blocked and externally matched to 50Ω at pin 3 in order to facilitate an easy interface to a 50Ω Image Filter.  27 GND4 Same as pin 25.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14 | PD      | turns the part on. In addition, pin 10 (C1) should also be taken low dur-                                                                                                                                                                                      |                                            |

| and connect immediately to ground plane for best performance.  17 LO OUT  Optional Buffered LO Output. This pin is internally DC blocked and matched to 50Ω. The buffer amplifier is switched on or off by the voltage level at pin 12.  18 GND9  Die flag ground. Keep traces physically short and connect immediately to ground plane for best performance.  19 LO IN-  Mixer LO bypass.  Ground connection for the mixer. Keep traces physically short and connect immediately to ground plane for best performance.  21 MIX IN  Mixer RF Input Pin. This pin is internally DC biased and should be DC blocked if connected to a device with DC present. External matching network sets RF and IF impedance for optimum performance.  22 BYP  Internal voltage reference. External RF and IF bypassing is required. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane.  23 GND7 Same as pin 2.  24 GND6 Same as pin 2.  25 GND5 Same as pin 2.  LNA OUTD LNA Output pin. This pin is internally DC blocked and externally matched to 50Ω at pin 3 in order to facilitate an easy interface to a 50Ω Image Filter.  27 GND4 Same as pin 25.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15 | LO IN+  |                                                                                                                                                                                                                                                                | LO IN-                                     |

| matched to 50Ω The buffer amplifier is switched on or off by the voltage level at pin 12.       18     GND9     Die flag ground. Keep traces physically short and connect immediately to ground plane for best performance.       19     LO IN-     Mixer LO bypass.     See pin 15.       20     GND8     Ground connection for the mixer. Keep traces physically short and connect immediately to ground plane for best performance.       21     MIX IN     Mixer RF Input Pin. This pin is internally DC blased and should be DC blocked if connected to a device with DC present. External matching network sets RF and IF impedance for optimum performance.       22     BYP     Internal voltage reference. External RF and IF bypassing is required. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane.       23     GND7     Same as pin 2.       24     GND6     Same as pin 2.       25     GND5     Same as pin 2.       26     LNA OUT     LNA Output pin. This pin is internally DC blocked and externally matched to 50Ω at pin 3 in order to facilitate an easy interface to a 50Ω lmage Filter.     See pin 1.       27     GND4     Same as pin 25.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16 | GND11   |                                                                                                                                                                                                                                                                |                                            |

| to ground plane for best performance.  19 LO IN- Mixer LO bypass. See pin 15.  20 GND8 Ground connection for the mixer. Keep traces physically short and connect immediately to ground plane for best performance.  21 MIX IN Mixer RF Input Pin. This pin is internally DC biased and should be DC blocked if connected to a device with DC present. External matching network sets RF and IF impedance for optimum performance.  22 BYP Internal voltage reference. External RF and IF bypassing is required. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane.  23 GND7 Same as pin 2.  24 GND6 Same as pin 2.  25 GND5 Same as pin 2.  26 LNA OUT LNA Output pin. This pin is internally DC blocked and externally matched to 50Ω at pin 3 in order to facilitate an easy interface to a 50Ω Image Filter.  27 GND4 Same as pin 25.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |         | matched to $50\Omega$ . The buffer amplifier is switched on or off by the voltage level at pin 12.                                                                                                                                                             | See pin 4.                                 |

| <ul> <li>GND8 Ground connection for the mixer. Keep traces physically short and connect immediately to ground plane for best performance.</li> <li>MIX IN Mixer RF Input Pin. This pin is internally DC biased and should be DC blocked if connected to a device with DC present. External matching network sets RF and IF impedance for optimum performance.</li> <li>BYP Internal voltage reference. External RF and IF bypassing is required. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane.</li> <li>GND7 Same as pin 2.</li> <li>GND6 Same as pin 2.</li> <li>GND5 Same as pin 2.</li> <li>LNA OUT LNA Output pin. This pin is internally DC blocked and externally matched to 50Ω at pin 3 in order to facilitate an easy interface to a 50Ω lmage Filter.</li> <li>GND4 Same as pin 25.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18 | GND9    |                                                                                                                                                                                                                                                                |                                            |

| <ul> <li>nect immediately to ground plane for best performance.</li> <li>Mix IN         <ul> <li>Mix RF Input Pin. This pin is internally DC biased and should be DC blocked if connected to a device with DC present. External matching network sets RF and IF impedance for optimum performance.</li> </ul> </li> <li>BYP         <ul> <li>Internal voltage reference. External RF and IF bypassing is required. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane.</li> </ul> </li> <li>GND7         <ul> <li>Same as pin 2.</li> </ul> </li> <li>GND6             <ul> <li>Same as pin 2.</li> </ul> </li> <li>GND5             <ul> <li>Same as pin 2.</li> </ul> </li> <li>LNA OUT             <ul> <li>LNA Output pin. This pin is internally DC blocked and externally matched to 50Ω at pin 3 in order to facilitate an easy interface to a 50Ω Image Filter.</li> </ul> </li> <li>GND4                      <ul> <li>Same as pin 25.</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19 | LO IN-  | Mixer LO bypass.                                                                                                                                                                                                                                               | See pin 15.                                |

| blocked if connected to a device with DC present. External matching network sets RF and IF impedance for optimum performance.  BYP Internal voltage reference. External RF and IF bypassing is required. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane.  Same as pin 2.  GND6 Same as pin 2.  CHA OUT LNA Output pin. This pin is internally DC blocked and externally matched to 50Ω at pin 3 in order to facilitate an easy interface to a 50Ω lmage Filter.  GND4 Same as pin 25.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20 | GND8    |                                                                                                                                                                                                                                                                |                                            |

| The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane.  23 GND7 Same as pin 2.  24 GND6 Same as pin 2.  25 GND5 Same as pin 2.  26 LNA OUT LNA Output pin. This pin is internally DC blocked and externally matched to $50\Omega$ at pin 3 in order to facilitate an easy interface to a $50\Omega$ lmage Filter.  27 GND4 Same as pin 25.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21 | MIX IN  | blocked if connected to a device with DC present. External matching                                                                                                                                                                                            | MIX IN O                                   |

| 24GND6Same as pin 2.25GND5Same as pin 2.26LNA OUTLNA Output pin. This pin is internally DC blocked and externally matched to $50\Omega$ at pin 3 in order to facilitate an easy interface to a $50\Omega$ lmage Filter.27GND4Same as pin 25.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22 | ВҮР     | The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect                                                                                                                        |                                            |

| <ul> <li>GND5 Same as pin 2.</li> <li>LNA OUT LNA Output pin. This pin is internally DC blocked and externally matched to 50Ω at pin 3 in order to facilitate an easy interface to a 50Ω lmage Filter.</li> <li>GND4 Same as pin 25.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23 | GND7    | Same as pin 2.                                                                                                                                                                                                                                                 |                                            |

| <ul> <li>LNA OUT LNA Output pin. This pin is internally DC blocked and externally matched to 50Ω at pin 3 in order to facilitate an easy interface to a 50Ω lmage Filter.</li> <li>GND4 Same as pin 25.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 24 | GND6    | Same as pin 2.                                                                                                                                                                                                                                                 |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25 | GND5    | Same as pin 2.                                                                                                                                                                                                                                                 |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26 | LNA OUT | matched to $50\Omega$ at pin 3 in order to facilitate an easy interface to a $50\Omega$                                                                                                                                                                        | See pin 1.                                 |

| 28 CND2 Same as nin 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27 | GND4    | Same as pin 25.                                                                                                                                                                                                                                                |                                            |

| 20 GIVDS Same as pin 25.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28 | GND3    | Same as pin 25.                                                                                                                                                                                                                                                |                                            |

8-18 Rev B7 991202

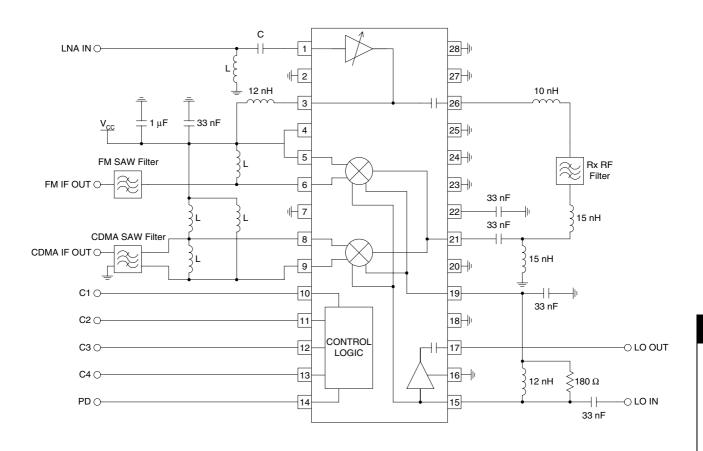

# **Application Schematic**

8

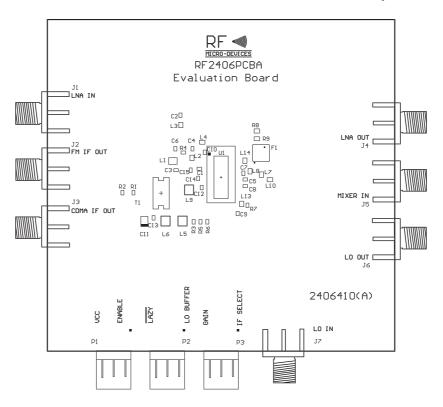

## **Evaluation Board Schematic**

(Download Bill of Materials from www.rfmd.com.)

8-20 Rev B7 991202

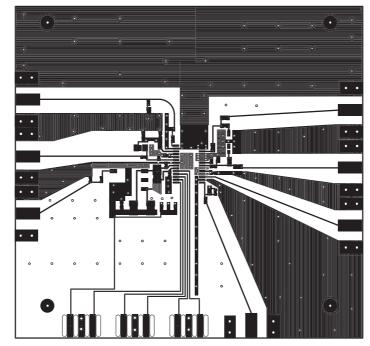

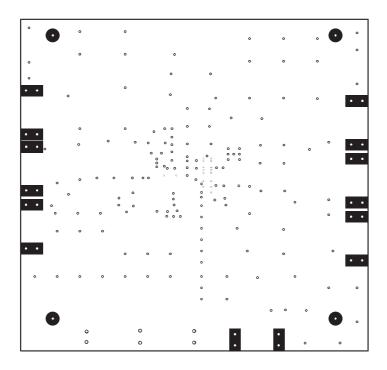

# Evaluation Board Layout Board Size 3.088" x 2.948"

Board Thickness 0.056", Board Material FR-4, Multi-Layer

8-22 Rev B7 991202