## **Product Description**

Sirenza Microdevices' SHF-0189 is a high performance AlGaAs/GaAs Heterostructure FET (HFET) housed in a low-cost surface-mount plastic package. The HFET technology improves breakdown voltage while minimizing Schottky leakage current resulting in higher PAE and improved linearity.

Output power at 1dB compression for the SHF-0189 is +27 dBm when biased for Class AB operation at 8V,100mA. The +40 dBm third order intercept makes it ideal for high dynamic range, high intercept point requirements. It is well suited for use in both analog and digital wireless communication infrastructure and subscriber equipment including 3G, cellular, PCS, fixed wireless, and pager systems.

The matte tin finish on Sirenza's lead-free package utilizes a post annealing process to mitigate tin whisker formation and is RoHS compliant per EU Directive 2002/95. This package is also manufactured with green molding compounds that contain no antimony trioxide nor halogenated fire retardants.

# SHF-0189

SHF-0189Z

0.05 - 6 GHz, 0.5 Watt GaAs HFET

#### **Product Features**

- Now available in Lead Free, RoHS Compliant, & Green Packaging

- High Linearity Performance at 1.96 GHz

- +27 dBm P1dB

- +40 dBm Output IP3

- +16.5 dB Gain

- High Drain Efficiency

- See App Note AN-031 for circuit details

## **Applications**

- Analog and Digital Wireless Systems

- 3G, Cellular, PCS

- Fixed Wireless, Pager Systems

| Symbol             | Device Characteristics                 | Test C on ditions, $25C$<br>V $_{DS}$ = $8$ V , $I_{DQ}$ = $100$ m A (unless otherwise noted) | Test<br>Frequency        | U n its | M in  | Тур              | Мах    |

|--------------------|----------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------|---------|-------|------------------|--------|

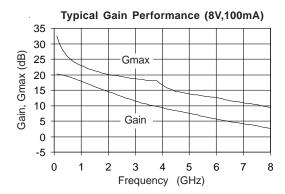

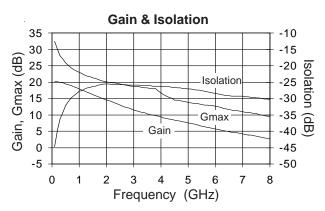

| Gmax               | Maximum Available Gain                 | $Z_s = Z_s^*, Z_L = Z_L^*$                                                                    | 0.90 GHz<br>1.96 GHz     | d B     | -     | 2 3 .3<br>2 0 .1 | -      |

| S 21               | Insertion Gain [1]                     | $Z_s = Z_L = 50 \text{ O hm s}$                                                               | 0.90 GHz<br>1.96 GHz     | d B     | 16.6  | 1 8 .4<br>1 4 .7 | 2 0 .2 |

| Gain               | Power Gain [2]                         | Application Circuit                                                                           | 0.90 GHz<br>1.96 GHz     | d B m   | -     | 1 8 .6<br>1 6 .7 | -      |

| O IP 3             | Output Third Order Intercept Point [2] | Application Circuit                                                                           | 0.90 GHz<br>1.96 GHz     | d B m   | -     | 4 0<br>4 0       | -      |

| P 1 d B            | Output 1dB Compression Point [2]       | Application Circuit                                                                           | 0.90 G H z<br>1.96 G H z | d B m   | -     | 2 7 .2<br>2 7 .5 | -      |

| NF                 | Noise Figure                           | Application Circuit                                                                           | 1.96 GHz                 | d B     | -     | 3 .2             | -      |

| I <sub>D S S</sub> | Saturated Drain Current                | V <sub>D S</sub> = V <sub>D S P</sub> , V <sub>G S</sub> = 0 V                                |                          | m A     | 2 0 4 | 2 9 4            | 3 8 4  |

| g m                | Tranconductance                        | V <sub>D S</sub> = V <sub>D S P</sub> , V <sub>G S</sub> = -0.25 V                            |                          | m S     | 1 4 4 | 198              | 252    |

| V <sub>P</sub>     | Pinch-Off Voltage [1]                  | V <sub>D S</sub> = 2.0 V , I <sub>D S</sub> = 0.6 m A                                         |                          | V       | -3.0  | -1.9             | -1.0   |

| BV <sub>GS</sub>   | Gate-Source Breakdown Voltage [1]      | I <sub>GS</sub> = 1.2 m A , drain open                                                        |                          | V       | -     | -17              | -15    |

| BV <sub>GD</sub>   | Gate-Drain Breakdown Voltage [1]       | $I_{GD} = 1.2 \text{ m A}, V_{GS} = -5.0 \text{ V}$                                           |                          | V       | -     | -22              | -17    |

| Rth                | Therm al Resistance                    | junction-to-le a d                                                                            |                          | °C/W    | -     | 8 0              | -      |

| V <sub>D S</sub>   | Operating Voltage [3]                  | drain-source                                                                                  |                          | V       | -     | -                | 8 .0   |

| I <sub>D Q</sub>   | Operating Current [3]                  | drain-source, quiescent                                                                       |                          | m A     | -     | -                | 160    |

| Poiss              | Power Dissipation [3]                  |                                                                                               |                          | W       | -     | -                | 0.8    |

<sup>[1] 100%</sup> tested - Insertion gain tested using a 50 ohm contact board (no matching circuitry) during final production test.

[3] Maximum recommended power dissipation is specified to maintain  $T_y$ <150C at  $T_L$ =85C.  $V_{DS}^* I_{DQ}$ <0.8W is recommended for continuous reliable operation.

The information provided herein is believed to be reliable at press time. Sirenza Microdevices assumes no responsibility for inaccuracies or omissions.

Sirenza Microdevices assumes no responsibility for the use of this information, and all such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. Sirenza Microdevices does not authorize or warrant any Sirenza Microdevices product for use in life-support devices and/or systems. Copyright 2003 Sirenza Microdevices, Inc. All worldwide rights reserved.

<sup>[2]</sup> Sample tested - Samples pulled from each wafer/package lot. Sample test specifications are based on statistical data from sample test measurements. The test fixture is an engineering application circuit board. The application circuit was designed for the optimum combination of linearity, P1dB, and VSWR.

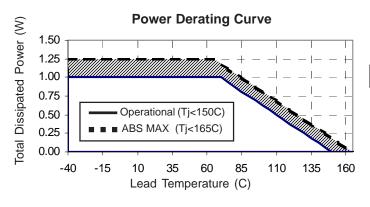

### **Absolute Maximum Ratings**

MTTF is inversely proportional to the device junction temperature. For junction temperature and MTTF considerations the bias condition should also satisfy the following expression:

$$P_{DC} < (T_J - T_L) / R_{TH}$$

where:

$$\begin{split} &P_{DC} = I_{DS} * V_{DS} \text{ (W)} \\ &T_{J} = \text{Junction Temperature (°C)} \\ &T_{L} = \text{Lead Temperature (pin 4) (°C)} \\ &R_{TH} = \text{Thermal Resistance (°C/W)} \end{split}$$

MTTF @ T<sub>i</sub>=150C exceeds 1E7 hours

| Parameter                  | Symbol            | Value       | Unit |

|----------------------------|-------------------|-------------|------|

| Drain Current              | I <sub>DS</sub>   | 200         | mA   |

| Forward Gate Current       | I <sub>GSF</sub>  | 1.2         | mA   |

| Reverse Gate Current       | I <sub>GSR</sub>  | 1.2         | mA   |

| Drain-to-Source Voltage    | V <sub>DS</sub>   | +9.0        | V    |

| Gate-to-Source Voltage     | V <sub>GS</sub>   | <-5 or >0   | V    |

| RF Input Power             | P <sub>IN</sub>   | 200         | mW   |

| Operating Lead Temperature | T <sub>L</sub>    | See Graph   | °C   |

| Storage Temperature Range  | T <sub>stor</sub> | -40 to +150 | °C   |

| Power Dissipation          | P <sub>DISS</sub> | See Graph   | W    |

| Channel Temperature        | $T_{J}$           | +165        | °C   |

Operation of this device beyond any one of these limits may cause permanent damage. For reliable continuous operation, the device voltage and current must not exceed the maximum operating values specified in the table on page 1.

This area not recommended for continuous reliable operation.

Typical Performance - Engineering Application Circuits (See App Note AN-031)

| Freq<br>(MHz) | V <sub>DS</sub> (V) | I <sub>DQ</sub><br>(mÅ) | P1dB<br>(dBm) | OIP3*<br>(dBm) | Gain<br>(dB) | S11<br>(dB) | S22<br>(dB) | NF<br>(dB) |

|---------------|---------------------|-------------------------|---------------|----------------|--------------|-------------|-------------|------------|

| 900           | 8                   | 100                     | 27.2          | 40             | 18.6         | -25         | -13         | 4.7        |

| 1960          | 8                   | 100                     | 27.6          | 40             | 16.7         | -20         | -8          | 3.2        |

| 2140          | 8                   | 100                     | 27.5          | 40             | 15.2         | -24         | -14         | 3.8        |

| 2450          | 8                   | 100                     | 27.3          | 40             | 15.2         | -16         | -14         | 3.1        |

<sup>\*</sup> P<sub>OUT</sub>= +15dBm per tone, 1MHz tone spacing

Data above represents typical performance of the application circuits noted in Application Note AN-031. Refer to the application note for additional RF data, PCB layouts, and BOMs for each application circuit. The application note also includes biasing instructions and other key issues to be considered. For the latest application notes please visit our site at www.sirenza.com or call your local sales representative.

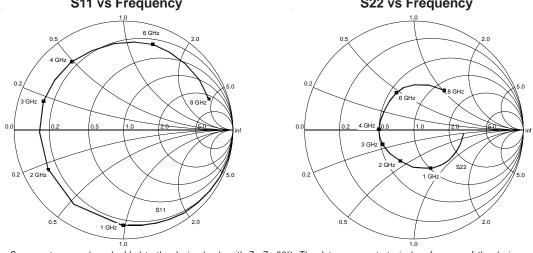

# De-embedded S-Parameters ( $Z_S$ = $Z_L$ =50 Ohms, $V_{DS}$ =8V, $I_{DS}$ =100mA, 25°C)

## S22 vs Frequency

Note: S-parameters are de-embedded to the device leads with  $Z_s = Z_1 = 50\Omega$ . The data represents typical performace of the device. De-embedded s-parameters can be downloaded from our website (www.sirenza.com).

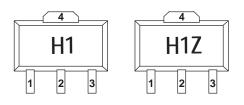

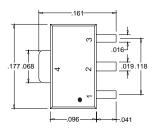

#### **Pin Description**

| Pin # | Function | Description                                                                                                     |  |  |

|-------|----------|-----------------------------------------------------------------------------------------------------------------|--|--|

| 1     | Gate     | RF Input                                                                                                        |  |  |

| 2     | Source   | Connection to ground. Use via holes to reduce lead inductance. Place vias as close to ground leads as possible. |  |  |

| 3     | Drain    | RF Output                                                                                                       |  |  |

| 4     | Source   | Same as Pin 2                                                                                                   |  |  |

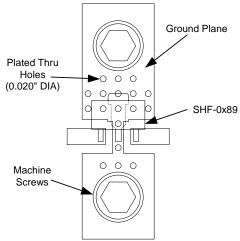

#### **Mounting and Thermal Considerations**

It is very important that adequate heat sinking be provided to minimize the device junction temperature. The following items should be implemented to maximize MTTF and RF performance.

- 1. Multiple solder-filled vias are required directly below the ground tab (pin 4). [CRITICAL]  $\,$

- 2. Incorporate a large ground pad area with multiple plated-through vias around pin 4 of the device. [CRITICAL]

- 3. Use two point board seating to lower the thermal resistance between the PCB and mounting plate. Place machine screws as close to the ground tab (pin 4) as possible. [RECOMMENDED]

- 4. Use 2 ounce copper to improve the PCB's heat spreading capability. [RECOMMENDED]

# Recommended Mounting Configuration for Optimum RF and Thermal Performance

#### **Part Number Ordering Information**

| Part Number | Reel Size | Devices/Reel |

|-------------|-----------|--------------|

| SHF-0189    | 7"        | 1000         |

| SHF-0189Z   | 7"        | 1000         |

#### Part Symbolization

The part will be symbolized with the "H1" designator and a dot signifying pin 1 on the top surface of the package.

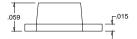

## **Package Dimensions**

DIMENSIONS ARE IN INCHES